## TESIS DE LA UNIVERSIDAD DE ZARAGOZA

2024

123

### Álvaro Manuel Llamazares Prieto

Técnicas de caracterización y mitigación de impedancias parásitas para convertidores basados en tecnología SiC

Director/es

García Gracia, Miguel

Universidad de Zaragoza Servicio de Publicaciones

ISSN 2254-7606

### **Tesis Doctoral**

### TÉCNICAS DE CARACTERIZACIÓN Y MITIGACIÓN DE IMPEDANCIAS PARÁSITAS PARA CONVERTIDORES BASADOS EN TECNOLOGÍA SIC

#### **Autor**

### Álvaro Manuel Llamazares Prieto

Director/es

García Gracia, Miguel

### UNIVERSIDAD DE ZARAGOZA Escuela de Doctorado

Programa de Doctorado en Energías Renovables y Eficiencia Energética

2023

### **Tesis Doctoral**

# Técnicas de caracterización y mitigación de impedancias parásitas para convertidores basados en tecnología SiC

**Autor**

Álvaro Manuel Llamazares Prieto

Director

Miguel García Gracia

Departamento de Ingeniería Eléctrica 2022

A mí familia, por su apoyo incondicional

### Resumen

En los últimos años el desarrollo de convertidores de potencia de última generación demanda densidades de energía más altas, más eficientes y fiables. Los transistores MOSFET de carburo de silicio (SiC) son una prometedora alternativa a día de hoy a la tecnología del silicio (Si). Presentan mejores propiedades térmicas y eléctricas que les permite trabajar a frecuencias de conmutaciones más rápidas. Sin embargo, su implantación presenta un desafío ya que a causa de la rapidez con la que conmuta se excitan las impedancias parásitas, de valor muy bajo, en el bucle de corriente de conmutación. Dando lugar a sobretensiones y oscilaciones no deseadas que aumentan las pérdidas y que limitan el potencial de los SiC MOSFET. El principal objetivo de esta tesis es contribuir al estado del arte para caracterizar y minimizar las impedancias parásitas en el bucle de conmutación.

Para medir las impedancias entre distintos puntos eléctricos separados varios cm se ha implementado una sonda flexible apantallada con terminales de prueba móviles para la medida de impedancias sobre PCB lo que permite evitar los montajes específicos para cada medida que eran necesarios en el uso del analizador vectorial de redes VNA.

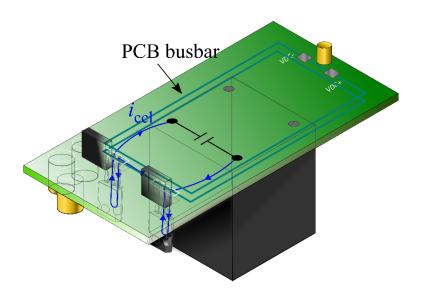

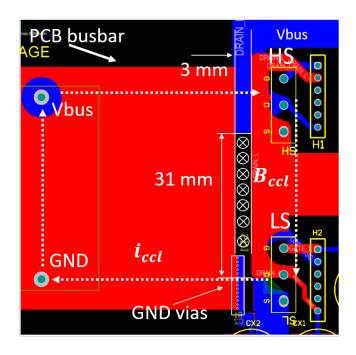

Con el empleo de esta sonda y del propio VNA, se han desarrollado las técnicas de medida para la caracterización de las impedancias parásitas en un semipuente alimentado por un PCB busbar, formado por dos planos paralelos, según la teoría de líneas de transmisión. El procedimiento desarrollado permite además caracterizar las impedancias parásitas del bucle de corriente de conmutación.

También se presentan dos técnicas para el estudio y la mitigación de las oscilaciones no deseadas durante la conmutación a corte. La primera técnica, es una metodología de medida de impedancias para la predicción de la frecuencia de oscilación y la duración de las mismas. La segunda técnica se trata de un apantallamiento magnético localizado sobre el bucle de corriente de conmutación en un semipuente con PCB busbar, que reduce la inductancia parásita del bucle de corriente de conmutación.

### Índice

| Capítulo  | 1.    | Introducción                                                            |

|-----------|-------|-------------------------------------------------------------------------|

| 1.        |       | R                                                                       |

| 1.1.      | Mot   | ivación y antecedentes                                                  |

| 1.2.      | Obje  | etivos 14                                                               |

| 1.3.      | Estr  | uctura de la tesis                                                      |

| Capítulo  | 2     |                                                                         |

| Caracteri | izaci | ón de la impedancia parásita mediante una sonda flexible apantallada 17 |

| 2.        |       | Resumen                                                                 |

| 2.1.      | Intro | oducción17                                                              |

| 2.2.      | Med   | dida de impedancias 19                                                  |

| 2.2.2     | 1     | Medida de impedancias con VNA                                           |

| 2.2.2     | 2     | Sonda flexible para la medida de impedancia 21                          |

| 2.2.3     | 3     | Impedancias parásitas de la sonda                                       |

| 2.2.4     | 4     | Técnicas de mitigación de parásitas24                                   |

| 2.3.      | Mor   | ntaje experimental25                                                    |

| 2.3.2     | 1     | Circuito de referencia                                                  |

| 2.3.2     | 2     | PCB experimentales y VNA                                                |

| 2.4.      | Cara  | acterización de PCB28                                                   |

| 2.4.2     | 1     | Procedimiento de medida directa                                         |

| 2.4.2     | 2     | Procedimiento de ajuste de curva                                        |

| 2.4.3     | 3     | Simulación PEEC                                                         |

| 2.5.   | Res   | ultados                                                      | . 32 |

|--------|-------|--------------------------------------------------------------|------|

| 2.     | 5.1   | Análisis del apantallamiento magnético                       | . 32 |

| 2.     | 5.2   | Procedimiento de medida directa                              | . 35 |

| 2.     | 5.3   | Procedimiento de ajuste de curva                             | . 36 |

| 2.     | 5.4   | Comparación de resultados                                    | . 38 |

| 2.     | 5.5   | Limitaciones de medida grandes planos de Cu                  | . 39 |

| Capítu | ılo 3 |                                                              | 43   |

|        | -     | y medida eléctrica de un PCB busbar con circuitos de parámet |      |

| 3.     |       | Resumen                                                      | 43   |

| 3.1    | Con   | nportamiento eléctrico del bus DC                            | . 43 |

| 3.2    | lmp   | edancia del busbar como línea de transmisión                 | . 50 |

| 3.3    | Circ  | uito equivalente de un semipuente con busbar                 | . 54 |

| 3      | 3.1   | Descripción de las impedancias que constituyen el circuito   | . 54 |

| 3.     | 3.2   | Impedancia de entrada                                        | . 55 |

| 3.     | 3.3   | Dipolo equivalente de carga                                  | . 56 |

| 3.     | 3.4   | Circuito equivalente del bucle de conmutación                | 60   |

| 3.4    | Téc   | nicas de medida                                              | 61   |

| 3.     | 4.1.  | Metodologías de medida de impedancias con VNA                | 61   |

| 3.     | 4.2.  | Medida de un cuadripolo con un VNA                           | 65   |

| 3.     | 4.3.  | Caracterización de Cbus                                      | 66   |

| 3.     | 4.4.  | Procedimiento de calibración                                 | 67   |

| 3.4      | .5.       | Montajes de ensayo                                         | 69  |

|----------|-----------|------------------------------------------------------------|-----|

| 3.4      | .6.       | Medida de la impedancia del circuito de disparo de puerta  | 74  |

| 3.6.1.   |           | Simulación de impedancias                                  | 75  |

| Capítulo | <b>4.</b> |                                                            | 78  |

| Caracte  | rizaci    | ión de la impedancia del bucle de corriente de conmutación | 78  |

| 4.       |           | Resumen                                                    | 78  |

| 4.1.     | Pro       | cedimiento de caracterización                              | 78  |

| 4.2.     | Cara      | acterización de la impedancia CCL                          | 80  |

| 4.2      | .1.       | Extracción de las impedancias parásitas en el CCL          | 80  |

| 4.3.     | Disc      | cusión de los resultados                                   | 85  |

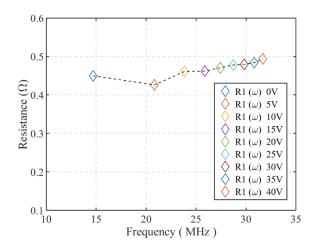

| 4.3      | .1        | Caracterización experimental del SiC MOSFET                | 85  |

| 4.3      | .2        | Caracterización experimental del condensador de bus        | 86  |

| 4.3      | .3        | Caracterización experimental del circuito de driver        | 88  |

| 4.3      | .4        | Caracterización del dipolo de carga ZL                     | 91  |

| 4.3      | .5        | Impedancias discretas del CCL                              | 98  |

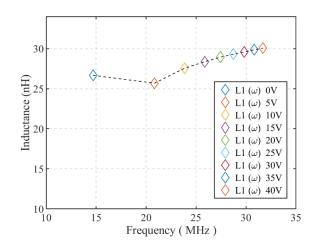

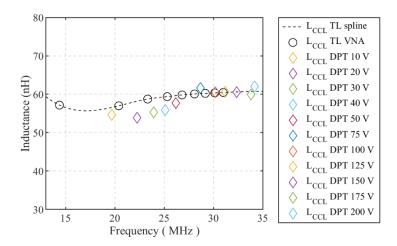

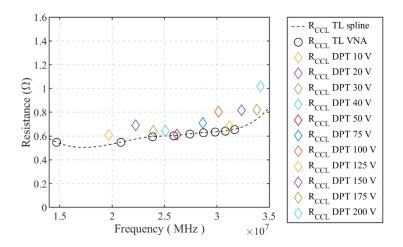

| 4.3      | .6        | Cálculo de la impedancia CCL                               | 99  |

| Capítulo | <b>5.</b> |                                                            | 104 |

| Técnica  | s par     | a la caracterización y mitigación de las oscilaciones      | 104 |

| 5.       |           | Resumen                                                    | 104 |

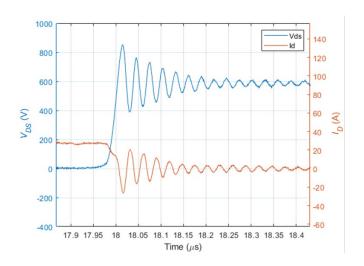

| 5.1.     | Osc       | ilaciones durante la conmutación                           | 104 |

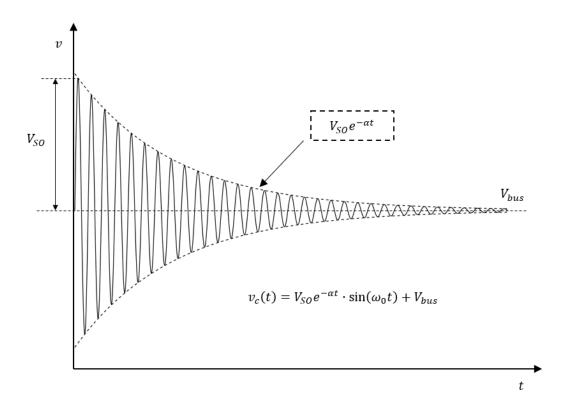

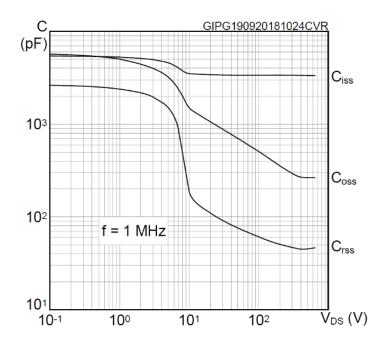

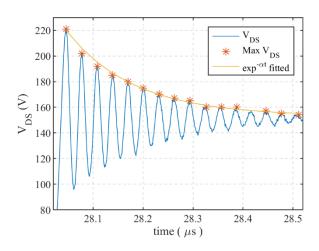

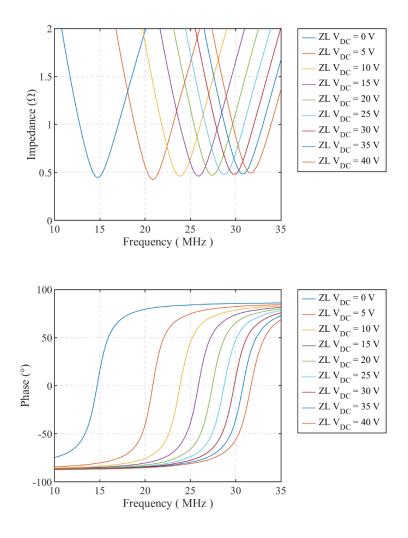

| 5.2.     | Сар       | acidades no lineales del SiC MOSFET                        | 108 |

| 5.3.     | Téc       | nica para la caracterización de las oscilaciones           | 109 |

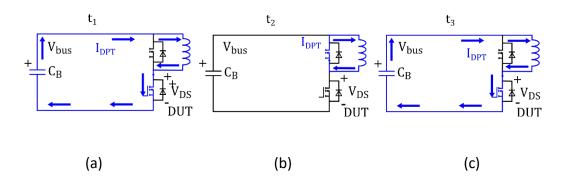

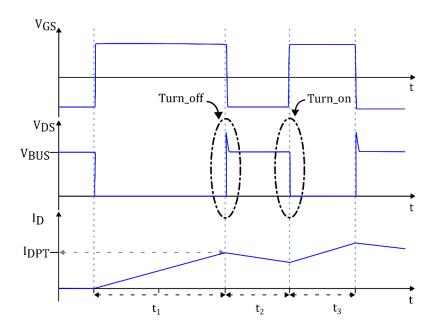

|   | 5.3.    | 1 Ensayo de doble pulso                                                   | .09        |

|---|---------|---------------------------------------------------------------------------|------------|

|   | 5.3.    | 1 Ajuste de la atenuación a partir de la medida del test de doble pulso 1 | .11        |

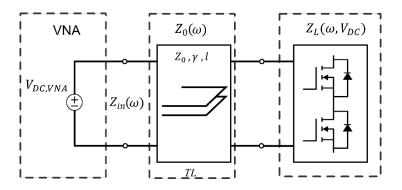

|   | 5.3.    | 1 Método de medida de impedancias por barrido de tensión                  | .12        |

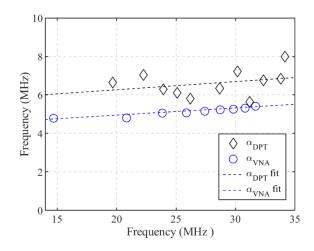

|   | 5.3.    | 1 COMPARACION DE METODOLOGÍAS 1                                           | .16        |

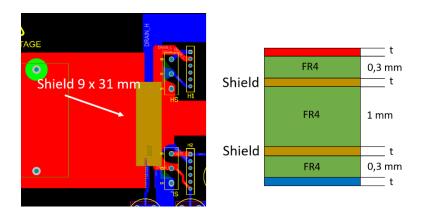

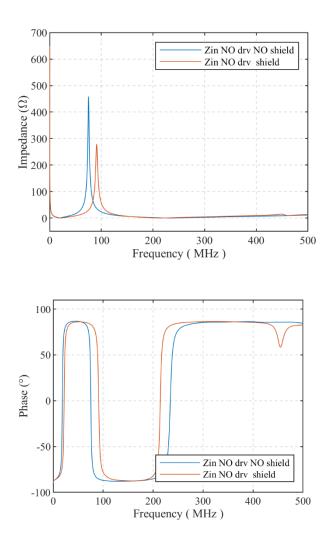

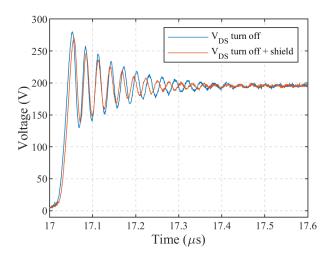

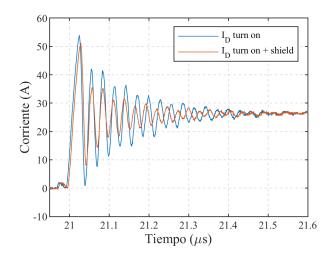

|   | 5.4.    | Metodología de apantallamiento del bucle de corriente de conmutación 1    | .20        |

|   | 5.4.    | 1 Apantallamiento magnético del bucle de conmutación 1                    | .20        |

| C | apítulo | <b>6.</b> 1                                                               | .26        |

| C | onclusi | ones y líneas futuras 1                                                   | .26        |

|   | 6.1.    | Conclusiones                                                              | .26        |

|   | 6.2.    | Contribuciones originales 1                                               | .28        |

|   | 6.3.    | Líneas de trabajo futuras 1                                               | .30        |

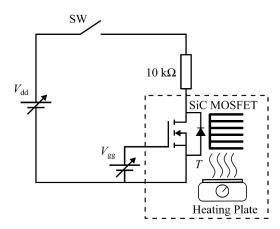

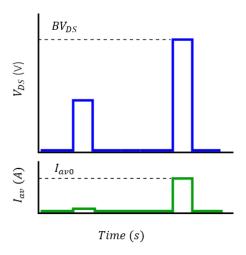

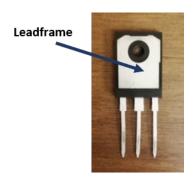

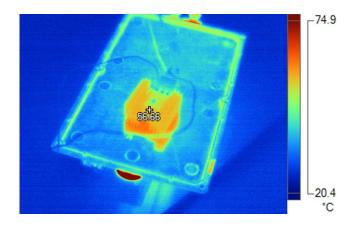

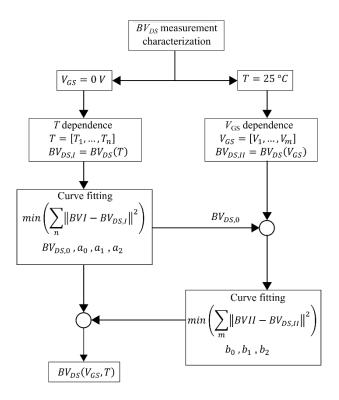

| A | nexo I. | Dependencia de la tensión de avalancha con la tensión de puerta 1         | .31        |

|   | I.A.    | Introducción                                                              | .31        |

|   | I.B.    | Montaje experimental 1                                                    | .32        |

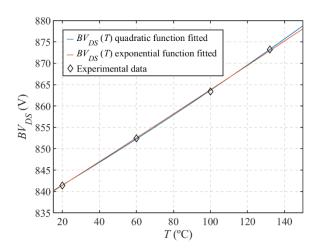

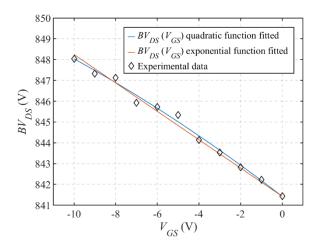

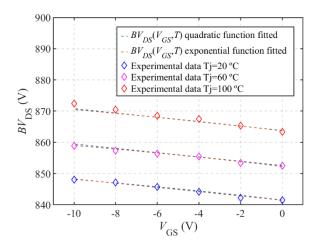

|   | I.C.    | Procedimiento de ajuste y resultados                                      | .35        |

|   | I.C.1.  | Procedimiento de ajuste funciones cuadráticas 1                           | .35        |

|   | I.C.2.  | Función de ajuste por exponenciales1                                      | .38        |

|   | I.C.3.  | Resultados experimentales                                                 | .38        |

|   | ΙD      | Conclusion 1                                                              | <b>4</b> 1 |

### Capítulo 1. Introducción

A continuación, se exponen las motivaciones de la investigación realizada en esta tesis, describiendo el enfoque utilizado para afrontar el trabajo desarrollado y estableciendo los objetivos de la misma.

### 1.1. Motivación y antecedentes

Actualmente existe una demanda creciente en sistemas de conversión de potencia eléctrica basados en semiconductores de potencia que requieren alta eficiencia y alta densidad de energía. El carburo de silicio (SiC) ofrece un desempeño mejorado respecto a los dispositivos basados en silicio (Si). Su potencial de aplicación incluye sectores como son las energías renovables[1], la electrificación del transporte[2], las aplicaciones industriales y domésticas[3].

En base a las propiedades del SiC se espera que en un futuro próximo sustituya en algunas aplicaciones a semiconductores de potencia de Si. En este sentido, los semiconductores basados en tecnología SiC, permiten conmutar a frecuencias más altas que los basados en silicio (Si) y, por tanto, hacen posible alcanzar altas densidades de potencia y eficiencia en convertidores de potencia. Los semiconductores con tecnología de SiC presentan mayor conductividad térmica, mayor campo eléctrico crítico, menor permitividad y mayor velocidad de saturación que los semiconductores de Si [1][4]. Asimismo, presentan una resistencia ideal de conducción menor [5]. Además, dispositivos como el SiC MOSFET, presentan capacidades parásitas más pequeñas entre las uniones de diferentes regiones de drenaje, fuente, y puerta que sus homólogos de Si [6], lo que permite que la conmutación de la tensión y de la corriente se realice en tiempos muy pequeños. Sin embargo, ello da lugar a muy altas variaciones de tensión (dv/dt) y de corriente (di/dt) [7], dv/dt hasta 88 V/ns and di/dt de 4.4 A/ns para transistores SiC MOSFET [8]. Con esas propiedades un convertidor basado en tecnología SiC puede alcanzar bajas pérdidas de potencia por conmutación y conducción en un amplio rango de tensiones y frecuencias de conmutación. Además, debido a las bajas pérdidas que presentan respecto a los dispositivos basados en silicio hacen posible simplificar las topologías de los convertidores a topologías más sencillas con un menor número de dispositivos de potencia para la mayoría de las aplicaciones [9].

Como consecuencia de las rápidas conmutaciones del SiC MOSFET se producen sobretensiones y oscilaciones no deseadas en el transistor. La frecuencia de conmutación en convertidores viene limitada por la amplitud y frecuencia de estas oscilaciones, que dependen de la impedancia en el bucle de corriente de conmutación [10]. Los picos de sobretensión en los SiC MOSFET aparecen durante los transitorios de conmutación a corte debido a las altas di/dt que circulan por las inductancias parásitas del bucle de corriente de conmutación [11]. Estas sobretensiones pueden llegar a ser hasta un 68% mayor que en transistores basados en silicio [12]. Asimismo, pueden ser la causa de sobrecalentamientos, degradación e incluso la destrucción del dispositivo. Las oscilaciones durante la conmutación en los en los SiC MOSFET se producen por la resonancia entre las impedancias parásitas del bucle de corriente de conmutación y las capacidades parásitas del SiC MOSFET [13] [14]. Estas oscilaciones dan lugar a pérdidas adicionales en aplicaciones con frecuencias de conmutación muy altas [15], reduciendo la posibilidad de alcanzar frecuencias de conmutación mayores. También, la duración de la oscilación limita la frecuencia a la que el convertidor puede trabajar de forma segura. Además, las oscilaciones de alta frecuencia causadas por las impedancias parásitas son las principales fuentes de emisión de interferencias electromagnéticas (EMI) [16]-[19] en un convertidor, dificultando el cumplimiento normativo para su comercialización.

Existen diferentes técnicas que abordan como mitigar los efectos de las oscilaciones no deseadas causadas por las impedancias parásitas. La más utilizada consiste en diseñar los convertidores para minimizar la inductancia total del bucle de corriente de conmutación, además se deben escoger componentes que presenten bajas inductancias parásitas[20]-[22]. También es frecuente añadir modificaciones al circuito introduciendo redes de amortiguamiento RC (Snubber) en paralelo con el SiC MOSFET[23]. Sin embargo, las pérdidas aumentan al tener que cargarse y descargarse la capacidad en

paralelo. También existen diferentes circuitos de disparo de puerta activos que controlan la trayectoria de conmutación mediante circuitería externa y cálculos a tiempo real [24].

Por tanto, las impedancias parásitas restringen el total aprovechamiento de los dispositivos con tecnología SiC. Por ello, para conseguir un diseño óptimo de convertidores basados en SiC MOSFET son necesarias técnicas para una caracterización precisa de las impedancias parásitas en el convertidor que faciliten su evaluación y mitigación.

### 1.2. **Objetivos**

Los objetivos establecidos para este trabajo son:

- Desarrollar una técnica para la medida de impedancias parásitas en alta frecuencia (> 100 MHz) en convertidores basados en tecnología SiC.

- Estudio y análisis mediante la teoría de líneas de transmisión de las impedancias parásitas en un semipuente con el busbar diseñado en una placa de circuito impreso (PCB).

- Analizar la impedancia del bucle de corriente de conmutación en la frecuencia.

- Desarrollar una técnica para la predicción de las oscilaciones de alta frecuencia en un semipuente debido a la corriente de conmutación de los SiC MOSFET.

- Desarrollar técnicas que mitiguen los efectos de la impedancia del bucle de corriente de conmutación.

#### 1.3. Estructura de la tesis

Los resultados de la investigación realizada se plasman en este documento de tesis que se ha organizado en cinco capítulos.

El capítulo 1 presenta la motivación que ha llevado a desarrollar esta tesis y se resumen los objetivos planteados. También se describe la estructura de esta tesis.

El capítulo 2 presenta una novedosa sonda flexible apantallada con terminales de prueba móviles. Esta sonda emplea un plano metálico de apantallamiento perpendicular a la PCB que elimina los principales errores de medida causados por la variación en el flujo magnético que existe por el cambio de posición de los terminales de prueba entre calibración y medida.

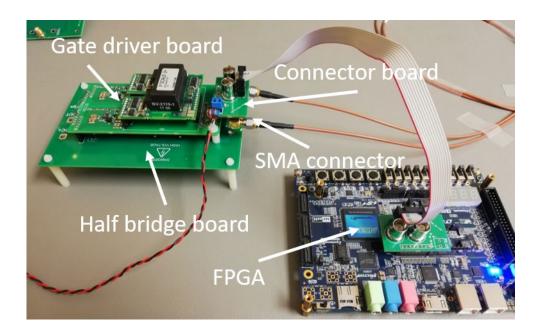

En el capítulo 3 se describe el comportamiento eléctrico de un PCB busbar (dos planos paralelos) mediante circuitos de parámetros distribuidos. Asimismo, se describen las impedancias parásitas de un semipuente con PCB busbar. Además, se describen las configuraciones y metodologías de medida de impedancias, así como sus montajes de ensayo.

En el capítulo 4 se presenta un procedimiento para caracterizar la impedancia del bucle de corriente de conmutación  $Z_{CCL}$  de un semipuente a través de la medida y modelado de cada elemento que lo componen. Estos elementos son el condensador de bus, el busbar laminado, las pistas que conectan con los SiC MOSFET y la conexión con la PCB driver (tarjeta de control de disparo de puerta).

Dos técnicas para el estudio y la mitigación de las oscilaciones no deseadas durante la conmutación a corte se presentan en el capítulo 5. La primera es una metodología de medida de impedancias que permite la predicción de las oscilaciones y la duración de las mismas. La segunda técnica se basa en el apantallamiento magnético localizado sobre el bucle de corriente de conmutación reduciendo el campo magnético total del bucle y por tanto su inductancia.

Finalmente, en el capítulo 6 se resumen las conclusiones y aportaciones de esta tesis, asimismo se proponen líneas futuras de trabajo.

En el Anexo I se describe la dependencia de la tensión de ruptura de avalancha de un SiC MOSFET con la tensión de puerta y la temperatura.

### Capítulo 2.

### Caracterización de la impedancia parásita mediante una sonda flexible apantallada.

Este capítulo presenta una nueva metodología de medida basada en los parámetros-S mediante un analizador vectorial de redes (VNA) y el uso de una sonda flexible apantallada con terminales de prueba móviles. La sonda flexible emplea un plano metálico de apantallamiento perpendicular a la PCB para evitar los principales errores en la medida, los cuales son introducidos por la variación del flujo magnético responsable de la inductancia de bucle durante el barrido de frecuencia del VNA. Se propone un procedimiento mediante ajuste de curvas que consiste en medir la impedancia característica y el tiempo de propagación de las pistas considerando que constituyen líneas de transmisión ideales, valores que son utilizados para realizar un ajuste por mínimos cuadrados no lineales para la línea real (con pérdidas).

#### 2.1. Introducción

Las impedancias parásitas se pueden caracterizar experimentalmente o por simulación electromagnética mediante diferentes métodos numéricos que tienen en cuenta la geometría y los materiales de la PCB [25]. Para la estimación por simulación de las impedancias parásitas existen dos métodos: el de circuitos equivalentes de elementos parciales (PEEC) [26]-[28] y el de análisis por elementos finitos (FEA) [29]-[30]. Ambos métodos se han utilizado para caracterizar las impedancias parásitas en módulos de potencia [27]-[29] y las inductancias parásitas en el bus de continua en inversores con tecnología SiC laminados [31] y en busbar basados en PCB [32]. Los métodos numéricos exigen conocer con exactitud la geometría, los materiales utilizados y sus propiedades para obtener resultados precisos. Por otra parte, presentan un alto coste computacional en estructuras complejas que requieren un análisis en frecuencia.

Las técnicas experimentales pueden ser en el dominio del tiempo o en el de la frecuencia, según sea la respuesta analizada por el equipo de medida. Time Domain Reflectometry (TDR) [33] consiste en obtener la respuesta a escalón o a impulso del circuito. La medida por TDR es una metodología que puede resultar compleja, especialmente porque los errores en frecuencia [34] aparecen en todos y cada uno de los instantes de tiempo requiriendo de un procesado posterior de los datos [35]. La segunda técnica es el test de doble pulso (DPT) utilizado en el estudio de la respuesta de los transitorios de conmutación en una conmutación dura de dispositivos de electrónica de potencia [36] en una rama de semipuente. En este test, el análisis de las conmutaciones permite obtener las pérdidas, visualizar las sobreoscilaciones y estimar la inductancia parásita del bucle de conmutación [37] en una conmutación dura. Es un método muy utilizado para verificar el resultado de la reducción de las parásitas observando la mitigación de las oscilaciones [32]-[38]. Sin embargo, la estimación de la inductancia en el bucle de conmutación se obtiene con la frecuencia de las oscilaciones en la tensión durante la conmutación y la capacidad de la unión del dispositivo de potencia, por lo que no se distinguen cada una de las impedancias parásitas en el convertidor. En [39] los autores caracterizan las impedancias parásitas que afectan a la conmutación de un semipuente con distintos ensayos experimentales basados en la respuesta temporal de la carga y descarga de capacidades conectadas en puntos clave del circuito.

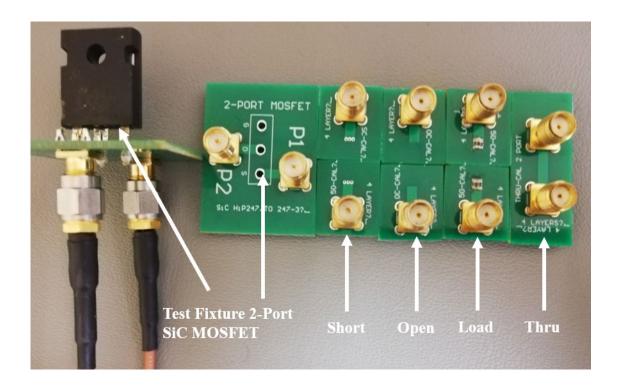

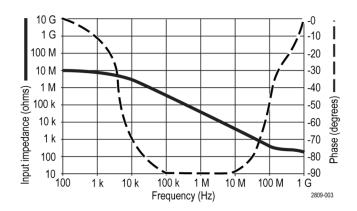

La impedancia en el dominio de la frecuencia se puede medir mediante un analizador de impedancias [40] o con un analizador vectorial de redes (VNA). El analizador de impedancias se ha utilizado para caracterizar la impedancia parásita del bucle de conmutación en inversores trifásicos de dos niveles hasta 100 MHz [32] y en T-Type inverter hasta 10 MHz [41] ambos con montajes de ensayo específicos diseñados ad hoc. También se ha utilizado para caracterizar las impedancias parásitas en dispositivos semiconductores de potencia de Si [42], así como en dispositivos de SiC [43]. El VNA caracteriza la impedancia en el rango que va desde centenas de kHz hasta GHz, a través de los parámetros-S. El VNA se ha empleado para determinar las impedancias parásitas en una PCB de pequeñas dimensiones para un convertidor de Nitruro de Galio (GaN) de baja potencia [44], con las conexiones para las medidas integradas en la propia PCB, es

decir utilizando montajes de ensayo (test fixture) fijos. También se ha empleado para caracterizar las impedancias parásitas en dispositivos discretos y módulos de potencia con técnicas de medida de un puerto y de dos puertos [45]. Por otra parte, los test fixture flexibles comerciales, como el 16089D y E de Keysight, disponibles actualmente, están limitados en frecuencia hasta 13 MHz [46].

### 2.2. Medida de impedancias

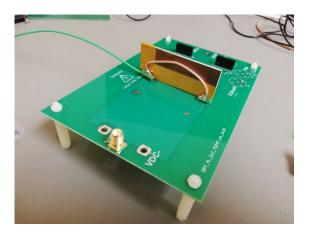

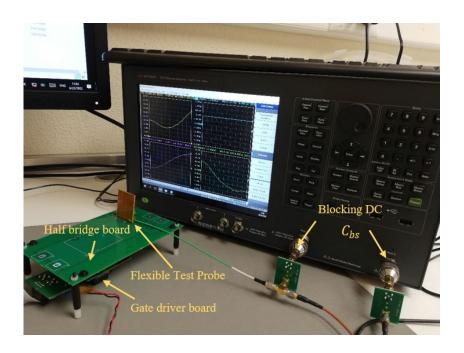

Para la caracterización y estudio de las impedancias parásitas en PCBs se ha desarrollado una sonda flexible apantallada que permite medir las impedancias parásitas en PCB con pistas largas, como las presentes en el busbar laminado de un inversor fotovoltaico, hasta los 350 MHz [47].

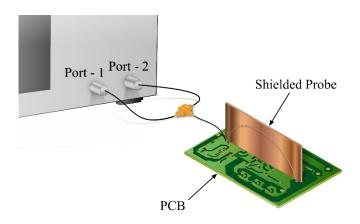

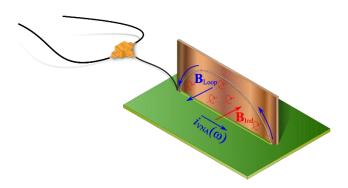

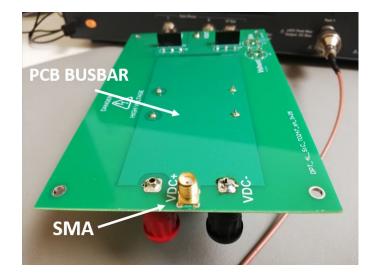

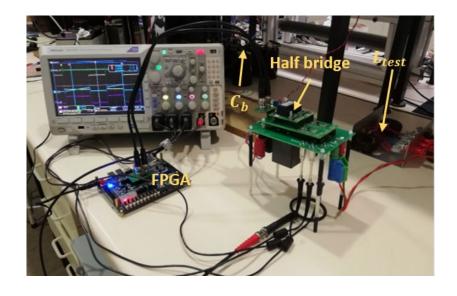

Fig. 2.1. Montaje experimental y la sonda apantallada propuesta.

La caracterización se ha basado en un nuevo test fixture (sonda flexible de prueba) cuyos terminales de medida pueden estar distanciados hasta unos 20 centímetros. La sonda flexible de prueba está formada por una sonda apantallada con una conexión fija y otra flexible, como se muestra en la Fig. 2.1 Para su validación se ha utilizado con una línea de transmisión microstrip, obteniendo resultados muy próximos a los obtenidos con otra microstrip idéntica en base a un test fixture fijo diseñado con el objeto de poder emplearla como referencia. Asimismo, estas medidas se contrastan con las obtenidas

por simulación electromagnética por PEEC y con cálculos obtenidos analíticamente, mostrando una clara mejora en la precisión.

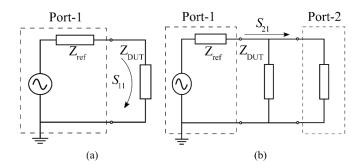

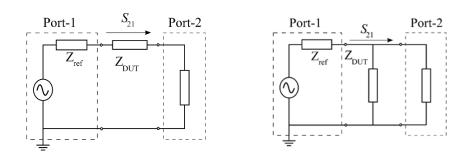

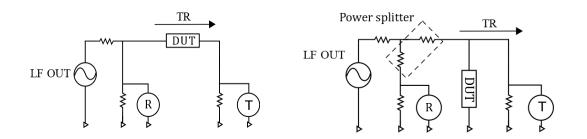

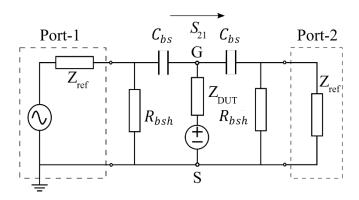

#### 2.2.1 Medida de impedancias con VNA

Con el VNA se miden los parámetros-S del DUT (device under test) conectado, el coeficiente de reflexión (S11) en la configuración de un puerto (Fig. 2.2 (a)) y el de transmisión (S21) en la de dos puertos con el DUT conectado en serie o en shunt(Fig. 2.2(b)). En función de estas medidas y de la medida de referencia ( $Z_{ref}$ ) empleada, en cada uno de estos métodos el valor de la impedancia del DUT viene dada por:

1-port reflection

$$Z_{DUT} = Z_{ref} \frac{1 + S_{11}}{1 - S_{11}} \tag{2.1}$$

2-port series-thru

$$Z_{DUT} = 2Z_{ref} \left( \frac{1}{S_{21}} - 1 \right) \tag{2.2}$$

2-port shunt-thru

$$Z_{DUT} = \frac{Z_{ref}}{2} \left( \frac{S_{21}}{1 - S_{21}} \right) \tag{2.3}$$

La precisión de cada uno de estos métodos depende del rango de valores de impedancia a medir [48]. El método de reflexión con un puerto es adecuado para el rango de impedancias bajas-medias (0.5  $\Omega$  - 2 k $\Omega$ ). En cambio, en el método de dos puertos, la conexión series-thru permite la caracterización de impedancias desde decenas de  $\Omega$  hasta decenas de k $\Omega$ , mientras que la conexión shunt-thru es preferible para bajas impedancias (250  $\mu\Omega$  - 25  $\Omega$ ) como las que presentan las pistas de PCB cuyas inductancias están en el rango de los nH. Por tanto, para la medida de impedancias parásitas en pistas de PCB, dado que el valor de impedancias es bajo, el método de medida que se ha empleado es el de dos puertos shunt-thru.

La conexión del VNA con el DUT requiere normalmente de un test fixture específico. Los test fixture comerciales permiten caracterizar la impedancia de componentes electrónicos discretos en encapsulados estándar, agujero pasante (through-hole) o de montaje superficial (surface mount). Sin embargo, cuando el DUT no es un componente discreto estándar o no es posible conectarlo con un coaxial directamente al VNA, es necesario diseñar una PCB de interconexión (text fixture), entre los puertos del VNA y los terminales del DUT, para poder realizar la medida de la impedancia en función de la frecuencia con precisión. En todos los casos, como parte de la medida, es necesario calibrar el equipo para eliminar la influencia del test-fixture en la medida.

Fig. 2.2. Métodos de medida de impedancias en conexión shunt con un VNA: (a) 1-puerto reflexión, (b) 2 puertos shunt-thru.

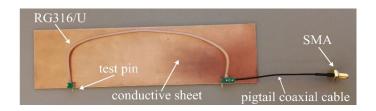

### 2.2.2 Sonda flexible para la medida de impedancia

El objetivo de la sonda propuesta es la caracterización de PCB entre puntos alejados. La sonda, tal como se muestra en la Fig. 2.1, conecta con los terminales PORT-1 y PORT-2 del VNA mediante un conector coaxial en T con terminales SMA y está constituida (ver Fig. 2.3) por un cable coaxial pigtail y un coaxial de tierra RG-316/U que permite el retorno a tierra de la corriente. El pigtail de la sonda está terminado en un conector SMA por un extremo mientras que el otro está abierto. Para facilitar la conexión con el punto de medida en cualquier agujero chapado de la PCB, en el extremo abierto, el conductor central del pigtail está conectado a un pin de prueba mientras que la pantalla se conecta al coaxial de tierra, cuyo conductor central y pantalla están cortocircuitados en ambos extremos. La impedancia característica de ambos cables es de 50  $\Omega$ , como la de los

puertos del VNA. El cable pigtail tiene 100 mm de longitud, 1.37 mm de diámetro externo, mientras que el cable coaxial de tierra RG-316/U es de 220 mm de longitud.

Fig. 2.3. Sonda de prueba flexible para la medida de impedancias.

Respecto al cable de tierra, este es una parte móvil de la sonda que permite adaptarse a diferentes puntos de conexión en PCB, evitando tener que desarrollar un test-fixture fijo para cada medida. Sin embargo, la sonda está situada sobre un plano conductor, aislado, perpendicular al plano horizontal de la PCB donde se van a realizar las medidas. La función de este plano conductor es apantallar el campo magnético cuya fuente es la corriente que circula durante el barrido en frecuencia con el VNA. Es de destacar que, durante el calibrado y la medida, tanto los cables del VNA como el pigtail deben permanecer en la misma posición para evitar errores inaceptables.

### 2.2.3 Impedancias parásitas de la sonda

En la medida de impedancias bajas con la sonda de prueba flexible aparece una impedancia serie parásita que no puede ser compensada completamente con la calibración, lo que limita el alcance en frecuencia de la sonda. Los errores en la medida se deben a las variaciones en las impedancias parásitas de la sonda entre la calibración y la medida.

Por una parte, esto es debido a la variación en la posición espacial de la sonda (respecto a la calibración en circuito abierto) que produce variaciones en las capacidades parásitas entre la sonda y el entorno de medida. Por otra parte, existe una variación en la forma que adopta la sonda flexible de prueba, lo que genera un cambio de inductancia de la sonda respecto a la calibración en cortocircuito. Por tanto, la sonda de prueba flexible se debe mantener en la misma posición durante la calibración y la medida para evitar variaciones en las impedancias parásitas.

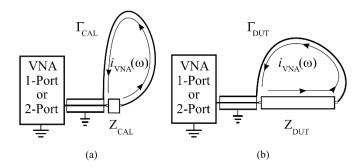

Fig. 2.4. Variación de la trayectoria de la corriente: (a) trayectoria en calibración y (b) trayectoria en la medida de DUT.

Sin embargo, como se observa en la Fig. 2.4, esto no es posible con el cable coaxial de tierra ya que, por la forzosa variación de la forma que adopta el cable en la calibración y la medida, se produce una variación en la inductancia de bucle  $L_{Loop}$  debida al bucle de corriente que hay entre el DUT y la sonda. Aunque si es posible mantener el plano del coaxial de tierra perpendicular a la PCB en ambas medidas, con lo que las variaciones en las capacidades parásitas son despreciables.

La inductancia de bucle  $L_{Loop}$  depende de la corriente  $i_{VNA}(\omega)$  y del flujo magnético  $\Psi$  que encierra el bucle. El campo magnético  $\mathbf B$  está relacionado con el vector potencial magnético  $\mathbf A$  como

$$\mathbf{B} = \nabla \times \mathbf{A} \tag{2.4}$$

Utilizando el Teorema de Stokes el flujo magnético  $\Psi$  a través de la superficie que encierra el bucle  $\Gamma$  es igual a la integral del vector potencial magnético  $\mathbf{A}$  alrededor del bucle  $\Gamma$ , de modo que la inductancia de bucle se puede expresar como

$$L_{loop} = \frac{1}{i_{\text{VNA}}} \cdot \oint_{\Gamma} \mathbf{A} \cdot d\mathbf{l}$$

(2.5)

Expresión válida siempre que la densidad de corriente sea constante y no haya materiales magnéticos no lineales en el medio circundante. Por tanto,  $L_{Loop}$  es función de la forma del bucle y su dimensión, así como de las propiedades magnéticas del medio circundante. Como se puede observar en la Fig. 2.4, el contorno del bucle  $\Gamma_{CAL^{\perp}}$  durante la calibración es diferente al que se tiene en la medida del DUT,  $\Gamma_{DUT}$ , debido a las diferentes longitudes del DUT y de la carga de calibración, por lo que la  $L_{Loop}$  es diferente en ambas situaciones.

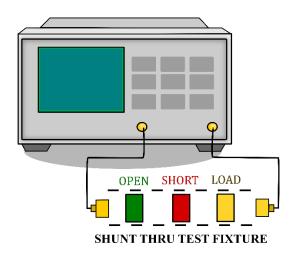

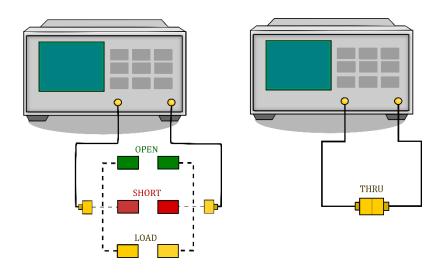

### 2.2.4 Técnicas de mitigación de parásitas

Mediante la calibración con diferentes cargas, las impedancias parásitas de la sonda, el conjunto de cables y los conectores coaxiales que conectan hasta los puertos de medida del VNA son medidas y compensadas. El estándar de calibración utilizado en el VNA es el SOL que consiste en calibrar con tres cargas: un cortocircuito (S), un circuito abierto (O) y una carga de  $50 \Omega$  (L).

Las impedancias parásitas debidas a la posición del coaxial de tierra no pueden ser eliminadas, pero sí minimizadas. Para ello, se mantiene el cable de tierra siempre perpendicular al plano de medida como se muestra en la Fig. 2.5, donde el cable de tierra se ha fijado a un soporte de material no magnético.

Fig. 2.5. Sonda con técnicas de mitigación de parásitas.

La inductancia del bucle que crea el cable de tierra se puede evitar anulando el campo magnético  ${\bf B}_{\rm Loop}(\omega)$  cuya fuente es la propia corriente de medida  $i_{VNA}(\omega)$  .Para ello, como apantallamiento se emplea una chapa de cobre, con un espesor de 35  $\mu$ m, a la

que se une el cable de tierra. Como se puede advertir en la Fig. 2.5 corrientes de Foucault son inducidas con la misma frecuencia que  $i_{VNA}(\omega)$  y circulan en bucles cerrados en el apantallamiento de cobre. Asimismo, debido a estas corrientes inducidas se genera un campo magnético  $\mathbf{B}_{\mathrm{ind}}(\omega)$  que se opone al campo que las origina.

De este modo, se consigue reducir el flujo magnético total responsable de la inductancia de bucle durante el barrido de frecuencia del VNA. Sin embargo, en el rango de frecuencias de interés, el uso de la placa de apantallamiento cambia ligeramente la impedancia de pista de la PCB debido al efecto proximidad, el cual afecta al factor de atenuación, como se ha señalado en el apartado 2.5.3.

### 2.3. Montaje experimental

#### 2.3.1 Circuito de referencia

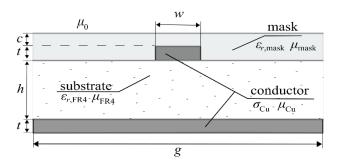

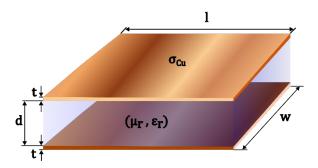

Los microstrips son líneas de transmisión ampliamente estudiadas en la literatura[49],[50], por lo que se ha elegido como circuito de referencia. Como se muestra en la Fig. 2.6, un microstrip está formado por dos conductores de cobre, de conductividad  $\sigma_{Cu}$ , impresos en cada una de las caras externas del sustrato dieléctrico con espesor h y permitividad dieléctrica  $\varepsilon_{r,FR4}$ .

Fig. 2.6. Estructura de un microstrip.

El conductor de la señal de anchura w y espesor t está situado en la cara superior de la PCB (ver Fig. 2.6). Como plano de tierra se dispone un conductor de anchura g y espesor t situado en la cara inferior. Los medios que forman la estructura son no magnéticos, su permeabilidad magnética se considera la misma que en el vacío  $\mu_0$  ( $\mu_{mask} \approx \mu_{FR4} \approx$

$\mu_{Cu} \approx \mu_0$ ). Una máscara aislante protectora cubre la PCB de permitividad relativa  $\varepsilon_{r,mask}$  similar a la del sustrato y permeabilidad la del vacío. Los parámetros geométricos y propiedades físicas utilizadas para la fabricación de la línea de transmisión microstrip utilizada se dan en la Tabla 2.1.

Tabla 2.1. Parámetros de diseño del microstrip de referencia

| Símbolo                   | Descripción               | Valor   |

|---------------------------|---------------------------|---------|

| w                         | Ancho de pista            | 0.21 mm |

| t                         | Espesor de la pista       | 40 μm   |

| g                         | Ancho del plano de tierra | 29.3 mm |

| I                         | Longitud de la pista      | 122 mm  |

| h                         | Altura del sustrato       | 1.6 mm  |

| С                         | Altura de la máscara      | 25 μm   |

| $arepsilon_{r,	ext{FR4}}$ | Permitividad relativa FR4 | 4.6     |

| $\mathcal{E}_{r,mask}$    | Permitividad relativa     | 3.5-4.2 |

Aunque hay dos medios de propagación (sustrato y máscara), dado que las dimensiones geométricas del microstrip son mucho menores que la longitud de onda  $\lambda$ , se considera que el campo eléctrico y magnético carecen de componentes en la dirección de propagación y se propaga como una onda transversal electromagnética (TEM). Este tipo de propagación permite resolver los campos como si fueran cuasi-estáticos (DC). Dentro de esta aproximación, en el cálculo de la impedancia característica  $Z_0$  se sustituyen los medios sustrato-máscara, por un medio homogéneo con constante dieléctrica efectiva  $\varepsilon_{r,eff}$  [51],[52] que depende de la geometría y propiedades de los medios. Con lo que es posible expresar  $Z_0$  en función de  $\varepsilon_{r,eff}$  y de la capacidad  $C_a$  ( $\varepsilon_r=1$ ) por unidad de longitud de la misma estructura con aire en lugar de máscara, según[53].

$$Z_0 = \left(c \cdot C_a \cdot \sqrt{\varepsilon_{r,eff}}\right)^{-1} \tag{2.6}$$

y la constante de fase  $\beta$  en función de la frecuencia angular  $\omega$  como

$$\beta = \omega \cdot \sqrt{\varepsilon_{r,eff}} \cdot c^{-1} \tag{2.7}$$

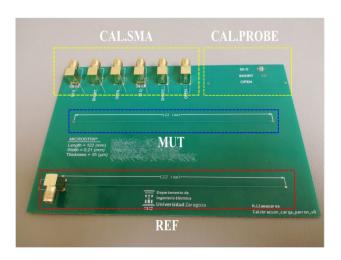

Fig. 2.7. PCB Experimental desarrollada para los ensayos de validación.

### 2.3.2 PCB experimentales y VNA

Para validar la metodología propuesta se ha desarrollado una PCB experimental (Fig. 2.7) para realizar los ensayos al objeto de validar el procedimiento de medida propuesto.

Respecto a la PCB, el sustrato escogido es FR4, el acabado que protege las pistas de cobre de corrosión es electroless nickel immersion gold (ENIG) y el espesor de la máscara, aunque no está especificado por el fabricante, se considera de al menos 25  $\mu$ m según [54].

Como se observa en la Fig. 2.7, en la PCB experimental hay dos líneas de transmisión microstrip (MUT y REF) idénticas de longitud 122 mm cuyos parámetros son los definidos en la Tabla 2.1.. Ambas líneas están terminadas en un extremo por un cortocircuito hecho con una vía (todas las vías utilizadas son de 0.762 mm de diámetro). La línea de transmisión considerada de referencia (REF) tiene un conector coaxial SMA que se conecta mediante cables coaxiales al VNA. La otra línea de transmisión (MUT), dedicada al método de medida con la sonda flexible de prueba, tiene en ambos extremos dos vías para conectar los pines de prueba de la sonda desarrollada. Además,

como se puede observar en la parte superior de la Fig. 2.7, hay dos kits de cargas de calibración: CAL.SMA para utilizar con la línea REF y CAL.PROBE para la línea MUT. El kit de calibración CAL.SMA emplea el mismo tipo de conector (SMA) que la línea REF para compensar el error que introduce el conector en la medida. La precisión de las cargas de 50  $\Omega$  es del 1% conectadas con pistas lo más cortas y anchas posibles. En el kit CAL.PROBE, para minimizar las impedancias parásitas de la carga de 50  $\Omega$ , se utiliza un encapsulado 0603. El mismo tipo de pistas (cortas y anchas) se emplea en la carga de cortocircuito.

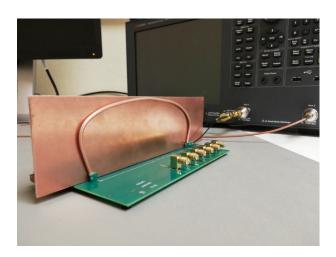

Fig. 2.8. Medida de la línea MUT con la sonda diseñada y el VNA.

Para la caracterización de la impedancia se ha utilizado el VNA E5061B de Keysight (Fig. 2.8), que calcula la impedancia a partir de los parámetros de dispersión [48].

### 2.4. Caracterización de PCB

### 2.4.1 Procedimiento de medida directa

El comportamiento de la línea de transmisión se caracteriza por su impedancia característica  $Z_0$  y por su constante de propagación  $\gamma$ . Como el rango de frecuencia de medida está por debajo de 1 GHz, la conductancia del sustrato de la PCB se puede considerar despreciable frente a la capacidad C de la línea  $\gamma$ , si las pistas tienen una

resistencia despreciable frente a la inductancia L, su comportamiento se puede aproximar por el de una línea sin pérdidas, cuya impedancia característica es

$$Z_0 = \sqrt{\frac{L}{C}} \tag{2.8}$$

y la constante de propagación un número complejo puro igual a la constante de fase β

$$\gamma = i\beta = i\sqrt{LC} \tag{2.9}$$

La caracterización frecuencial de una pista de PCB puede realizarse con la línea terminada en circuito abierto o en cortocircuito. Aunque, para visualizar el error introducido por la inductancia parásita debida a la corriente de retorno a tierra, se ha elegido una línea terminada en cortocircuito ya que entonces la línea presenta carácter inductivo hasta que alcanza la frecuencia de antirresonancia.

En condiciones de cortocircuito, la impedancia de entrada  $Z_i$  de una línea sin pérdidas y de longitud l es un valor complejo dado por [55]

$$Z_i = jZ_0 \cdot tan(\beta l) \tag{2.10}$$

El producto de la constante de fase  $\beta$  de la onda y la longitud l de la línea se conoce como longitud eléctrica  $\theta$  y su relación con la longitud de onda  $\lambda$  es

$$\theta = 2 \cdot \pi \cdot l \cdot \lambda^{-1} \tag{2.11}$$

La longitud de onda es el cociente entre la velocidad de propagación de la onda en el medio  $v_p$  y su frecuencia f, reordenando los términos en (2.11) se puede expresar la longitud eléctrica  $\theta$  en función de la frecuencia angular  $\omega$  de la onda y se obtiene

$$\theta = \omega \cdot l \cdot v_p^{-1} \tag{2.12}$$

relación que puede expresarse en función del tiempo de retardo de la línea  $t_{pd}$  (tiempo que tarda una onda en recorrer 1 m a la velocidad de propagación  $v_p$ ) como

$$\theta = \omega \cdot l \cdot t_{pd} \tag{2.13}$$

Según (2.10), cuando  $\theta=\pi/2$  la impedancia de entrada presenta un máximo, lo que ocurre para una longitud de onda de  $\lambda/4$  y a la frecuencia de antirresonancia  $f_{\lambda/4}$ , como se observa en la Fig. 2.12 Por tanto, de la medida experimental se obtiene directamente  $\omega_{\lambda/4}$  lo que permite calcular  $t_{pd}$  y  $v_p$  a partir de la relación

$$t_{pd} = \pi \cdot \left(2 \cdot \omega_{\lambda/4} \cdot l\right)^{-1} \tag{2.14}$$

Por otra parte, la impedancia característica de la línea  $Z_0$  se obtiene del valor de la medida a  $f_{\lambda/8}$ , ya que, de acuerdo con (2.10), para una longitud  $\lambda/8$  ( $\theta=\pi/4$ ), la impedancia medida es directamente  $Z_0$ . Este análisis es similar e igualmente válido para líneas de transmisión terminadas en circuito abierto. Mediante  $f_{\lambda/4}$  y  $f_{\lambda/8}$  se puede caracterizar con el mismo procedimiento una línea de transmisión terminada en circuito abierto debido a la dependencia de la impedancia de entrada con la cotangente de  $\theta$ .

#### 2.4.2 Procedimiento de ajuste de curva

En una línea de transmisión ideal en cortocircuito, la impedancia a la frecuencia de antirresonancia tiende a infinito. Sin embargo, la medida de la impedancia, obtenida a  $f_{\lambda/4}$ , siempre es un valor finito. Por tanto, la línea de transmisión se está comportando como una línea con bajas pérdidas cuya constante de atenuación  $\alpha$  es distinta de cero. La consideración de un modelo de línea con pérdidas implica la introducción de nuevas incógnitas: además de  $Z_0$  y  $t_{pd}$  se introduce la incógnita  $\alpha$  que se puede aproximar en el caso de bajas pérdidas por [55]

$$\alpha \approx \frac{1}{2} \cdot (R \cdot Z_0^{-1} + G \cdot Z_0) \tag{2.15}$$

Donde R es la resistencia por unidad de longitud y G la conductancia por unidad de longitud. Despreciando la resistencia en DC, R es proporcional a la raíz de la frecuencia debido al efecto skin y G depende directamente de la frecuencia, por tanto,  $\alpha$  se puede expresar en función de las constantes  $k_1$  y  $k_2$  como

$$\alpha \approx k_1 \cdot \sqrt{f} + k_2 \cdot f \tag{2.16}$$

$Z_0$  y  $t_{pd}$  son calculadas mediante el procedimiento de medida directa y se estiman utilizando el método de mínimos cuadrados no lineales[56], el cual también es aplicado para averiguar  $k_1$  y  $k_2$ . Con el método de mínimos cuadrados no lineales se resuelve la ecuación

$$min\left(\sum_{f} \left\|Z_{i} - Z_{VNA}\right\|^{2}\right) \tag{2.17}$$

donde  $Z_i$  se expresa como

$$Z_i = |Z_0 \cdot tanh(\gamma \cdot l)| \tag{2.18}$$

y  $Z_{VNA}$  son los valores experimentales medidos con el VNA.

Los valores de  $Z_0$ ,  $t_{pd}$ ,  $k_1$  y  $k_2$ . se iteran hasta alcanzar un resultado satisfactorio con un coeficiente  $R^2$  mayor de 0.95.

#### 2.4.3 **Simulación PEEC**

El método de circuitos equivalentes de elementos parciales (PEEC) permite convertir la disposición física de los conductores de un circuito en una red de circuitos de elementos concentrados. PEEC analiza problemas estáticos y cuasi-estáticos y es utilizado para extraer las inductancias y capacidades parásitas en encapsulados de módulos de

potencia, embarrados, bus bar y para aplicaciones de compatibilidad electromagnética (EMC)[27].

La línea microstrip se ha modelado en PEEC como dos conductores rectangulares según los datos de la Tabla 2.1. Para obtener la impedancia característica y el tiempo de retardo del microstrip se simulan dos condiciones estáticas. En primer lugar, se considera los conductores rodeados de aire, sin sustrato, ni máscara. Del análisis PEEC se obtiene la capacidad equivalente entre ambos conductores que forman el microstrip y, dividiendo por la longitud de la línea de transmisión, su valor por unidad de longitud con sustrato aire  $C_a$ . En segundo lugar, se considera el sustrato FR4 y la máscara de soldadura con permitividad relativa  $\varepsilon_{r,mask}=4.2$  y altura constante 25 µm. La capacidad por unidad de longitud obtenida en estas condiciones es  $C_{FR4}$ . El cociente entre ambas es la llamada constante dieléctrica efectiva ( $\varepsilon_{r,eff}$ )

$$\varepsilon_{r,eff} = C_{FR4}/C_a \tag{2.19}$$

La impedancia característica  $Z_0$  de la línea de transmisión microstrip se calcula mediante (2.6) con  $C_a$  y  $\varepsilon_{r,eff}$  obtenidas en el análisis PEEC se calcula la impedancia característica  $Z_0$  de la línea microstrip, mientras que el retardo de propagación  $t_{pd}$  por unidad de longitud en una línea de transmisión sin pérdidas se obtiene como

$$t_{pd} = \sqrt{\varepsilon_{r,eff}}/c \tag{2.20}$$

#### 2.5. Resultados

# 2.5.1 Análisis del apantallamiento magnético

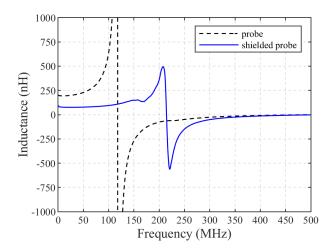

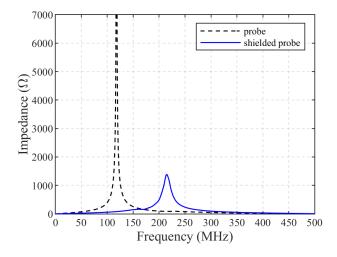

Para valorar los efectos de la pantalla metálica en la sonda propuesta, se caracteriza la sonda con y sin pantalla magnética. En la Fig. 2.9 se comparan las medidas de la inductancia para ambas sondas. El valor de la inductancia de la sonda apantallada incluye el pigtail, el conector SMA y el cable de tierra. Así, por ejemplo, para una frecuencia de 10 MHz, la inductancia medida en la sonda sin apantallamiento es de 184 nH y con el apantallamiento su valor se reduce a 77.54 nH.

Fig. 2.9. Inductancia medida con la sonda con y sin apantallamiento durante la calibración en cortocircuito entre 100 kHz y 500 Mhz.

Fig. 2.10. Impedancia medida con la sonda con y sin apantallamiento durante la calibración en cortocircuito entre 100 kHz y 500 Mhz.

Como se observa en la Fig. 2.9, la sonda sin apantallamiento se comporta como una inductancia hasta la frecuencia de resonancia de 124 MHz, después predomina el efecto capacitivo. Cuando se apantalla el bucle de retorno a tierra, es decir con la sonda con pantalla, la frecuencia de resonancia se elevada hasta los 218 MHz debido a la reducción de la inductancia de bucle. Además, aparece una atenuación en la impedancia debida a un aumento en la disipación de potencia (Fig. 2.10).

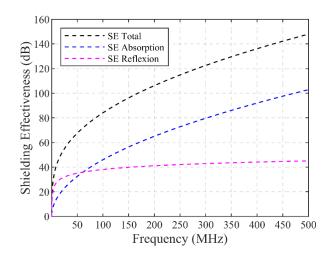

La efectividad del apantallamiento ( $SE_{dB}$ ) viene definida por la atenuación del campo magnético después de atravesar el apantallamiento. En este sentido, las pérdidas del apantallamiento se deben a las pérdidas de absorción  $A_{dB}$  y pérdidas de reflexión  $R_{dB}$  [57]. Debido al efecto Joule, en el interior del apantallamiento metálico aparecen las pérdidas de absorción cuando circulan las corrientes de Foucault. Estas pérdidas por absorción dependen de la profundidad de penetración del efecto skin y del espesor del apantallamiento, de forma que a menor espesor menores pérdidas por absorción. Por otra parte, como consecuencia de la diferencia entre las impedancias características que hay entre el medio por donde se propaga la onda incidente (aire) y el cobre de la pantalla aparecen las denominadas pérdidas por reflexión.

Fig. 2.11. Eficacia del apantallamiento magnético propuesto.

En la Fig. 2.11 se muestra la  $SE_{dB}$  para una lámina de cobre de 35 µm, considerando una distancia de 1.5 mm entre el conductor central del cable de tierra y el plano de apantallamiento. Estos cálculos se han realizado según las expresiones aproximadas para el apantallamiento del campo magnético cercano para el cobre [57]

$$A_{dB} = 8.686 \cdot (s/\delta) \tag{2.21}$$

$$R_{dB} = 14.57 + 10 \cdot log(f \cdot r^2) \tag{2.22}$$

$$SE_{dB} = A_{dB} + R_{dB} + MR_{dB}$$

(2.23)

donde s es el espesor del apantallamiento de cobre,  $\delta$  es la profundidad de penetración por efecto skin en el cobre, f es la frecuencia y r es la distancia al apantallamiento. El término  $MR_{dB}$  corresponde a las pérdidas debidas a las múltiples reflexiones que aparecen dentro del cobre de apantallamiento.

De esta forma, a 1 MHz la atenuación calculada es de 19 dB y se incrementa con la frecuencia. Sin embargo, para frecuencias por debajo de 1 MHz el apantallamiento se observa que es menos efectivo, 4.7 dB a 200 kHz. Por todo ello, finalmente se opta por una pantalla con un segundo plano de cobre de las mismas características y distanciado 1.6 mm del anterior para reforzar la atenuación en el campo magnético para frecuencias por debajo de 1 MHz. Para la construcción del doble apantallamiento se ha utilizado una PCB de dos caras con cobre de espesor 35 μm.

#### 2.5.2 Procedimiento de medida directa

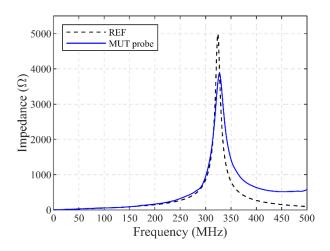

A continuación, se presentan los resultados de la caracterización de las microstrips REF y MUT aplicando el procedimiento de medida directa que ha sido descrito en 2.4.1. La medida del microstrip REF se realiza a través de una conexión SMA fija, mientras que la medida de la línea MUT se lleva a cabo con sonda flexible apantallada propuesta.

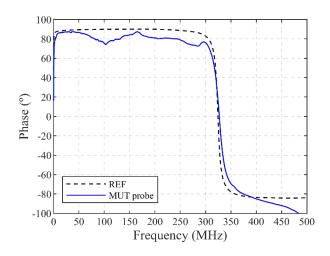

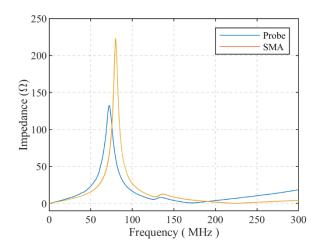

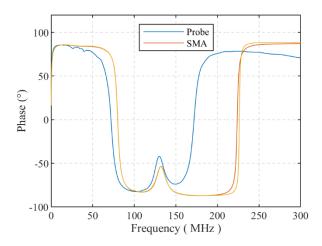

En la Fig. 2.12 y Fig. 2.13 se muestra la impedancia y la fase de las líneas REF y MUT medidas en función de la frecuencia, hasta 500 MHz. La frecuencia de antirresonancia medida, que corresponde con una longitud de onda de  $\lambda/4$ , es 324.41 MHz en la línea REF y 327.22 MHz en la MUT. En la Fig. 2.12 se puede ver que el pico de antirresonancia, donde el carácter de la impedancia cambia de inductivo a capacitivo, es mayor en la línea REF que en la línea MUT. Ello es debido a que en la línea MUT, las pérdidas por efecto skin en el apantallamiento no han sido totalmente compensadas por el cambio de geometría de la sonda. En una línea de transmisión ideal la impedancia en antirresonancia es infinita y su valor se reduce, a medida que la componente resistiva aumenta. Lo mismo se puede concluir de la Fig. 2.13 donde se observa una menor pendiente (en el cambio de fase) en la línea MUT que en la línea REF.

Esta figura también revela como la fase supera los -90º a partir de 380 MHz, debido probablemente a una capacidad parásita equivalente que no ha sido compensada durante el calibrado. Esta capacidad limita en frecuencia el alcance de la sonda.

Fig. 2.12. Impedancia medida en la línea REF y MUT desde 100 kHz hasta 500 MHz.

Fig. 2.13. Fase de la impedancia medida en la línea REF y MUT desde 100 kHz hasta 500 MHz.

#### 2.5.3 Procedimiento de ajuste de curva

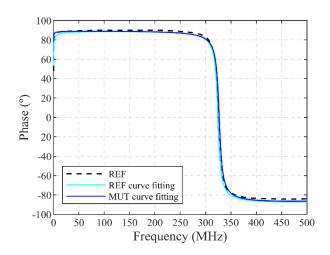

Como se ha descrito en 2.4.2, el comportamiento de la línea microstrip se puede asemejar al de una línea con pérdidas, utilizando un método iterativo (procedimiento de ajuste de curvas) para la medida de la impedancia. Este método se ha aplicado a las líneas REF y MUT, cuyas medidas son realizadas con conectores SMA fijo y con sonda

flexible respectivamente. La frecuencia máxima de ajuste considerada en el procedimiento ha sido de 350 MHz.

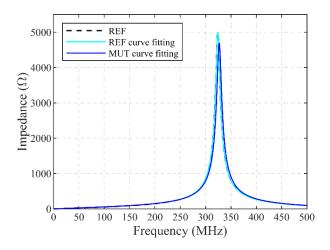

Fig. 2.14. Impedancia de la línea REF y MUT ajustadas por el procedimiento de ajuste de curvas.

Fig. 2.15. Fase de la línea REF y MUT ajustadas por el procedimiento de ajuste de curvas.

En la Fig. 2.14 y Fig. 2.15 se muestra la impedancia y la fase de las líneas REF y MUT en función de la frecuencia. La frecuencia de antirresonancia que se obtiene ahora es de 324.34 MHz en la línea REF (prácticamente el mismo resultado que antes) y 326.92 MHz en la MUT, es decir el error con sonda flexible se consigue reducir a 0.8%.

El resultado del procedimiento de ajuste de curvas aplicado a la medida con terminal SMA en la línea REF da un valor máximo para  $\alpha$  de 0.21 Np/m a 500 MHz Este valor contrasta con el que se obtiene con sonda flexible para la línea MUT, que da un valor de 0.24 Np/m. Es un error del 14.3% debido a que existe una atenuación o pérdidas en la sonda flexible que no se han considerado en el modelo de ajuste y, existen, y son incluidas en la atenuación de la constante de propagación.

## 2.5.4 Comparación de resultados

En la Tabla 2.2 se comparan los resultados obtenidos para la impedancia característica  $Z_0$  y el retardo de propagación  $t_{pd}$  obtenidos experimentalmente por el procedimiento de medida directa y de ajuste de curvas, con los obtenidos por simulación PEEC y con los que se obtienen analíticamente empleando las fórmulas[58] con los parámetros del microstrip dados en la Tabla 2.1. Los resultados de la simulación por PEEC se han obtenido según las expresiones (2.19) y (2.20) calculando la capacidad del microstrip rodeado de aire y sin sustrato  $C_a$ , y la capacidad del microstrip considerando el sustrato FR4 y una máscara con permitividad relativa  $\varepsilon_{r,mask}=4.2$ .

La comparación de los resultados (Tabla 2.2) se realiza tomando como referencia el resultado obtenido con el procedimiento de ajuste de curvas sobre la línea microstrip REF. De esta forma, el tiempo de propagación, en todos los casos, presenta un error inferior al 1%. Sin embargo, los errores son mayores en el caso de la impedancia característica, alcanzando valores de hasta el 12.7 % en simulación PEEC, debido probablemente a la imposibilidad de modelar las pistas conductoras reales, ya que estas tienen tolerancias, rugosidades y, generalmente, son de perfil trapezoidal. El error (9.51%) en la impedancia característica obtenida analíticamente con la formula [58] está probablemente causado por la precisión de la expresión en función de la geometría del microstrip y por considerar la máscara como uniforme y de altura constante sobre el conductor superior.

La aplicación del procedimiento de medida directa sobre la línea MUT da un error del 1.96 % en impedancia y del 0.89% en el tiempo de propagación. Estos errores son principalmente debidos a la variación de la impedancia por los cambios en la forma de

la sonda entre la calibración y la medida. Asimismo, la consideración de línea sin pérdidas, aunque simplifica el procedimiento de cálculo, introduce como se está viendo un cierto error.

El procedimiento de ajuste de curvas aplicado a la línea MUT con la sonda propuesta presenta errores de 1.37% en impedancia y 0.81% en el tiempo de propagación. Valores muy precisos para una técnica que presenta la ventaja de poder determinar la impedancia de una pista larga en una PCB, con los puntos de conexión separados varios centímetros evitando desarrollar un test fixture fijo para cada pista.

Tabla 2.2. Impedancia característica y retardo de la propagación estimado

|                    | Z <sub>0</sub> (Ω) | t <sub>pd</sub> (ns/m) | ε <sub>rror</sub> Z <sub>0</sub> (%) | Error $t_{pd}$ (%) |

|--------------------|--------------------|------------------------|--------------------------------------|--------------------|

| REF medida directa | 100,54             | 6,316                  | -1,91                                | -0,03              |

| REF curve fitting  | 102,50             | 6,318                  | -                                    | -                  |

| MUT medida directa | 104,51             | 6,262                  | 1,96                                 | 0,89               |

| MUT curve fitting  | 103,9              | 6,267                  | 1,37                                 | 0,81               |

| Formula [58]       | 112,25             | 6,377                  | 9,51                                 | 0,93               |

| PEEC               | 115,56             | 6,258                  | 12,74                                | 0,95               |

Por último, la flexibilidad de la sonda permite caracterizar las pistas en una PCB sin necesidad de diseñar un test fixture específico para la medida. El procedimiento con sonda flexible puede ser aplicado en la caracterización de la impedancia en busbar laminados en PCB.

## 2.5.5 Limitaciones de medida grandes planos de Cu

Cuando la sonda flexible es utilizada para medir la impedancia de grandes áreas de cobre, como en los planos de alimentación en una PCB, la capacidad parásita entre los planos de cobre del apantallamiento de la sonda y las áreas de cobre aumenta. Esta

capacidad parásita no es posible compensarla y modifica la impedancia de medida, dando lugar a un error en la medida.

Fig. 2.16. Ejemplo de medida de la sonda flexible sobre un plano de alimentación con gran área.

En la Fig. 2.16 se muestra la sonda flexible sobre un plano de alimentación de una etapa semipuente sin condensador de bus. El plano de alimentación tiene 100 mm de longitud y 50 mm de anchura. El apantallamiento tiene 55 mm de largo y 15 mm de alto. En la Fig. 2.17 y Fig. 2.18 se muestra la impedancia y la fase respectivamente, medidas desde los terminales VDC+ y VDC- (Fig. 2.16) con la sonda flexible, y con el conector SMA.

Fig. 2.17. Impedancia medida con conector SMA y sonda flexible(probe) para un plano de cobre de gran tamaño.

Fig. 2.18. Fase medida con conector SMA y sonda flexible(probe) para un plano de cobre de gran tamaño.

En la Fig. 2.17 e aprecia el error en la medida de la impedancia, principalmente en el pico de la antiresonancia, debido a la atenuación no compensada. La frecuencia de antiresonancia medida con el conector SMA es 70.2 MHz y con la sonda flexible es 80.1 MHz como se puede ver en la Fig. 2.18. El error en la medida de la frecuencia de antiresonancia es del 9.98%. A partir de 150 MHz el error es inasumible y marca el límite de medida para la sonda utilizada.

# Capítulo 3.

# Descripción y medida eléctrica de un PCB busbar con circuitos de parámetros distribuidos.

Este capítulo se presenta la descripción eléctrica en la frecuencia de un busbar laminado en PCB así como los métodos de medida utilizados.

## 3.1 Comportamiento eléctrico del bus DC

En un convertidor con electrónica de potencia, con topología de semipuente o puente completo, para distribuir la tensión DC hacia el condensador de bus y hacia los dispositivos de electrónica de potencia de cada rama se utiliza una estructura formada por varios conductores conocida como busbar. Esta estructura originalmente está formada por barras de cobre que le dan su nombre. Sin embargo, dependiendo de la potencia nominal del convertidor y de la frecuencia de trabajo, también hay busbar formados por cables, y por láminas de cobre superpuestas con un dieléctrico entre ellas. En inversores de potencia con SiC MOSFET, la frecuencia de conmutación puede alcanzar decenas de kHz con altas di/dt y dv/dt durante la conmutación. Para evitar sobretensiones en los dispositivos y ruido electromagnético, es un objetivo de diseño reducir la inductancia entre el condensador de bus y los transistores. Por ello es habitual utilizar como busbar una estructura laminada. Un busbar laminado presenta una menor inductancia que las barras de cobre ya que la distancia entre planos conductores es la mínima para garantizar las condiciones de aislamiento eléctrico. Además, entre los planos conductores de la estructura laminada aparece un condensador parásito. Este condensador ayuda a filtrar las interferencias electromagnéticas conducidas entre los polos positivo y negativo de la tensión DC.

Fig. 3.1. Estructura de un busbar laminado de dos capas.

Este trabajo se centra en los busbar laminados [59] en particular en un busbar de dos capas (two-layer laminated busbar) constituido por un par de planos rectangulares conductores en paralelo separados por un dieléctrico. El empleo del busbar laminado permite reducir el valor de la inductancia respecto a una conexión con cables. A su vez, el ajuste de las dimensiones del busbar laminado (Fig. 3.1), permite ajustar el valor de la inductancia [60] según la expresión

$$L = \frac{\mu_0 \mu_r l}{\pi} \left( \frac{1}{4} + \frac{4t}{t+w} - \frac{2t}{\sqrt{4(d+t)^2 + kw^2}} \right)$$

(3.1)

donde  $\mu_0$  es la permeabilidad magnética del vacio,  $\mu_r$  es la permeabilidad relativa del medio y k es un coeficiente de corrección. Las dimensiones físicas del plano conductor t, w y l son el espesor, la anchura y la longitud; d es la distancia entre ambos planos.

En un busbar basado en PCB (PCB based busbar), el aislamiento dieléctrico típico es un sustrato de tipo FR-4. Para una onda de frecuencia f, la longitud de onda en la PCB  $\lambda_{PCB}$  viene dada por

$$\lambda_{PCB} = \frac{c}{f \cdot \sqrt{\varepsilon_{r,FR4}}} \tag{3.2}$$

donde c es la velocidad de propagación de una onda electromagnética en el vacío  $3\cdot 10^8$  m/s y  $\varepsilon_{r,FR4}$  es la permitividad relativa del sustrato FR-4. La permitividad relativa  $\varepsilon_{r,FR4}$

es mayor que la unidad (valores típicos entre 2 y 5). Por tanto,  $\lambda_{PCB}$  es menor que la longitud de onda en el vacío  $\lambda_0$ .

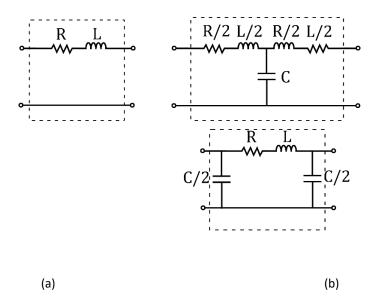

Un modelo de busbar sencillo y muy utilizado, incluso en análisis por elementos finitos(FEA), asemeja su comportamiento al de una inductancia L en serie con una resistencia R [61] como se muestra en la Fig. 3.2a. Un circuito equivalente más completo incluye la capacidad parásita C y las pérdidas en el dieléctrico G con parámetros concentrados se muestra en la Fig. 3.2b. Se puede representar o bien por una red de impedancias en T o en  $\Pi$ , ambas equivalentes entre sí según el Teorema de Rosen. En ambos modelos es frecuente despreciar los parámetros concentrados R y G, por su bajo valor a las frecuencias de interés, frente al resto de elementos en un convertidor con electrónica de potencia [62]. Sin embargo, conforme las frecuencias involucradas aumentan, los efectos capacitivos van ganando importancia.

Fig. 3.2. Circuito equivalente de un busbar. (a) circuito con impedancia serie, (b) circuito equivalente en T y en  $\pi$ .

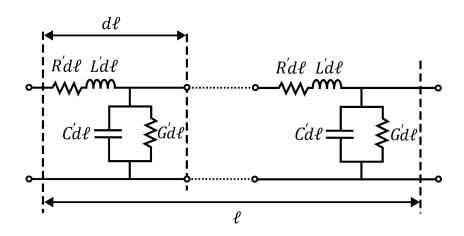

Para longitudes de línea comparables a la longitud de onda  $\lambda_{PCB}$ , el tiempo de transmisión deja de ser despreciable frente al periodo de la señal y el bus basado en PCB se comporta como una línea de transmisión, es decir como un circuito de parámetros distribuidos como se muestra en la Fig. 3.3. Donde L' es la inductancia por unidad de longitud (PUL), R' es la resistencia PUL, C' la capacidad PUL y G' la conductancia PUL,  $\ell$

la longitud de la línea de transmisión y  $d\ell$  una longitud infinitesimal. En base a estos parámetros, se expresa la impedancia característica de la línea en ohmios  $Z_0$  como

$$Z_0(\omega) = \sqrt{\frac{R' + j\omega L'}{G' + j\omega C'}}$$

(3.3)

y su constante de propagación compleja  $\gamma(j\omega)$  como

$$\gamma(\omega) = \sqrt{(R' + j\omega L') \cdot (G' + j\omega C')}$$

(3.4)

donde  $\omega$  es la frecuencia angular.

Fig. 3.3. Circuito equivalente de una línea de transmisión larga.

La elección entre el modelado del busbar mediante los circuitos equivalentes de parámetros concentrados (Fig. 3.2) o de parámetros distribuidos (Fig. 3.3) depende del error que se puede asumir. La aplicación principal de este trabajo es la caracterización de la impedancia en función de la frecuencia basado en un barrido de señales sinusoidales de tensión/corriente, siendo la frecuencia máxima de medida dependiente de las necesidades del estudio de la impedancia. Así, en convertidores de potencia con dispositivos de banda prohibida ancha (WBG), como es el carburo de silicio (SiC), se producen oscilaciones de alta frecuencia (hasta 100 MHz) durante los eventos de conmutación [63] y el espectro del ruido electromagnético radiado de campo cercano se extiende hasta los 500 MHz según [64] y radiado de campo lejano hasta 300 MHz

según [65] . Asimismo, en el rango de potencia de decenas de kW, debido a las dimensiones del busbar, la distancia entre los elementos conectados al busbar (condensador de bus y transistores) pueden alcanzar varios cm e incluso dm. Estas dimensiones son debidas principalmente a las dimensiones físicas de los condensadores para alta potencia y a los voluminosos sistemas de refrigeración necesarios para la operación segura de la electrónica de potencia.

La longitud eléctrica es adimensional y se puede define como la ratio entre la longitud física de la línea l y la longitud de onda  $\lambda$  de la frecuencia de la señal sinusoidal que la atraviesa.

$$\theta(f) = \frac{l}{\lambda(f)} \tag{3.5}$$

En la literatura es frecuente el uso de una regla general (rough rule of thumb) donde una línea de transmisión se modela con parámetros distribuidos, y es considerada eléctricamente larga, cuando la longitud eléctrica  $\theta \geq 1/20$  [66][67]. Por debajo de ese límite, la línea se considera eléctricamente corta y puede ser modelada con un circuito de parámetros concentrados.

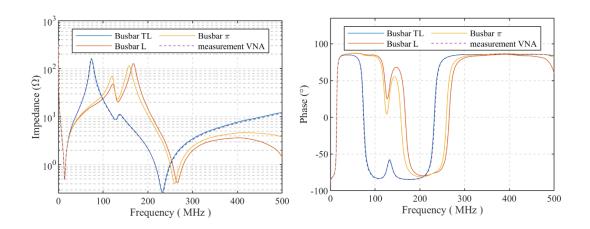

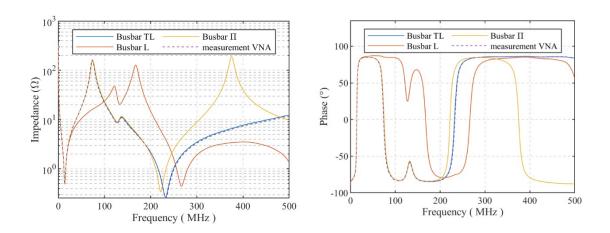

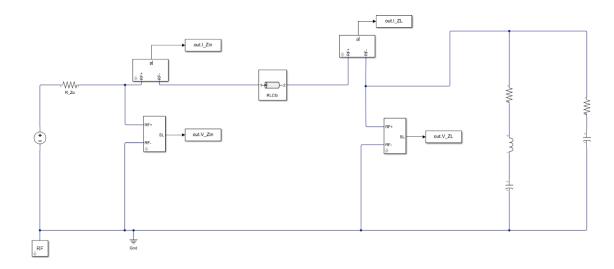

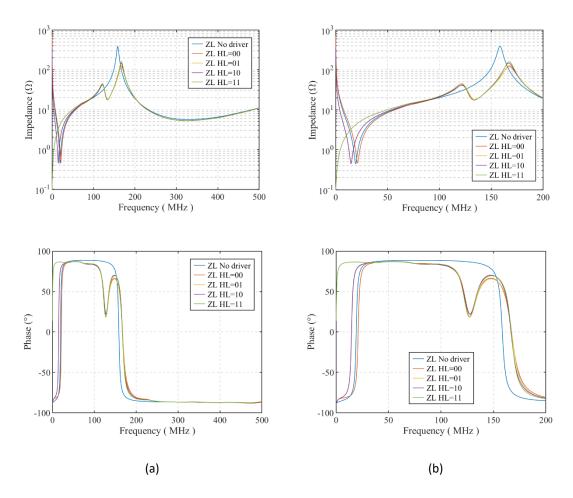

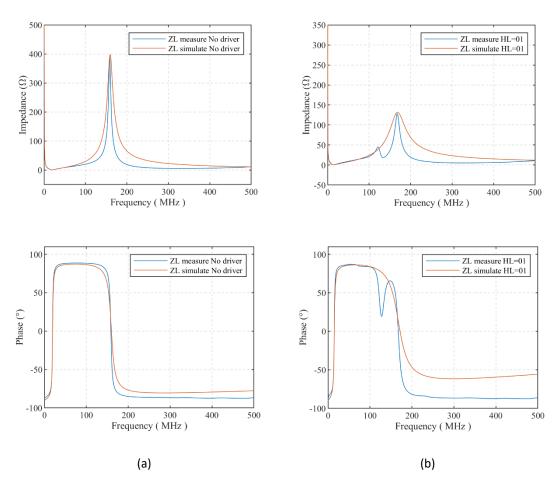

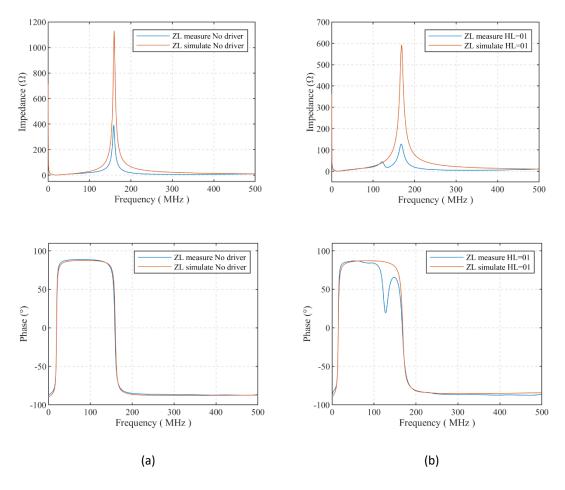

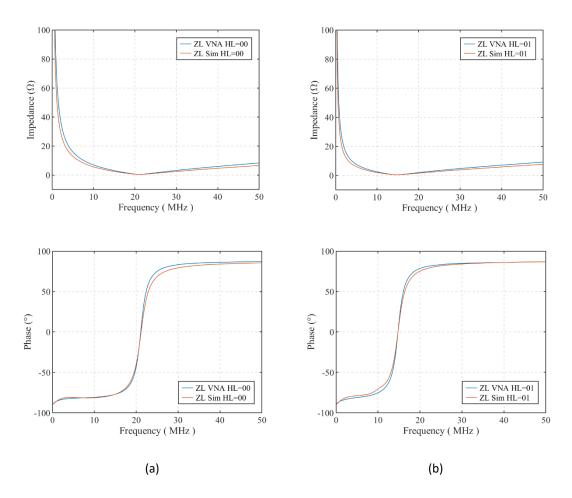

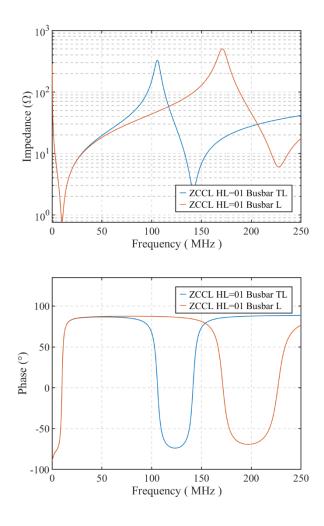

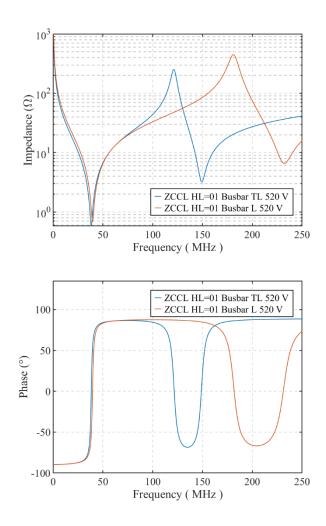

En un semipuente, el busbar está conectado en un extremo con los SiC MOSFET. La impedancia de los SiC MOSFET y de las conexiones entre el busbar y los SiC MOSFET presentan una impedancia variable. Cada cambio de geometría, como por ejemplo la impedancia de los SiC MOSFET, produce una desadaptación de impedancia variable en el rango de la frecuencia de interés. En este sentido, las 0 y Fig. 3.5 muestran la impedancia y la fase medida desde un extremo de un busbar (dos planos paralelos de 100 mm de longitud y 50 mm de ancho) terminado en un semipuente. En el caso de la 0, los resultados se han obtenido sin considerar la dependencia frecuencial de los parámetros, estos se han ajustado a 10 MHz, como es común en la bibliografía. En cambio, en la Fig. 3.5 si se ha tenido en cuenta esa dependencia frecuencial, realizando el ajuste a cada frecuencia (1601 frecuencias). En ambos casos, uno de los SiC MOSFET está en estado conducción y el otro SiC MOSFET en estado de no conducción. La impedancia medida se compara con los resultados obtenidos a partir de los circuitos

equivalentes de parámetros concentrados de la Fig. 3.2a inductancia L en serie (Busbar L) y de la Fig. 3.2b circuito en  $\pi$  que incluye efectos capacitivos (Busbar  $\pi$ ). También se compara con el modelo de línea de transmisión (Busbar TL). Para realizar la comparación se han simulado las impedancias en MATLAB-Simulink®, utilizando la libreria RF Blockset<sup>TM</sup> [68].

Fig. 3.4. Comparación de la medida de la impedancia y la fase de un busbar terminado en un semipuente con diferentes modelos eléctricos del busbar sin considerar la dependencia frecuencial de sus parámetros.

Fig. 3.5. Comparación de la medida de la impedancia y la fase de un busbar terminado en un semipuente con diferentes modelos eléctricos del busbar ajustando la dependencia de los parámetros.

En el caso de no considerar la dependencia frecuencial de los parámetros, 0, los resultados obtenidos como el modelo de impedancia serie (Busbar L) así como el

equivalente en  $\pi$  (Busbar  $\pi$ ) se comportan correctamente hasta la frecuencia de 20 MHz.

En los resultados obtenidos, se puede observar que el modelo de impedancia serie (Busbar L) de nuevo solo es válido por debajo de 20 MHz. En cambio, el circuito equivalente formado por un equivalente en  $\pi$  (Busbar  $\pi$ ) muestra un error despreciable hasta 180 MHz. Por último, el modelo de parámetros distribuidos y de la línea de transmisión (Busbar TL) describe adecuadamente el comportamiento de la impedancia en todo el rango frecuencia.

Se considera como criterio para la medida de la impedancia, que el cambio de un modelo de parámetros concentrados a parámetros distribuidos ocurra con  $\theta=1/100$ . Con esta aproximación el máximo error de magnitud de una señal sinusoidal entre cada extremo de la línea es del 6.27 % y el error en la fase es de 3.6°.

Tabla 3.1. Frecuencias límite del modelo de busbar con parámetros concentrados.

| Length (m) | $f_{\lambda/50}({ m MHz})$ | $f_{\lambda/100}$ (MHz) |

|------------|----------------------------|-------------------------|

| 0,05       | 54,73                      | 27,37                   |

| 0,1        | 27,37                      | 13,68                   |

| 0,15       | 18,24                      | 9,12                    |

| 0,20       | 13,68                      | 6,84                    |

En la Tabla 3.1 se muestra las frecuencias  $f_{\lambda/50}$  y  $f_{\lambda/100}$  calculadas para un busbar laminado con sustrato FR-4, con longitudes entre 5 cm y 20 cm. La permitividad relativa es considerada constante ( $\varepsilon_{r,FR4}$ = 4.8). La frecuencia  $f_{\lambda/50}$  corresponde a la frecuencia límite cuando  $\theta=1/50$  y la frecuencia  $f_{\lambda/100}$  cuando  $\theta=1/100$ . Por debajo del valor de esas frecuencias, el busbar se puede modelar como un circuito de parámetros concentrados. Además, como se puede ver, cuanto mayor es la longitud del busbar laminado, peor es la aproximación del busbar con parámetros concentrados para

frecuencias altas. Así que, para modelar correctamente la impedancia de un semipuente (alimentado con un busbar) hasta las frecuencias del ruido electromagnético derivado de la conmutación, es necesario considerar el busbar como una línea de transmisión con parámetros distribuidos

## 3.2 Impedancia del busbar como línea de transmisión

El busbar laminado (Fig. 3.1) puede ser caracterizado con precisión empleando una línea de transmisión cuyos parámetros distribuidos R', L', C' y G' son dependientes de la frecuencia. El efecto skin y el efecto de proximidad en los conductores debido al campo magnético variable, y los mecanismos de polarización en el dieléctrico cuando estos están sujetos a un campo eléctrico externo variable son las causas de la dependencia con la frecuencia.

La densidad de corriente por las capas conductoras depende de la frecuencia, de modo que a altas frecuencias el efecto skin y el de proximidad se hacen predominantes. Conforme aumenta la frecuencia, se produce un desplazamiento de la corriente hacia el exterior del conductor lo que aumenta su resistencia R' por unidad de longitud. El efecto skin y de proximidad comienzan a predominar en el conductor para un valor de frecuencia  $f_{sk}$  a la cual la resistencia  $R'_{ac}$  asociada a los efectos skin y de proximidad es igual a la resistencia en continua  $R'_{dc}$ ,  $f_{sk}$  viene dada por [69]

$$f_{sk} = \frac{1}{\sigma_{Cu} \cdot \mu_0 \cdot t^2} \tag{3.6}$$

donde  $\sigma_{Cu}$ =58·10 <sup>6</sup> S/m es la conductividad del cobre curado utilizado en una PCB. El parámetro R' depende del valor de  $f_{sk}$  y de la profundidad de penetración del efecto skin  $\delta=(2/\omega\cdot\sigma_{Cu}\cdot\mu_0)^{1/2}$  en el conductor como muestra la siguiente relación

$$R'(\omega) = \begin{cases} R'_{dc} & f < f_{sk} \\ R'_{ac} = R'_{dc} \cdot K_R & f \ge f_{sk} \end{cases}$$

(3.7)

donde la resistencia  $R_{dc}^{\prime}$  de los dos planos del bus DC es

$$R'_{dc} = \frac{2}{\sigma_{Cu} \cdot t \cdot w} \tag{3.8}$$

y  $K_R$  es el factor de la resistencia AC (the AC resistance factor) de cada plano conductor que puede ser expresada como [69]

$$K_{R} = \left(\frac{t}{\delta}\right) \cdot \frac{\sinh\left(\frac{2t}{\delta}\right) + \sin\left(\frac{2t}{\delta}\right)}{\cosh\left(\frac{2t}{\delta}\right) - \cos\left(\frac{2t}{\delta}\right)}$$

(3.9)

La dependencia frecuencial del parámetro L' se puede expresar en función de una inductancia externa  $L'_e$  y una inductancia interna  $L'_i$  como [70]

$$L'(\omega) = L'_e + L'_i(\omega) \tag{3.10}$$

$L_e'$  está asociada al bucle de corriente que se forma entre los dos planos conductores cuando la corriente es superficial y fluye por el exterior del conductor. En este caso, la dirección de las corrientes es opuesta en cada uno de los planos conductores. Como consecuencia del efecto proximidad, entre dos corrientes opuestas, la densidad de corriente se concentra en las caras de los planos conductores que hacen contacto con el sustrato dieléctrico FR-4. Así, la inductancia externa queda asociada a la inductancia ideal de los dos planos conductores de espesor despreciable t =0 que está dada por

$$L_e' = \mu \frac{d}{w} \tag{3.11}$$

La corriente que circula por el interior del conductor da lugar a  $L_i'$ . Esta inductancia depende de la distribución de la corriente en el interior del conductor. Cuando la frecuencia aumenta, el efecto skin y el efecto de proximidad se hacen predominantes y la corriente que circula por el interior del conductor disminuye. Así, de acuerdo con la

inductancia de cada plano conductor considerando estos efectos [71],  $L_i^\prime$  se puede modelar como

$$L_i'(\omega) = \frac{R_{dc}'}{\omega} \cdot K_X \tag{3.12}$$

donde  $K_X$  es la reactancia normalizada (the normalized reactance) de cada plano conductor y puede ser expresada como

$$K_X = \left(\frac{t}{\delta}\right) \cdot \frac{\sinh\left(\frac{2t}{\delta}\right) - \sin\left(\frac{2t}{\delta}\right)}{\cosh\left(\frac{2t}{\delta}\right) - \cos\left(\frac{2t}{\delta}\right)}$$

(3.13)

Hay que destacar que conforme aumenta la frecuencia,  $L_i'$  disminuye y, para valores de frecuencia suficientemente altos, L' se puede aproximar por  $L_e'$ .

El sustrato dieléctrico FR-4 (Flame Retardant 4), consistente en fibras de vidrio incrustadas en resina epoxi, es el más utilizado en PCBs. Las propiedades del FR-4 dependen de la frecuencia. Los fabricantes del sustrato no proporcionan información detallada del material en un rango amplio de frecuencias y sus propiedades pueden variar entre fabricantes, tipos de FR-4 y espesor. En este trabajo se utiliza un sustrato FR-4 estándar de uso general, con temperatura de transición vítrea (Tg) de 155 ºC. La permitividad compleja se expresa como

$$\varepsilon_{r,FR4} = \varepsilon' - j\varepsilon'' = \varepsilon'(1 - j\tan\delta)$$

(3.14)

De acuerdo con [72] en un FR-4 estándar la parte real  $\varepsilon'$  varía entre 5.5 y 4.2 desde 10 Hz hasta 10 GHz. Para frecuencias por debajo de 1 GHz,  $\varepsilon'$  decrece ligeramente con la frecuencia. La tangente de perdidas  $\tan\delta$  se puede considerar constante por debajo de 1 GHz. Por tanto, en el enfoque de líneas de transmisión propuesto para un busbar laminado en PCB se considera adecuado considerar que  $\varepsilon'$  es constante a frecuencias menores de 1 MHz. El efecto capacitivo es menos predominante que el inductivo a esas frecuencias y el error cometido con esta aproximación es despreciable. Se modela la parte real  $\varepsilon'$  como

$$\varepsilon'(\omega) = \begin{cases} \varepsilon'_{LF} & f \le f_{LF} \\ \varepsilon'_{LF} - \frac{\omega(\varepsilon'_{LF} - \varepsilon'_{HF})}{\omega_{HF} - \omega_{LF}} & f > f_{LF} \end{cases}$$

(3.15)

donde  $\varepsilon'_{LF}$  es la permitividad a la frecuencia más baja de la hoja de características (1 MHz)  $\omega_{LF}$  y  $\varepsilon'_{HF}$  es la permitividad a la frecuencia más alta  $\omega_{HF}$ . Es usual encontrar dos valores de  $\varepsilon'$  correspondientes a dos frecuencias conforme a los datos del fabricante.

La capacidad C' en una estructura formada por dos planos paralelos, despreciando el efecto punta (fringing effect) ( $w \gg d$ ), viene dado por

$$C' = \varepsilon' \cdot \varepsilon_0 \cdot \frac{w}{d} \tag{3.16}$$

Finalmente, la conductancia  $G^{\prime}$  entre ambas placas a través del dieléctrico se puede aproximar por

$$G' = \omega \cdot C' \cdot \tan \delta \tag{3.17}$$

donde  $\tan \delta$  es la tangente de pérdidas (loss tangent).

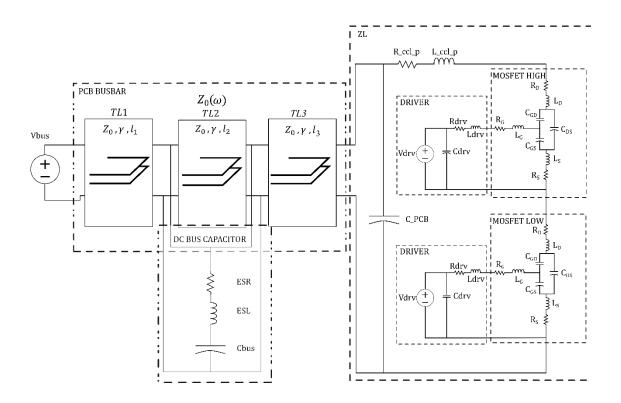

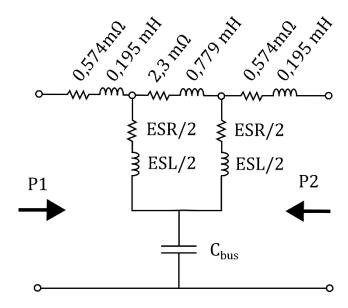

Fig. 3.6. Circuito equivalente del busbar y del semipuente.

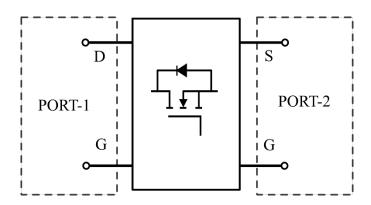

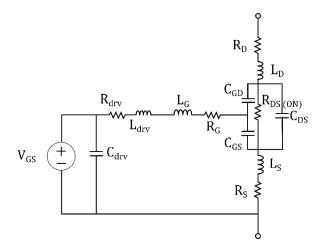

## 3.3 Circuito equivalente de un semipuente con busbar

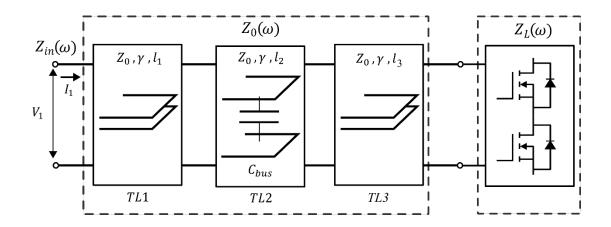

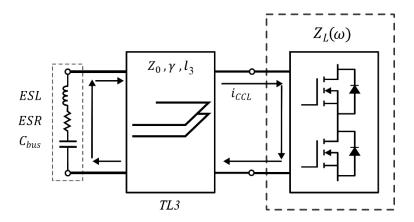

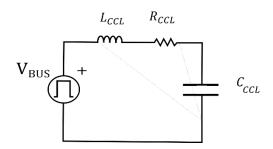

En la Fig. 3.6 se muestra el circuito de un semipuente con SiC MOSFET donde están representadas las impedancias parásitas en el bucle de corriente de conmutación CCL (del inglés current commutation loop). La tensión de alimentación de corriente continua del semipuente es  $V_{bus}$ . El PCB busbar está modelado como una línea de transmisión dividida en tres tramos (TL1, TL2, TL3) de longitudes  $\ell_1$ ,  $\ell_2$  y  $\ell_3$ . El condensador de bus  $C_{bus}$  tiene cuatro pines de conexión, dos para cada polaridad.

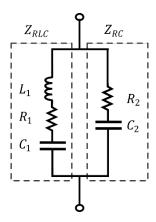

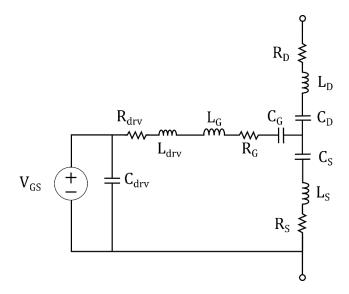

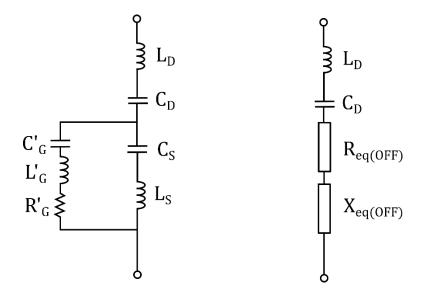

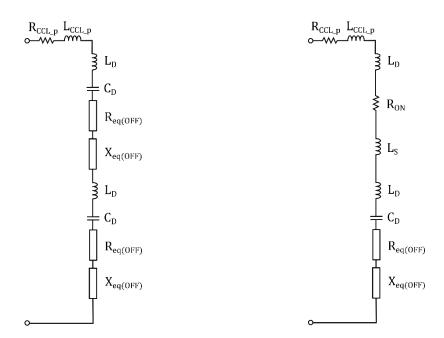

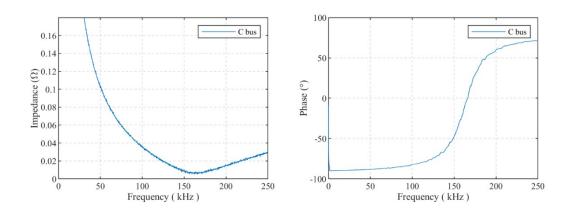

# Descripción de las impedancias que constituyen el circuito

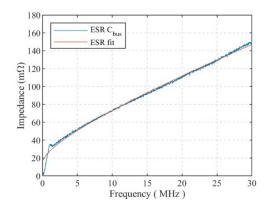

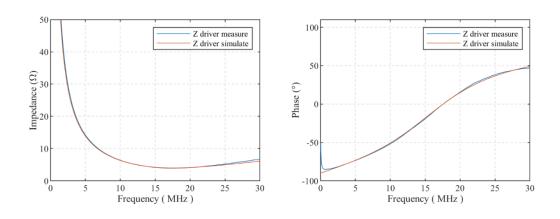

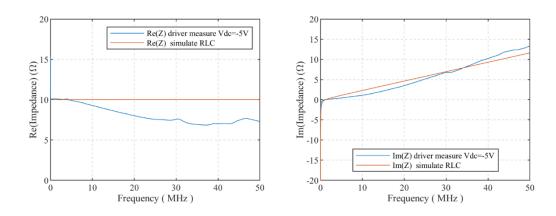

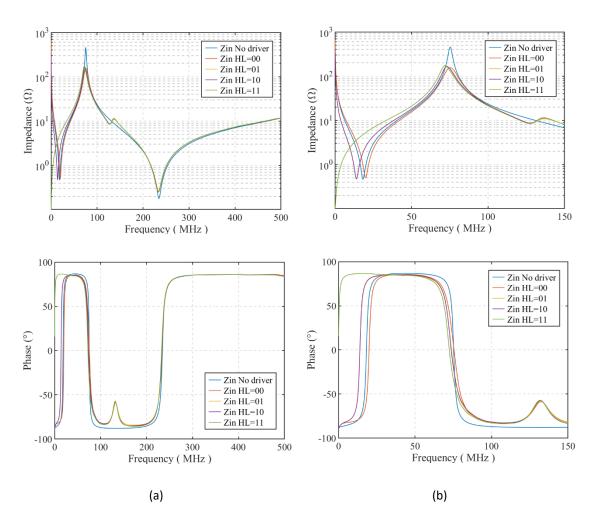

El primer tramo del busbar con longitud  $\ell_1$  conecta la fuente DC  $V_{bus}$  con el condensador de bus  $C_{bus}$ . El segundo tramo del busbar con longitud  $\ell_2$  corresponde al tramo del busbar entre los pares de pines del condensador de bus. El tercer tramo del busbar con longitud  $\ell_3$  conecta  $C_{bus}$  con los SiC MOSFET. El condensador de bus tiene una resistencia serie equivalente  $R_{ESR}$  y una inductancia serie equivalente  $L_{ESL}$ .Las pistas impresas en la PCB que interconectan el busbar y los SiC MOSFET forman la impedancia