UNIVERSIDAD DE ZARAGOZA

Centro Politécnico Superior

PROYECTO FIN DE CARRERA

Ingeniería de Telecomunicaciones

# **DISEÑO E IMPLEMENTACIÓN DE AMPLIFICADOR DE TRANSIMPEDANCIA Y ECUALIZADOR PARA COMUNICACIONES DE BANDA ANCHA CON FIBRA ÓPTICA DE PLÁSTICO**

(MEMORIA 1/2)

AUTOR: IGNACIO LOPE MORATILLA

DIRECTOR: JAVIER MATEO GASCÓN

Zaragoza Septiembre 2010

Grupo de Diseño

Electrónico

Departamento Ingeniería

Electrónica y de Comunicaciones

**GTF**

Photonic Technologies

Group

Grupo de Tecnologías

Fotónicas

# Agradecimientos

En primer lugar, debo agradecer la oportunidad que me han dado tanto el director de este PFC, D. Javier Mateo Gascón, como D. Santiago Celma Pueyo de poder realizar este trabajo y formar parte de sus proyectos de investigación. Su apoyo y confianza en mi trabajo han sido fundamentales, no solamente en el desarrollo de este proyecto sino también en mi formación como investigador.

Imprescindible la aportación del Grupo de Diseño Electrónico (GDE) y del Grupo de Tecnologías Fotónicas (GTF) por el material y ayuda técnica proporcionada a lo largo de todo el proyecto. No menos transcendente ha sido el apoyo intelectual y técnico proporcionado por el Servicio de Instrumentación de la Universidad de Zaragoza. Mi más sincero agradecimiento a todos ellos.

Destacar el apoyo recibido de D. Óscar Lasarte, por su disponibilidad y respaldo técnico a lo largo de mi estancia en el GDE. De D. Pedro Martínez, por su asesoramiento y colaboración, enriqueciendo en todo momento el trabajo realizado. De D. José Barquillas, por esos momentos en los que ha conseguido que mi estancia sea más agradable.

Mi reconocimiento al MEC y al I3A, instituciones que me han permitido la realización de una Beca de Colaboración y una Beca Multidisciplinar de Iniciación a la Investigación respectivamente. También agradecer la financiación y apoyo proporcionado por los diferentes proyectos de investigación en los que he colaborado: MICINN (TEC2008-05455/TEC, TEC2009-14718-C03-02) y DGA (PI127/08). Esto me ha permitido aprender la metodología y los pasos a seguir en un trabajo de investigación.

Gracias a la desinteresada colaboración de D. Julen Urdangarín y D. José María García del Pozo he disfrutado y aprendido de una de las cosas que más valoro después de este proyecto: trabajar en equipo. Y si esto significa, como es el caso, el surgimiento de una sólida amistad, pues mejor. Julen, muchas gracias por ayudarme a cumplir este objetivo como si fuera tuyo. Chema, agradecerte de la forma más sincera, tu esfuerzo, dedicación, orientación, paciencia, motivación, persistencia... Ha sido un privilegio contar con tus consejos y conocimientos.

# Resumen

## Diseño e implementación de amplificador de transimpedancia y ecualizador para comunicaciones de banda ancha con fibra óptica de plástico.

En este Proyecto Fin de Carrera (PFC), se ha realizado un sistema óptico para comunicaciones de banda ancha con fibra óptica de plástico (POF). Todo ello utilizando componentes comerciales. El objetivo final ha sido corregir las limitaciones frecuenciales de la POF mediante técnicas de ecualización analógica, consiguiendo aumentar el ancho de banda (BW) del sistema y, por lo tanto, disminuyendo la tasa de error (BER). Para ello se ha realizado el diseño y la implementación de un amplificador de transimpedancia (TIA) y de un ecualizador (EQ), siendo esto el núcleo central del PFC.

El TIA y el ecualizador se han diseñado buscando un compromiso entre ancho de banda, ganancia, ruido y consumo. Otra condición de diseño ha sido el bajo coste, que es intrínseco a los sistemas POF. En la etapa de diseño analítico, se realiza un estudio de las diferentes configuraciones y componentes, utilizando simulación SPICE para la optimización del diseño.

Una vez finalizado el proceso anterior, se procede al diseño e implementación de las diferentes Placas de Circuito Impreso (PCB), aplicando las reglas básicas de EMI/EMC para su correcto funcionamiento.

Finalmente, se ha utilizado la instrumentación específica para la caracterización experimental del sistema óptico, poniendo en relieve la mejora que proporciona el ecualizador.

- **Palabras Clave:** Ecualizador, Fibra Óptica de Plástico (POF), Amplificador de Transimpedancia (TIA), Comunicaciones Serie, Diseño PCBs.

# Índice General

|                                                                              |           |

|------------------------------------------------------------------------------|-----------|

| Índice de Figuras y Tablas .....                                             | I         |

| Símbolos .....                                                               | III       |

| Acrónimos.....                                                               | V         |

| <b><u>CAPÍTULO 1: Introducción .....</u></b>                                 | <b>7</b>  |

| 1.1. Interés y Objetivos del Proyecto .....                                  | 8         |

| 1.2. Contexto .....                                                          | 9         |

| 1.3. Descripción del Proyecto y Metodología .....                            | 10        |

| 1.4. Fases y Programación del Trabajo.....                                   | 10        |

| 1.5. Herramientas Utilizadas .....                                           | 11        |

| 1.6. Contenidos de la Memoria .....                                          | 12        |

| <b><u>CAPÍTULO 2: Sistema de comunicación para banda ancha POF .....</u></b> | <b>13</b> |

| 2.1. Visión General.....                                                     | 14        |

| 2.2. Transmisor .....                                                        | 15        |

| 2.3. Fibra Óptica de Plástico (POF) .....                                    | 16        |

| 2.4. Fotodetector.....                                                       | 19        |

| 2.5. Preamplificador .....                                                   | 21        |

| 2.5.1. Análisis de etapas preamplificadoras.....                             | 21        |

| 2.5.2. Diseño del amplificador de transimpedancia (TIA) .....                | 25        |

| 2.6. Ecualizador.....                                                        | 28        |

| 2.6.1. Análisis de etapas ecualizadoras .....                                | 28        |

| 2.6.2. Diseño del ecualizador (EQ).....                                      | 32        |

| <b><u>CAPÍTULO 3: Caracterización experimental .....</u></b>                 | <b>35</b> |

| 3.1. Láser.....                                                              | 36        |

| 3.2. Sistema completo .....                                                  | 38        |

| 3.3. Caracterización experimental del sistema completa .....                 | 41        |

| <b><u>CAPÍTULO 4: Conclusiones .....</u></b>                                 | <b>45</b> |

| 4.1. Conclusiones Generales.....                                             | 46        |

| 4.2. Líneas Futuras.....                                                     | 47        |

| 4.3. Valoración Personal.....                                                | 48        |

| Referencias .....                                                            | 49        |

|                                                                                                                                                          |           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <b><u>ANEXO I: Técnicas de Ecualización Adaptativa .....</u></b>                                                                                         | <b>53</b> |

| I.1.    Introducción .....                                                                                                                               | 54        |

| I.2.    Clasificación .....                                                                                                                              | 54        |

| <br>                                                                                                                                                     |           |

| <b><u>ANEXO II: Descripción de la Instrumentación.....</u></b>                                                                                           | <b>57</b> |

| II.1.    DCA 86100C, Agilent.....                                                                                                                        | 58        |

| II.2.    BERT N4906A, Agilent.....                                                                                                                       | 60        |

| II.3.    ZVL 9KHz/6GHz, R&S .....                                                                                                                        | 60        |

| II.4.    Multimeter 3458A, Agilent.....                                                                                                                  | 61        |

| II.5.    FM300, Fotec m.....                                                                                                                             | 61        |

| <br>                                                                                                                                                     |           |

| <b><u>ANEXO III: Hojas de Características .....</u></b>                                                                                                  | <b>63</b> |

| III.1.    Red laser diode. DL 3149-057, Sanyo .....                                                                                                      | 64        |

| III.2.    SI-POF. ESKA Premier GH 4002 2.2 mm, Mitsubishi.....                                                                                           | 65        |

| III.3.    Fotodiodo. Si PIN S5972, Hamamatsu .....                                                                                                       | 66        |

| III.4.    Transistor. BFP640, Infineon .....                                                                                                             | 69        |

| III.5.    Array de Transistores. HFA3127, Intersil.....                                                                                                  | 73        |

| III.6.    Bias-T. ZFBT-4R2G+, Minicircuits.....                                                                                                          | 79        |

| III.7.    Balun. Model BIB-100G, Prodyn .....                                                                                                            | 81        |

| <br>                                                                                                                                                     |           |

| <b><u>ANEXO IV: Publicaciones del Autor .....</u></b>                                                                                                    | <b>83</b> |

| IV.1.    Introducción .....                                                                                                                              | 84        |

| IV.2.    “Low-Cost TIA and Equalizer For SI-POF”. 19th International Conference on Plastic Optical Fibers                                                |           |

| IV.3.    “1.8V - 3GHz CMOS Limiting Amplifier with Feedforward Frequency Compensation”. Microelectronics Reliability                                     |           |

| IV.4.    “A 0.18 $\mu$ m CMOS Integrated Transimpedance Amplifier- Equalizer for 2.5 Gb/s”. IEEE International Midwest Symposium on Circuits and Systems |           |

# Índice de Figuras y Tablas

- **Índice de Figuras**

|       |                                                                                                                                                                                                                  |    |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1.  | Instalación de POF junto al cableado eléctrico .....                                                                                                                                                             | 8  |

| 1.2.  | Espacio multidimensional en el diseño analógico [RAZ99] .....                                                                                                                                                    | 9  |

| 2.1.  | Esquemático de nuestro sistema óptico completo .....                                                                                                                                                             | 14 |

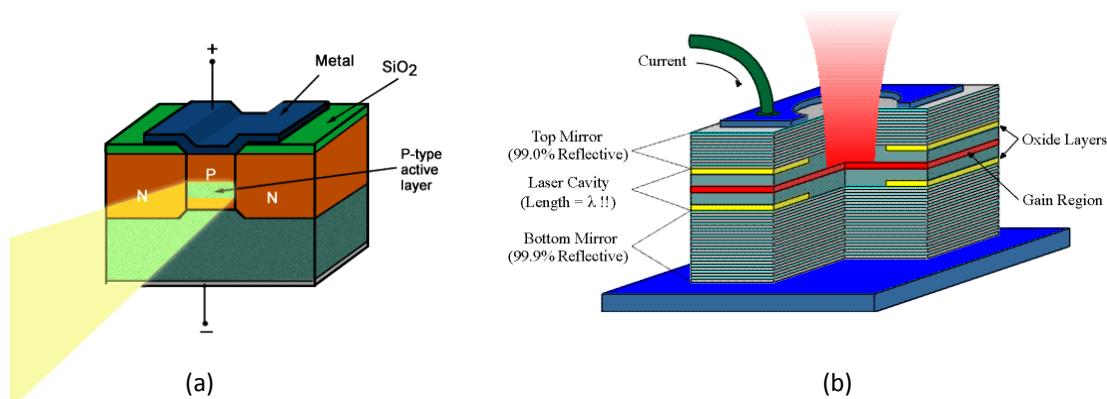

| 2.2.  | Diagramas de emisión de un (a) LD y (b) VCSEL [GIO03].....                                                                                                                                                       | 15 |

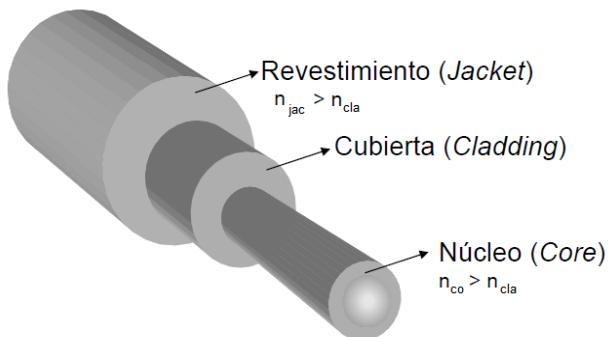

| 2.3.  | Núcleo, cubierta y revestimiento de una PMMA-POF [GAR08] .....                                                                                                                                                   | 16 |

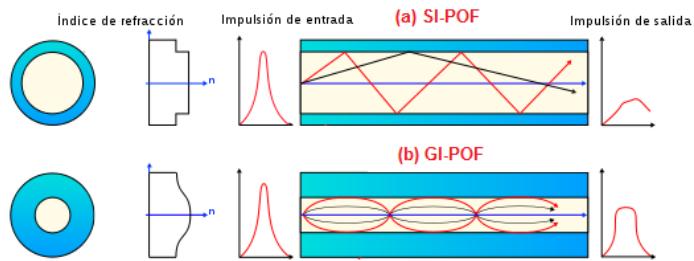

| 2.4.  | Distribución de índices de refracción, pulso de entrada, diagrama de rayos en la POF y pulso de salida. SI-POF (superior) y GI-POF (inferior) [ARA10] .....                                                      | 17 |

| 2.5.  | Efecto de la dispersión y atenuación en una transmisión por fibra óptica [GAR08].....                                                                                                                            | 17 |

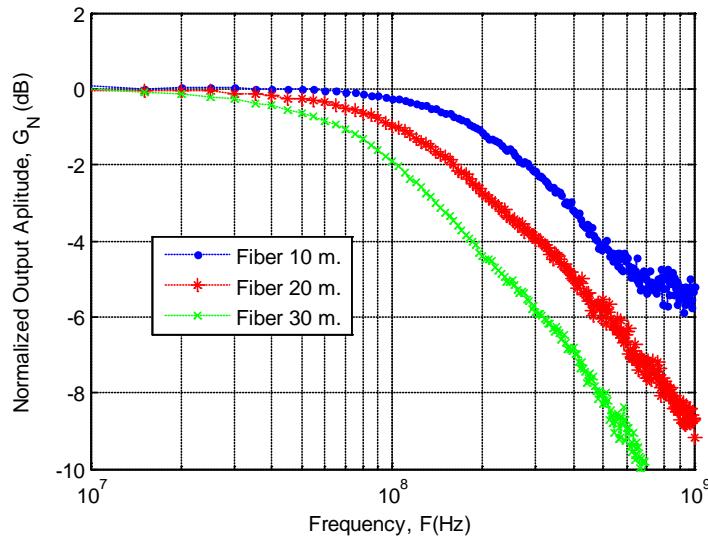

| 2.6.  | Respuesta frecuencial de la fibra para diferentes longitudes [MAT05].....                                                                                                                                        | 18 |

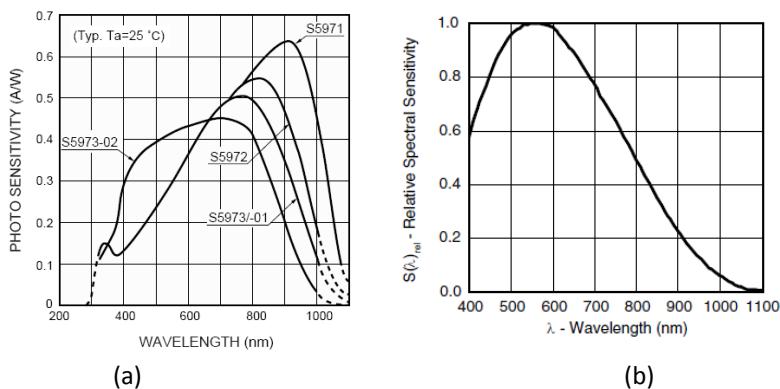

| 2.7.  | Responsividad de: (a) S597X Series, Hamamatsu (Si PIN PD), [Anexo III] y (b) T1670P, Vishay (Si PIN PD), [VIS10].....                                                                                            | 19 |

| 2.8.  | Capacidad parasite de deplexión: (a) Serie S597X, Hamamatsu (Si PIN PD) [Anexo III] y (b) T1670P, Vishay (Si PIN PD) [VIS10] .....                                                                               | 20 |

| 2.9.  | Fotodiodo: (a) Símbolo y (b) modelo de pequeña señal del PD.....                                                                                                                                                 | 20 |

| 2.10. | Preamplificador de carga resistiva pasiva: (a) circuito y (b) modelo equivalente .....                                                                                                                           | 21 |

| 2.11. | TIA: (a) circuito y (b) modelo equivalente de pequeña señal.....                                                                                                                                                 | 22 |

| 2.12. | Diagrama de Bloques de preamplificadores de modo corriente combinados con: (a) Carga resistiva pasiva y (b) TIA.....                                                                                             | 23 |

| 2.13. | Configuraciones monoetapa: (a) emisor-común y (b) cascodo .....                                                                                                                                                  | 24 |

| 2.14. | (a) Valores característicos del transistor BFP640, $V_{BE}$ (azul) y $\beta$ (verde). (b) Valores de las resistencias del TIA: $R_F$ (azul) y $R_C$ (verde). Todo ello en función de $I_C$ y con $V_C=1.7$ ..... | 25 |

| 2.15. | Modelo equivalente para pequeña señal del TIA.....                                                                                                                                                               | 26 |

| 2.16. | <i>Capability</i> normalizada del TIA en función de $I_C$ .....                                                                                                                                                  | 27 |

| 2.17. | Arquitectura del preamplificador propuesto .....                                                                                                                                                                 | 27 |

| 2.18. | Respuesta representativa del canal, ecualizador y respuesta global para el caso ideal y real .....                                                                                                               | 29 |

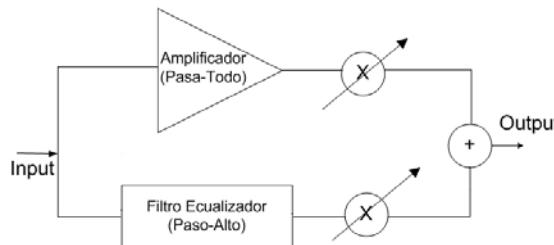

| 2.19. | Diagrama de bloques de un EQ-CT. La respuesta obtenida es un filtro paso-alta de ganancia variable .....                                                                                                         | 30 |

| 2.20. | Arquitectura del EQ propuesto: par diferencial con degeneración de fuente....                                                                                                                                    | 31 |

| 2.21. | Esquema del espejo de corriente implementado .....                                                                                                                                                               | 32 |

| 2.22. | <i>Capability</i> normalizada del EQ en función de $I_C$ .....                                                                                                                                                   | 33 |

| 2.23. | Modelo equivalente de pequeña señal del EQ.....                                                                                                                                                                  | 34 |

|       |                                                                                                                                                                                                                                                                                                                                                                                             |    |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.24. | Esquemático del EQ propuesto .....                                                                                                                                                                                                                                                                                                                                                          | 34 |

| 3.1.  | LD: (a) Esquemático de la PCB y (b) implementación.....                                                                                                                                                                                                                                                                                                                                     | 36 |

| 3.2.  | Setup para la caracterización del láser .....                                                                                                                                                                                                                                                                                                                                               | 37 |

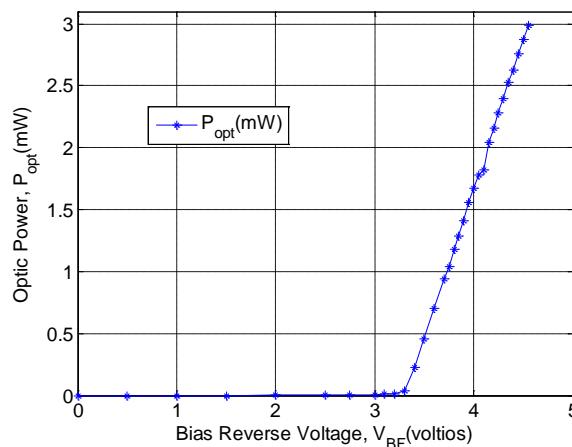

| 3.3.  | Recta de carga experimental del <i>red laser diode</i> DL 3149-057 .....                                                                                                                                                                                                                                                                                                                    | 37 |

| 3.4.  | Arquitectura del <i>front-end</i> complete .....                                                                                                                                                                                                                                                                                                                                            | 38 |

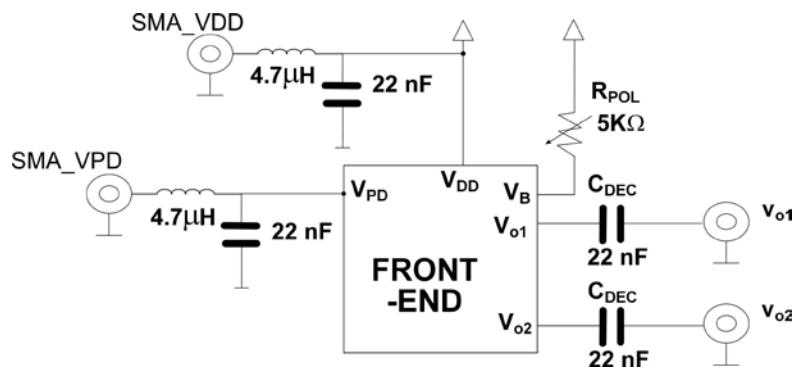

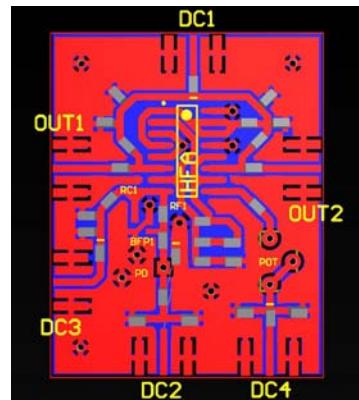

| 3.5.  | Esquemático de la PCB del <i>front-end</i> .....                                                                                                                                                                                                                                                                                                                                            | 40 |

| 3.6.  | Trazado pistas cara <i>top</i> del <i>front-end</i> .....                                                                                                                                                                                                                                                                                                                                   | 40 |

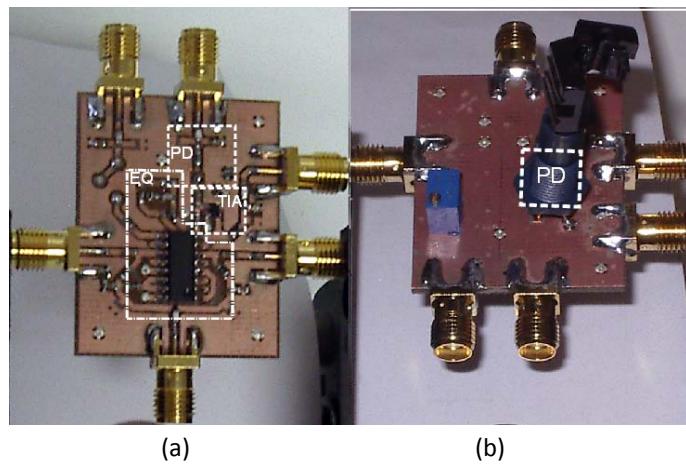

| 3.7.  | PCB <i>front-end</i> implementada: (a) <i>top</i> y (b) <i>bottom</i> .....                                                                                                                                                                                                                                                                                                                 | 40 |

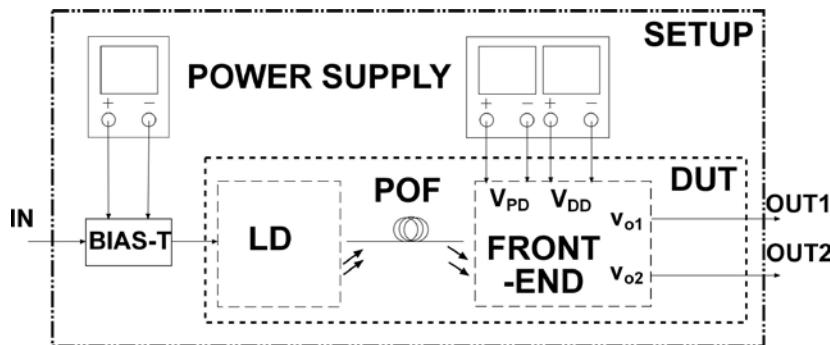

| 3.8.  | Setup de medida del circuito bajo test (DUT).....                                                                                                                                                                                                                                                                                                                                           | 41 |

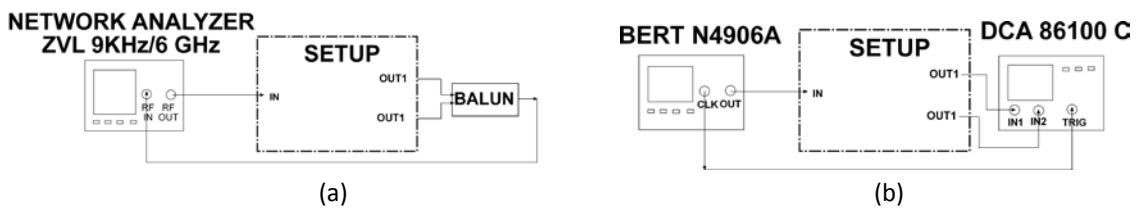

| 3.9.  | Configuraciones caracterización del sistema completo: (a) Respuesta<br>frecuencial y (b) Transmisión de datos.....                                                                                                                                                                                                                                                                          | 41 |

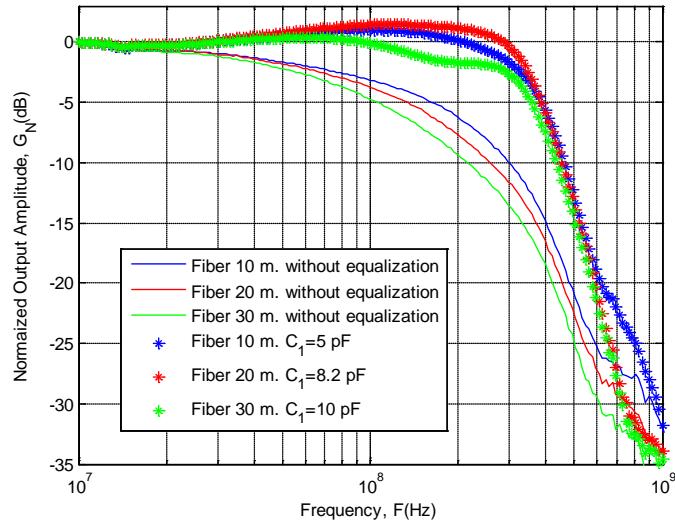

| 3.10. | Respuesta frecuencial del sistema POF .....                                                                                                                                                                                                                                                                                                                                                 | 43 |

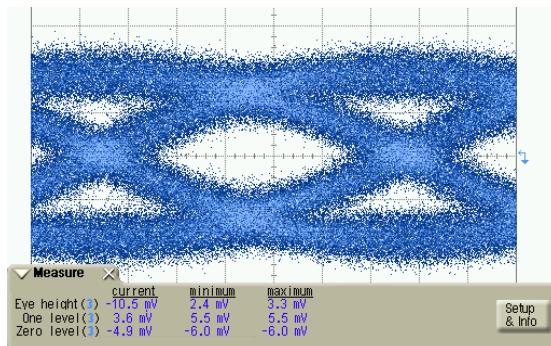

| 3.11. | Diagrama de ojo para $2^{31}-1$ NRZ PRBS. $R_1=220\ \Omega$ , $R_2 = 5\Omega$ , $C_2 = 10\ \text{pF}$ .<br>Longitud de fibra 30 m y tasa 800 Mb/s.....                                                                                                                                                                                                                                      | 43 |

| 3.12. | Diagrama de ojo para $2^{31}-1$ NRZ PRBS. $R_1=220\ \Omega$ , $R_2 = 5\Omega$ , $C_2 = 8.2\ \text{pF}$ .<br>Longitud de fibra 20 m y tasa 800 Mb/s.....                                                                                                                                                                                                                                     | 43 |

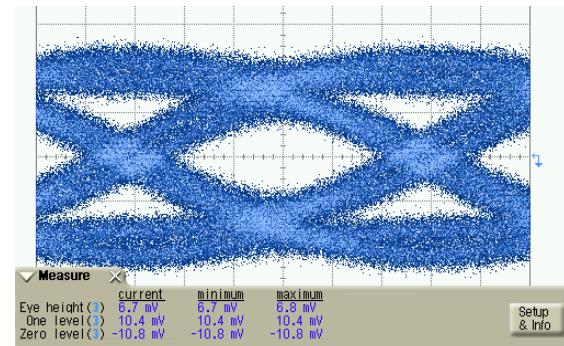

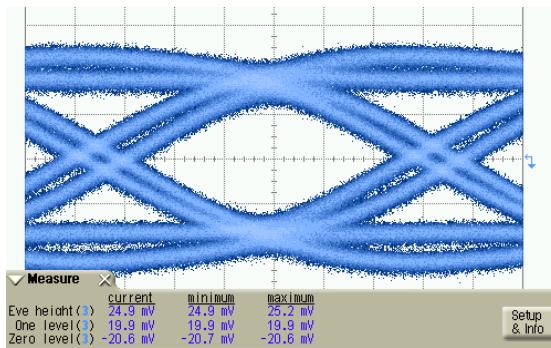

| 3.13. | Diagrama de ojo para $2^{31}-1$ NRZ PRBS. $R_1=220\ \Omega$ , $R_2 = 5\Omega$ , $C_2 = 5\ \text{pF}$ .<br>Longitud de fibra 10 m y tasa 800 Mb/s.....                                                                                                                                                                                                                                       | 43 |

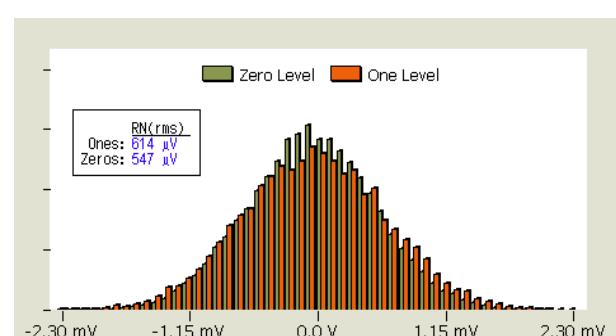

| 3.14. | Distribución del ruido en función del estado lógico “1/0” .....                                                                                                                                                                                                                                                                                                                             | 43 |

| I.1.  | Diagrama de bloques de un ecualizador adaptativo .....                                                                                                                                                                                                                                                                                                                                      | 54 |

| I.2.  | Diagrama de bloques de ecualizadores analógicos adaptativos de alta<br>velocidad: (a) Obtiene la diferencia de la componente en DC antes y<br>después de un <i>slicer</i> [BAB98](b) compara la componente en DC con la<br>potencia total recibida [SUN05] y (c) analiza la señal a 200 MHz y a 600<br>MHz para una aplicación de transmisión por cable coaxial a 3.2 Gbps<br>[MAX01] ..... | 55 |

| II.1. | Analizador de redes. DCA 86100 C, Agilent [AGI05].....                                                                                                                                                                                                                                                                                                                                      | 58 |

| II.2. | Método de muestreo y reconstrucción en un osciloscopio de tiempo<br>equivalente: (a) Diagrama de ojo y (b) Modo osciloscopio normal [AGI05] .....                                                                                                                                                                                                                                           | 59 |

| II.3. | Medidor Tasa de Error. BERT N4906A, Agilent [AGI08] .....                                                                                                                                                                                                                                                                                                                                   | 60 |

| II.4. | Analizador de Redes Vectorial. ZVL 9KHz/6GHz, R&S [R&S09] .....                                                                                                                                                                                                                                                                                                                             | 60 |

| II.5. | Multímetro de Precisión. <i>Multimeter</i> 3458A, Agilent [AGI01].....                                                                                                                                                                                                                                                                                                                      | 61 |

| II.6. | Medidor de Potencia Óptica para Fibra. FM300, Fotec m [FOT00] .....                                                                                                                                                                                                                                                                                                                         | 61 |

• **Índice de Tablas**

|      |                                                        |    |

|------|--------------------------------------------------------|----|

| 1.1. | Diagrama de Gantt que detalla el plan de trabajo ..... | 10 |

| 2.1. | Análisis de las Técnicas de Ecualización .....         | 30 |

| 4.1. | Comparativa con otros autores .....                    | 46 |

# Símbolos

|               |                                                       |

|---------------|-------------------------------------------------------|

| $\beta$       | Ganancia en Corriente                                 |

| $\phi$        | Diámetro                                              |

| $\lambda$     | Longitud de Onda                                      |

| BW            | Ancho de Banda                                        |

| $BW_n$        | Ancho de Banda del ruido blanco referido a la entrada |

| $C_{bc}$      | Capacidad Base-Colector                               |

| $C_{be}$      | Capacidad Base-Emisor                                 |

| $C_d$         | Capacidad de Unión                                    |

| $C_{DEC}$     | Condensador de Desacoplo                              |

| $C_N$         | <i>capability</i> normalizada                         |

| $G$           | Ganancia                                              |

| $H_x$         | Función de Transferencia                              |

| $I_c$         | Corriente del Colector                                |

| $i_{n,TIA}^2$ | Ruido Referido a la Entrada del TIA                   |

| $k$           | Constante de Boltzman                                 |

| $n_{cla}$     | Índice de Refracción de la cubierta                   |

| $n_{co}$      | Índice de Refracción del núcleo                       |

| $P_{opt}$     | Potencia Óptica                                       |

| $q$           | Carga Eléctrica del Electrón                          |

| $Q_i$         | Transistor                                            |

| $r_{be}$      | Resistencia Base-Emisor                               |

| $r_o$         | Resistencia de Colector-Emisor                        |

| $s$           | Frecuencia Compleja                                   |

| Si            | Silicio                                               |

| $S_{intr}$    | Polo Intrínseco                                       |

| $S_p$         | Polo Complejo                                         |

| $S_z$         | Cero Complejo                                         |

| T             | Temperatura                                           |

| $T_R$         | TransResistencia                                      |

| $V_{BE}$      | Voltaje en Continua de Base-Emisor                    |

| $V_{BF}$      | Voltaje Polarización en Inversa                       |

| $V_C$         | Voltaje en Continua de Colector                       |

| $V_{CE}$      | Voltaje en Continua de Colector-Emisor                |

| $V_{DD}$      | Tensión de Alimentación                               |

| $V_R$         | Voltaje en Inversa                                    |

| $Z_{in}$      | Impedancia de Entrada                                 |

# Acrónimos

|        |                                                          |

|--------|----------------------------------------------------------|

| 3DTV   | <i>Three-Dimensional Television</i>                      |

| AC     | <i>Alternating Current</i>                               |

| ADC    | <i>Analog to Digital Converter</i>                       |

| BER    | <i>Bit Error Rate</i>                                    |

| BERT   | <i>Bit Error Rate Test</i>                               |

| BW     | <i>BandWidth</i>                                         |

| CAD    | <i>Computer Aided Design</i>                             |

| CAM    | <i>Computer Aided Manufacturing</i>                      |

| CMOS   | <i>Complementary Metal-Oxide-Semiconductor</i>           |

| DC     | <i>Direct Current</i>                                    |

| DCA    | <i>Digital Communications Analyzer</i>                   |

| DUT    | <i>Device Under Test</i>                                 |

| DVD    | <i>Digital Versatile Disc</i>                            |

| EMC    | <i>ElectroMagnetic Compatibility</i>                     |

| EMI    | <i>ElectroMagnetic Interference</i>                      |

| EQ     | <i>EQualizer</i>                                         |

| EQ-CT  | <i>EQualizer Continuous Time</i>                         |

| EQ-P   | <i>EQualizer Passive</i>                                 |

| FIR    | <i>Finite Impulse Response</i>                           |

| FOM    | <i>Figure Of Merit</i>                                   |

| FTTH   | <i>Fiber To The Home</i>                                 |

| GDE    | Grupo de Diseño Electrónico                              |

| GI-POF | <i>Graded-Index Plastic Optic Fiber</i>                  |

| GOF    | <i>Glass Optic Fiber</i>                                 |

| GTF    | Grupo de Tecnologías Fotónicas                           |

| HDTV   | <i>High Definition TeleVision</i>                        |

| I3A    | Instituto de Investigación en Ingeniería de Aragón       |

| IEEE   | <i>Institute of Electrical and Electronics Engineers</i> |

| IPTV   | <i>Internet Protocol Television</i>                      |

| ISI    | <i>Interference Inter-Symbol</i>                         |

| LA     | <i>Limiter Amplifier</i>                                 |

| LAN    | <i>Local Area Network</i>                                |

| LD     | <i>Laser Diode</i>                                       |

| LMS    | <i>Least Mean Square Error</i>                           |

| MEC    | Ministerio de Educación y Ciencia                        |

| MICINN | Ministerio de Ciencia e Innovación                       |

| MSE    | <i>Mean Squared Error</i>                                |

|        |                                                            |

|--------|------------------------------------------------------------|

| NRZ    | <i>Non Return to Zero</i>                                  |

| PCB    | <i>Printed Circuit Board</i>                               |

| PD     | <i>PhotoDiode</i>                                          |

| PFC    | Proyecto Fin de Carrera                                    |

| PIN    | <i>PN junction with Isolated region</i>                    |

| PMMA   | Polimetacrilato                                            |

| POF    | <i>Polymer Optic Fiber</i>                                 |

| PRBS   | <i>PseudoRandom Binary Sequence</i>                        |

| RX     | Receiver                                                   |

| S&H    | <i>Sample and Hold</i>                                     |

| SI-POF | <i>Step-Index Plastic Optic Fiber</i>                      |

| SMA    | <i>SubMiniature - Version A</i>                            |

| SMD    | <i>Surface Mounted Device</i>                              |

| SNR    | <i>Signal to Noise Ratio</i>                               |

| SOIC   | <i>Small-Outline Integrated Circuit</i>                    |

| SOT    | <i>Small Outline Transistor</i>                            |

| SPICE  | <i>Simulation Program with Integrated Circuit Emphasis</i> |

| TIA    | <i>TransImpedance Amplifier</i>                            |

| TX     | <i>Transmitter</i>                                         |

| VCSEL  | <i>Vertical-Cavity Surface-Emitting Laser</i>              |

# 1

## Introducción

- 1.1. Interés y Objetivos del Proyecto

- 1.2. Contexto

- 1.3. Descripción del Proyecto y Metodología

- 1.4. Fases y Programación del Trabajo

- 1.5. Herramientas Utilizadas

- 1.6. Contenidos de la Memoria

En este capítulo se describe el objetivo y alcance del proyecto, el contexto en que se realiza, la forma en que se aborda el problema –metodología, programación del trabajo y herramientas utilizadas- y, finalmente, se detallan los contenidos de la memoria.

Es sabido que en los sistemas de comunicación los niveles de interferencia inter-símbolo (ISI) aumentan considerablemente conforme la velocidad de transmisión o *bitrate* supera el ancho de banda (BW) del canal de transmisión. En consecuencia, la tasa de error de transmisión (BER) puede ser inaceptable para un determinado estándar de comunicación.

La solución más común para reducir el ISI es recurrir a la técnica de ecualización. Será ésta la técnica empleada en este Proyecto Fin de Carrera (PFC) para corregir la limitación frecuencial producida por la dispersión de la luz en las comunicaciones de fibra óptica de plástico (POF).

## 1.1. Interés y Objetivos del Proyecto

La POF representa una tecnología ya asentada en las comunicaciones serie de banda ancha, asegurando una buena calidad de servicio para aplicaciones emergentes como los servicios *triple-play*, IPTV y HDTV, e incluso para las necesidades futuras de 3DTV, cumpliendo estándares como Fast Ethernet o el IEEE 1394.

La aplicación de la fibra óptica de plástico en redes de comunicaciones de corta distancia (redes LAN) tiene un gran interés por diversos motivos que hacen que sea una alternativa tanto a la transmisión por hilo de cobre, por su mayor BW, como a la fibra óptica de vidrio (GOF), en el último tramo de redes Fiber to the Home (FTTH), debido principalmente a su mayor robustez y menor coste.

Entre las ventajas que ofrece la POF podemos citar: flexibilidad, ligereza, robustez, inmunidad total a las perturbaciones de origen electromagnético, que no produzca ni sufra interferencias por otras redes o sistemas inalámbricos y una fácil conectividad, como la tipo *garden hose*, Fig. 1.1, que permite una instalación rápida, sencilla -incluso junto al cableado eléctrico- y barata, pues no necesita personal especializado para su instalación y mantenimiento.

Fig. 1.1 Instalación de POF junto al cableado eléctrico.

Al utilizar la POF una luz dentro del espectro visible, es la única tecnología interconectada donde puede verse la señal en ambos extremos, lo que permite localizar los cortes y averías, a la vez que supone un aumento de la seguridad al no haber peligro de dañar a la retina como ocurre con la GOF.

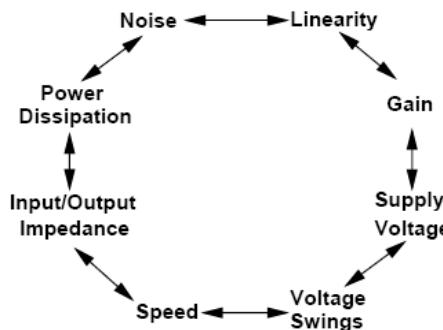

El bajo coste y la mayor robustez de la POF conlleva unas limitaciones importantes, como su alta atenuación y su bajo ancho de banda. Siendo el objetivo de este PFC corregir la limitación frecuencial de la POF, se han implementado un preamplificador y un ecualizador analógico, ambos realizados con componentes pasivos y activos comerciales. Los objetivos de diseño, Fig. 1.2, han sido el bajo coste, inherente a los sistemas de comunicaciones POF, el bajo consumo y un compromiso entre ganancia, BW y ruido que nos proporcione una optimización del diseño.

Fig. 1.2 Espacio multidimensional en el diseño analógico [RAZ99].

## 1.2. Contexto

Este PFC se encuadra en el ámbito de dos proyectos de investigación desarrollados en la Universidad de Zaragoza:

- *Estrategias de diseño de front-ends para comunicaciones ópticas* (TEC2008-05455/TEC) del Grupo de Diseño Electrónico (GDE).

- *Convergencia digital en el hogar mediante fibra óptica de plástico* (TEC2009-14718-C03-02) del Grupo de Tecnologías Fotónicas (GTF).

Durante la realización de este PFC el autor ha disfrutado de las siguientes becas:

- Beca de Colaboración, Sept. 2009/ Jun. 2010.

- Beca Multidisciplinar de Iniciación a la Investigación del I3A, Jul 2010 - Actualidad.

### 1.3. Descripción del Proyecto y Metodología

En este PFC se implementa un sistema óptico completo. El objetivo es compensar las limitaciones frecuenciales para diferentes longitudes de fibra, por lo que el trabajo desarrollado se centra en el diseño de un preamplificador y un ecualizador. De esta forma, se consigue un sistema que realiza una transmisión compatible con estándares de alta velocidad -como el IEEE 1394- para diferentes longitudes de fibra.

Para la realización del PFC, en primer lugar, se ha llevado a cabo una revisión bibliográfica y un estudio de mercado de todas las partes del sistema. Simultáneamente, se ha procedido a un estudio en profundidad de las etapas preamplificadoras y de las técnicas de ecualización analógicas.

Vistas las opciones que da el mercado y las diferentes técnicas existentes, se aplican métodos de diseño electrónico para optimizar de manera interdependiente el preamplificador y el ecualizador. Todo ello basado en un análisis sistemático mediante simulación eléctrica.

Una vez elegidos los componentes y las estructuras definitivas, se da paso al diseño e implementación de las placas de circuito impreso (PCBs) correspondientes. A continuación, se procede a la caracterización experimental de los circuitos utilizando la instrumentación específica.

Finalmente, se efectúa una optimización, reevaluando todo lo ejecutado en cada una de las etapas del proceso de diseño, se extraen las principales conclusiones y se proponen líneas futuras de actuación.

### 1.4. Fases y programación del trabajo.

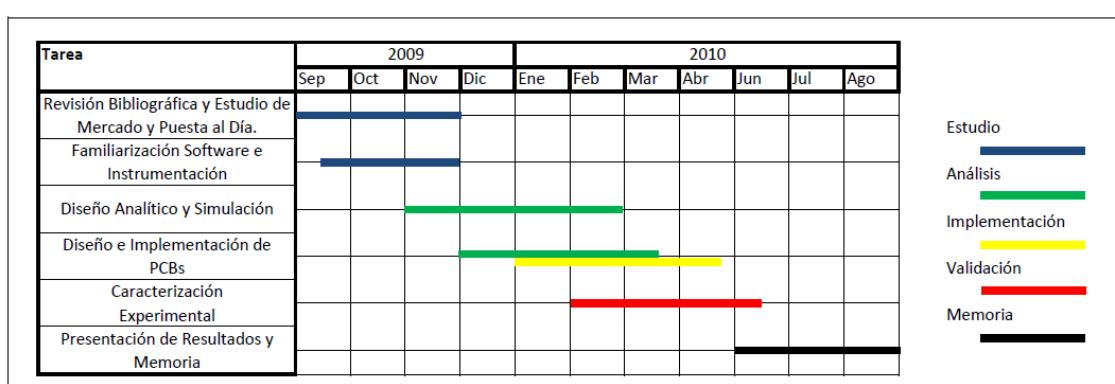

Una vez descrito el proyecto y su metodología, en el diagrama de Gantt siguiente, Tabla 1.1, se detalla el plan de trabajo de este PFC.

Tabla 1.1 Diagrama de Gantt que detalla el plan de trabajo.

## 1.5. Herramientas Utilizadas

### Herramientas Informáticas:

- Micro-Cap: Este programa se ha utilizado para realizar la simulación eléctrica de los circuitos. Se trabaja con programación SPICE y se emplean para ello los modelos SPICE que modelan el comportamiento de cada componente. Destacar que es un programa que tiene una versión gratuita que permite implementar los diferentes circuitos de manera intuitiva [MIC08].

- Altium Designer: Es un programa de diseño de placas de circuito impreso. Este software de ingeniería concurrente permite integrar el diseño de los circuitos esquemáticos y sus correspondientes placas de circuito impreso. También permite generar los archivos estándar para la fabricación de PCBs, convirtiéndose entonces en una herramienta de CAD/CAM [ALT09].

- Matlab: Gracias a sus potentes herramientas computacionales y visuales, ha servido tanto de herramienta matemática como gráfica [MAT08].

### Instrumentación:

- Analizador de Comunicaciones Digitales (DCA 86100C, Agilent): Osciloscopio de tiempo equivalente que permite analizar y visualizar señales periódicas, como pueden ser las señales PRBS (Secuencias de Bits Pseudoaleatorias) [AGI08].

- Medidor de Tasa de Error (BERT N4096A, Agilent): Genera señales PRBS que permiten, con su interacción con el DCA, obtener información sobre un sistema de transmisión. También permite medir el BER de un sistema [AGI05].

- Analizador de Redes Vectorial (ZVL 9KHz-6GHz, Rhode&Schwarz): Instrumento utilizado para obtener la respuesta frecuencial de los diferentes circuitos [R&S09].

En el anexo II se presentan de una manera más detallada tanto estos instrumentos como otros que se han empleado en la realización de este PFC.

## 1.6. Contenidos de la Memoria

- **Capítulo 1: Introducción**

Se explica el interés del proyecto y se definen los objetivos que se quieren alcanzar y su metodología. Además, se comentan los recursos utilizados a lo largo del PFC y se describe la estructura de la memoria.

- **Capítulo 2: Sistema de comunicación para banda ancha de POF**

Se realiza un repaso de los fundamentos teóricos de los diferentes componentes de un sistema de transmisión POF. Se procede, asimismo, a un estudio sobre el estado del arte de las diferentes configuraciones propuestas. Y se presenta el método de diseño electrónico, realizado mediante análisis teórico y simulación del TIA y del ecualizador.

- **Capítulo 3: Caracterización experimental**

Desarrolla la implementación y optimización de las diferentes PCBs. Detalla los *setup* necesarios para caracterizar el láser y el sistema completo. Por último, se analizan y exponen los resultados experimentales.

- **Capítulo 4: Conclusiones finales**

Tras una recapitulación del trabajo realizado, se extraen las conclusiones finales, se plantean posibles líneas futuras y se realiza una valoración personal.

# 2

## Sistemas POF

- 2.1. Visión General

- 2.2. Transmisor

- 2.3. Fibra Óptica de Plástico (POF)

- 2.4. Fotodetector

- 2.5. Preamplificador

- 1.5.1. Estudio de etapas preamplificadoras

- 1.5.2. Diseño del Amplificador de Transimpedancia (TIA)

- 2.6. Ecualizador

- 1.6.1. Estudio de Técnicas Ecualizadoras

- 1.6.2. Diseño del ecualizador (EQ)

En este capítulo se muestra primero el esquema de un sistema de transmisión de datos óptico para, a continuación, explicar los componentes que conforman el sistema completo. En los apartados correspondientes al preamplificador y el ecualizador, se detalla el diseño analítico y por simulación realizado.

## 2.1. Visión General

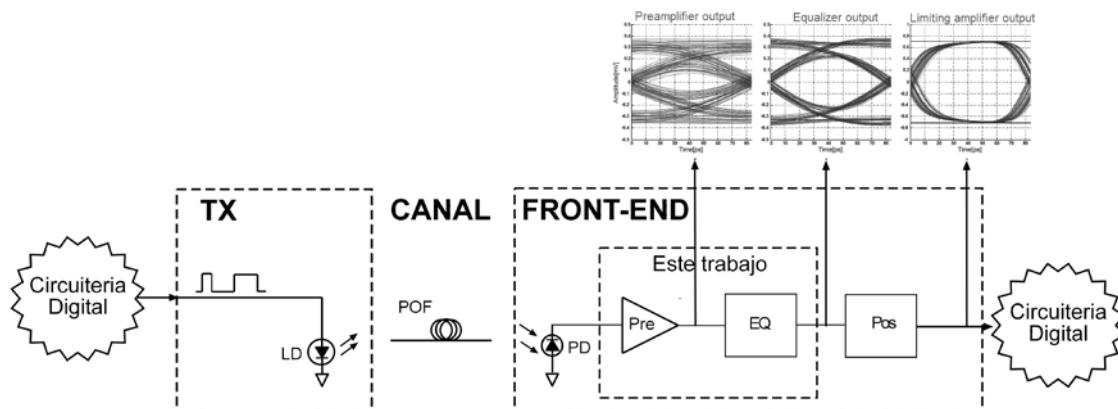

Un sistema de transmisión óptico está formado por tres componentes básicos: el transmisor (TX), el canal de transmisión y, por último, el bloque que se encarga de la recepción de la señal óptica, el *front-end*. El esquema general del sistema óptico desarrollado se representa en la Fig. 2.1.

En el sistema propuesto, el bloque de transmisión óptico lo constituye el láser (LD), que es el que transforma las señales eléctricas en luminosas. El canal empleado es la POF, por donde se transmite la luz. El *front-end* del receptor, cuya implementación es la parte central de este PFC, completa el sistema.

En el *front-end*, se encuentra en primer lugar el fotodetector o fotodiodo (PD), que es el que transforma la señal luminosa en corriente eléctrica. La etapa que viene a continuación es la preamplificador (Pre), que es la encargada de convertir la corriente generada en voltaje. Sigue la etapa ecualizadora, cuyo objetivo es corregir las limitaciones frecuenciales del sistema y, así, mejorar la señal recibida. El último bloque es la etapa postamplificadora (Pos), la encargada de proporcionar valores digitales compatibles con la circuitería digital posterior.

Fig. 2.1 Esquemático del sistema óptico completo.

## 2.2. Transmisor

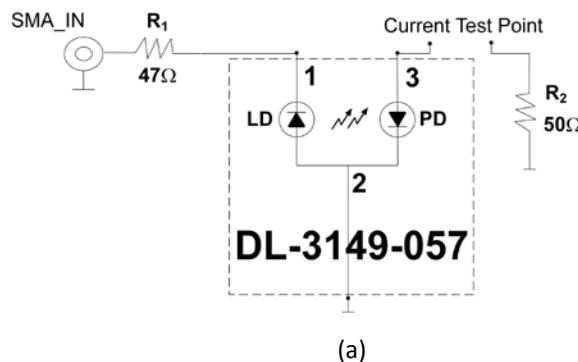

En este sistema, como ya se ha dicho en el apartado anterior, la función de transmisor la realiza el láser, que es el que convierte la señal eléctrica a transmitir en luz. En las transmisiones POF para comunicaciones de banda ancha, la emisión se realiza con láseres semiconductores (LD) basados en emisión estimulada. Esta emisión se realiza en la parte roja del espectro visible, en torno a 660-670 nm de longitud onda ( $\lambda$ ).

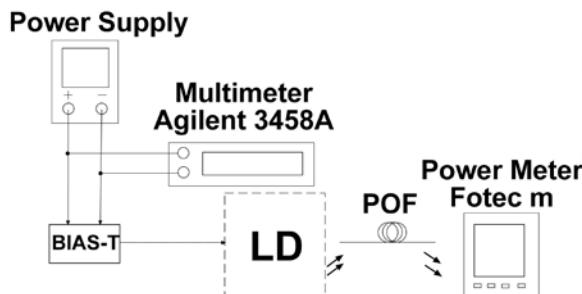

En la realización del PFC se ha utilizado un láser de bajo coste, el *red laser diode DL-3149-057*, Sanyo [Anexo III]. La principal aplicación de este láser es la de puntero láser, por lo que ha sido necesaria la implementación de una PCB específica para su uso como TX en comunicaciones de banda ancha. Hay que destacar que el uso de este tipo de láseres en comunicaciones POF fue bastante habitual hasta que se desarrollaron láseres específicos en el espectro visible para POF [ZIE08].

El desarrollo de láseres específicos de altas prestaciones para POF es uno de los ámbitos con mayor trabajo de investigación. Como demuestran las publicaciones internacionales, donde se están desarrollando los láseres VCSEL (emisión sobre superficie de cavidad vertical) en el rango de 660-680 nm [FIR06, ZIE08]. No obstante, hay que destacar el mayor inconveniente que presentan los VCSEL que se encuentran en el mercado: su alto precio.

Los criterios para elegir el LD especificado han sido: 1) el coste y 2) un comportamiento adecuado en el rango frecuencial de operación deseado. En la Fig. 2.2 se muestra de manera esquemática el diagrama de radiación de un LD y un VCSEL.

Fig. 2.2 Diagramas de emisión de un (a) LD y (b) VCSEL [GIO03]

## 2.3. Fibra Óptica de Plástico (POF)

La fibra óptica de plástico POF es el medio de transmisión en el sistema de comunicación óptico.

La POF es una guía de ondas cilíndrica formada por un polímero altamente transparente. El material más comúnmente utilizado es el polimetilmetacrilato (PMMA). La estructura física de la POF es la misma que la de las GOF y consta de tres partes, como se muestra en la Fig. 2.3.

El núcleo (*core*), en la POF, tiene una diámetro de hasta 1 mm, frente a 10  $\mu\text{m}$  que puede tener el núcleo de la GOF; es la parte central de la fibra y por donde viaja la señal luminosa, por lo que su índice de refracción ( $n_{co}$ ) ha de ser mayor que el de la cubierta ( $n_{cla}$ ). La cubierta (*cladding*) envuelve el núcleo con un material similar al de éste, pero con un índice de refracción menor para que se produzca el fenómeno de la reflexión total interna y, así, los rayos de luz sean guiados hasta el otro extremo. La capa de revestimiento (*jacket*), normalmente un polímero fluorado, no tiene incidencia en el guiado de la luz y su función es proteger el núcleo y la cubierta.

Fig. 2.3 Núcleo, cubierta y revestimiento de una PMMA-POF [GAR08].

La POF es una fibra multimodo que según el perfil de su índice de refracción puede ser de dos tipos, aquellos con una estructura de salto de índice (SI-POF) y los de índice gradual (GI-POF).

En las SI-POF, el índice de refracción del núcleo y de la cubierta son uniformes, siendo el del núcleo sensiblemente mayor, por lo que el cambio de índice de refracción al pasar de una zona a otra se produce bruscamente. En las GI-POF, el índice del núcleo varía gradualmente desde el centro del mismo hasta el revestimiento, por lo que se reduce la dispersión modal. En la Fig. 2.4, se muestra un esquemático del diagrama de rayos en ambos tipos de fibra.

Fig. 2.4 Distribución de índices de refracción, pulso de entrada, diagrama de rayos en la POF y pulso de salida. SI-POF (superior) y GI-POF (inferior) [ARA10].

Los principales parámetros que limitan el BW y la velocidad de transmisión de la POF son la atenuación y la dispersión. Los efectos de estos dos parámetros en la transmisión se aprecian en la Fig. 2.5.

Las pérdidas en las fibras se pueden clasificar en intrínsecas, las que dependen del material, y extrínsecas, las que se deben a malas conexiones o curvaturas de la fibra. La atenuación intrínseca en la POF ( $\approx 200$  dB/Km) es mucho mayor que la que se produce en la GOF (3 dB/Km), lo que limita la POF a aplicaciones de corta distancia.

Junto a la atenuación, el otro parámetro que limita el BW y la velocidad de transmisión es la dispersión. Entendiendo por dispersión el fenómeno por el cual un pulso se ensancha a medida que se propaga a través de la fibra. Esto se debe a que los distintos modos de la luz viajan a distintas velocidades y llegan al receptor en diferentes instantes de tiempo. Los principales tipos de dispersión son: modal, cromática y de polarización [ZIE08].

Fig. 2.5 Efecto de la dispersión y atenuación en una transmisión por fibra óptica [GAR08].

Si se analiza el efecto de la dispersión en el dominio de la frecuencia, se observa que las diferentes componentes frecuenciales sufren distintos retardos y atenuaciones. Las altas frecuencias son más fuertemente atenuadas. De esta forma, se puede afirmar que la POF tiene un marcado carácter de filtro paso-bajo, por lo que una ecualización que elimine esta limitación frecuencial es necesaria para comunicaciones con velocidades elevadas. Hay que destacar que tanto la atenuación como el BW de la POF varían en función de la longitud de la fibra, lo que impone la necesidad de una ecualización adaptativa.

La fibra que se va a utilizar es SI-POF, en concreto la ESKA Premier GH 4002 2.2 mm, Mitsubishi [Anexo III]. Este tipo de fibras suponen una limitación frecuencial mucho mayor que las GI-POF, sin embargo, la ventaja que tienen es su bajo coste. En la Fig. 2.6, se representa la respuesta frecuencial de esta fibra para diferentes longitudes.

Fig. 2.6. Respuesta frecuencial de la fibra para diferentes longitudes [MAT05].

## 2.4. Fotodetector

El fotodetector es el primer dispositivo de los que conforman el *front-end*, y el encargado de convertir la luz que atraviesa la fibra en corriente eléctrica.

En las aplicaciones para comunicaciones de banda ancha POF, los fotodetectores más utilizados son los fotodiodos PIN (PD). Están fabricados con semiconductores de estado sólido, siendo el material más usado el Silicio (Si), por su reducido coste de fabricación y por presentar buena eficiencia en la longitud de onda de trabajo de la POF ( $\lambda \approx 660$  nm), Fig. 2.7. Dicha eficiencia viene determinada por la responsividad del fotodiodo. Esta magnitud viene definida como la constante de proporcionalidad entre la corriente eléctrica generada por el fotodiodo y la potencia óptica incidente en el mismo.

Fig. 2.7 Responsividad de: (a) S597X Series, Hamamatsu (Si PIN PD), [Anexo III] y (b) T1670P, Vishay (Si PIN PD), [VIS10].

Desde un punto de vista eléctrico, los dos parámetros que más determinan las prestaciones de un PD son: ruido y ancho de banda. El primero está relacionado con la densidad de ruido ( $I_{N,PD}^2$ ). El segundo, con la capacidad de unión ( $C_d$ ).

En todo sistema óptico es necesario que el ruido introducido por el PD sea reducido. Principalmente el PD genera ruido térmico y *shot*, siendo normalmente el segundo el término dominante. La densidad de ruido puede expresarse de manera aproximada por la ecuación 2.1. En esta expresión,  $I_{OFFSET}$  representa la componente en DC de la señal de entrada más la corriente de oscuridad del PD y  $q$ , la carga eléctrica del electrón [SÄC05]:

$$I_{N,PD}^2 \approx 2qI_{OFFSET} \quad (2.1)$$

Por otro lado, en un PD, la  $C_d$  es quien condiciona la respuesta en frecuencia. Esta magnitud depende del voltaje en inversa que se aplique al PD ( $V_R$ ). Si se ponen valores altos de voltaje inverso, esta capacidad se ve reducida considerablemente. Esto puede ser visto en las siguientes gráficas proporcionadas por varios fabricantes, Fig. 2.8.

Fig. 2.8 Capacidad de unión: (a) Serie S597X, Hamamatsu (Si PIN PD) [Anexo III] y (b) T1670P, Vishay (Si PIN PD) [VIS10].

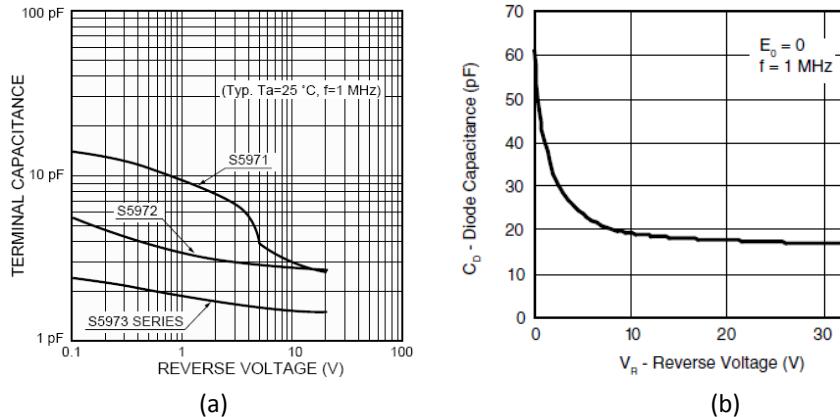

Teniendo en cuenta lo anteriormente mencionado, el modelo para pequeña señal de un PD será el mostrado en la Fig. 2.9:

Fig. 2.9 Fotodiodo: (a) Símbolo y (b) modelo de pequeña señal del PD.

El fotodetector que se ha elegido es el S5972 Si-PIN PD, Hamamatsu, con distribución de pines T0-18 [Anexo III]. Un aspecto determinante, y que ha condicionado la elección de nuestro PD, ha sido su área de detección. Ésta viene condicionada por el diámetro de la POF ( $\phi \approx 1 \text{ mm}$ ), puesto que ambos deben ser similares. Esta característica impone un rango de valores relativamente elevado para  $C_d$ : de 3 a 5 pF.

Las severas limitaciones frecuenciales impuestas por la POF y el fotodetector hacen imprescindible que deban aplicarse ciertas técnicas de ecualización que permitan compensar estas limitaciones y alcanzar las velocidades de transmisión adecuadas.

## 2.5. Preamplificador

En primer lugar, se realiza un estudio del estado del arte sobre las diferentes etapas preamplificadoras, eligiendo aquella etapa y componentes que después de un riguroso análisis teórico más convenga a esta aplicación. En el siguiente punto, se realiza un diseño analítico y por simulación con el fin de optimizar la etapa elegida.

### 2.5.1. Análisis de Etapas Preamplificadoras

El preamplificador se encarga de transformar la corriente generada por el fotodiodo en un voltaje de salida. Las condiciones ideales de un buen preamplificador son: alta transresistencia ( $T_R$ ), elevado ancho de banda, bajo ruido referido a la entrada ( $I_{N,IN}^2$ ) y bajo consumo en potencia.

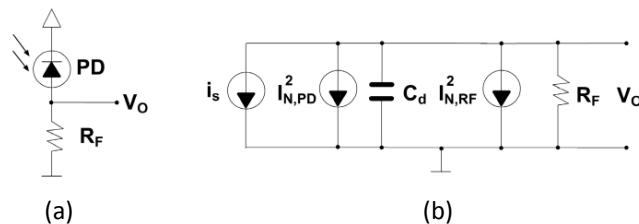

En líneas generales, las tres implementaciones más comunes son: carga resistiva pasiva, amplificador de transimpedancia tipo *shunt-feedback* (TIA), y modo corriente [ING04]. A continuación se examinan las características de cada implementación.

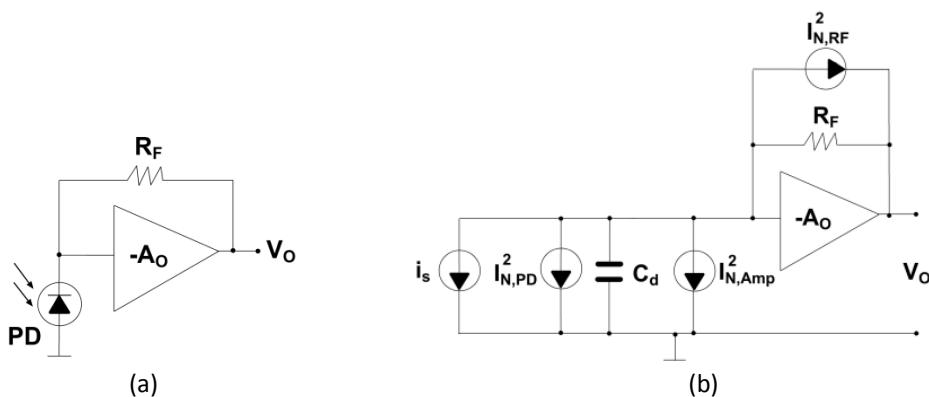

Los preamplificadores basados en carga pasiva convierten la corriente fotogenerada en voltaje a través de una resistencia,  $R_F$ . Considerando el modelo de pequeña señal, Fig. 2.10, e incluyendo el ruido térmico generado por la resistencia  $R_F$  ( $I_{N,RF}^2$ ), se obtienen los diferentes parámetros críticos de este tipo de preamplificador:

$$T_R = R_F \quad (2.2)$$

$$BW = \frac{1}{C_d R_F} \quad (2.3)$$

$$I_{N,IN}^2 = I_{N,PD}^2 + I_{N,RF}^2 = 2qI_{OFFSET} + \frac{4kT}{R_F} \quad (2.4)$$

Fig. 2.10 Preamplificador de carga resistiva pasiva: (a) circuito y (b) modelo equivalente.

donde las magnitudes fundamentales que aparecen son:  $k$ , la constante de Boltzman;  $q$ , la carga eléctrica del electrón; y  $T$ , la temperatura ambiente ( $T=300K$ ).

Si el valor de la resistencia es bajo, el BW será elevado, pero la sensibilidad del sistema se reduce notablemente. Esto último se debe a que la  $T_R$  se ve reducida y la contribución de ruido del sistema se ve incrementada. Sin embargo, si se elige una resistencia elevada, la situación sería la opuesta. La aplicación de esta etapa preamplificadora requiere el uso de postamplificadores de altas prestaciones, haciendo el diseño altamente complejo.

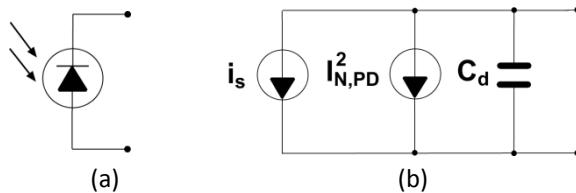

Situaciones intermedias a las expuestas con anterioridad se encuentran con el uso de preamplificadores TIA y los de modo-corriente. En la Fig. 2.11, se muestra la configuración básica del TIA y su modelo para pequeña señal. En esta configuración, la resistencia es conectada en un bucle de realimentación negativa a través de un amplificador de voltaje. Considerando este amplificador ideal con ganancia  $A_o$  y aplicando una aproximación de primer orden, se obtienen las magnitudes más importantes de este tipo de preamplificadores, mostradas en las siguientes ecuaciones [RAZ03]:

$$T_R(s \rightarrow 0) = \frac{-A_o}{1 + A_o} \cdot R_F \approx -R_F \quad \text{si } A_o \gg 1 \quad (2.5)$$

$$BW = \frac{1 + A_o}{C_d R_F} \approx \frac{A_o}{C_d R_F} \quad \text{si } A_o \gg 1 \quad (2.6)$$

$$I_{N,IN}^2 \approx I_{N,PD}^2 + I_{N,RF}^2 + I_{N,Amp}^2 \approx 2qI_{OFFSET} + \frac{4kT}{R_F} + I_{N,Amp}^2 \quad (2.7)$$

Fig. 2.11 TIA: (a) circuito y (b) modelo equivalente de pequeña señal.

En las ecuaciones (2.5-2.7), se tiene que  $A_o$  es la ganancia del amplificador de voltaje, e  $I_{N,AMP}^2$ , el ruido referido al amplificador.

Si la prioridad es una alta sensibilidad, se usará un valor alto de  $R_F$ . De esta forma  $T_R$  aumenta, pero el BW disminuye. Sin embargo, en este caso la presencia de  $A_0$  en el numerador del BW permitirá compensar la reducción de ancho de banda, debido al aumento de valor de  $R_F$ . Esta es la principal ventaja de usar este tipo de configuración [TAO06].

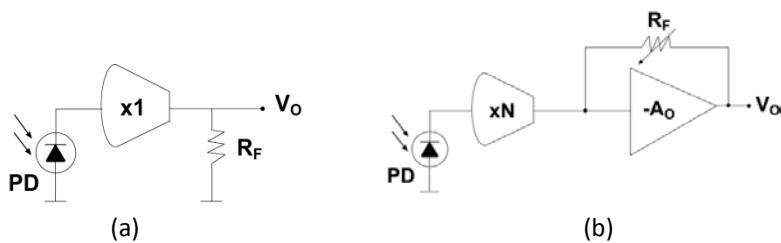

El otro tipo de preamplificador se basa en una amplificación en modo-corriente como etapa de entrada, combinada con alguna de las etapas intensidad-voltaje anteriormente comentadas, Fig. 2.12. La única ventaja que aporta es el aumento de BW, debido a la reducida resistencia de entrada. Sin embargo, presenta dos serios inconvenientes: los aumentos considerables de ruido y un mayor consumo de potencia [SAC05].

Fig. 2.12 Diagrama de Bloques de preamplificadores de modo corriente combinados con:

(a) Carga resistiva pasiva y (b) TIA.

Del análisis anterior se desprende que el preamplificador que proporciona un mejor compromiso entre  $T_R$ , BW y ruido, así como un moderado consumo, será un TIA.

Entre las diferentes implementaciones del TIA, se ha optado por diseñar la parte activa con una sola etapa. Con ello se consigue un menor coste, menor consumo, menor ruido y mayor estabilidad que con otras configuraciones de más etapas.

A la hora de elegir la implementación del TIA con componentes comerciales, el dispositivo más importante es el transistor. De entre las posibles tecnologías, las dos con una mayor versatilidad son la CMOS y la bipolar. Los transistores bipolares tienen un mayor ruido, pero también tienen un mayor factor de ganancia y, por lo tanto, el sistema debería mantener o favorecer la sensibilidad. Dado que no se ha encontrado en el mercado transistores CMOS comerciales para las frecuencias deseadas, la decisión final ha sido la elección de tecnologías bipolares. Se utilizarán transistores NPN por su mayor velocidad frente a los PNP.

Las implementaciones monoetapa consideradas son dos: la configuración emisor común y la configuración cascodo, ambas representadas en la Fig. 2.13.

Fig 2.13 Configuraciones monoetapa: (a) emisor-común y (b) cascodo.

La segunda configuración impone un rango dinámico reducido a la salida. Esta característica hace que no sea adecuada para comunicaciones POF, pues la excursión de la señal de entrada varía considerablemente en función de la longitud de la fibra. Otra desventaja es su mayor coste, debido a que necesita una fuente de tensión flotante para desplazar el nivel en DC a la salida ( $V_{LEV}$ ), así como el uso de un transistor extra.

Una característica muy importante de la etapa emisor-común es que se trata de una etapa autopolarizada, por lo que no se necesitará ningún voltaje de polarización ( $V_B$ ) para el correcto funcionamiento del TIA.

Una condición de diseño impuesta al transistor bipolar del TIA es que sea de altas prestaciones, principalmente de una alta frecuencia de transición. La razón de esta condición es doble: validar las ecuaciones de primer orden previamente expuestas y simplificar el diseño del ecualizador. Esto se consigue gracias a que el polo introducido por el amplificador de tensión queda en frecuencias suficientemente mayores que la de operación, pudiendo modelar el amplificador de tensión como un bloque ideal. Por todo esto, la tecnología elegida ha sido la de Silicio-Germanio y el transistor utilizado es el BFP640, Infineon con *package* SOT-343 [Anexo III].

### 2.5.2. Diseño del Amplificador de Transimpedancia (TIA)

Una vez elegida la implementación de la etapa preamplificadora, el objetivo va a ser buscar el compromiso óptimo entre  $T_R$ , BW, ruido y consumo en potencia.

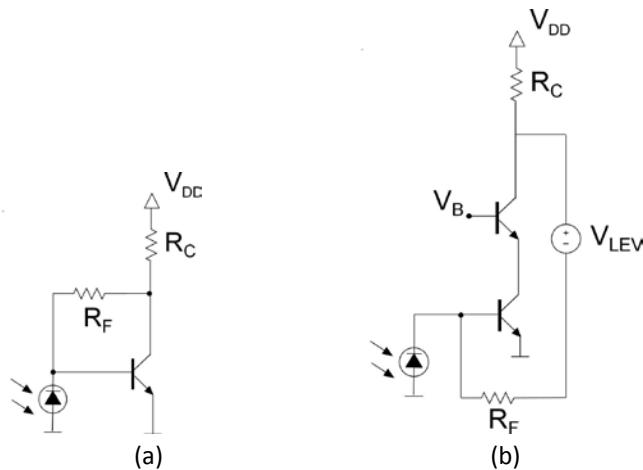

En primer lugar, debe establecerse un punto óptimo de polarización de la etapa. Para ello se analiza la estructura elegida (Fig. 2.13.a) y se fija de partida la corriente ( $I_C$ ) y la tensión de colector ( $V_C$ ). Posteriormente, se obtiene el valor de las resistencias en función de dichos parámetros. Este segundo paso es relativamente sencillo, y de hecho las expresiones (2.8) y (2.9) así lo demuestran. En la Fig. 2.14.a aparecen las magnitudes características del transistor y en la Fig. 2.14.b el valor de las resistencias, ambas obtenidas por simulación y en función de  $I_C$ .

$$R_C = \frac{V_{DD} - V_C}{I_C} \quad (2.8)$$

$$R_F = \beta \cdot \frac{V_C - V_{BE}}{I_C} \quad (2.9)$$

Figura 2.14 (a) Valores característicos del transistor BFP640,  $V_{BE}$  (azul) y  $\beta$  (verde). (b) Valores de las resistencias del TIA:  $R_F$  (azul) y  $R_C$  (verde). Todo ello en función de  $I_C$  y con  $V_C=1.7$ .

Sin embargo, la elección de  $I_C$  y  $V_C$  no es una tarea sencilla. Existen diversas condiciones de diseño que deben cumplirse simultáneamente. Por un lado, para asegurar un buen rango dinámico y un óptimo voltaje de polarización, tanto de esta etapa (preamplificador) como de la siguiente (ecualizador), se impone una  $V_C \approx 1.7$  V. Y por otro lado, la elección de  $I_C$  exige un riguroso análisis de la *capability* del sistema. Este parámetro proporciona una figura de mérito (FOM) de la capacidad de transmisión del canal, tal y como se detalla en [VER03]. En la siguiente ecuación (2.10), se presenta dicho análisis:

$$C = BW \cdot \log_2 \left( \frac{i_{in} + (\bar{i}_{n,TIA}^2)^{\frac{1}{2}}}{(\bar{i}_{n,TIA}^2)^{\frac{1}{2}}} \right) \quad (2.10)$$

donde  $i_{in}$  representa la amplitud de la señal de entrada -tomando un valor estándar de  $1\mu\text{A}$ - e  $\bar{i}_{n,TIA}^2$  es el ruido referido a la entrada del TIA. Dicha magnitud es la FOM a optimizar, ya que tiene en cuenta todos los parámetros importantes involucrados en el diseño. Por todo ello, a continuación, se realiza un estudio teórico de los diferentes parámetros del TIA.

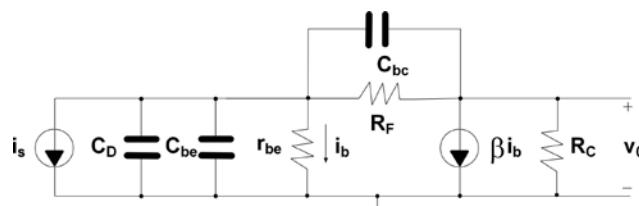

Si se aplica el modelo equivalente para pequeña señal [GRA10], Fig. 2.15, se puede calcular la transimpedancia (2.11), el ancho de banda (2.12), la impedancia de entrada (2.13) y el ruido referido a la entrada (2.14). Las principales fuentes de ruido son el ruido térmico que genera la  $R_F$  y el ruido *shot* debido a la corriente que circula por la base ( $I_B$ ) [SÄC05]. En el análisis del ruido, hay que resaltar que los condensadores no contribuyen al ruido a menos que tengan una componente resistiva importante.

$$T_R(s \rightarrow 0) \approx (\beta \cdot R_{L1}) \parallel R_F \quad (2.11)$$

$$BW \approx \frac{1}{2\pi \cdot \left( \frac{C_d + C_{be}}{\beta} + C_{bc} \right) \cdot T_R} \quad (2.12)$$

$$Z_{in}(s \rightarrow 0) = \frac{\beta \cdot R_C \cdot R_F + R_C \cdot r_{be}}{r_{be} + R_F + R_C \cdot (\beta + 1)} \quad (2.13)$$

$$\bar{i}_{n,TIA}^2 \approx \left( \frac{4kT}{R_F} + 2qI_B \right) BW_n = \left( \frac{4kT}{R_F} + \frac{2qI_C}{\beta} \right) BW_n \quad (2.14)$$

Fig. 2.15 Modelo equivalente para pequeña señal del TIA.

En las expresiones y modelos anteriores,  $r_{be}$  representa la resistencia base-emisor;  $C_{be}$ , la capacidad base-emisor;  $C_{bc}$ , la capacidad base-colector; y  $BW_n$  es el ancho de banda del ruido blanco referido a la entrada ( $BW_n = 1.1 \cdot BW$ ).

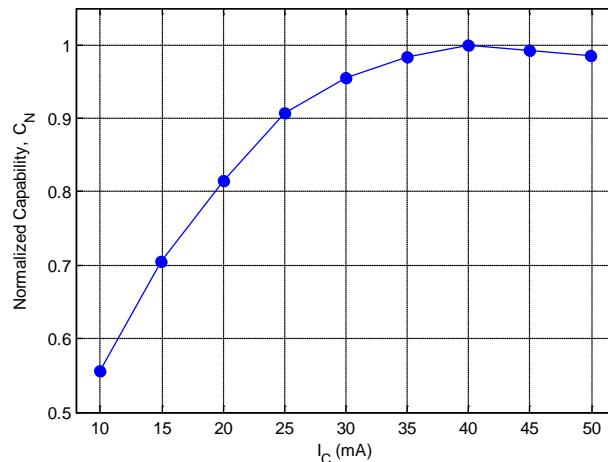

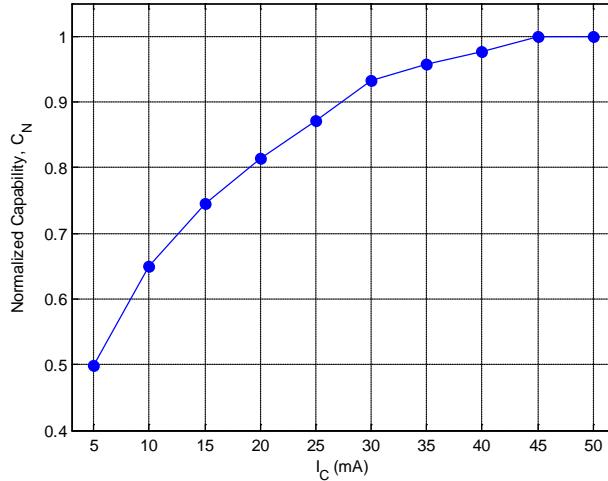

El siguiente paso será calcular la *capability* (2.10) en función de  $I_C$ . Para ello, se utiliza el simulador eléctrico, debido a la complejidad de las dependencias con la corriente. En la Fig. 2.16 se representa de manera normalizada.

Fig. 2.16 *Capability* normalizada del TIA en función de  $I_C$ .

Se observa que la *capability* normalizada ( $C_N$ ) es máxima para  $I_C=40$  mA, pero la elección final ha sido  $I_C=30$  mA. Esto se debe a dos motivos: a que se consigue un *matching* de  $50\Omega$  a la salida y a que el aumento de  $C_N$  no justifica el mayor consumo.

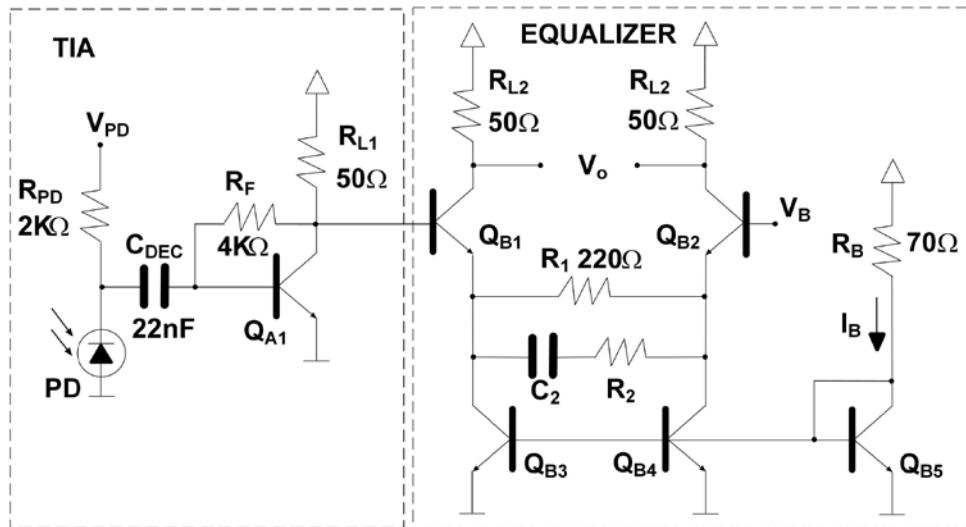

Como conclusión, el punto de polarización elegido es  $I_C = 30$  mA y  $V_{CE} \approx 1.75$  v. Las resistencias del TIA toman los valores de  $R_F = 4$  k $\Omega$  y  $R_{L1} = 50\Omega$ . Las prestaciones obtenidas son:  $T_R \approx 70$  dB $\Omega$ ,  $BW \approx 251$  MHz y  $i_{n,TIA}^2 \approx 125$  nA<sub>rms</sub> (referido a la salida,  $V_{on,TIA}^2 \approx 410$   $\mu$ V<sub>rms</sub>).

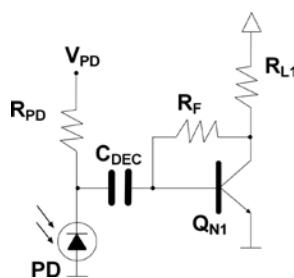

Para garantizar que el punto de polarización sea estable y que el fotodetector se pueda polarizar de manera independiente, se implementa la red de desacoplo mostrada en la Fig. 2.17. Para asegurar el correcto funcionamiento del preamplificador, se imponen dos importantes condiciones de diseño: 1)  $C_{DEC}$  debe ser suficientemente elevado como para que la constante de tiempo no influya en el comportamiento del circuito a altas frecuencias y 2)  $R_{PD} \gg Z_{in}$ . Según (2.13) tenemos una  $Z_{in} \approx 100\Omega$ . De esta forma, los valores elegidos son  $C_{DEC}=22nF$  y  $R_{PD}=2K\Omega$ .

Fig. 2.17 Arquitectura del preamplificador propuesto.

## 2.6. Ecualizador

La distribución de este apartado tiene la misma estructura que la del preamplificador. En primer lugar, estudio del arte de las técnicas de ecualización y, a continuación, diseño analítico y por simulación de la opción elegida.

### 2.6.1. Análisis Etapas Ecualizadoras

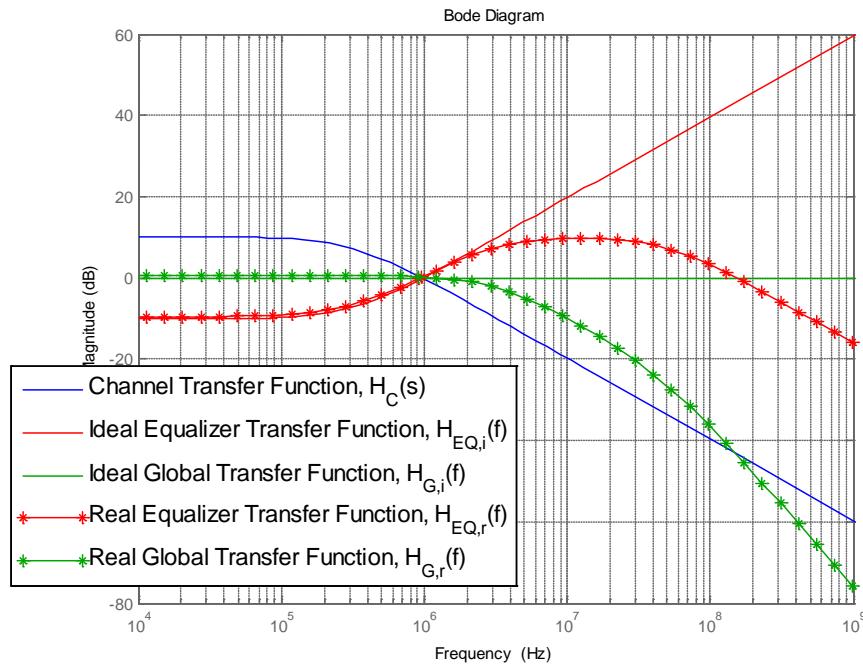

El ecualizador es el bloque que corrige la limitación frecuencial debida a las características de la POF y al PD. La característica ideal de un EQ es que tenga una respuesta frecuencial inversa a la del canal, consiguiendo así que el sistema se comporte idealmente como un filtro paso-todo. A continuación se exponen los conceptos básicos de la ecualización.

El canal se modela de manera simplificada como un filtro paso-bajo con un polo dominante desplazado del origen,  $H_C$  (2.15); el objetivo del EQ es compensar la frecuencia asociada al polo ( $s_p$ ) del canal, por lo que la respuesta ideal del ecualizador,  $H_{EQ,i}$  (2.16), debe ser la inversa del canal. De esta forma se consigue un canal paso-todo en la respuesta del canal ideal ( $H_{C,i}$ ), como queda representado en la Fig. 2.18 [SUN05].

Antes de continuar, resaltar que lo expuesto anteriormente es un caso ideal. En un caso real, la respuesta del ecualizador,  $H_{EQ,r}$  (2.17), va a tener incluido al menos un polo intrínseco dominante ( $s_{intr}$ ) y, por lo tanto, la respuesta global del canal,  $H_{G,r}$  (2.18), más la del ecualizador tendrá un comportamiento típico paso-bajo. En la Fig. 2.18 se representa la respuesta frecuencial de un caso real de ecualización.

$$H_C(s) = \frac{A}{1 + \frac{s}{s_p}} \quad (2.15)$$

$$H_{EQ,i}(s) = \frac{1}{H_C(s)} = \frac{1}{A} \cdot \frac{1 + \frac{s}{s_p}}{1 + \frac{s}{s_z}} = A_{EQ} \cdot \left(1 + \frac{s}{s_z}\right) \quad (2.16)$$

$$H_{EQ,r}(s) = \frac{1}{H_C(s)} = A_{EQ} \cdot \frac{\left(1 + \frac{s}{s_z}\right)}{\left(1 + \frac{s}{s_{intr}}\right)} \quad (2.17)$$

$$H_{G,r}(s) = H_C(s) \cdot H_{EQ,r}(s) = \frac{A}{1 + \frac{s}{s_p}} A_{EQ} \cdot \frac{(1 + \frac{s}{s_z})}{(1 + \frac{s}{s_{intr}})} = \frac{1}{(1 + \frac{s}{s_{intr}})} \quad (2.18)$$

Fig. 2.18 Respuesta representativa del canal, ecualizador y respuesta global para el caso ideal y real.

Una vez introducidos los conceptos básicos, el siguiente punto es presentar las diferentes técnicas de ecualización. Para tener una visión global de las mismas se ha realizado un esquema de las diferentes implementaciones, teniendo en cuenta diversos criterios de diseño, Tabla 2.1.

La realización de una ecualización en el transmisor (EQ-TX) [HAR06] imposibilita la ecualización adaptativa necesaria en la POF. Los bajos niveles de señal hacen que un ecualizador pasivo (EQ-P) [MAX03] no resulte práctico. Y por último, utilizar los filtros FIR de alta velocidad como ecualizadores (EQ-FIR) [LEE01] incumpliría la condición de bajo coste y bajo consumo que perseguimos.

Tras este análisis teórico de las propuestas recogidas en la bibliografía, se llega a la conclusión de que la mejor elección es la ecualización de tiempo continuo en el receptor (EQ-CT). Esta opción es la que proporciona un mejor compromiso entre coste, consumo y adaptabilidad.

| Ubicación                    | Técnica                           | Ventajas                                               | Desventajas                                             |

|------------------------------|-----------------------------------|--------------------------------------------------------|---------------------------------------------------------|

| Transmisor<br><b>(EQ-TX)</b> | De-énfasis                        | Fácil de aplicar. Filtros FIR usando bus de datos      | No dispone información sobre el canal                   |

|                              | Pre-énfasis                       |                                                        |                                                         |

| Receptor<br><b>(EQ-RX)</b>   | Pasivo<br><b>(EQ-P)</b>           | Consumo Nulo                                           | Se necesita amplitud elevada de entrada y elevado SNR   |

|                              | Tiempo Continuo<br><b>(EQ-CT)</b> | Compromiso entre consumo, coste y adaptabilidad        | Escasa Programabilidad                                  |

|                              | Filtros FIR<br><b>(EQ-FIR)</b>    | Altamente adaptativo. Uso algoritmo como LMS, MSE, ... | Alta Complejidad. Necesidad ADC y S&H de alta velocidad |

Tabla 2.1 Análisis de las Técnicas de Ecualización.

La técnica EQ-CT [LIU04] se basa en la división de la señal en dos caminos: uno en el que se amplifican las altas frecuencias mediante un filtro paso-alta y otro en el que se implementa un paso-todo. De esta forma se consigue un comportamiento de filtro paso-alto de ganancia variable. En la Fig. 2.19 se presenta su diagrama de bloques.

Fig. 2.19 Diagrama de bloques de un EQ-CT. La respuesta obtenida es un filtro paso-alta de ganancia variable.

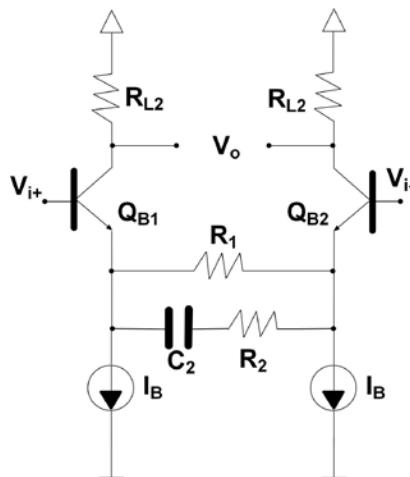

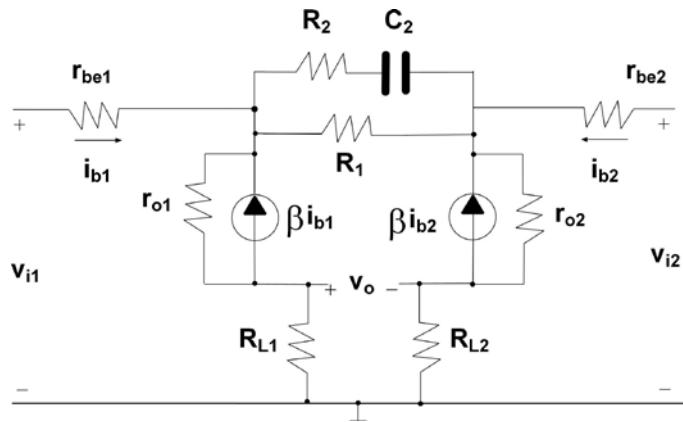

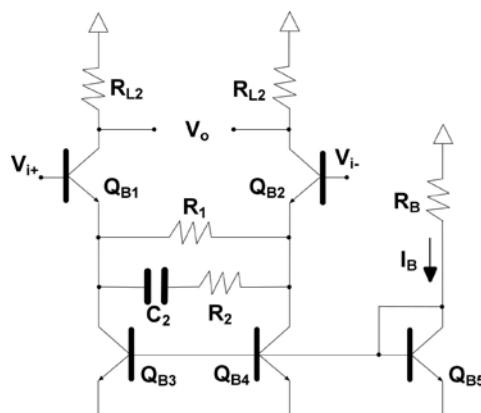

En este trabajo, el anterior diagrama de bloques se implementa con la configuración mostrada en la Fig. 2.20. Dicha estructura está basada en una etapa diferencial con degeneración de fuente implementada en tecnología CMOS [AZN10, RAD05], con la que se obtiene también una relación señal a ruido (SNR) mejor. La topología será analizada con detalle en el siguiente apartado. Hay que destacar que variando los valores de la red del par degenerado ( $R_1, C_2, R_2$ ) se modifica el comportamiento en frecuencia del ecualizador y que, de esta forma, se puede implementar una ecualización adaptativa. Un estudio sobre las técnicas de ecualización adaptativa se realiza en el anexo I.

Fig. 2.20 Arquitectura del EQ propuesto: par diferencial con degeneración de fuente.

Para la implementación del circuito se ha optado por el uso de *arrays* de transistores en vez de transistores singulares. Los motivos de esta elección han sido el menor coste y el mejor *matching* entre los transistores que componen el *array*. Esta última ventaja asegura un funcionamiento más eficaz tanto del par diferencial como de los espejos de corriente. El *array* de transistores elegido ha sido el HFA3127, Intersil, compuesto por cinco transistores NPN y encapsulado SOIC [Anexo III].

### 2.6.2. Diseño del Ecualizador

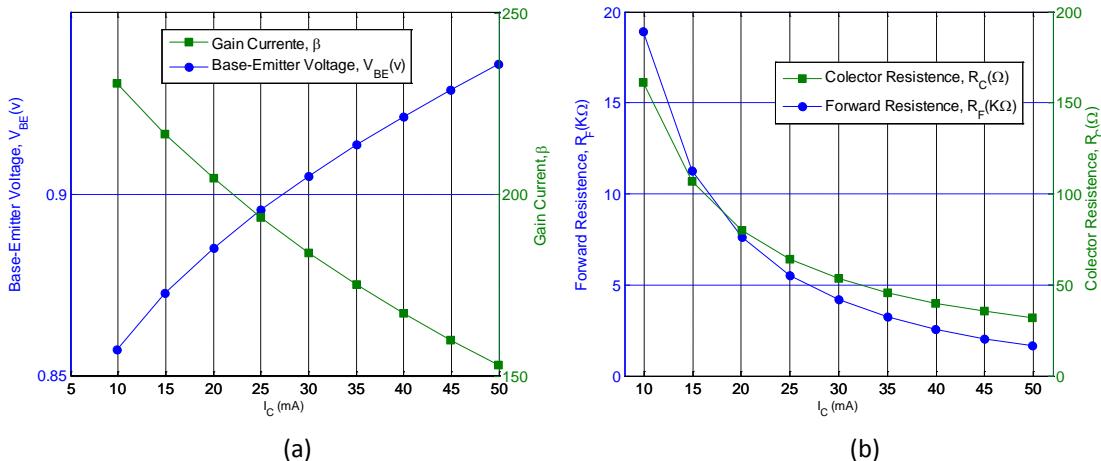

Llegados a este punto, y al igual que se hizo con el TIA, debemos establecer un punto óptimo de polarización. Los criterios que se tienen en cuenta son: la correcta polarización de los espejos de corriente y maximizar la *capability* [VER03].

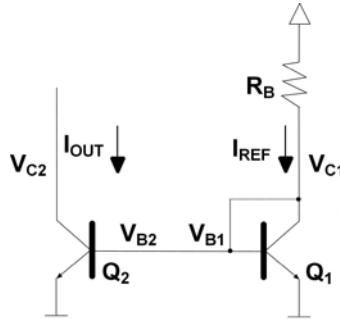

El primer paso es implementar las fuentes de corriente ideales. Se ha optado por la utilización de espejos de corriente en su estructura más sencilla. Esta configuración nos permite replicar de manera correcta la intensidad de polarización en ambas ramas.

El espejo de corriente, Fig. 2.21, consta de dos transistores, uno de ellos ( $Q_1$ ) genera una intensidad de referencia ajustable dada por la ecuación 2.19, y el otro replica dicha corriente. Para asegurar su funcionamiento, es necesario que ambos trabajen en modo activo. Como el  $Q_1$  se encuentra en configuración de diodo, siempre está en activa, por lo que sólo hay que asegurar que  $V_{C2} \geq 0.2$  v. Se decide que  $V_{C2} \approx V_{C1} \approx 0.8$  v. y de esta forma la réplica de corriente es más exacta [MAL03].

$$I_{REF} = \frac{V_{DD} - V_{BE1}}{R_B} \quad (2.19)$$

Fig.2.21 Esquema del espejo de corriente implementado.

Como se ha podido observar, el espejo de corriente nos impone un voltaje en el emisor de los transistores  $Q_{B1}$  y  $Q_{B2}$ , Fig. 2.20, de aproximadamente 0.8 V. Por esto, se decide que un voltaje óptimo para el colector de dichos transistores es  $V_C = 1.75$  V. Con estas consideraciones lo que se consigue es que los voltajes colector-emisor de los transistores del par sean  $V_{CE} \approx 1$  V.

El siguiente parámetro a fijar es la  $I_C$ , para lo cual se estudia inicialmente el par diferencial sin degeneración de fuente. Nuevamente, la magnitud a optimizar es la *capability* (2.10), pero en este caso se toma ruido unidad al no ser un parámetro crítico en esta etapa. Procediendo de la misma manera que con el TIA, los resultados de la *capability* normalizados son los mostrados en la Fig. 2.22.

Fig. 2.22 Capability normalizada del EQ en función de  $I_C$ .

Se puede observar que la máxima *capability* se alcanza con  $I_C=50$  mA. Pero de nuevo nuestra elección será  $I_C=30$  mA. Esta elección está justificada por dos razones: 1) con el valor de corriente escogido se obtiene una  $R_{L1} \approx 50 \Omega$  y por lo tanto el *matching* de salida está asegurado y 2) un aumento en el consumo del 66 % apenas supone una pérdida del 5% de *capability*. Con el par diferencial polarizado con  $I_C = 30$  mA y  $V_{CE} \approx 1$  V, se tiene que  $R_B = 70 \Omega$ ,  $G \approx 17$  dB y  $BW \approx 600$  MHz.

Una vez seleccionado el punto de operación, se procede a diseñar la red de ecualización. Para ello se aplica el modelo equivalente para pequeña señal, Fig. 2.23, y se obtiene la función de transferencia y las impedancias de entrada y salida. Las expresiones de dichas magnitudes son las ecuaciones 2.20, 2.21 y 2.22 [GRA10]. Si se analiza la función de transferencia, se aprecia la aparición de un polo y un cero, que es precisamente la que se espera de un ecualizador.

$$H(s) \approx \frac{\beta R_L}{r_{be} + (\beta + 1)R_1} \cdot \frac{1 + sC_1(R_1 + R_2)}{1 + s \frac{C_1(r_{be}(R_1 + R_2) + (\beta + 1)R_1R_2)}{r_{be} + (\beta + 1)R_1}} \quad (2.20)$$

$$Z_{in}(s \rightarrow 0) \approx r_{be} + (\beta + 1)R_1 \quad (2.21)$$

$$Z_o(s \rightarrow 0) \approx R_{L1} \left\| r_o \cdot \left( \frac{r_{be} + (\beta + 1)R_1}{r_{be} + R_1} \right) \right\| \quad (2.22)$$

Fig. 2.23 Modelo equivalente de pequeña señal del EQ.

En estas ecuaciones y en el modelo, aparece  $r_{oi}$  que se corresponde con la resistencia de colector-emisor. Debido a su alto valor sólo influye en el cálculo de la impedancia de salida.