2020

36

Miguel García Bosque

# Digital Design of New Chaotic Ciphers for Ethernet Traffic

Departamento

Ingeniería Electrónica y Comunicaciones

Director/es

Celma Pueyo, Santiago Sánchez Azqueta, Carlos

#### **Tesis Doctoral**

## DIGITAL DESIGN OF NEW CHAOTIC CIPHERS FOR ETHERNET TRAFFIC

**Autor**

Miguel García Bosque

Director/es

Celma Pueyo, Santiago Sánchez Azqueta, Carlos

#### **UNIVERSIDAD DE ZARAGOZA**

Ingeniería Electrónica y Comunicaciones

2019

# DIGITAL DESIGN OF NEW CHAOTIC CIPHERS FOR ETHERNET TRAFFIC

#### Miguel García Bosque

Grupo de Diseño Electrónico – I3A

Departamento de Ingeniería Electrónica y Comunicaciones

Facultad de Ciencias

Universidad de Zaragoza

# DIGITAL DESIGN OF NEW CHAOTIC CIPHERS FOR ETHERNET TRAFFIC

A thesis submitted to the University of Zaragoza in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in Physics

by **Miguel García Bosque**

Thesis Supervisors

Dr. Santiago Celma Pueyo Dr. Carlos Sánchez Azqueta

Electronic Design Group – I3A

Department of Electronic Engineering and Communications

Faculty of Science – University of Zaragoza

Zaragoza, September 2019

# DIGITAL DESIGN OF NEW CHAOTIC CIPHERS FOR ETHERNET TRAFFIC

Tesis presentada a la Universidad de Zaragoza para optar al grado de Doctor en Física

por **Miguel García Bosque**

bajo la supervisión de los Doctores

Dr. Santiago Celma Pueyo Dr. Carlos Sánchez Azqueta

Grupo de Diseño Electrónico – I3A

Departamento de Ingeniería Electrónica y Comunicaciones

Facultad de Ciencias - Universidad de Zaragoza

A mi familia.

#### **Agradecimientos**

En primer lugar, me gustaría agradecer a mis directores, Dr. Santiago Celma y Dr. Carlos Sánchez-Azqueta, por todo su apoyo, su paciencia y sus consejos. Por compartir conmigo su conocimiento y su entusiasmo por la física y la electrónica. Gracias por haber estado siempre disponibles para echarme una mano cuando lo he necesitado.

A todas las personas que durante estos años han formado parte del GDE, por conseguir que el trabajo diario, el que no queda recogido en este documento, haya sido mucho más fácil y divertido.

También quiero agradecer a mi supervisor durante mis estancias en la Universidad de Siena, Dr. Tommaso Addabbo, por toda la ayuda prestada. Además, me gustaría agradecer a todo el grupo de investigación por haberme hecho la estancia mucho más llevadera.

Gracias a toda mi familia y amigos, por haber estado conmigo en todo momento y por hacerme merecedor de vuestro tiempo. Gracias por todas las cosas bonitas que me habéis dicho y por el apoyo que me habéis dado.

Por último, agradezco también a todas las instituciones que han financiado la investigación recogida en este trabajo: Ministerio de Economía y Competitividad del Gobierno de España, Fondo Europeo de Desarrollo Regional, Gobierno de Aragón y Horizon 2020 a través de los proyectos (TEC2014-52840-R, RTC-2015-3807-7, A38790, T26-17R y TEC2017-85867-R) y Ministerio de Educación a través del contrato predoctoral FPU (FPU14/03523). También agradecer a la Associazione di Fondazioni e di Casse di Risparmio S.p.A. y a la Circuits and Systems Society por financiar mi segunda estancia a través del programa YITP.

### **Contents**

| 1. | Intro | ducti | on                                                        | 1  |

|----|-------|-------|-----------------------------------------------------------|----|

|    | 1.1.  | Brie  | ef history of modern cryptography                         | 2  |

|    | 1.2.  | Def   | inition                                                   | 3  |

|    | 1.3.  | Sta   | te of the art and research lines                          | 5  |

|    | 1.3   | 3.1.  | Chaos-based ciphers                                       | 6  |

|    | 1.3   | 3.2.  | True Random Number Generators                             | 10 |

|    | 1.3   | 3.3.  | Optical Gigabit Ethernet                                  | 11 |

|    | 1.4.  | Obj   | ectives                                                   | 13 |

|    | 1.5.  | The   | esis organization                                         | 15 |

|    | 1.6.  | Ref   | erences                                                   | 17 |

| 2. | Impo  | rtant | Concepts and Definitions                                  | 25 |

|    | 2.1.  | Ove   | erview of a secure communication system                   | 26 |

|    | 2.1   | .1.   | Symmetric and asymmetric ciphers                          | 26 |

|    | 2.1   | .2.   | Other cryptographic primitives                            | 35 |

|    | 2.1   | .3.   | A possible secure communication protocol                  | 40 |

|    | 2.2.  | Cha   | aotic cryptography                                        | 41 |

|    | 2.2   | 2.1.  | Definition and properties of chaotic systems              | 41 |

|    | 2.2   | 2.2.  | Chaos-based stream ciphers                                | 44 |

|    | 2.2   | 2.3.  | Basic security requirements of chaos-based stream ciphers | 47 |

|    | 2.3.  | TRI   | NGs                                                       | 48 |

|    | 2.3   | 3.1.  | Statistical tests                                         | 48 |

|    | 2.3   | 3.2.  | Post-processing algorithms                                | 55 |

|    | 2.4.  | Cor   | nclusions                                                 | 57 |

|    | 2.5.  | Ref   | erences                                                   | 59 |

| 3. | Desi  | gn of | New Chaos-Based Stream Ciphers                            | 63 |

|    | 3.1.  | Sim   | ple maps: Logistic Map and Skew Tent Map                  | 64 |

|    | 3.2.  | Dig   | ital implementation of chaotic maps                       | 67 |

|    | 3.3.  | Usi   | ng a multi-encryption scheme based on DWRR                | 68 |

|    | 3.3   | 3.1.  | Implementation results                                    | 70 |

|    | 3.3   | 3.2.  | Security analysis                                         | 74 |

|    | 3.4.  | Cha   | anging the chaotic control parameter dynamically          | 75 |

|    | 3.4   | l.1.  | Fixed value of sequence partition s                       | 76 |

|    | 3.4   | l.2.  | Dynamically changed value of sequence partition s         |    |

|    | 3.4   | l.3.  | Implementation results                                    | 76 |

|    | 3.4   | .4.   | Security analysis                                 | 80 |

|----|-------|-------|---------------------------------------------------|----|

|    | 3.5.  | Usir  | ng an LFSR to perturb the chaotic orbits          | 83 |

|    | 3.5   | .1.   | Implementation results                            | 83 |

|    | 3.5   | .2.   | Security analysis                                 | 85 |

|    | 3.6.  | Fina  | al implementation                                 | 88 |

|    | 3.7.  | Cor   | nclusions                                         | 91 |

|    | 3.8.  | Ref   | erences                                           | 93 |

| 4. | Desig | n of  | New TRNGs                                         | 97 |

|    | 4.1.  | TRI   | NG based on a MEMS accelerometer                  | 98 |

|    | 4.1   | .1.   | Noise signal analysis                             | 98 |

|    | 4.1   | .2.   | Bitstream generation and post-processing          | 99 |

|    | 4.1   | .3.   | Mechanical response of the accelerometer 1        | 03 |

|    | 4.2.  | TRI   | NG based on Digital Nonlinear Oscillators1        |    |

|    | 4.2   | .1.   | Ring oscillator 1                                 | 05 |

|    | 4.2   | .2.   | Golić system 1                                    | 06 |

|    | 4.2   | .3.   | A novel class of DNOs                             | 07 |

|    | 4.2   | .4.   | Comparison among the three different structures 1 | 08 |

|    | 4.2   | .5.   | Post processing 1                                 | 12 |

|    | 4.3.  | Ana   | alysis and comparison of the proposed systems1    | 12 |

|    | 4.4.  | Cor   | nclusions1                                        | 13 |

|    | 4.5.  | Ref   | erences 1                                         | 15 |

| 5. | Appli | catic | ons for Ethernet Communications1                  | 19 |

|    | 5.1.  | Intro | oduction to the physical layer1                   | 20 |

|    | 5.2.  | 1 G   | b Optical Ethernet encryption1                    | 22 |

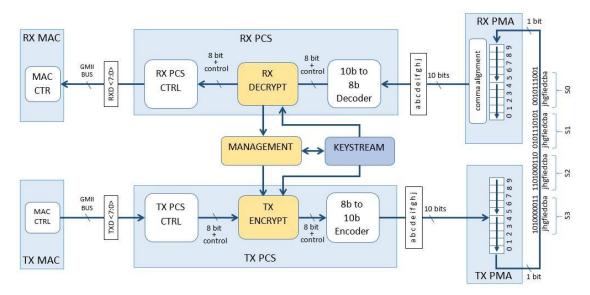

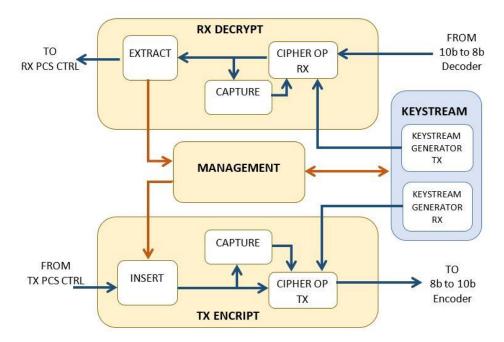

|    | 5.2   | .1.   | Overall structure of the encryption system 1      | 23 |

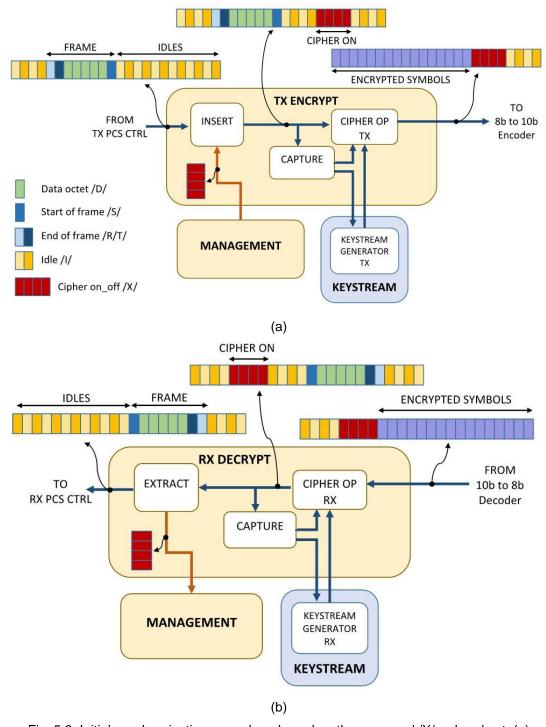

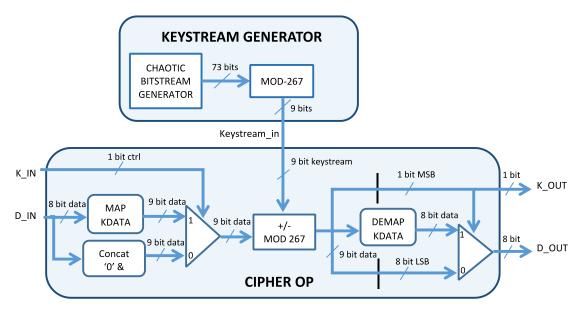

|    | 5.2   | .2.   | Encryption algorithm 1                            | 26 |

|    | 5.2   | .3.   | Implementation results1                           | 29 |

|    | 5.2   | .4.   | Security analysis1                                | 31 |

|    | 5.3.  | 10 (  | Gb Optical Ethernet encryption1                   | 33 |

|    | 5.3   | .1.   | Overall structure of the encryption system 1      | 35 |

|    | 5.3   | .2.   | Encryption algorithm1                             | 37 |

|    | 5.3   | .3.   | Implementation results1                           | 39 |

|    | 5.3   | .4.   | Security analysis1                                | 40 |

|    | 5.4.  | Cor   | nclusions1                                        | 41 |

|    | 5.5.  | Ref   | erences1                                          | 43 |

| 6. | Conc  | lusic | ons1                                              | 45 |

|    | 6 1   | Ger   | neral conclusions                                 | 45 |

| 6.2. Future research lines                                              | 148 |

|-------------------------------------------------------------------------|-----|

| Appendix A. NIST Statistical Test Suite                                 | 151 |

| Appendix B. TSMC 0.18 μm CMOS Logic or MS/RF, General Purpose 1.8V/3.3V | 155 |

| Appendix C. Xilinx 7 Series FPGAs                                       | 157 |

| Appendix D. List of own publications                                    | 159 |

### **List of Figures**

| Fig. | 1.1.  | Basic scheme of a communication process over an insecure channel                                                                                                                                                    | 4    |

|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. | 1.2.  | (a) CSK transmitter. (b) CSK receiver.                                                                                                                                                                              | 7    |

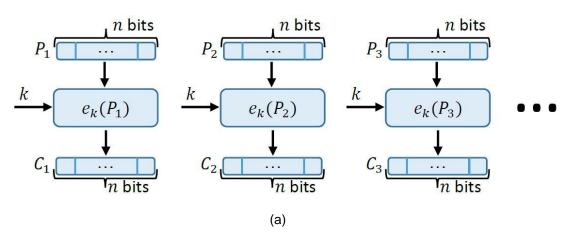

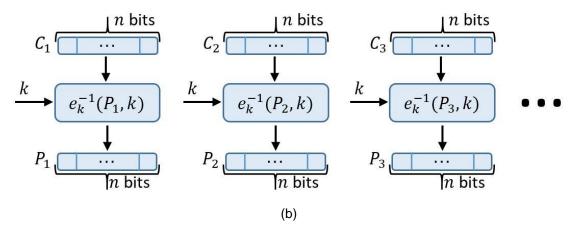

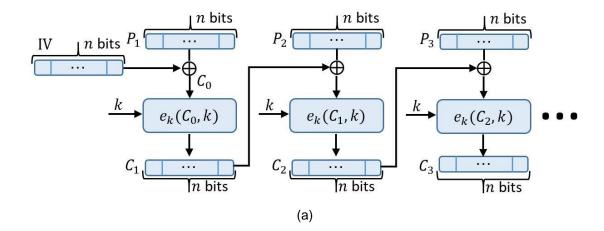

| Fig. | 2.1.  | Electronic Codebook (ECB) mode for (a) encryption and (b) decryption.                                                                                                                                               | . 28 |

| Fig. | 2.2.  | (a) Original Image. (b) Image encrypted with ECB. (c) Image encrypted with CBC.                                                                                                                                     | . 28 |

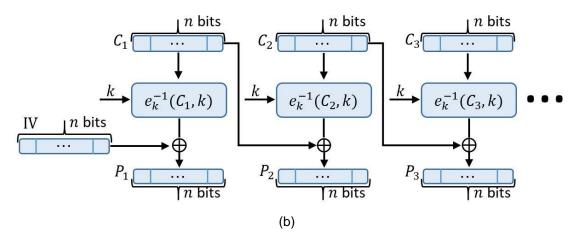

| Fig. | 2.3.  | Cipher Block Chaining (CBC) mode for (a) encryption and (b) decryption.                                                                                                                                             | . 29 |

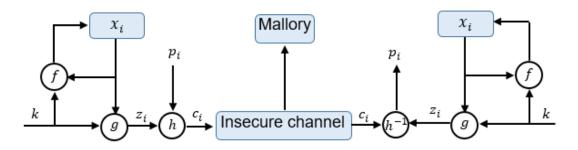

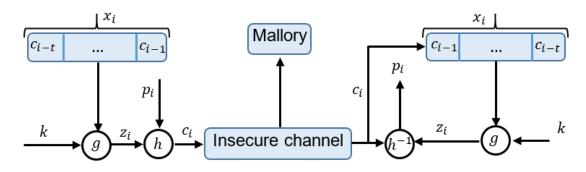

| Fig. | 2.4.  | Synchronous stream cipher                                                                                                                                                                                           | . 29 |

| Fig. | 2.5.  | A self-synchronizing stream cipher                                                                                                                                                                                  | . 31 |

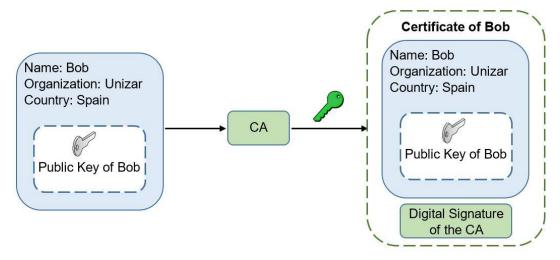

| Fig. | 2.6.  | Procedure of obtaining a public key certified by a CA. Bob sends its information and its public key to the CA. The CA verifies the identity and signs it with its private key                                       | . 39 |

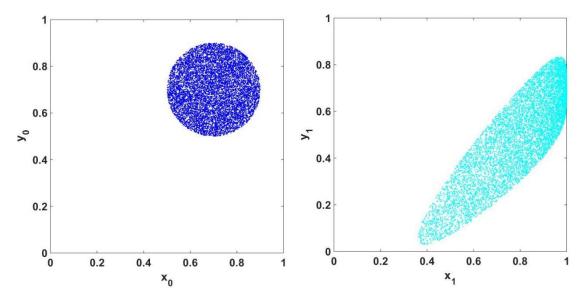

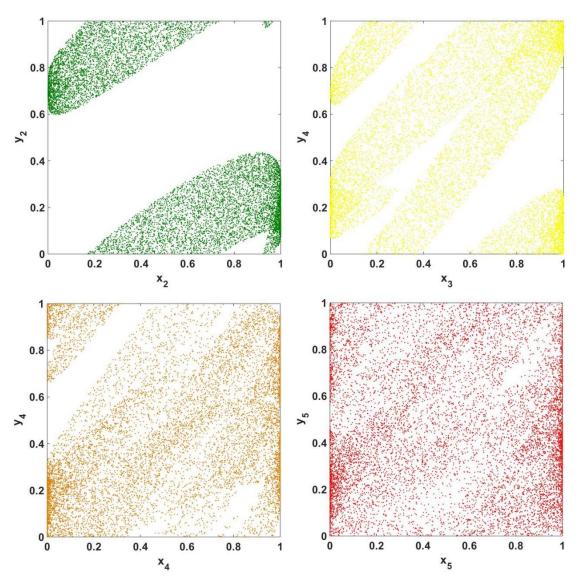

| Fig. | 2.7.  | Six consecutive iterations of a set of states $x, y$ passed through the logistic map                                                                                                                                | . 43 |

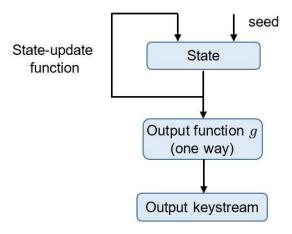

| Fig. | 2.8.  | Example of a secure way of generating a keystream                                                                                                                                                                   | . 46 |

| Fig. | 2.9.  | Example of a signal obtained from a physical noise source                                                                                                                                                           | . 49 |

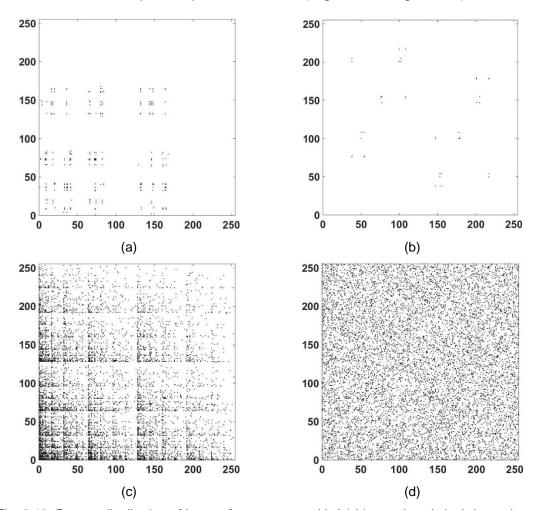

| Fig. | 2.10. | Pattern distribution of bytes of a sequence with (a) bias and statistical dependence, (b) no bias and statistical dependence, (c) bias and no statistical dependence and (d) no bias and no statistical dependence. | . 51 |

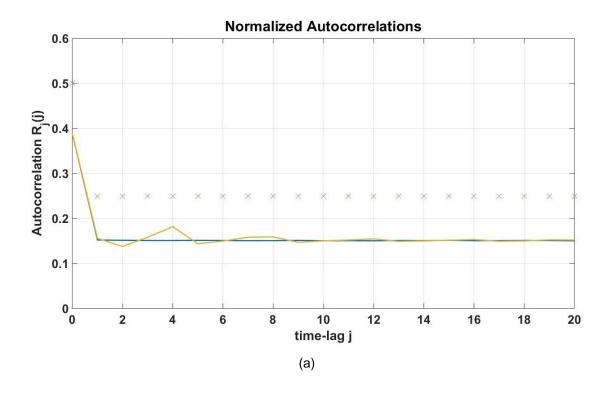

| Fig. | 2.11. | Correlations of (a) biased source, (b) unbiased source                                                                                                                                                              | . 53 |

| Fig. | 2.12. | ASRn of sequences generated by a TRNG with (a) bias and no statistical dependence, (b) no bias and statistical dependence                                                                                           | . 54 |

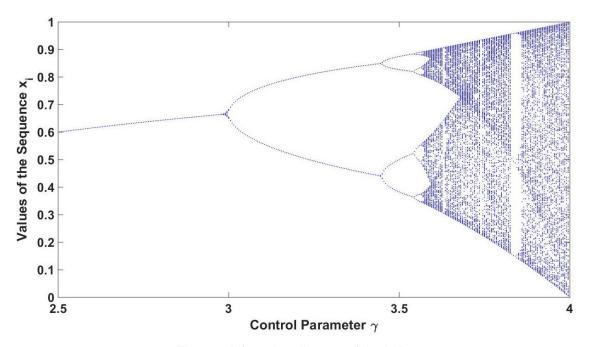

| Fig. | 3.1.  | Bifurcation diagram of the LM                                                                                                                                                                                       | . 65 |

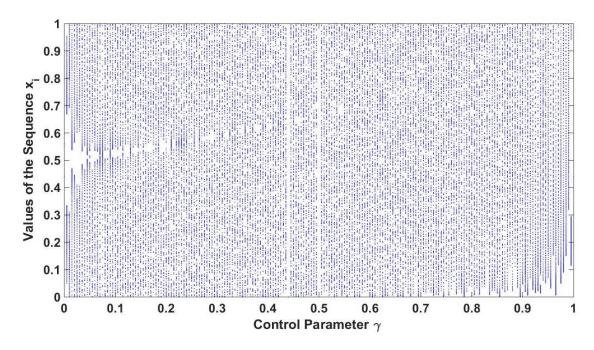

| Fig. | 3.2.  | Bifurcation diagram of the STM.                                                                                                                                                                                     | . 66 |

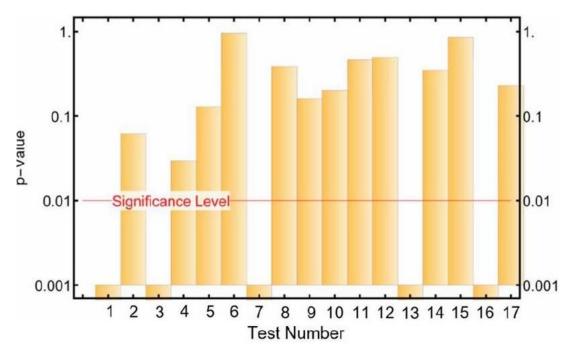

| Fig. | 3.3.  | NIST tests for a sequence generated by a 32-bit STM, extracting the LSB of each $xi$                                                                                                                                | . 68 |

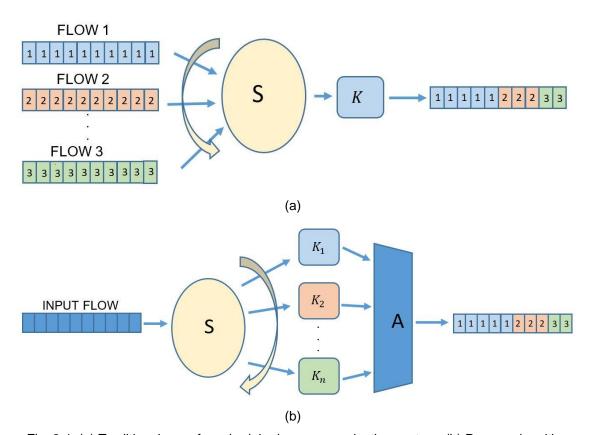

| Fig. | 3.4.  | (a) Traditional use of a scheduler in a communication system. (b) Proposed multi-encryption system with n cipher modules $(Ki)$ , a scheduler and an aggregator block.                                              | . 69 |

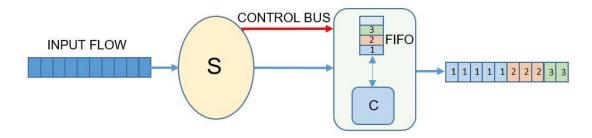

| Fig. | 3.5.  | Proposed dynamically configurable cipher structure when all the cipher modules use the same encryption algorithm                                                                                                    | . 71 |

| Fig. | 3.6.  | Block diagram of a Skew Tent Map generator                                                                                                                                                                          | . 71 |

| Fig. | 3.7.  | Proposed configurable cipher structure.                                                                                                                                                                             | . 72 |

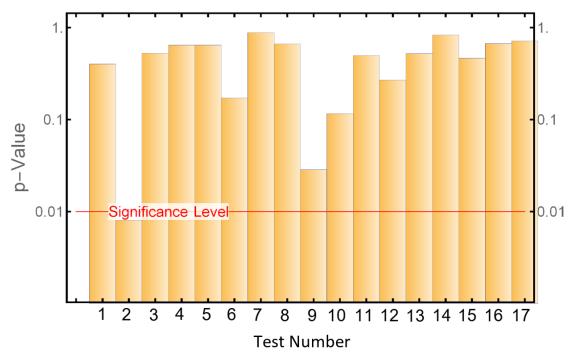

| Fig. | 3.8.  | NIST test results for a keystream generated by 8 STM modules combined with a DWRR algorithm                                                                                                                         | . 74 |

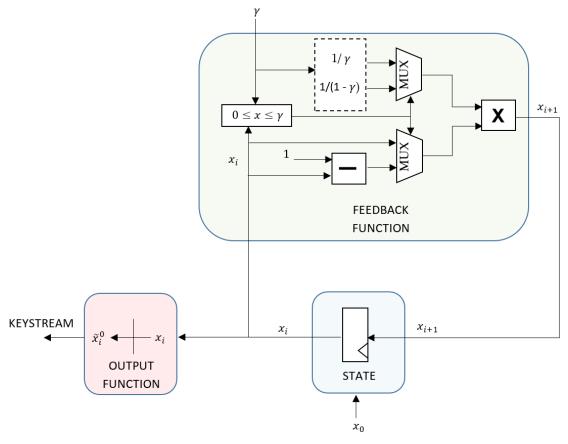

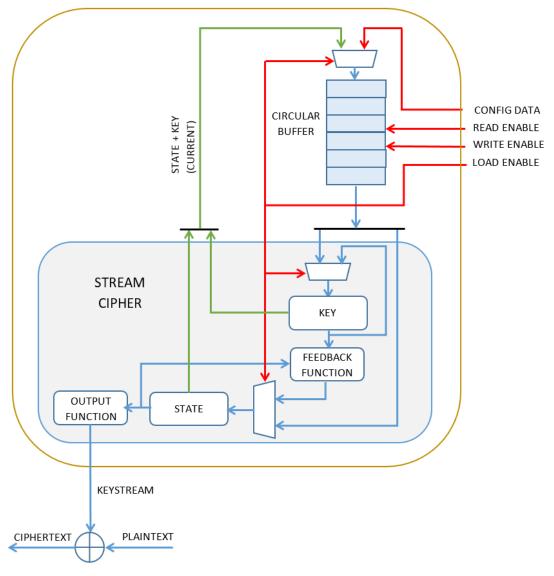

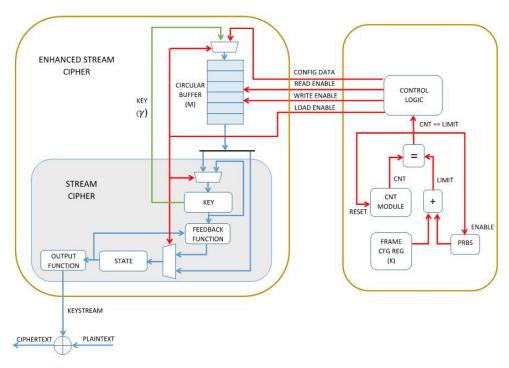

| Fig. 3.9.  | Scheme of the proposed enhanced stream cipher                                                                                                                                                     | . 77 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

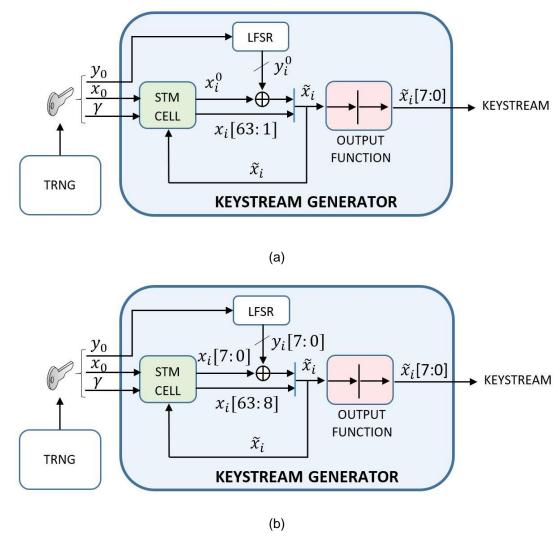

| Fig. 3.10. | Proposed 64-bit STM-LFSR stream cipher. Version 1 (a) and version 2 (b).                                                                                                                          | . 84 |

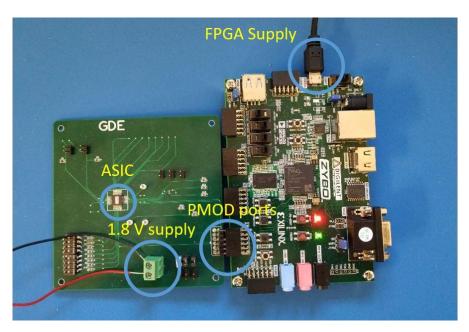

| Fig. 3.11. | PCB for the ASIC test setup connected to the Zybo board used to feed the clock and the reset signals. PMOD ports have been used for the connection.                                               | . 90 |

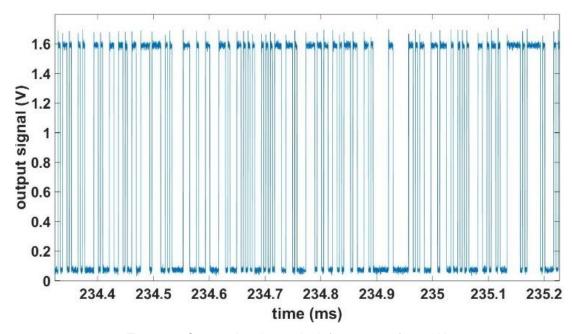

| Fig. 3.12. | Output signal at a clock frequency of 250 kHz.                                                                                                                                                    | . 91 |

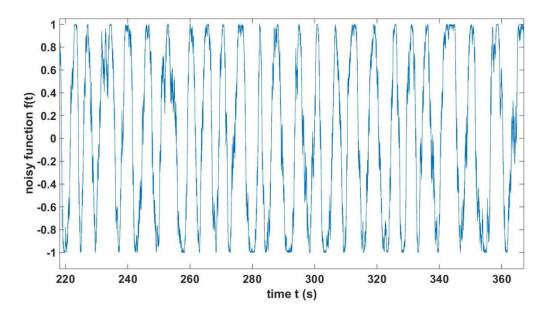

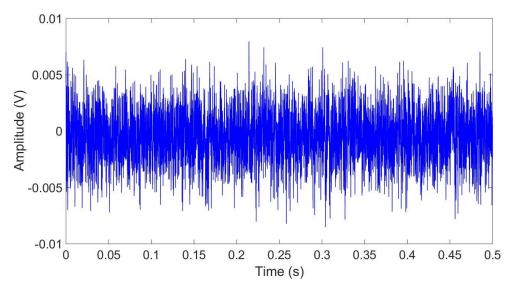

| Fig. 4.1.  | Sample random data signal generated by the accelerometer at rest, measured using a sampling frequency of 25 kHz                                                                                   | . 99 |

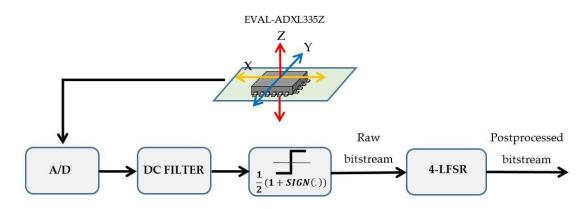

| Fig. 4.2.  | Conceptual block diagram of the processing performed                                                                                                                                              | . 99 |

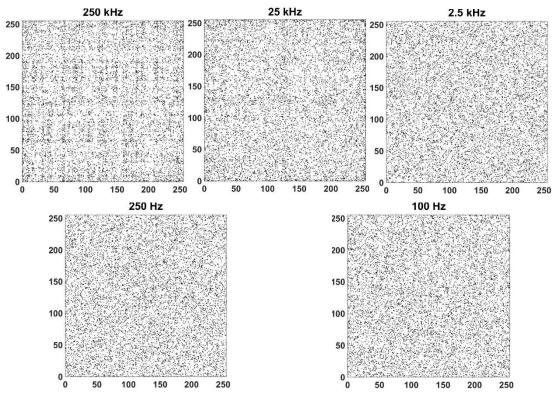

| Fig. 4.3.  | Pattern distribution of bytes at sampling frequencies of 250 kHz, 25 kHz, 250 Hz and 100 Hz                                                                                                       | 100  |

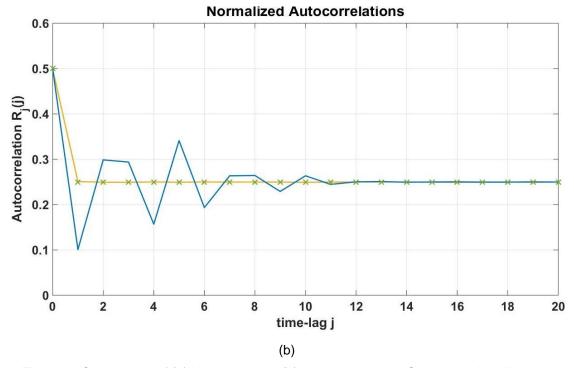

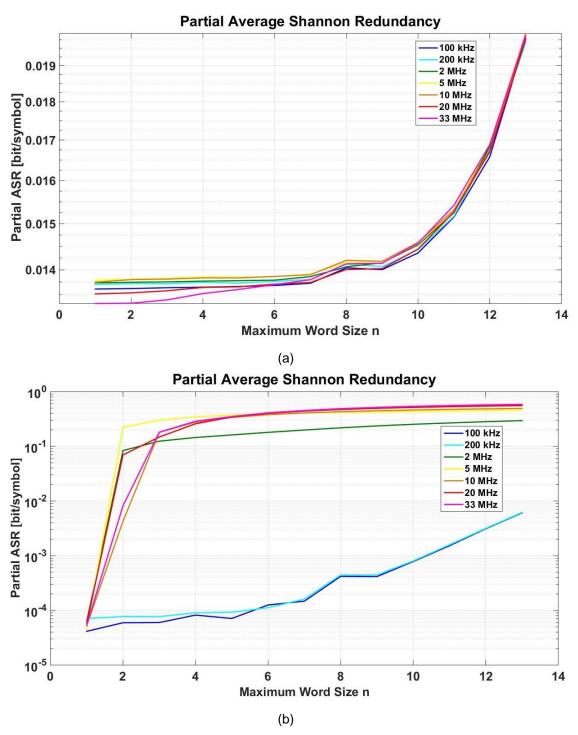

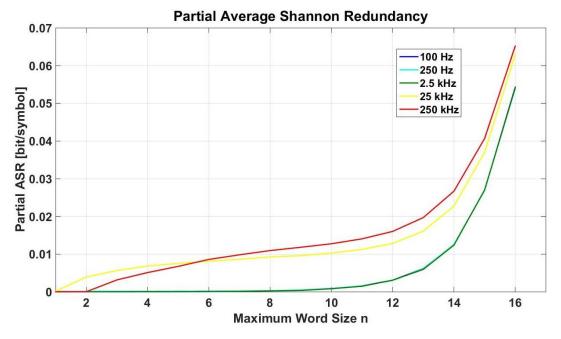

| Fig. 4.4.  | Partial Average Shannon Redundancy at all sampling frequencies. Lines at 2.5 kHz, 250 Hz and 100 Hz are overlapped                                                                                | 100  |

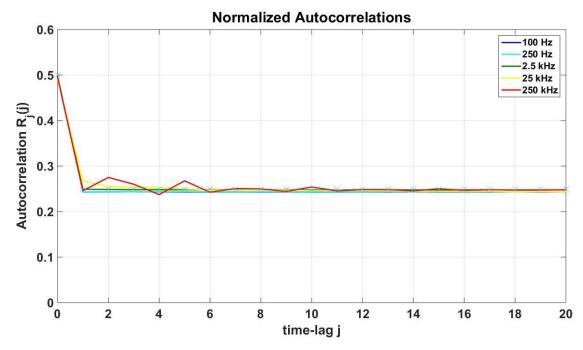

| Fig. 4.5.  | Autocorrelation coefficients at all sampling frequencies. Lines at 2.5 kHz, 250 Hz and 100 Hz are almost the same.                                                                                | 101  |

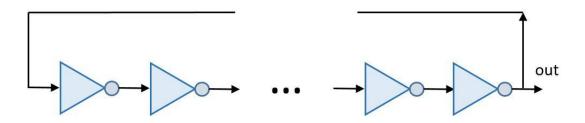

| Fig. 4.6.  | Scheme of a ring oscillator. The number of inverters must be odd.                                                                                                                                 | 105  |

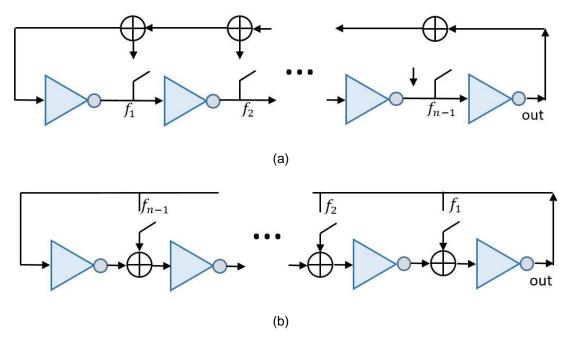

| Fig. 4.7.  | Scheme of a (a) Fibonacci ring oscillator and (b) Galois ring oscillator.                                                                                                                         | 107  |

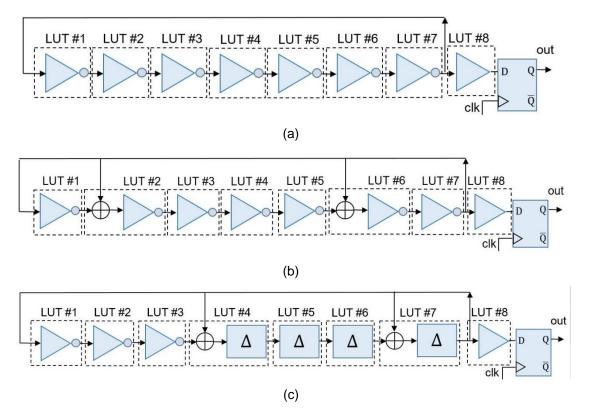

| Fig. 4.8.  | Scheme of the proposed novel class of DNOs. $\Delta$ symbol represents a delay operation (the implemented function is $x \rightarrow x$ ).                                                        | 108  |

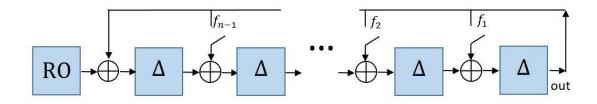

| Fig. 4.9.  | Implemented TRNGs. (a) Ring oscillator, (b) Golić's structure, (c) Proposed structure.                                                                                                            |      |

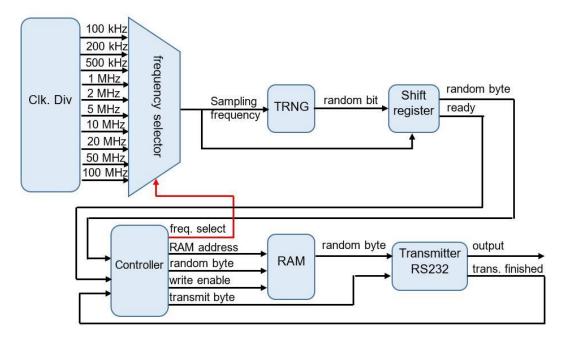

| Fig. 4.10. | Scheme of the measuring system.                                                                                                                                                                   | 109  |

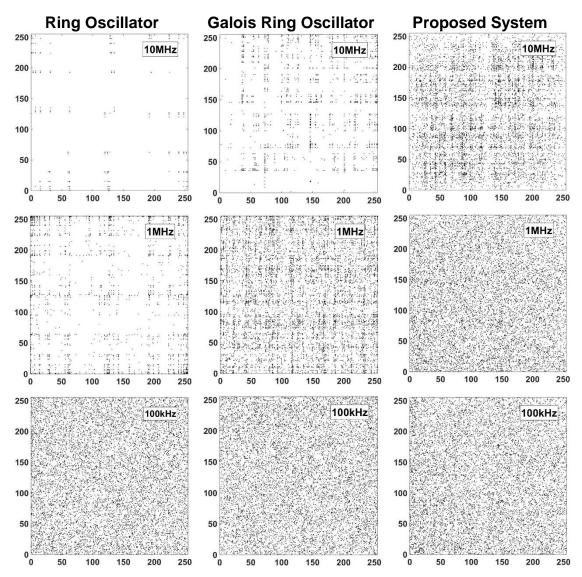

| Fig. 4.11. | Pattern distributions of successive generated bytes on the plane for the three DNOs considered in this work, for sampling frequencies of 10 MHz, 1MHz and 100 kHz.                                |      |

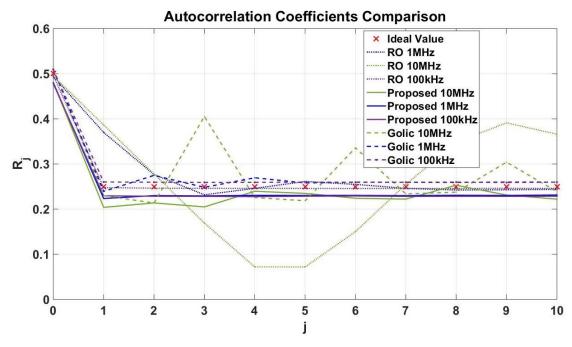

| Fig. 4.12. | Autocorrelation coefficients for the three DNOs considered in this work, for sampling frequencies of 10 MHz, 1MHz and 100 kHz                                                                     | 111  |

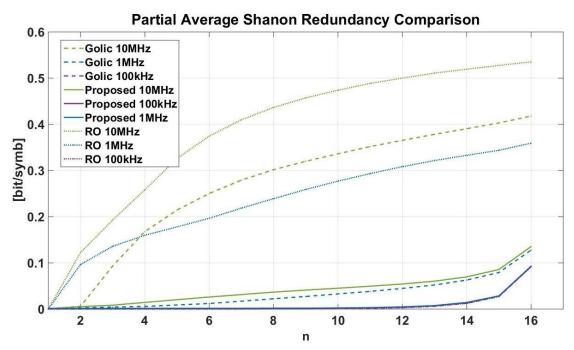

| Fig. 4.13. | Partial Average Shannon Redundancy for the three DNOs considered in this work, for sampling frequencies of 10 MHz, 1MHz and 100 kHz.                                                              | 111  |

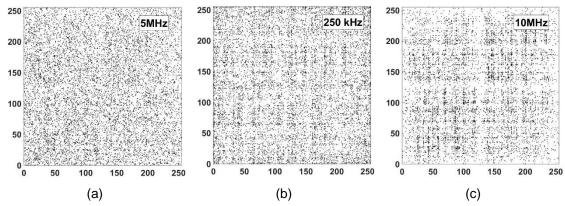

| Fig. 4.14. | Pattern distributions of successive generated bytes on the plane for (a) the proposed DNO-based TRNG at 5 MHz (b) the MEMS-based TRNG at 250 kHz and (c) the proposed DNO-based TRNG at a 10 MHz. | 113  |

| Fig. 5.1.  | PCS structure with the proposed encryption function PHYsec included.                                                                                                                              | 123  |

| Fig. 5.2.  | Encryption infrastructure for PHYsec function.                                                                                                                                                    | 124  |

| Fig. 5.3.  | Initial synchronization procedure, based on the proposed /X/ ordered set, (a) transmission, (b) reception                                                                                                                                                          | 25 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

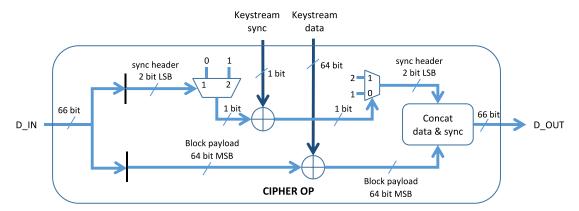

| Fig. 5.4.  | Stream cipher operation performed in CIPHER_OP module next to one of the keystream generators (RX or TX)                                                                                                                                                           | 27 |

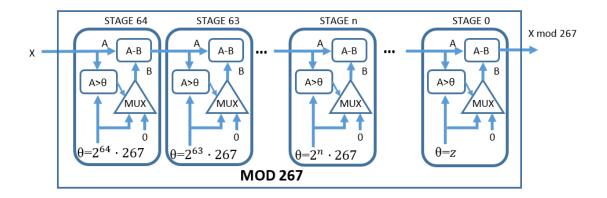

| Fig. 5.5.  | Modulo-267 hardware1                                                                                                                                                                                                                                               | 28 |

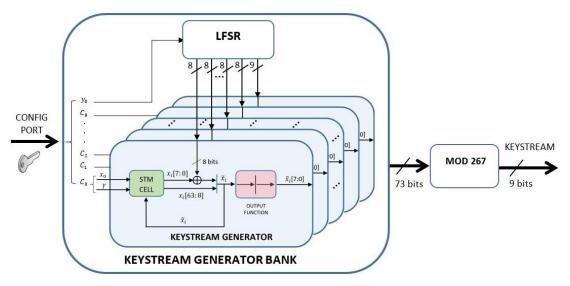

| Fig. 5.6.  | Keystream generator1                                                                                                                                                                                                                                               | 28 |

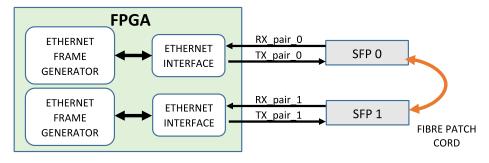

| Fig. 5.7.  | Test setup scheme                                                                                                                                                                                                                                                  | 29 |

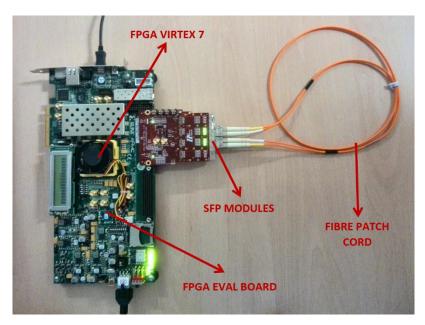

| Fig. 5.8.  | Test setup photo1                                                                                                                                                                                                                                                  | 30 |

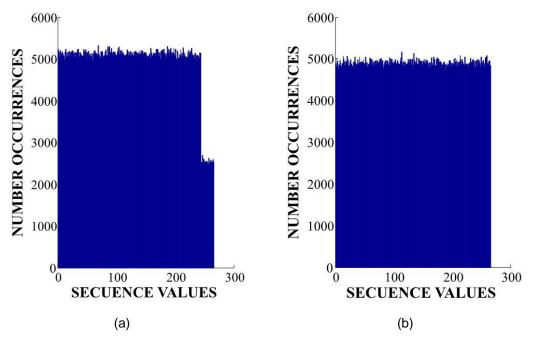

| Fig. 5.9.  | Histogram of the output keystream (without applying the NIST recommendation and (b) applying the NIST recommendation 1                                                                                                                                             | 32 |

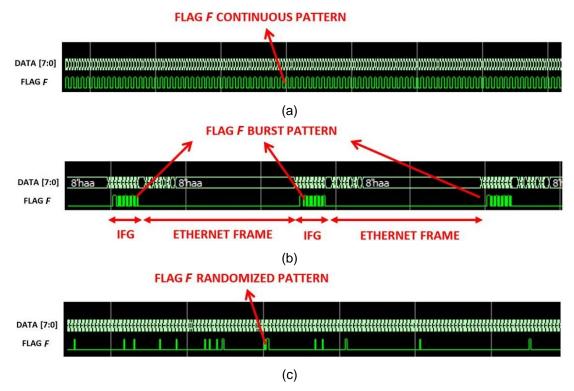

| Fig. 5.10. | (a) $F$ flag pattern before encryption when transmitting an Ethenet frame burst, (b) $F$ pattern before encryption when no Ethernet frame is transmitted and (c) $F$ pattern after encryption regardless of the transmission or nontransmission of Ethernet frames | 33 |

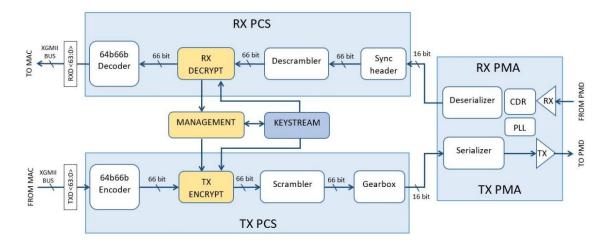

| Fig. 5.11. | PCS structure in 10GBase-R standard including the proposed encryption function                                                                                                                                                                                     | 35 |

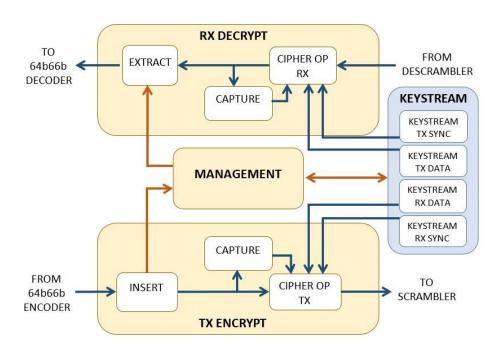

| Fig. 5.12. | Encryption infrastructure for 10G-PHYsec function1                                                                                                                                                                                                                 | 36 |

| Fig. 5.13. | Stream cipher operation 1                                                                                                                                                                                                                                          | 38 |

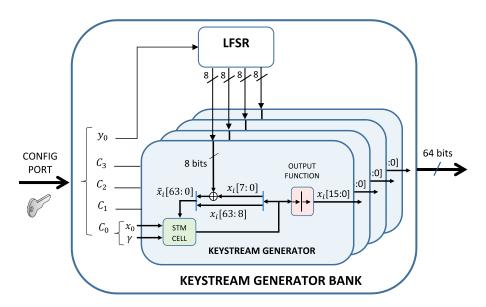

| Fig. 5.14. | Proposed keystream generator. The 189-bit key is the concatenation of the three parameters $y_0, x_0, \gamma$                                                                                                                                                      | 39 |

| Fig. 5.15. | 64-bit keystream generator for the 64-bit payload 1                                                                                                                                                                                                                | 39 |

| Fig. 5.16. | Synchronization headers and payloads after performing the proposed encryption                                                                                                                                                                                      | 41 |

### **List of Tables**

| Table 2.1. | Cryptographic primitives and their security goals                                                              |

|------------|----------------------------------------------------------------------------------------------------------------|

| Table 2.2. | Comparison between cryptographic and chaotic properties 45                                                     |

| Table 3.1. | Implementation results in a Virtex 7 FPGA73                                                                    |

| Table 3.2. | NIST test results for fixed values of the partition sequence s 78                                              |

| Table 3.3. | NIST test results for variable values of the partition sequence $s\dots 78$                                    |

| Table 3.4. | Implementation results of the STM and the LM with and without the proposed randomness-enhancement technique 81 |

| Table 3.5. | Implementation results of the 64-bit STM-LFSR                                                                  |

| Table 3.6. | Comparison among several implemented stream ciphers based on different strategies                              |

| Table 3.7. | Implementation results and comparison with other chaotic stream ciphers                                        |

| Table 3.8. | ASIC implementation of the 64-bit STM-LFSR algorithm 89                                                        |

| Table 3.9. | Comparison with other chaotic stream ciphers implemented in ASIC                                               |

| Table 4.1. | NIST test results for the raw bitstreams (106 bits) obtained at different sampling frequencies                 |

| Table 4.2. | NIST test results for the post-processed bitstreams (106 bits) obtained at different sampling frequencies      |

| Table 5.1. | FPGA resources used in the keystream generator submodules 129                                                  |

| Table 5.2. | 64b/66b block formats in 10GBase-R standard                                                                    |

| Table 5.3. | Link fault signaling ordered sets and new proposed ordered sets                                                |

| Table 5.4. | FPGA resources in the keystream generator submodules 140                                                       |

| Table B.1. | Technology characteristics                                                                                     |

| Table B.2. | 2-NAND gate information                                                                                        |

| Table C.1. | Mean features of Arty, Zybo and VC707 boards                                                                   |

#### **List of Symbols**

$a_i, a_i'$  Elements (bits) of a binary sequence

A, A' Binary sequence

ASE Average Shannon Entropy

ASE<sub>k</sub> Partial Average Shannon Entropy

$b_k$  kth byte

$b_k$  kth byte bit

$\beta$  Set of bits

c, c' Ciphertext

$c_i$  ith bit or symbol of the ciphertext

c(t) Analog masked signal (ciphertext)

$C, C_i$  Ciphertext of the size of an encryption block

$d_k$  Decryption function

*DC<sub>i</sub>* Deficit counter

$e_k$  Encryption function

f Feedback/state-update function

*F* Flag

g Extraction function

h Function that combines plaintext and ciphertext

h Hash function

k Key

K Cipher bank

l Integer number

m Transmitted message

*n* Integer number

p, p' Plaintext

$p_i$  ith bit or symbol of the plaintext

p(t) Analog message signal (plaintext)

$P, P_i$  Plaintext of the size of an encryption block

*Pr* Probability

$Q_i$  Quantum

r Integer number

$R_i$  Correlations

$s_i$  Element of the sequence partition

$\{s_i\}$  Sequence partition

$t_i$  ith time step

$\Delta T$  Sampling period

T Period of a sequence

U, V Metric space

$x_i$  State of the system at *i*th iteration/time step (one dimension)

$X_i$  State of the system at *i*th iteration/time step (multiple dimensions)

z Keystream

$z_i$  ith bit or symbol of the keystream

z(t) Analog masking signal

$\beta$  Set of bits

$\mathcal{C}$  Set of possible ciphertexts

$\delta$  Arbitrarily small distance

$\mathcal{E}$  Set of all encryption functions (rules)  $e_k: \mathcal{P} \to \mathcal{C}$

γ Control parameter

Γ Set of control parameters

$\kappa$  Key space size

- ${\mathcal K}$  Keyspace (set of possible keys)

- $\lambda$  Lyapunov exponent

- $\mathcal{P}$  Set of possible plaintexts

- $au_d$  Delay

#### **List of Acronyms**

AES Advanced Encryption Standard

APN Almost Perfect Nonlinear

ASE Average Shannon Entropy

ASIC Application-Specific Integrated Circuit

ASR Average Shannon Redundancy

BER Bit-Error-Rate

CA Certification Authority

CBC Cipher Block Chaining

CDR Clock and Data Recovery

CFB Cipher Feedback

CMAC Cipher-based Message Authentication Code

CMOS Complementary Metal-Oxide-Semiconductor

COOK Chaos On-Off Keying

CRC Cyclic Redundancy Check

CSK Chaos Shift Keying

CTR Counter

DCSK Differential Chaos Shift Keying

DES Data Encryption Standard

DNO Digital Nonlinear Oscillators

DWRR Deficit Weighted Round Robin

ECB Electronic Codebook

ENISA European Union Agency for Network and Information Security

FIFO First In First Out

FIPS Federal Information Processing Standard

FM-DCSK Frequency Modulated Differential Chaos Shift Keying

FPGA Field Programmable Gate Array

HDDCS Higher-Dimensional Chaotic Systems

HMAC Hash-Based Message Authentication Code

IEC International Electrotechnical Commission

IEEE Institute of Electrical and Electronics Engineers

IFG Interframe Gap

ISO International Organization for Standardization

IV Initialization Vector

LAN Local Area Networks

LFSR Linear Feedback Shift Register

LM Logistic Map

LSB Least Significant Bit

LUT Lookup Table

MA

MAC Message Authentication Code/Medium Access Control

MAN Metropolitan Area Networks

MEMS Microelectromechanical

MLE Maximal Lyapunov Exponent

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MSB Most Significant Bit

NAND Not-And

NIST National Institute of Standards and Technology

NLD Nonlinear Dynamic Forecasting

OFB Output Feedback

PCB Printed Circuit Board

PCS Physical Coding Sublayer

PHY Physical Layer

PLD Programmable Logic Device

PMA Physical Medium Attachment

PMD Physical Medium Dependent

PMOD Peripheral Module

PRBS Pseudorandom Binary Sequence

PRNG Pseudorandom Number Generator

RAM Random Access Memory

RNG Random Number Generator

RSA Rivest Shamir Adleman

RTL Register-Transfer Level

RX Receiver

SERDES Serializer/Deserializer

SFP Small Form-Factor Pluggable

SHA Secure Hash Algorithm

STM Skew Tent Map

TRNG True Random Number Generator

TSMC Taiwan Semiconductor Manufacturing Company

TX Transmitter

WAN Wide Area Networks

#### Introduction

- 1.1. Brief history of modern cryptography

- 1.2. Definition

- 1.3. State of the art and some research lines

- 1.3.1. Chaos-based ciphers

- 1.3.2. True Random Number Generators

- 1.3.3 Optical Gigabit Ethernet

- 1.4. Objectives

- 1.5. Thesis organization

- 1.6. References

This introduction starts with a brief overview of modern cryptography, pointing out some of the greatest achievements carried out in the last century in this field. In Section 1.2, a formal definition of cryptography as well as some basic concepts that will be used during the whole Thesis are presented. Section 1.3 will cover the state of the art as well as some important research lines. This section includes some of the issues that current cryptosystems present, and present some of the alternatives that have been proposed. Based on the study of the state of the art, the objectives will be presented in Section 1.4. Finally, the Thesis organization is presented in Section 1.5.

#### 1.1. Brief history of modern cryptography

Traditionally, cryptography has been intimately linked to military and diplomatic applications. The usage of cryptography outside of military circles, can be dated at the end of World War II. In those years, communications suffered several changes, and the encryption and decryption processes had to adapt to those changes. In that sense, it can be highlighted that the information started to be transmitted in chains of bits instead of words of a certain language. Furthermore, with the development of computers, there was a crescent number of people that needed to protect the transmitted information, as well as the stored data.

During the 1970's decade, cryptography suffered two major public advances. The first one was the development of the Data Encryption Standard (DES) and its publication as an official Federal Information Processing Standard (FIPS) for the United States [NAT77]. This algorithm, became the standard used by most of the commercial applications.

The second advance, was the proposal of a new key-exchange protocol by Whitfield Diffie and Martin Hellman [DIF76]. Up to that point, all the ciphers were symmetric key algorithms, which needed both transmitter and receiver to share the same secret key. This key had to be exchanged between the communicating parties in some secure way, such as face-to-face contact or using a secure channel. Thanks to Diffie and Hellman's work keys could be exchanged in a secure way and was the precursor of a new class of encryption algorithms: public-key algorithms. Some of the principal ones are Rivest Shamir Adleman (RSA) [RIV78] and ElGamal [ELG85].

One of the most important contributions of public-key cryptosystems were the digital signatures, whose first international standard (ISO/IEC 9796:1991, nowadays ISO/IEC 9796-2:2010) was adopted in 1991.

More recently, in 1997, the National Institute of Standards and Technology (NIST) announced the necessity of replacing the DES algorithm with a new one, "an unclassified publicly disclosed encryption algorithm capable of protecting sensitive government information well into the next century". After a selection process, Rijndael algorithm [DAE98] was chosen, becoming the Advanced

Encryption Standard (AES), which is the most commonly used encryption algorithm nowadays.

#### 1.2. Definition

The main objective of cryptography is to allow two people to communicate over an insecure channel but preventing an attacker from obtaining the information contended in the message. Often, in cryptography explanations, the person that sends the information is called Alice and the person who receives the message is called Bob. For the attacker, usually the names Mallory or Eve are used (in this Thesis, the name Mallory will be used). The information that Alice wants to send to Bob is called plaintext. To prevent Mallory from obtaining the information, Alice encrypts the plaintext using a key and sends it to Bob. The encrypted message is called ciphertext. This way, even if Mallory manages to eavesdrop the communication, she cannot determine what the plaintext was. However, Bob knows the key needed to decrypt the message and can reconstruct the plaintext.

A cryptosystem is the set of algorithms that allows Alice and Bob to exchange information confidentially. Usually, cryptosystems consist on 3 algorithms: one for key generation, one for encryption and one for decryption. Generally, the term *cipher* is used to refer to the pair of algorithms used for encryption and decryption while the term cryptosystem includes everything. However, in many cases it is common to use the terms "cipher" and "cryptosystem" [KAT14] interchangeably. These ideas can be described mathematically as follows.

A cryptosystem is a five-tuple  $(\mathcal{P}, \mathcal{C}, \mathcal{K}, \mathcal{E}, \mathcal{D})$ , where the following conditions are satisfied [STI05]:

- $\mathcal{P}$  is a finite set of possible plaintexts.

- C is a finite set of possible ciphertexts.

- $\mathcal{K}$ , the keyspace, is a finite set of possible keys.

- $\mathcal{E} = \{e_k : k \in \mathcal{K}\}$  is the set of all encryption functions (rules)  $e_k : \mathcal{P} \to \mathcal{C}$ .

- $\mathcal{D} = \{d_k : k \in \mathcal{K}\}$  is the set of all decryption functions (rules)  $d_k : \mathcal{C} \to \mathcal{P}$ .

- For each  $k \in \mathcal{K}$ , there is an encryption function  $e_k \in \mathcal{E}$  and a corresponding decryption function  $d_k \in \mathcal{D}$  such that  $d_k \big( e_k(p) \big) = p$  for any plaintext element  $p \in \mathcal{P}$ .

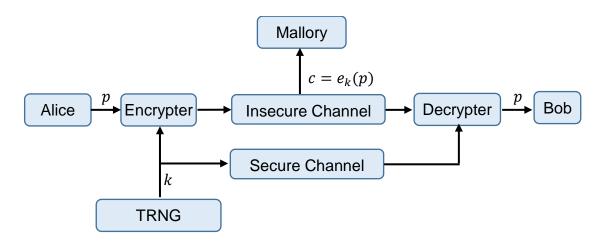

Fig. 1.1. Basic scheme of a communication process over an insecure channel.

With this cryptosystem definition, if Alice and Bob wanted to establish a communication over an insecure channel, the process would be as follows:

- Alice and Bob agree on the communication protocol (the set of encryption and decryption rules) and choose a random key k ∈ K. While the encryption and decryption rules can be known by anyone, the key should be kept in secret. Therefore, the key exchange should be done secretly, when they are not being observed by Mallory, or via a secure channel.

- When Alice wants to send a message to Bob over an insecure channel, Alice uses the encryption rule  $e_K$  corresponding to the chosen key k.

- Bob receives the ciphertext and decrypts it using the decryption rule  $d_k$  corresponding to the chosen key k.

This process has been illustrated in Fig. 1.1.

It is clear that the encryption function must be injective (one-to-one) since, otherwise, the decryption cannot be accomplished unambiguously, i.e.:  $p_1 \neq p_2 \Rightarrow e_k(p_1) \neq e_k(p_1) \ \forall k \in \mathcal{K}, p_1, p_2 \in \mathcal{P}.$

Apart from the encryption and decryption functions, there are other functions that can be used in security-related applications. Usually, the term cryptographic primitives is used to refer to any low-level algorithm used to build cryptographic protocols. This term includes the encryption and decryption algorithms, but there

are other important cryptographic functions that will be explained in the next chapter.

## 1.3. State of the art and research lines

During the last decades, there has been a great development in the field of cryptography, and many encryption algorithms as well as other cryptographic functions have been proposed.

However, despite this development, there has been a great interest in the last years in creating new cryptographic primitives or improving the current ones. Some of the reasons why it is necessary are the following:

- First, with the development of the communication technologies, the amount of information transmitted is constantly increasing. In this context, there are many applications that require to encrypt a high amount of data in real time or in a limited amount of time. A simple example, could be high-quality video encryption. Unfortunately, most of the current encryption algorithms are not able to encrypt high amounts of data at a high speed, while maintaining high security standards.

- Due to the development of computer technology, many algorithms that have traditionally been considered secure, can be now brute-forced in a reasonable amount of time. As an example, DES was first released with a key size of only 56 bits while, for current symmetric cryptographic algorithms, NIST recommends that they should have, at least, key sizes of 112 bits [BAR11]. On the other hand, there is currently a big amount of research in the area of quantum computing and it is expected that, at some point, large-scale quantum computers will be developed. It has been proven that, some of the current encryption algorithms such as RSA could be easily broken by quantum computers [SHO94a].

- Along with the development of cryptography, there has been a big development in the field of mathematical cryptanalysis. Therefore, new attacks are constantly being proposed and new vulnerabilities are constantly being found in some of the current encryption algorithms. Thus, new algorithms robust to all kind of attacks must be proposed to substitute the vulnerable ones. On the other hand, the security of some of the most

commonly used public-key encryption algorithms such as RSA or ElGamal, are based on the assumption that some mathematical problems such as factoring the product of two large primes or computing discrete logarithms are difficult to solve. However, there is no proof that, in the future, new algorithms capable of solving these problems fast (in a polynomial time) could be developed.

• Ideally, the keys used to encrypt data should be randomly generated to be as unpredictable as possible. Since the sequences generated by a Pseudo Random Number Generator (PRNG) are, in principle, predictable, they are potentially vulnerable to cryptanalysis. Therefore, the keys are usually generated using True Random Number Generators (TRNGs). Unfortunately, typically TRNGs offer slower bit generation rates than PRNGs and usually provide sequences with non-ideal statistical properties that need to be improved using some kind of post-processing techniques. A poor TRNG can compromise the security of a system even if it uses a secure encryption algorithm, as it has happened in some cases [BER13]. Finding a TRNG fast and with good statistical properties is an important research topic.

To sum up, it is clear that the field of cryptography is a hot research topic with numerous research lines. Since the field of cryptography is too extensive to be covered in a Thesis, this work has focused on three particular research lines: the design of new TRNGs, the design of new chaos-based synchronous stream ciphers for secure fast communications and, finally, the implementation of new cryptosystems suitable for Optical Gigabit Ethernet. These last cryptosystems should include both a TRNG for generating the keys and a chaos-based ciphering algorithm. Below, the antecedents and state of the art in the area of chaos-based cryptography, TRNGs and Optical Gigabit Ethernet encryption are presented.

#### 1.3.1. Chaos-based ciphers

The origin of synchronizable (analog) chaos-based cryptography starts in 1990, when Louis M. Pecora and Thomas L. Carroll proved that certain chaotic systems could synchronize with each other by linking them to common signals [PEC90]. Soon after this discovery, the usage of chaos for secure communication was proposed in numerous papers in the following years [CAR91, PEC92, CUO92a,

CUO92b, KOC92, PAR92, HAL93, WU93]. Some of the first proposed encryption techniques were:

- Chaotic masking [KOC92, WU93, CUO93a, CUO93b]. In this case, in the transmitter, the analog message signal, p(t), is added to a chaotic signal, z(t). The masked signal, c(t) = p(t) + z(t) is then sent to the receiver. As long as the message signal is much smaller than the chaotic signal  $(p(t) \ll z(t))$ , the receiver can generate an approximate synchronous chaotic signal,  $z'(t) \approx z(t)$ . When this synchronous chaotic signal is subtracted from the encrypted signal, the message signal is approximately recovered  $p'(t) = c(t) z'(t) \approx p(t)$ .

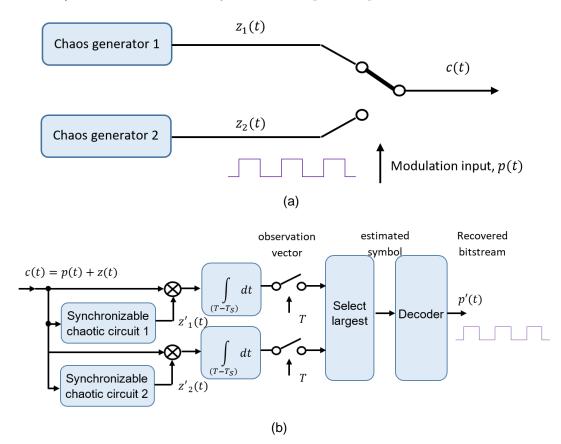

- Chaos shift keying (CSK) [DED93, PAR92]. In this case, each symbol is used to choose among several different chaotic circuits (Fig. 1.2a). The symbols are then detected at the receiver by using cascaded synchronizable chaotic circuits (Fig. 1.2b). Some other methods based on CSK that have been proposed are chaos on-off keying (COOK), differential chaos shift keying (DCSK) and frequency modulated differential chaos shift keying (FM-DCSK). A survey of these methods is presented in [KEN00].

Fig. 1.2. (a) CSK transmitter. (b) CSK receiver.

- Chaotic modulation [HAL93, CUO93a, YAN96]. In this case, the message signal, p(t), is used to modulate a parameter of the chaotic generator. In these systems, the receiver can exactly synchronize with the transmitter even when the message is incorporated.

- Chaos control methods [HAY93, HAY94]. The double scroll attractor in Chua's circuit consists of a random-like sequence of positive and negative peaks, each peak can be associated to a 1 or a 0. By using small control perturbations is it possible to cause the signal to follow an orbit whose binary sequence represents the information we wish to communicate. The same approach can be used with other chaotic systems [LAI99].

- Inverse system approach [FEL96, ZHO97b]. The information signal, p(t), controls a chaotic system, the transmitter. The output of the transmitter, c(t) is the input of a receiver which has to retrieve the information signal. In order to do this, the receiver has an input-output relation inverse to that of the transmitter.

Unfortunately, most of these methods were soon proved to be insecure and several methods to attack these systems were proposed. The first method that was proposed, nonlinear dynamic forecasting (NLD), was capable of extracting the carrier signal, z(t), for the chaotic masking and some chaotic modulation schemes [SHO94, SHO96, SHO97, SHO98, PAR01]. The message signal, p(t), could then trivially be recovered by removing the carrier signal, z(t), from the transmitted ciphertext signal, c(t).

Other methods could directly extract the message signal. Some of these methods were power spectral analysis [YAN98a], return map analysis [PER95, ZHO97], [YAN98b], correlation analysis [ZHO97], generalized synchronization technique [YAN98c] or short-time period [YAN95].

Finally, other methods were proposed to try to estimate the parameters needed for decryption [ZHO97, DED97, ZHO99, GED99].

Despite that many new synchronization-based cryptosystems were proposed in the following years to resist these attacks, new attacks were proposed and were able to successfully break most of these of systems [LI05, ALV06]. Due to this fact, most of the research (including the one in this Thesis) carried out nowadays focuses on digital chaos-based cryptosystems. In these systems, the chaotic system is digitized and implemented in hardware or software using a finite precision. Apart from the fact that they usually offer higher security than synchronization-based communication systems, these systems are easier to be implemented in current communication standards where the plaintext and ciphertext are expected to be digital signals and the most commonly used ciphering algorithms (RSA, RC4, Trivium, AES, ...) are all digital.

The first papers that proposed digital ciphers with dynamical systems were based on cellular automata and proposed in 1985 and 1987 [WOL85, GUA87]. However, the first paper usually cited as the first chaos-based cryptosystem was proposed by Robert A. J. Matthews in 1989 [MAT89]. After that paper, digital chaotic ciphers attracted the attention of many cryptographers and many papers were published in a short period of time, proposing new chaos-based PRNGs and stream ciphers [BER90, FOR91, BER91, BIA91], block ciphers [HAB90, HAB91, BIH91] and a few public-key ciphers [GUA87, DEL91, FRE93]. Almost at the same time, some papers [WHE91a, WHE91b, BIH91, ERD92, AND92] proved the vulnerabilities of most of those systems and, since then, the number of papers published in this area dropped.

Despite this fact, new digital chaos-based cryptosystems have been continuously being proposed and they have constantly improved in terms of encryption speed, power consumption, area and security. Although some chaotic algorithms have been proposed to be used in public-key cryptosystems (e.g. public-key ciphering based on Chebyshev polynomials [KOC05, KOC11]), this Thesis will focus on symmetric algorithms. The main reason is that the ultimate purpose of this Thesis is to implement in hardware a chaos-based cryptosystem suitable for Optical Gigabit Ethernet communications. For the same reason, this Thesis will only focus on hardware oriented algorithms so software oriented algorithms will not be considered.

In this area, several cryptosystems have been proposed and implemented in the last years, achieving promising results. As the chaotic encryption algorithms, most of them are based on the Logistic Map (LM) although some modifications are usually introduced for improving the security. Some of the best performing

algorithms based on the LM are [CHE10a, CHE10b, LI10, DAB11, DAB14, LI12, PAN13]. Other chaotic algorithms that have been used for designing secure cryptosystems are the Rényi Map [ADD07], the Lorenz's attractor [AZZ09], or higher-dimensional chaotic systems (HDDCS) [WAN16a]. In some cases, several chaotic algorithms are implemented and compared in the same work. This is the case of [DAB12] that compares the implementations of the Logistic Map and the Henon map or [GIA12] that compares implementations of the Bernoulli, Chebyshev, Tent and Cubic maps. Recently, chaotic iterations have been proposed to post-process linear pseudorandom number generators. Unfortunately, most of these algorithms are not fast enough for Gigabit Ethernet or have not passed a strict security analysis [BAK16, BAK18].

#### 1.3.2. True Random Number Generators

The best and most complete TRNGs solutions that have been proposed in literature (and on the market as well) so far, have been designed in ASICs [ACO17]. These generators, can be classified according to the source of randomness that it is used:

- Jitter oscillation [TAN14, YAN14, YAN16]. These generators use as a source

of randomness the deviation of an oscillator output from its true periodicity,

causing uncertainty in the low-high/high-low transition times.

- Electronic noise. In this case, the conventional method is to amplify noise with a high-gain and high-bandwidth amplifier followed by quantization. Some of the common noise sources are thermal noise [PET00], oxide trap noise [BRE06], SiN device noise [MAT08] or oxide breakdown noise [LIU11].

- Metastability [TOK07, MAT12]. When there are setup or hold time violations

in flip-flops they enter in a metastable state. These generators exploit the

unpredictability of the metastable states as a source of randomness.

- Finally, some generators use several entropy sources such as [BAE17] which

uses both jitter oscillation and metastability or [KUA14] that uses both

electronic noise and metastability.

Besides ASIC design, researchers are exploring the design of TRNGs in Programmable Logic Devices (PLDs). Compared to ASICs, PLD-TRNGs present a great advantage in terms of cost and versatility. Usually, the sources of randomness used by these systems are the same as the ones explained before: thermal noise [DAN09], metastability [DAN09, HAT12] or jitter oscillation [GOL06, SUN07, WOL08, WAN16b, LIU17]. Unfortunately, PLD-TRNGs still suffer from a lack of trust in information security communities, mainly due to some major cryptographic weaknesses found in solutions based on ring oscillators [BAU11, RAI15].

Finally, there is a possibility of using the noise generated by a sensor to generate random numbers. The main advantage of this approach is that it is possible to reuse a sensor (temperature, acceleration, pressure, ...) that it is already present in a device to use it as a TRNG. Although some studies about this possibility have been made [VOR11, WAL16] and some sensor-based TRNGs have been proposed [HON15, REV17], this approach has been relatively unexplored.

To sum up, although some quite complete TRNG solutions have been proposed for ASIC, in our opinion, the potential of PLDs or sensors for the design of reliable and efficient TRNGs is far from being completely explored. Due to the fact that, as explained above, both of these approaches present some advantages against ASIC-TRNGs, we have decided to focus our research on these kind of generators.

## 1.3.3. Optical Gigabit Ethernet

Ethernet has been expanded widely in local area networks (LAN), metropolitan area networks (MAN) and wide area networks (WAN). In recent decades, it has also been used in industrial control systems and critical infrastructures, replacing the traditional communication field buses [SAU11a, DEP08].

Optical Ethernet is widely used since it has some advantages over other wired methods such as higher bandwidth, less signal losses, and more immunity to electromagnetic interference. In addition, due to the fact that it does not emit radiation, it is safer than wireless systems that are more exposed to eavesdropping.

However, vulnerability and threat analysis in the physical layer (PHY) of optical systems is critical to guarantee secure communications [SKO16, FUR14]. At present, low-cost method for intercepting the optical signal through the fiber coupling devices and optoelectronic converters are available without the need to

perceptibly interfere in communications (splitting attack) [ZAF11]. To avoid or detect eavesdropping, encryption and intrusion detection systems have been proposed as solutions [SKO16].

In a layered communication model, encryption methods can be implemented at different communication levels, depending on the communication layer where confidentiality is needed. In the particular case of industrial Ethernet, solutions are usually proposed for network and transport layers (layers 3 and 4), such as IPsec or transport layer security protocols [SAU11b, BHA06]. Other solutions are proposed for the data link layer (layer 2), such as MACsec standard [LAZ17]. Although some protocols have been proposed for physical layer (layer 1) encryption in some telecommunication networks [ELK13, JI17, GUA16], as far as we know, no solutions have been proposed for optical Ethernet networks.

An encryption at a physical layer would bring some advantages against encryption at other layers such minimum latency and line rate (zero overhead). As an example, in IPsec, the inherent overhead introduced during encryption reduces the overall throughput between 20% and 90% of the maximum achievable [TRO05], so the improvement achieved by an encryption at a physical layer would be considerable. Finally, another advantage is that, by performing the encryption at a physical layer, obfuscation of customer data traffic patterns can be achieved. Since all of these advantages would result in an overall improvement over the state of the art, we intend to implement an encryption system that works at the physical layer (1000Base-X in the case of 1 Gb Ethernet and 10GBase-R in the case of 10 Gb Ethernet).

As far as we know, no chaos-based cryptosystems have been proposed as an Ethernet solution so far. On the other hand, both IPsec [SAU11b] and MACsec [LAZ17] protocols indicate the ciphering algorithm as well as the key exchange process, but they do not specify how the keys should be generated. Therefore, designing a chaos-based cryptosystem that includes a good TRNG used to generate the keys would undoubtedly be a significant contribution to the state of the art.

# 1.4. Objectives

It has been seen that most of the chaos-based cryptosystems proposed so far cannot achieve enough speed for Gigabit Ethernet communications, require a big amount of area for being implemented or lack of a strict security analysis. In addition to that, most of the encryption algorithms (both chaotic and non-chaotic) proposed so far do not address the key generation process. Ideally, a TRNG should be used for key generation. This generator should not only be capable of generating random sequences but it should also be fast and robust (i.e., it should always present good randomness properties regardless of any external interference). However, no complete solutions of TRNGs for PLDs or TRNGs based on the noise generated by sensors have been proposed so far, despite the advantages that these approaches would present against ASIC-TRNGs.

The scope of this work is the design of new secure physical layer encryption schemes suitable for Optical Gigabit Ethernet traffic. In order to design and implement a full communication scheme, we will design new secure chaos-based encryption algorithms as well as new TRNGs suitable for key generation. Finally, in order to encrypt at a physical layer, the algorithms will have to be adapted to preserve the data coding.

To design new TRNGs suitable for key generation, two possibilities will be studied. One consists of the usage of the noise generated by a Microelectromechanical (MEMS) accelerometer while, the other one will be based on the jitter generated by digital nonlinear oscillators (DNOs). For the last case, the proposed structures will be tested using an Arty board, which includes an Artix-7 Field Programmable Gate Array (FPGA). This board includes a set of ports that will be helpful for measuring the proposed structures. Xilinx Vivado Design Suite will be used for the implementations as well as to perform behavioral, post-synthesis and post-implementation simulations. Once implemented, to carry out the measurements, this FPGA will be connected to a computer using a LabVIEW platform.

The proposed encryption algorithms will be first implemented in a Virtex 7 FPGA, which is faster than the Artix 7 FPGA. Once the designs have been implemented and tested in the FPGA, we intend to select one of the encryption algorithms and

implement it in an Application-Specific Integrated Circuit (ASIC) using Cadence. A 0.18-μm CMOS process will be used for this implementation.

For the implementation of the Optical Gigabit Ethernet encryption system, we will also use the FPGA. In the setup for test, the FPGA will be connected to two Small From-Factor Pluggable (SFP+) modules capable of transmitting at a rate of 10.3125 Gbps at 850 nm over multimode fiber.

The concrete objectives of this work are summarized below:

- Study of the state of the art, including the encryption algorithms that are currently being used. This part will analyze the main issues that current standard encryption algorithms present and what solutions, if any, have been proposed. This study will help us to design new algorithms that overcome these issues.

- Proposal of new TRNGs suitable for key generation. We will explore two different possibilities: the usage of the noise generated by a MEMS accelerometer and the jitter generated by Digital Nonlinear Oscillators (DNOs). Both cases will be analyzed in detail by performing several statistical analyses at different sampling frequencies. If necessary, a simple post-processing algorithm will be proposed and implemented to improve the randomness of the generated sequences. Finally, the possible usage of these TRNGs as key generators will be discussed.

- Proposal of new encryption algorithms that are fast, secure and can be implemented using a small amount of resources. Among all the possibilities, this work will focus on cryptosystems based on chaotic since, thanks to their intrinsic properties such as ergodicity or random-like behavior, they can be a good alternative to classical encryption. To overcome some of the issues that appear when these systems are digitized, several strategies will be studied: using a multi-encryption scheme, changing the chaotic control parameters and perturbing the chaotic orbits.

- Implementation of the proposed encryption algorithms. For this purpose, a

Virtex 7 FPGA and Vivado Design Suite will be used. The different

implementations will be tested and compared, and some important aspects

such as their power consumption, area usage, throughput and security will

be discussed. One of these designs will be selected and implemented in an

ASIC using a 0.18-µm technology. Nevertheless, the solutions that we will look for will be generic so they will also be able to be implemented in other platforms or other technologies.

Finally, the proposed algorithms will be adapted and applied to Optical Gigabit Ethernet communications and will use one of the proposed TRNG to generate the keys. In particular, we intend to implement and analyze cryptosystems that work at the physical layer for 1 Gb and 10 Gb Ethernet communications. In order to perform the encryption at the physical layer, these algorithms will have to be adapted to preserve the data coding, 8b/10b in the case of 1 Gb Ethernet and 64b/66b in the case of 10 Gb Ethernet. In both cases, the cryptosystems will be implemented on a Virtex 7 FPGA and an experimental setup, including two SFP modules capable of transmitting at a rate up to 10.3125 Gbps at 850 nm over multimode fiber, will be design. With this setup we will check that the encryption systems work correctly and synchronously without harming data traffic or link establishment between Ethernet interfaces. Furthermore, we will check that the encryption is good (i.e., passes all the security tests) and that the data traffic pattern is hidden.

# 1.5. Thesis organization

This Thesis is divided into six chapters, of which the first one is devoted to this introduction and the last one presents the general conclusions of the work. The remaining four chapters form the core of the work that has been carried out during the whole Thesis.

Chapter 1 is an introduction that includes a brief overview of the field of cryptography, the antecedents of this work, its motivation and the main objectives.

Chapter 2 includes an extensive theoretical background with all the concepts and definitions needed to understand this work. First, it gives a general overview of the whole protocol needed to transmit information confidentially and explains some of the most important cryptographic primitives. Second, it explains the most important aspects of chaos based cryptography with its advantages and the current state of the art. Third, it explains the main aspects of TRNGs and their applications in cryptography. Finally, this chapter presents the randomness tests

and cryptanalysis that must be used to evaluate the security of both TRNGs and the encryption algorithms.

Chapter 3 explains the basic scheme of a chaos-based stream cipher, its advantages, and its drawbacks. Furthermore, it presents several chaos-based stream ciphers that have been proposed. All of them are based on simple known chaotic maps, such as the Skew Tent Map or the Logistic Map, but include some techniques to improve their security.

Chapter 4 presents two different TRNGs that have been proposed and analyzed in this work. The first one, uses the thermal noise produced by a MEMS accelerometer at rest while, the second one, consists on a family of TRNGs based on nonlinear oscillators that can be implemented in CPLs.

Chapter 5 applies the proposed encryption algorithms for Optical Gigabit Ethernet communications. Both 1 Gb and 10 Gb Ethernet communications systems are proposed, implemented and analyzed in this section.

Finally, in Chapter 6, the conclusions of the work carried out in this Thesis as well as possible future research lines are presented.

## 1.6. References

- [ADD07] T. Addabbo, M. Alioto, A. Fort, A. Pasini, S. Rocchi, V. Vignoli, "A Class of Maximum-Period Nonlinear Congruential Generators Derived from the Rènyi Chaotic Map," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 54, no. 4, pp. 816-828, 2007.

- [ALV06] G. Alvarez, S. Li, "Some Basic Cryptography Requirements for Chaos-Based Cryptosystems," *International Journal of Bifurcation and Chaos*, vol. 16, no. 8, pp. 2129-2151, 2006.

- [AND92] R. Anderson, "Letter to the Editor: Chaos and Random Numbers," *Cryptologia*, vol. 16, no. 3, pp. 226, 1992.

- [AZZ09] M. S. Azzaz, C. Tanougast, S. Sadoudi, A. Dandache, "Real-Time FPGA Implementation of Lorenz's Chaotic Generator for Ciphering Telecommunications," Proceedings of the IEEE International Circuits and Systems and Taisa Conference, 2009.

- [BAE17] S.-G. Bae, Y. Kim, Y. Park, C. Kim, "3-Gb/s High-Speed True Random Number Generator Using Common-Mode Operating Comparator and Sampling Uncertainty of D Flip-Flop," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 2, pp. 605-610, 2017.

- [BAK16] M. Bakiri, J.-F. Couchot, C. Guyeux, "FPGA Implementation of F2-Linear Pseudorandom Number Generators Based on Zynq MPSoc: A Chaotic Iterations Post Processing Case Study," Proceedings of the 13<sup>th</sup> International Joint Conference on e-Business and Telecommunications, pp. 302-309, 2016.

- [BAK18] M. Bakiri, C. Guyeux, J.-F. Couchot, L. Marangio, S. Galatolo, "A Hardware and Secure Pseudorandom Generator for Constrained Devices," *IEEE Transactions on Industrial Informatics*, vol. 14, no. 8, pp. 3754-3765, 2018.

- [BAR11] E. Barker, A. Roginsky, "Transitions: Recommendation for Transitioning the Use of Cryptographic Algorithms and Key Lengths," NIST Special Publication 800-131 A, 2011.

- [BAU11] M. Baudet, D. Lubiez, J. Micolod, A. Tassiaux, "On the Security of Oscillator-Based Random Number Generators," *Journal of Cryptology*, vol. 24, no. 2, pp. 398-425, 2011.

- [BER90] G. M. Bernstein, M. A. Lieberman, "Secure Random Number Generation Using Chaotic Circuits," *IEEE Transactions on Circuits and Systems*, vol. 37, no. 9, pp. 1157-1164, 1990.

- [BER91] G. M. Bernstein, M. A. Lieberman, "Method and Apparatus for Generating Secure Random Numbers Using Chaos," *US Patent No. 5008087*, 1991.

- [BER13] D. J. Bernstein, Y. Chang, C. Cheng, L. Chou, N. Heninger, T. Lange, N. van Someren, "Factoring RSA Keys from Certified Smart Cards: Coppersmith in the Wild," Advances in Cryptology – ASIACRYPT, pp. 341-360, 2013.

- [BHA06] D. V. Bhatt, S. Schulze, G. P. Hancke, "Secure Internet Access to Gateway Using Secure Socket Layer," *IEEE Transactions on Instrumentation and Measurements*, vol. 55, no.3, pp. 793-800, 2006.

- [BIA91] M. E. Bianco, D. A. Reed, "Encryption System Based on Chaos Theory," *US Patent No. 5048086*, 1991.

- [BIH91] T. Habutsu, Y. Nishio, I. Sasage, S. Mori, "Cryptanalysis of the Chaotic-Map Cryptosystem Suggested at EuroCrypt'91," Advances in Cryptology – EuroCrypt'91, pp. 532-534, 1991.

- [BRE06] R. Brederlow, R. Prakash, C. Paulus, R. Thewes, "A Low-Power True Random Number Generator Using Random Telegraph Noise of Single Oxide-Traps," Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC). Digest of Technical Papers, pp. 1666-1675, 2006.

- [CAR91] T. M. Carroll, L. M. Pecora, "Synchronizing Chaotic Circuits," *IEEE Transactions on Circuits and Systems*, vol. 38, pp. 453-456, 1991.

- [CHE10a] S.-L. Chen, T. Hwang, W.-W. Lin, "Randomness Enhancement Using Digitalized Modified Logistic Map," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 57, no. 12, pp. 996-1000, 2010.

- [CHE10b] S.-L. Chen, T. Hwang, S.-M. Chang, W.-W. Lin, "A Fast Digital Chaotic Generator for Secure Communication," *International Journal of Bifurcation and Chaos*, vol. 20, no. 12, pp. 3969-3987, 2010.

- [CUO92a] K. M. Cuomo, A. V. Oppenheim, S. H. Isabelle, "Spread Spectrum Modulation and Signal Masking Using Synchronized Chaotic Systems," MIT Technical Report, no. 570, 1992.

- [CUO92b] K. M. Cuomo, A. V. Oppenheim, "Synchronized Chaotic Circuits and Systems for Communications," MIT Technical Report, no. 575, 1992.

- [CUO93a] K. M. Cuomo, A. V. Oppenheim, "Circuit Implementation of Synchronized Chaos with Applications to Communications," *Physical Review Letters*, vol. 71, no. 1, pp. 65-68, 1993.

- [CUO93b] K. M. Cuomo, A. V. Oppenheim, S. H. Strogatz, "Synchronization of Lorenz-Based Chaotic Circuits with Applications to Communications," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 40, no. 10, pp. 626-633, 1993.

- [DAB11] P. Dabal, R. Pelka, "A Chaos-Based Pseudo-Random Bit Generator Implemented in FPGA Device," *Proceedings of the International Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS)*, pp. 151-154, 2011.

- [DAB12] P. Dabal, R. Pelka, "FPGA Implementation of Chaotic Pseudo-Random Bit Generators," Proceedings of the 19<sup>th</sup> International Conference on Mixed Design of Electronics Circuits and Systems (MIXDES), pp. 260-264, 2012.

- [DAB14] P. Dabal, R. Pelka, "A Study on Fast Pipelined Pseudo-Random Number Generator Based on Chaotic Logistic Map," *Proceedings of the 17<sup>th</sup> International Symposium on Design and Diagnostics of Electronic Circuits and Systems*, pp. 195-200, 2014.

- [DAE98] J. Daemen, V. Rijmen, "AES Proposal: Rijndael," AES submission, 1998.

- [DEL91] J.-P. Delahaye, "Les Automates (in French)," *Pour la Science (French Edition of Scientific American)*, pp. 126-134, 1991.

- [DEP08] A. Depari, P. Ferrari, A. Flammini, D. Marioli, A. Taroni, "A New Instrument for Real-Time Ethernet Performance Measurement," *IEEE Transactions on Instrumentation* and Measurements, vol. 57, no. 1, pp. 121-127, 2008.

- [DIF76] W. Diffie, M. E. Hellman, "New Directions in Cryptography," *IEEE Transactions on Information Theory*, vol. it-22, no. 6, pp. 644-654, 1976.

- [ELG85] T. ElGamal, "A Public Key Cryptosystem and a Signature Scheme Based on Discrete Logarithms," *IEEE Transactions on Information Theory*, vol. IT-31, pp. 469-472, 1985.

- [ELK13] D. Elkouss, J. Martinez-Mateo, A. Ciruana, V. Martin, "Secure Optical Networks Based on Quantum Key Distribution and Weakly Trusted Repeaters," *Journal of Optical Communications and Networking*, vol. 5, no. 4, pp. 316-328, 2013.

- [ERD92] D. Erdmann, S. Murphy, "Henon Stream Cipher," *Electronics Letters*, vol. 28, no. 9, pp. 893-895, 1992.

- [HON15] S. L. Hong, C. Liu, "Sensor-Based Random Number Generator Seeding," *IEEE Access*, vol. 3, pp. 562-568, 2015.

- [HWU93] F. Hwu, "The Interpolating Random Spline Cryptosystem and the Chaotic-Map Public-Key Cryptosystem," PhD thesis, Faculty of the Graduate School, University of Missouri, 1993.

- [FOR90] R. Forré, "The Hénon Attractor as a Keystream Generator," *Abstracts of Eurocrypt* 91, pp. 469-472, 1990.

- [FUR14] M. Furdek, N. Skorin-Kapov, S. Zsigmond, L. Wosinska, "Vulnerabilities and Security Issues in Optical Networks," *Proceedings of the International Conference on Transparent Optical Networks (ITCON)*, pp. 1-4, 2014.

- [GIA12] P. Giard, G. Kaddoum, F. Gagnon, C. Thibeault, "FPGA Implementation and Evaluation of Discrete-Time Chaotic Generators Circuits," *Proceedings of the IEEE* 38<sup>th</sup> Annual Conference of the Industrial Electronics Society (IECON 2012), pp. 3221-3224, 2012.

- [GOL06] J. D. Golíc, "New Methods for Digital Generation and Postprocessing of Random Data," *IEEE Transactions on Computers*, vol. 55, no. 10, pp. 1217-1229, 2006.

- [GUA87] P. Guan, "Cellular Automaton Public-Key Cryptosystem," *Complex Systems*, vol. 1, pp. 51-57, 1987.

- [GUA16] K. Guan, J. Kakande, J. Cho, "On Deploying Encryption Solutions to Provide Secure Transport-as-a-Service (TaaS) in Core and Metro Networks," *Proceedings of the European Conference on Optical Communications*, pp. 1-3, 2016.

- [HAB90] T. Habutsu, Y. Nishio, I. Sasage, S. Mori, "A Secret Key Cryptosystem Using a Chaotic Map," *Transactions IEICE*, vol. 73, no. 7, pp. 1041-1044, 1990.

- [HAB91] T. Habutsu, Y. Nishio, I. Sasage, S. Mori, "A Secret Key Cryptosystem by Iterating a Chaotic Map," *Advances in Cryptology EuroCrypt'91*, pp. 127-140, 1991.

- [HAL93] K. S. Halle, C. W. Wu, M. Itoh, L. O. Chua, "Spread Spectrum Communications through Modulation of Chaos," *International Journal of Bifurcation and Chaos*, vol. 3, no. 2, pp. 469-477, 1993.

- [JI17] J. Ji, G. Zhang, W. Li, L. Sun, K. Wang, M. Xu, "Performance Analysis of Physical-Layer Security in an OCDMA-Based Wiretap Channel," *Journal of Optical Communications and Networking.*, vol. 9, no. 10, pp. 813-818, 2017.

- [KAT14] J. Katz, Y. Lindell, "Introduction to Modern Cryptography," *Chapman & Hall/CRC*, 2014.

- [KEN00] M. P. Kennedy, G. Kolumbán, "Digital Communications Using Chaos," *Signal Processing*, vol. 80, no. 7, pp. 1307-1320, 2000.

- [KOC92] L. J. Kocarev, K. S. Halle, K. Eckert, L. O. Chua, U. Parlitz, "Experimental Demonstration of Secure Communications Via Chaotic Synchronization," International Journal of Bifurcation and Chaos, vol. 2, no. 3, pp. 709-713, 1992.

- [KOC05] L. J. Kocarev, J. Makraduli, "Public-Key Encryption Based on Chebyshev Polynomials," Circuits Systems Signal Processing, vol. 24, no. 5, pp. 497-517, 2005.

- [KOC11] L. J. Kocarev, S. Lian, "Chaos-Based Cryptography: Theory, Algorithms and Applications," *Springer-Verlag*, Berlin Heidelberg.

- [KUA14] T. K. Kuan, Y. H. Chiang, S. I. Liu, "A 0.43pJ7bit True Random Number Generator," 2014 IEEE Asian Solid-State Circuits Conference (A-SSCC), pp. 33-36, 2014.

- [LAI99] Y.-C. Lai, E. Bolt, C. Grebogi, "Communicating with Chaos Using Two-Dimensional Symbolic Dynamics," *Physics Letters A*, vol. 255, no. 1-2, pp. 75-81, 1999.

- [LAZ17] J. Lázaro, A. Astarloa, J. Araujo, N. Moreira, U. Bidarte, "MACsec Layer 2 Security in HSR Rings in Substation Automation Systems," *Energies*, vol. 10, no. 2, pp. 162, 2017.

- [LI05] S. Li, "Chaotic Cryptography (1): Analog Chaos-Based Secure Communications," Invited lecture, Department of Physics, Beijing Normal University, Beijing, China, 2005.

- [LI10] C.-Y. Li, T.-Y. Chang, C.-C. Huang, "A Nonlinear PRNG Using Digitized Logistic Map with Self-Reseeding Method," *Proceedings of the 2010 International Symposium on VLSI Design, Automation and Test*, 2010.

- [LI12] C.-Y. Li, Y.-H. Chen, T.-Y. Chang, L.-Y. Deng, K. To, "Period Extension and Randomness Enhancement Using High-Throughput Reseeding-Mixing PRNG," *IEEE Transactions on VLSI Systems*, vol. 20, no. 2, 2012.

- [LIU11] N. Liu, N. Pinckney, S. Hanson, D. Sylvester, D. Blaauw, "A True Random Number Generator Using Time-Dependent Dielectric Breakdown," *Proceedings of the 2011* Symposium on VLSI Circuits – Digest of Technical Papers, pp. 216-217, 2011.

- [LIU17] Y. Liu, R. C. C. Cheung, H. Wong, "A Bias-Bounded Digital True Random Number Generator Architecture," *IEEE Transactions on Circuits and Systems I*, vol. 64, no. 1, pp. 133-144, 2017.

- [MAT89] R. A. J. Matthews, "On the Derivation of a "Chaotic" Encryption Algorithm," *Cryptologia*, vol. 13, no. 1, pp. 29-41, 1989.

- [MAT08] M. Matsumoto, S. Yasuda, R. Ohba, K. Ikegami, T. Tanamoto, S. Fujita, "1200 μm2 Physical Random-Number Generators Based on SiN MOSFET for Secure Smart-Card Application," *Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC). Digest of Technical Papers*, pp. 414-624, 2008.

- [MAT08] S. K. Matthew et al., "2.4 Gbps 7mW All-Digital PVT-Variation Tolerant True Random Number Generator for 45 nm CMOS High-Performance Microprocessors," IEEE Journal of Solid-State Circuits, vol. 47, no. 11, pp. 2807-2821, 2012.

- [NAT77] National Bureau of Standards (U.S), Federal Information Processing Standards Publication 46, "Data Encryption Standard (DES)," 1977.

- [PAN13] A. Pande, J. A. Zambreno, "A Chaotic Encryption Scheme for Real-Time Embedded Systems: Design and Implementation," *Telecommunication Systems*, vol. 52, no. 2, pp. 515-561, 2013.

- [PAR92] U. Parlitz, L. O. Chua, L. J. Kocarev, K. S. Halle, A. Shang, "Transmission of Digital Signals by Chaotic Synchronization," *International Journal of Bifurcation and Chaos*, vol. 2, no. 4, pp. 973-977, 1992.

- [PAR01] A. T. Parler, K. M. Short, "Reconstructing the Keystream from a Chaotic Encryption Scheme," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 48, no. 5, pp. 624-630, 2001.

- [PEC90] L. Pecora, T. Carroll, "Synchronization in Chaotic Systems," *Physical Review Letters*, vol. 64, no. 8, pp. 821-825, 1990.

- [PEC92] L. M. Pecora, T. M. Carroll, "Synchronized Chaotic Signals and Systems," Proceedings of the 1992 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP-92), pp. 137-140, 1992.

- [PET00] C. S. Petrie, J. A. Connelly, "A Noise-Based IC Random Number Generator for Applications in Cryptography," *IEEE Transactions on Circuits and Systems I:* Express Briefs, vol. 47, no. 5, pp. 615-621, 2000.

- [RAI15] M. Raitza, M. Vogt, C. Hochberger, T. Pionteck, "Raw 2014: Random Number Generators on FPGAs," ACM Transactions on Reconfigurable Technology and Systems, vol. 9, no. 2, pp. 15:1-15:21, 2015.

- [REV17] G. Revadigar, C. Javali, W. Xu, A. V. Vasilakos, W. Hu, S. Jha, "Accelerometer and Fuzzy Vault-Based Secure Group Key Generation and Sharing Protocol for Smart Wearables," *IEEE Transactions on Information Forensics and Security*, vol. 12, no. 10, pp. 2467-2482, 2017.

- [RIV78] R. Rivest, A. Shamir, L. Adleman, "A Method for Obtaining Digital Signatures and Public Key Cryptosystems," *Communications of the ACM*, vol. 21, no. 2, pp. 120-126, 1978.

- [SAU11a] T. Sauter, S. Soucek, W. Kastner, D. Dietrich, "The Evolution of Factory and Building Automation," *IEEE Industrial Electronics Magazine*, vol. 5, no.3, pp. 35-48, 2011.

- [SAU11b] T. Sauter, M. Lobashov, "How to Access Factory Floor Information Using Internet Technologies and Gateways," *IEEE Tranactions on Industrial Informatics*, vol. 7, no.4, pp. 699-712, 2011.

- [SHO94a] P. W. Shor, "Algorithms for Quantum Computation: Discrete Logarithms and Factoring," *Proceedings of the 35<sup>th</sup> Annual Symposium On Foundations of Computer Science*, pp. 124-134, 1994.

- [SHO94b] K. M. Short, "Steps Toward Unmasking Secure Communications," *International Journal of Bifurcaction and Chaos*, vol. 4, no. 4, pp. 959-977, 1994.