**Universidad**

Zaragoza

## Trabajo Fin de Máster

### MEMORIA

Control digital de un convertidor *Buck* mediante

realimentación lineal del estado

Máster en Ingeniería Electrónica

Autor

Roberto Velázquez Millán

Director/es

Luis Ángel Barragán Pérez

Carlos Sagüés Blázquez

Escuela de Ingeniería y Arquitectura

Universidad de Zaragoza

2013

|                                             |                                                                                         |                |

|---------------------------------------------|-----------------------------------------------------------------------------------------|----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 1 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                |

## CONTROL DIGITAL DE UN CONVERTIDOR *BUCK* MEDIANTE REALIMENTACIÓN LINEAL DEL ESTADO

### RESUMEN

Aunque el control de un convertidor CC-CC *Buck* está hoy en día ampliamente desarrollado, se considera de interés académico el estudio de un control más avanzado del mencionado convertidor mediante realimentación lineal del estado. De esta forma se profundiza en los conocimientos de control y electrónica de potencia a la vez que se ahonda en el dominio de herramientas de simulación y análisis.

En este Trabajo Fin de Máster se presenta el control digital por realimentación del estado de un convertidor *Buck*. La implementación se realiza en coma fija sobre una FPGA. Los fundamentos básicos se obtienen de las asignaturas “Control de etapas electrónicas de potencia” y “Modelado de convertidores electrónicos de potencia” del Máster de Ingeniería Electrónica y de la asignatura “Ingeniería de control” optativa de 5º curso Ingeniería Industrial. Se usan referencias específicas que se detallan en la memoria para conseguir de forma ordenada el objetivo planteado.

Los aspectos más destacados se resumen de la siguiente forma:

Estudio del estado del arte en cuanto a control de convertidores electrónicos de potencia consultando publicaciones científicas y libros.

Se obtiene el modelo dinámico del convertidor *Buck*. Este modelo se utiliza en el planteamiento del esquema de control. Además se realiza un modelo conmutado del convertidor que se utiliza en las simulaciones.

Se realiza el cálculo de la ley de control y se plantea el esquema de control. Las simulaciones en bucle cerrado permiten obtener conclusiones que llevan a simplificaciones y decisiones útiles a la hora de implementar el control digital en una FPGA.

Se compara mediante simulación el control del convertidor *Buck* mediante realimentación lineal del estado y un control modo tensión, se señalan ventajas e inconvenientes de uno y otro. Adicionalmente se simula un control mediante realimentación del estado basado en un esquema con observador, comparándose con el control por realimentación del estado formal. Se simula en coma fija la implementación que se ha decidido realizar en VHDL sintetizable en la FPGA.

Se desarrolla un programa de testbench en VHDL no sintetizable para simular el control digital. Se simula el control en coma fija por realimentación lineal del estado en VHDL sintetizable y se implementa el control digital en la FPGA. Se desarrolla un interfaz de usuario acorde a la tarjeta de evaluación de la FPGA que se dispone.

Se realizan mediciones y toma de datos experimentales. Los datos tomados se comparan con los obtenidos en simulación.

Como posible continuación del trabajo, se analizan las razones por las que sería de interés la implementación en coma fija en una FPGA de un control por realimentación del estado basado en un esquema con observador.

|                                             |                                                                                         |                |

|---------------------------------------------|-----------------------------------------------------------------------------------------|----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 2 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                |

## INDICE

|                                                    |    |

|----------------------------------------------------|----|

| <b>1 Introducción</b> .....                        | 4  |

| 1.1 Antecedentes.....                              | 4  |

| 1.2 Objetivos y alcance.....                       | 5  |

| 1.3 Organización de la memoria.....                | 6  |

| <b>2 Modelado del convertidor</b> .....            | 7  |

| 2.1 Convertidor Buck .....                         | 7  |

| 2.2 Modelo de estado de pequeña señal .....        | 8  |

| 2.2.1 Modelo promediado de gran señal .....        | 8  |

| 2.2.2 Modelo de pequeña señal .....                | 9  |

| 2.3 Modelo de estado conmutado .....               | 10 |

| <b>3 Diseño del control digital</b> .....          | 13 |

| 3.1 Esquema de integradores .....                  | 13 |

| 3.2 Simulación en números reales .....             | 14 |

| 3.2.1 Instante de muestreo .....                   | 14 |

| 3.2.2 Aproximación del estado por la salida .....  | 15 |

| 3.2.3 Efecto de antiwindup .....                   | 16 |

| 3.2.4 Comparación con control modo tensión.....    | 17 |

| 3.2.5 Esquema de control con observador .....      | 19 |

| 3.2.6 Comparativa por número de productos .....    | 21 |

| 3.3 Simulación en coma fija .....                  | 21 |

| 3.3.1 Simplificaciones adoptadas .....             | 21 |

| 3.3.2 Formatos numéricos .....                     | 22 |

| <b>4 Implementación en FPGA</b> .....              | 25 |

| 4.1 Testbench en VHDL.....                         | 25 |

| 4.1.1 Modelado del convertidor conmutado .....     | 25 |

| 4.1.2 Modelado del conversor ADC.....              | 25 |

| 4.1.3 Modelado del modulador.....                  | 26 |

| 4.1.4 Modelado del control en números reales ..... | 27 |

| 4.1.5 Simulación en números reales .....           | 27 |

| 4.2 Descripción en VHDL sintetizable.....          | 27 |

|                                             |                                                                                         |                |

|---------------------------------------------|-----------------------------------------------------------------------------------------|----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 3 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                |

|                                                                   |    |

|-------------------------------------------------------------------|----|

| 4.2.1 Control del conversor ADC .....                             | 28 |

| 4.2.2 Modulador .....                                             | 28 |

| 4.2.3 Control y formatos numéricos .....                          | 29 |

| 4.2.4 Interfaz de usuario .....                                   | 31 |

| 4.2.5 Simulación en coma fija .....                               | 32 |

| 4.2.6 Implementación en la FPGA .....                             | 32 |

| <b>5 Resultados experimentales</b> .....                          | 33 |

| 5.1 Banco de pruebas utilizado .....                              | 33 |

| 5.2 Resultados y comparación con simulación .....                 | 33 |

| <b>6 Conclusiones y líneas de trabajo futuro</b> .....            | 38 |

| 6.1 Conclusiones .....                                            | 38 |

| 6.2 Líneas de trabajo futuro .....                                | 38 |

| <b>Anexo A1: Modelo de gran señal</b> .....                       | 42 |

| A1.1 Notación de variables .....                                  | 42 |

| A1.2 Datos .....                                                  | 42 |

| A1.3 Modelo de estado durante $t_{ON}$ .....                      | 43 |

| A1.4 Modelo de estado durante $t_{OFF}$ .....                     | 44 |

| A1.5 Modelo de estado durante $\Delta$ .....                      | 45 |

| A1.6 Modelo promediado de gran señal .....                        | 46 |

| <b>Anexo A2: Modelo de pequeña señal</b> .....                    | 48 |

| A2.1 Introducción de una perturbación $p(t)$ .....                | 48 |

| A2.2 Linealización de la ecuación de estado .....                 | 48 |

| A2.3 Linealización de la ecuación de salida .....                 | 50 |

| A2.4 Modelo de estado de pequeña señal del convertidor Buck ..... | 50 |

| <b>Anexo A3: Contenido CD anexo</b> .....                         | 51 |

| A3.1 Código Matlab .....                                          | 51 |

| A3.2 VHDL no sintetizable .....                                   | 51 |

| A3.3 VHDL sintetizable .....                                      | 51 |

|                                             |                                                                                         |                |

|---------------------------------------------|-----------------------------------------------------------------------------------------|----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 4 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                |

## 1 INTRODUCCIÓN

El modelado y control de los convertidores electrónicos de potencia de continua a continua CC está ampliamente desarrollado, entre estos convertidores se encuentra el *Buck* objeto de este proyecto. Para la implementación de un control mediante realimentación lineal del estado en coma fija en una FPGA, resulta a la vez una motivación y una exigencia la conjugación de conocimientos por una parte de control y por otra de electrónica. En el desarrollo de este proyecto se realizan diversas simulaciones comparándose resultados, en el análisis de estas simulaciones se profundiza en lo predicho por la teoría de control y la teoría de electrónica de potencia. De la misma manera se profundiza en el uso de herramientas de simulación y análisis de los resultados de las simulaciones, así como en el uso de herramientas para la implementación del control en VHDL sintetizable en la FPGA.

### 1.1 Antecedentes

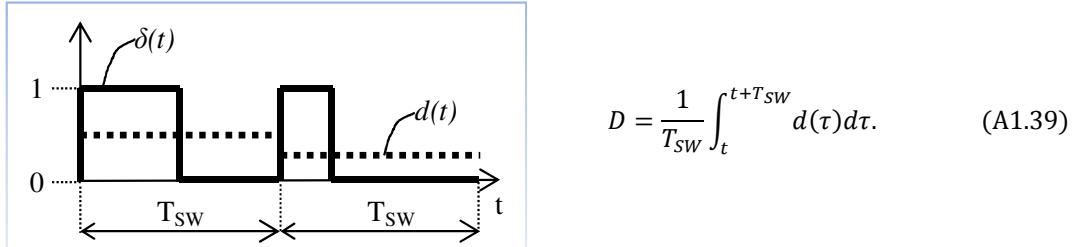

Los convertidores CC-CC son sistemas variantes en el tiempo y no lineales. Por esta razón no resulta posible la aplicación directa de las técnicas clásicas de control lineal. Para el diseño de controles lineales, se han desarrollado por ejemplo en [1, pp. 187-213] modelos promediados que permiten obtener un modelo lineal en pequeña señal. En estos modelos la pequeña señal es considerada sobre el valor promedio de las variables en un periodo de conmutación  $T_{SW}$ .

Dependiendo de si la corriente por la bobina llega a anularse o no, se tienen modelos promediados para modo de conducción continuo CCM y para modo de conducción discontinuo DCM, siendo en ambos modelos la relación de servicio  $d(t)$  la acción de entrada al modelo del convertidor. Además de depender de las no idealidades de los componentes del convertidor, la relación de tensiones entre la salida y entrada del convertidor dependen en modo de conducción continuo de la relación de servicio  $d(t)$ , mientras que en modo de conducción discontinuo dependen además de la frecuencia de conmutación  $f_{SW}$  y de la carga.

En [1, pp. 187-213] se presenta el control tradicional en modo tensión y en [1, pp. 439-489] el control tradicional en modo corriente de pico. El control modo tensión presenta una única realimentación con la tensión de salida  $v_O(t)$  mientras que el modo corriente de pico se realiza una realimentación con la tensión de salida y otra con el valor de pico de corriente por la bobina  $i_L(t)$ . El control en modo corriente de pico presenta la desventaja de ser inestable para una relación de servicio superior a 0.5 necesitando de una rampa adicional de estabilización. En [2] se desarrolla un control modo corriente basado en la corriente media por la bobina donde no se hace necesaria la rampa de estabilización. En [3] se desarrolla un control mixto de tensión y corriente que ofrece un mejor rendimiento que un control PI convencional. Un control que además necesita la medida de la corriente  $i_L(t)$  presenta la desventaja de coste económico frente a otro que únicamente precisa la medida de  $v_O(t)$ .

En ese contexto se plantea el control por realimentación lineal del estado en el convertidor CC-CC con la obtención de un modelo de pequeña señal como ilustra [1, pp. 213-226] y la aplicación de esquemas de control propios de la realimentación lineal del estado [4]. A priori, la ventaja de la realimentación de estado es la ubicación exacta de polos, lo que debe de resultar en una mejor respuesta dinámica. El control por realimentación del estado toma mayor importancia cuando el convertidor a controlar no es estable realimentando únicamente en tensión, un caso de este tipo se desarrolla en [5].

|                                             |                                                                                         |                |

|---------------------------------------------|-----------------------------------------------------------------------------------------|----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 5 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                |

Por otra parte, la utilización de circuitos integrados de ejecución concurrente como son las FPGA en el control digital de un convertidor CC-CC permiten la lectura simultánea de la tensión  $v_o(t)$  y la corriente  $i_L(t)$ . Esta ventaja junto con una representación interna de datos en coma fija hace posible alcanzar frecuencias de conmutación y muestreo más elevadas que las que se consiguen con un microcontrolador y que los dispositivos de potencia actuales pueden perfectamente alcanzar.

## 1.2 Objetivos y alcance

Los objetivos que se proponen son:

- Estudiar en simulación la forma más viable y práctica de implementar un control digital en coma fija mediante realimentación lineal del estado de un convertidor *Buck* en una FPGA.

- Implementar el control por realimentación de estado en una FPGA en coma fija.

- Realizar pruebas reales en laboratorio y comparar con las simulaciones.

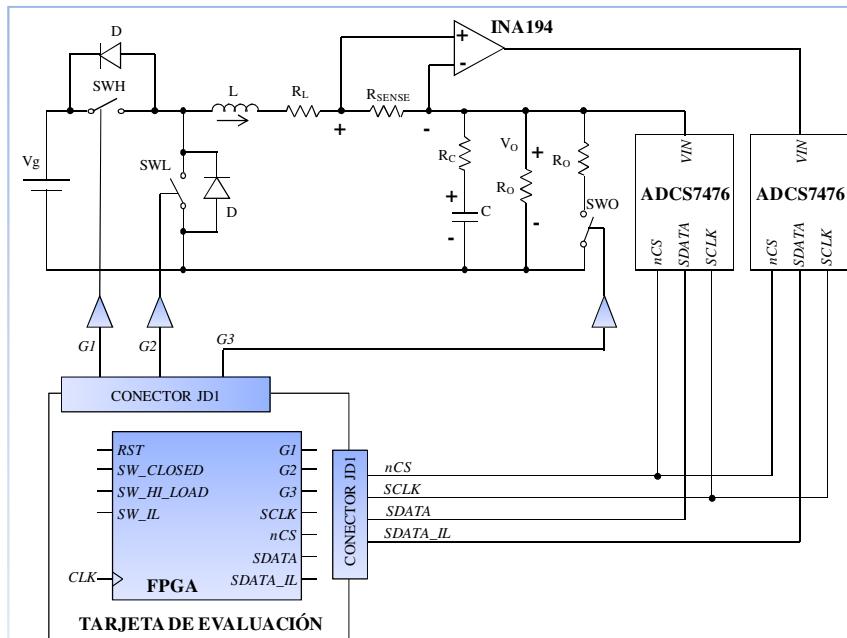

Como banco de pruebas se dispone de un convertidor *Buck* de pequeña potencia (2.5 W) montado en un circuito impreso y de una tarjeta de evaluación de una FPGA comercial.

Para alcanzar los objetivos expuestos se llevan a cabo las siguientes tareas:

- Se modela el sistema y se estudia su dinámica con objeto de establecer una especificación coherente en las prestaciones del control a realizar. Se plantea un esquema de control basado en realimentación del estado y se calcula la ley de control. El esquema de control planteado debe disponer de un integrador del error de la tensión de salida  $v_o(t)$  de forma que se garantiza el error de posición cero. Se desarrolla un modelo conmutado del convertidor que se utiliza en simulación.

- Se simula en números reales el esquema y ley de control utilizando el modelo conmutado mencionado. En esta simulación se estudian detalles clave a tener en cuenta en la posterior implementación en la FPGA, como son el instante de medida o la utilización de la salida en lugar del estado en el cálculo de la acción. Se realiza una comparativa con un control tradicional en modo tensión señalando las diferencias con el control por realimentación del estado. Se plantea un esquema de control basado en observador y se comprueba su funcionamiento en simulación, se compara con el control por realimentación del estado sin observador. Como conclusión de la simulación en reales se toman una serie de decisiones acerca de cómo se realiza la implementación en coma fija en el control digital en la FPGA.

- Aplicando las conclusiones obtenidas en la simulación en reales, se simula en coma fija planteando los formatos numéricos de las variables, la precisión a utilizar en las medidas y en la relación de servicio. Se comprueba que el control en magnitudes cuantizadas funciona y alcanza el error cuantizado cero.

- Se modela en VHDL no sintetizable un testbench del convertidor conmutado *Buck*, modulador PWM, conversor analógico a digital ADC y control en números reales. Con esto se realiza una simulación en lazo cerrado en números reales donde se validan los modelos del convertidor *Buck* y conversor ADC.

- Se describe en VHDL sintetizable el modulador PWM, lectura del ADC, control en coma fija y un interfaz de usuario que permite mediante pulsadores interactuar con el control y visualizar el estado en un visualizador led de 7 segmentos. Se realiza una simulación en lazo cerrado en coma fija donde se

|                                             |                                                                                         |                |

|---------------------------------------------|-----------------------------------------------------------------------------------------|----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 6 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                |

utilizan el convertidor *Buck* y el ADC previamente modelados. En esta simulación se comprueba que el control alcanza el error cuantizado cero.

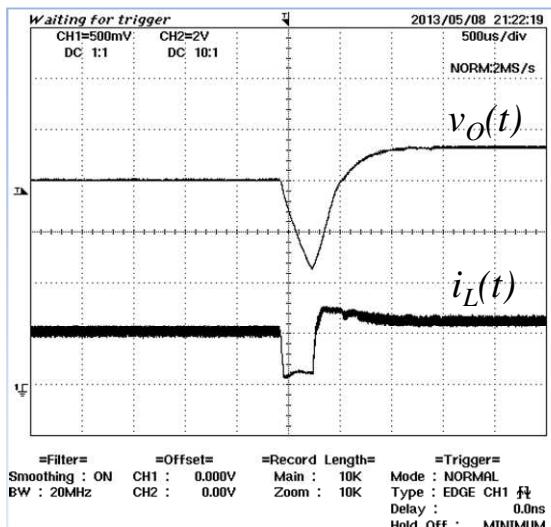

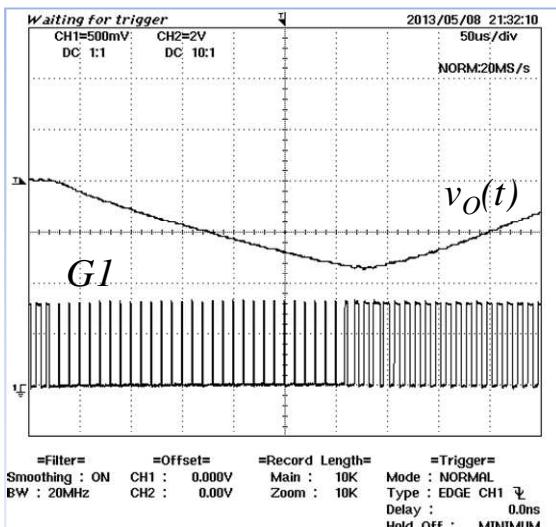

- Se configura la FPGA con el fichero de configuración obtenido y se realizan medidas experimentales en laboratorio. Las medidas capturadas se comparan con las previamente obtenidas en simulación en números reales.

- Se extraen conclusiones finales del desarrollo del proyecto y se plantea una posible continuación del trabajo.

### 1.3 Organización de la memoria

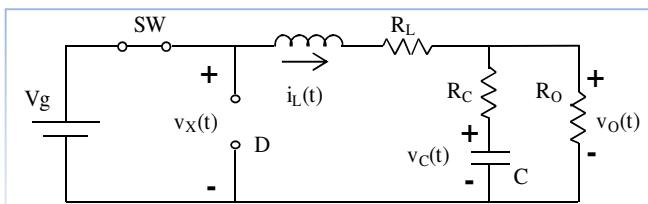

En el capítulo 2 se obtiene el modelo de pequeña señal del convertidor *Buck* objeto de estudio en este trabajo, se trata de un convertidor con no idealidades en los componentes. El modelo de pequeña señal es el utilizado para el cálculo de la ley de control y esquema de control aplicados. Se obtiene además el modelo conmutado que se utiliza en simulación para el testeo del control.

En el capítulo 3 se realiza el cálculo de la ley de control y el planteamiento del esquema de control. Se realizan simulaciones en números reales donde se determinan puntos clave a la hora de implementar el control en la FPGA. Se simula un control tradicional en modo tensión y un control por realimentación de estado basado en un observador de estado y perturbación. Se comparan estos últimos con el control por realimentación de estado objeto de este proyecto. De acuerdo a los puntos clave estudiados previamente, se toman las decisiones en cuanto a cómo se implementa el control en coma fija en la FPGA. Con estas decisiones se realiza una simulación en coma fija determinando formatos numéricos.

Con las decisiones aplicadas en la simulación en coma fija, se aborda en el capítulo 4 el diseño del testbench. Así se modela en VHDL no sintetizable y se realiza una simulación en números reales validando los modelos del convertidor *Buck* y ADC realizados. A continuación se realiza el código VHDL sintetizable del ADC, modulador PWM, control en coma fija e interfaz de usuario. Se realiza una simulación en coma fija utilizando el modelado VHDL no sintetizable previamente desarrollado. Finalmente se realiza la implementación física con la generación del fichero \*.bit con la configuración de la FPGA.

En el capítulo 5 se explica el banco de pruebas utilizado donde está montado el convertidor *Buck* y se realizan pruebas de laboratorio que se comparan con los resultados obtenidos en simulación.

Finalmente en el capítulo 6 se resumen las conclusiones del trabajo realizado y se propone una posibilidad de continuación del trabajo orientada al empleo de un observador en el control por realimentación de estado.

Los ficheros de código de simulación y los ficheros VHDL se encuentran en el CD anexo, en anexo 3 se describe el contenido de dicho CD.

## 2 MODELADO DEL CONVERTIDOR

### 2.1 Convertidor *Buck*

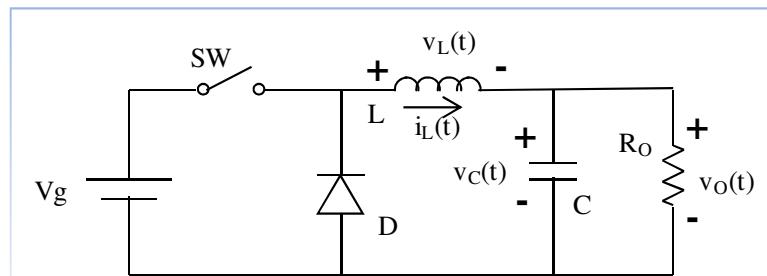

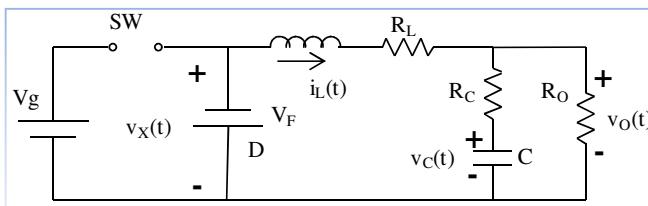

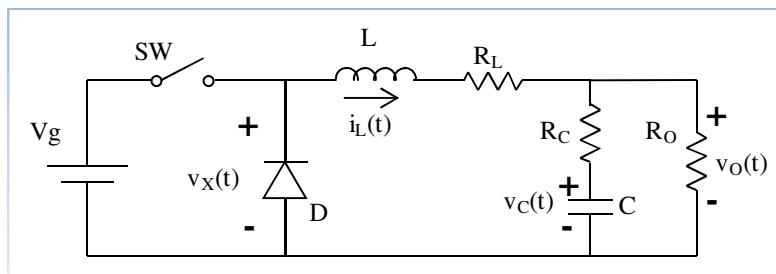

La Fig. 1 muestra el convertidor *Buck* (*step-down*) ideal.

Fig. 1. Convertidor *Buck*.

El interruptor de potencia *SW* conduce un tiempo  $t_{ON}$  dentro de un período  $T_{SW}$ . Se define la relación de servicio (*duty ratio*):

$$d(t) = \frac{t_{ON}}{T_{SW}}, \text{ cumpliéndose } d'(t) = 1 - d(t). \quad (2.1)$$

El resto del tiempo dentro del período  $T_{SW}$  se denomina  $t_{OFF}$ ,  $t_{OFF} = T_{SW} - t_{ON}$ . A la relación de servicio en régimen estacionario se la denomina  $D$ , con  $D' = 1 - D$ .

Se dice que el convertidor trabaja en modo de conducción continuo CCM cuando la corriente por la bobina  $i_L(t)$  no llega a hacerse cero en ningún momento durante el período  $T_{SW}$ . En CCM la relación de tensiones medias entre entrada y salida viene determinada por la relación de servicio en estado estacionario:

$$D = \frac{V_O}{V_g}. \quad (2.2)$$

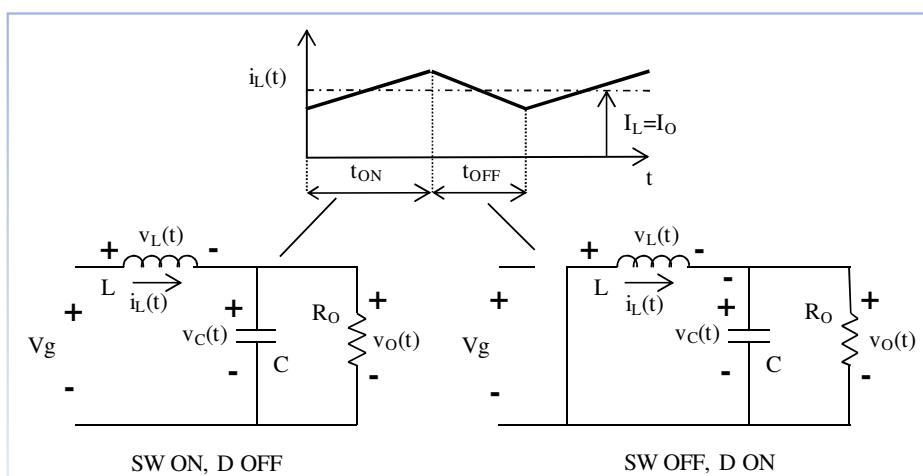

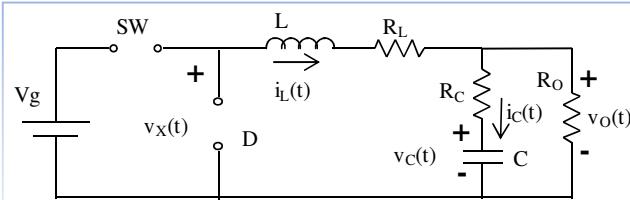

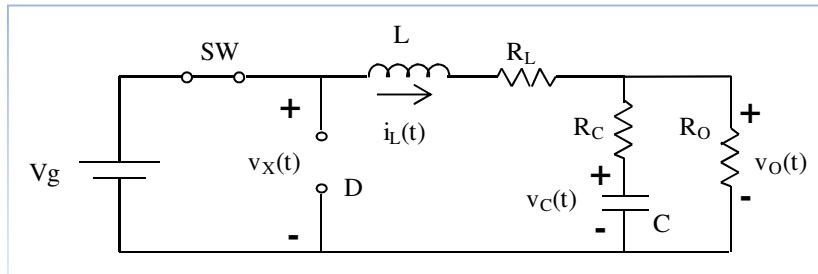

En modo CCM el convertidor presenta dos topologías diferentes, como muestra la Fig. 2

Fig. 2. Topologías del convertidor *Buck* en CCM.

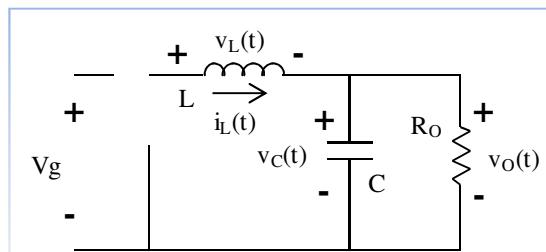

Si la corriente  $i_L(t)$  llega a hacerse cero se dice que el convertidor trabaja en modo de conducción discontinuo DCM. En este caso, además de los conocidos  $t_{ON}$  y  $t_{OFF}$  aparece un tercer período de tiempo denominado  $\Delta$  cuya topología es la mostrada en la Fig. 3.

Fig. 3. Topología del convertidor *Buck* en intervalo  $\Delta$ .

Puede encontrarse una descripción completa del convertidor *Buck* en [6].

## 2.2 Modelo de estado de pequeña señal

La notación de variables así como los datos del convertidor pueden consultarse en los anexos. En [7] se desarrolla la descripción interna de un sistema por medio del modelo de estado.

### 2.2.1 Modelo promediado de gran señal

Supuesto que el convertidor *Buck* trabaja en CCM, se plantea un sistema con variables instantáneas de gran señal, con  $n = 2$  variables de estado,  $m = 2$  entradas y  $p = 2$  salidas.

Como vector de estado:

$$x(t) = \begin{pmatrix} i_L(t) \\ v_C(t) \end{pmatrix}. \quad (2.3)$$

Como vector de entradas:

$$u(t) = \begin{pmatrix} V_g \\ V_F \end{pmatrix}. \quad (2.4)$$

Como vector de salidas:

$$y(t) = \begin{pmatrix} i_L(t) \\ v_O(t) \end{pmatrix}. \quad (2.5)$$

Se trata de un sistema lineal y variante en el tiempo, la Fig. 4 muestra la topología en el intervalo  $t_{ON}$  donde se plantea la ecuación de estado (2.6) y de salida (2.7):

$$\dot{x}(t) = A_1 x(t) + B_1 u(t) \quad (2.6)$$

$$y(t) = C_1 x(t). \quad (2.7)$$

Fig. 4. Modelo de estado en intervalo  $t_{ON}$ .

Donde la matriz dinámica  $A_1$ , de entradas  $B_1$  y de salidas  $C_1$  se pueden expresar:

$$A_1 = \begin{pmatrix} a & b \\ c & d \end{pmatrix}, B_1 = \begin{pmatrix} 1 & 0 \\ 0 & 0 \end{pmatrix}, C_1 = \begin{pmatrix} 1 & 0 \\ e & f \end{pmatrix}. \quad (2.8)$$

Los coeficientes  $a, b, c, d, e$  y  $f$  se encuentran en anexo A1.

La Fig. 5 muestra la topología en el intervalo  $t_{OFF}$ , con ecuación de estado (2.9) y de salida (2.10):

$$\dot{x}(t) = A_2 x(t) + B_2 u(t) \quad (2.9)$$

$$y(t) = C_2 x(t). \quad (2.10)$$

Fig. 5. Modelo de estado en intervalo  $t_{OFF}$ .

|                                             |                                                                                         |                |

|---------------------------------------------|-----------------------------------------------------------------------------------------|----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 9 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                |

Donde la matriz dinámica  $A_2$ , de entradas  $B_2$  y de salidas  $C_2$  se pueden expresar:

$$A_2 = \begin{pmatrix} a & b \\ c & d \end{pmatrix}, B_2 = \begin{pmatrix} 0 & -1 \\ 0 & L \end{pmatrix}, C_2 = \begin{pmatrix} 1 & 0 \\ e & f \end{pmatrix}. \quad (2.11)$$

Con las variables de estado  $X$ , entrada  $U$ , salida  $Y$  de gran señal promediadas en  $T_{SW}$ :

$$X = \frac{1}{T_{SW}} \int_t^{t+T_{SW}} x(\tau) d\tau, U = \frac{1}{T_{SW}} \int_t^{t+T_{SW}} u(\tau) d\tau, Y = \frac{1}{T_{SW}} \int_t^{t+T_{SW}} y(\tau) d\tau. \quad (2.12)$$

Y la relación de servicio  $D$  de gran señal promediada en  $T_{SW}$ :

$$D = \frac{1}{T_{SW}} \int_t^{t+T_{SW}} d(\tau) d\tau. \quad (2.13)$$

Promediando las matrices en (2.8) y (2.11) para una relación de servicio  $D$ , se obtiene el modelo promediado de gran señal:

$$\dot{X} = (DA_1 + D'A_2)X + (DB_1 + D'B_2)U \quad (2.14)$$

$$Y = (DC_1 + D'C_2)X. \quad (2.15)$$

## 2.2.2 Modelo de pequeña señal

Las matrices promediadas en el punto de operación con una relación de servicio de gran señal  $D_0$  son:

$$A = D_0 A_1 + D'_0 A_2 \quad (2.16)$$

$$B = D_0 B_1 + D'_0 B_2 \quad (2.17)$$

$$C = D_0 C_1 + D'_0 C_2. \quad (2.18)$$

La ecuación de estado en el permanente del punto de operación con una entrada  $U_0$  se expresa:

$$0 = (D_0 A_1 + D'_0 A_2)X_0 + (D_0 B_1 + D'_0 B_2)U_0 = AX_0 + BU_0. \quad (2.19)$$

De donde se obtiene el vector de estado en el punto de operación en función de la acción:

$$X_0 = -A^{-1}BU_0. \quad (2.20)$$

Las ecuaciones (2.14) y (2.15) son no lineales. Linealizando en el punto de operación utilizando para ello la igualdad (2.20), se obtiene la expresión del modelo de estado de pequeña señal:

$$\dot{x} = Ax + Bu + B_d d \quad (2.21)$$

$$y = Cx. \quad (2.22)$$

Donde  $x$ ,  $u$ ,  $d$  e  $y$  son variables de pequeña señal. La matriz  $B_d$  de entradas respecto a la entrada  $d$  se expresa como:

$$B_{d2x1} = (A_1 - A_2)X_0 + (B_1 - B_2)U_0. \quad (2.23)$$

Aplicando principio de superposición considerando nula la entrada  $u$  en el modelo de estado formado por (2.21) y (2.22), se obtiene la función de transferencia en continuo  $G_{yd}(s)$  respecto a la entrada  $d$ :

$$G_{yd}(s) = \begin{pmatrix} \frac{83824(s+1762)}{(s+2171.5 \pm 7911.8i)} \\ \frac{6498(s+56818)}{(s+2171.5 \pm 7911.8i)} \end{pmatrix}. \quad (2.24)$$

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 10 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

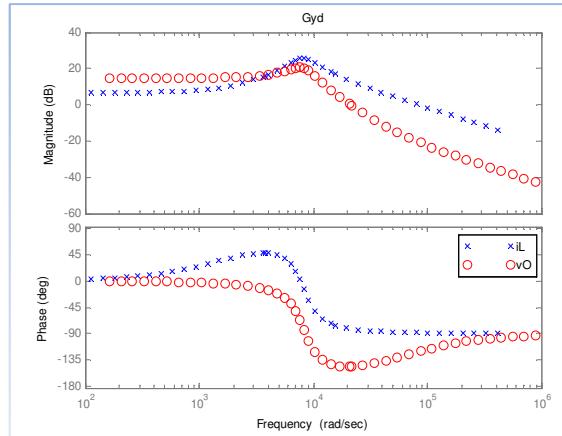

En la Fig. 6 se representa diagrama de *Bode* de  $G_{yd}(s)$ .

Fig. 6. Diagrama de *Bode* de  $G_{yd}(s)$ .

La dinámica es de un sistema de segundo orden con cero y dos polos complejos conjugados, con una frecuencia natural  $w_n = 8204$  rad/seg y un coeficiente de amortiguamiento  $\xi = 0.264$ . En la frecuencia amortiguada  $w_p = w_n\sqrt{1 - \xi^2} = 7911$  rad/seg se mide el pico de resonancia en el diagrama de *Bode* y el periodo de la frecuencia amortiguada es:

$$T_p = \frac{2\pi}{w_p} = 0.794 \text{ ms.} \quad (2.25)$$

En [8] se explica la teoría de sistemas de segundo orden y la representación de diagramas de *Bode*.

Ya que la entrada de control es  $d$ , el modelo de estado en pequeña señal a utilizar para el cálculo de la ley de control es:

$$\dot{x} = Ax + B_d d \quad (2.26)$$

$$y = Cx. \quad (2.27)$$

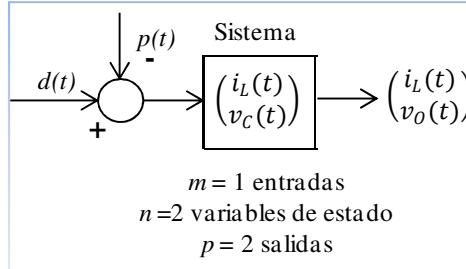

Con  $n = 2$  variables de estado,  $m = 1$  entrada y  $p = 2$  salidas.

Puesto que la ley de control se calcula directamente en discreto, se discretiza la ecuación de estado (2.26) por el método *Zero Order Hold* con un periodo de muestreo  $T_{SW}$ . La discretización por *Zero Order Hold* se realiza mediante la función *c2d* de *Matlab*, en [9] se estudian varios métodos de discretización.

Se obtiene la expresión del modelo de estado en pequeña señal en discreto:

$$x(k+1) = Fx(k) + Gd(k) \quad (2.28)$$

$$y(k) = Cx(k). \quad (2.29)$$

### 2.3 Modelo de estado conmutado

El modelo conmutado es un modelo lineal variante en el tiempo y de gran señal. Es utilizado para simulación, es decir, no se utiliza en absoluto para el cálculo de la ley de control. Como se describe en este apartado, la relación de servicio  $d(k)$  calculada por el control se aplica en simulación a un modelo de estado conmutado discretizado en  $T_{CLK}$ , siendo  $T_{CLK} \ll T_{SW}$  y teniendo en cuenta que el modelo de estado de pequeña señal (2.28) y (2.29) utilizado para el cálculo de la ley de control ha sido discretizado en  $T_{SW}$ .

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 11 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

Además de los modelos de gran señal instantáneos obtenidos en 2.2.1 para los intervalos  $t_{ON}$  y  $t_{OFF}$ , se calcula el correspondiente al intervalo  $\Delta$  como indica la Fig 7, con ecuación de estado (2.30) y de salida (2.31):

$$\dot{x}(t) = A_3 x(t) + B_3 u(t) \quad (2.30)$$

$$y(t) = C_3 x(t). \quad (2.31)$$

Fig. 7. Modelo de estado en intervalo  $\Delta$ .

Donde la matriz dinámica  $A_3$ , de entradas  $B_3$  y de salidas  $C_3$  se pueden expresar:

$$A_3 = \begin{pmatrix} 0 & 0 \\ 0 & d \end{pmatrix}, B_3 = \begin{pmatrix} 0 & 0 \\ 0 & 0 \end{pmatrix}, C_3 = \begin{pmatrix} 1 & 0 \\ 0 & f \end{pmatrix}. \quad (2.32)$$

La utilidad del modelo comutado es hacer evolucionar el estado del sistema en un periodo de tiempo mucho menor que  $T_{SW}$ . Se utiliza para ello la señal de reloj de la FPGA con un periodo  $T_{CLK}$ . Puesto que la simulación del sistema se realiza en discreto, se discretizan en  $T_{CLK}$  los tres modelos de estado de gran señal correspondientes a los intervalos  $t_{ON}$ ,  $t_{OFF}$  y  $\Delta$  por el método *Zero Order Hold*.

Intervalo  $t_{ON}$ , discretizando (2.6) y (2.7) se obtiene:

$$x(k+1) = F_1 x(k) + G_1 u(k) \quad (2.33)$$

$$y(k) = C_1 x(k). \quad (2.34)$$

Intervalo  $t_{OFF}$ , discretizando (2.9) y (2.10) se obtiene:

$$x(k+1) = F_2 x(k) + G_2 u(k) \quad (2.35)$$

$$y(k) = C_2 x(k). \quad (2.36)$$

Intervalo  $\Delta$ , discretizando (2.30) y (2.31) se obtiene:

$$x(k+1) = F_3 x(k) + G_3 u(k) \quad (2.37)$$

$$y(k) = C_3 x(k). \quad (2.38)$$

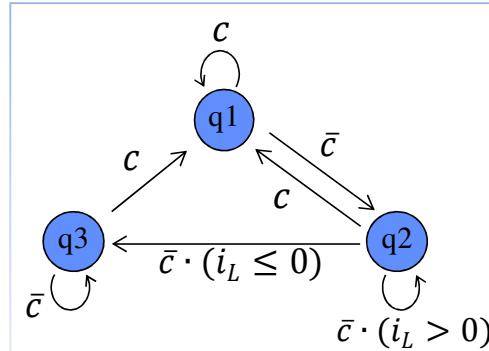

Siendo  $c$  la señal de control del interruptor de potencia  $SW$ , las tres configuraciones expuestas son  $q1$  para  $t_{ON}$ ,  $q2$  para  $t_{OFF}$  y  $q3$  para  $\Delta$ . La Fig. 8 muestra las condiciones de transición en un diagrama de estados.

Fig. 8. Diagrama de estados del modelo comutado.

El módulo del contador digital en el modulador es:

$$N_C = \frac{f_{CLK}}{f_{SW}} = 500. \quad (2.39)$$

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 12 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

Se tienen  $N_C$  periodos  $T_{CLK}$  dentro de un periodo  $T_{SW}$ . Por cada de uno de estos periodos  $T_{CLK}$  se aplica el modelo correspondiente al intervalo  $t_{ON}$ ,  $t_{OFF}$  o  $\Delta$  dependiendo de la acción  $d(k)$  calculada por el control y del estado. Puesto que la ley de control es calculada sobre un modelo que es muestrado en  $T_{SW}$ , se debe tomar una muestra del estado por cada periodo  $T_{SW}$ . Más adelante en este trabajo se determina cuál de las  $N_C$  muestras es la idónea a registrar como estado del sistema y ser utilizada en el cálculo de la acción en el siguiente periodo  $T_{SW}$ .

En [10] se expone con detalle el modelo conmutado con restricciones de un convertidor.

|                                             |                                                                                                                             |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster<br>Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado | Página 13 de 52 |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------|

### 3 DISEÑO DEL CONTROL DIGITAL

#### 3.1 Esquema de integradores

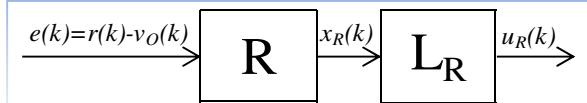

Partiendo del modelo en pequeña señal en discreto obtenido en (2.28) y (2.29) se aplica un esquema de control que incluye un integrador  $x_R(k)$  del error  $e(k)$  de la referencia  $r(k)$  respecto a  $v_o(k)$  con una ganancia  $L_R$ , como muestra la Fig. 9:

$$x_R(k+1) = F_R x_R(k) + G_R e(k) \quad (3.1)$$

$$F_R = I, G_R = I. \quad (3.2)$$

Fig. 9. Integrador.

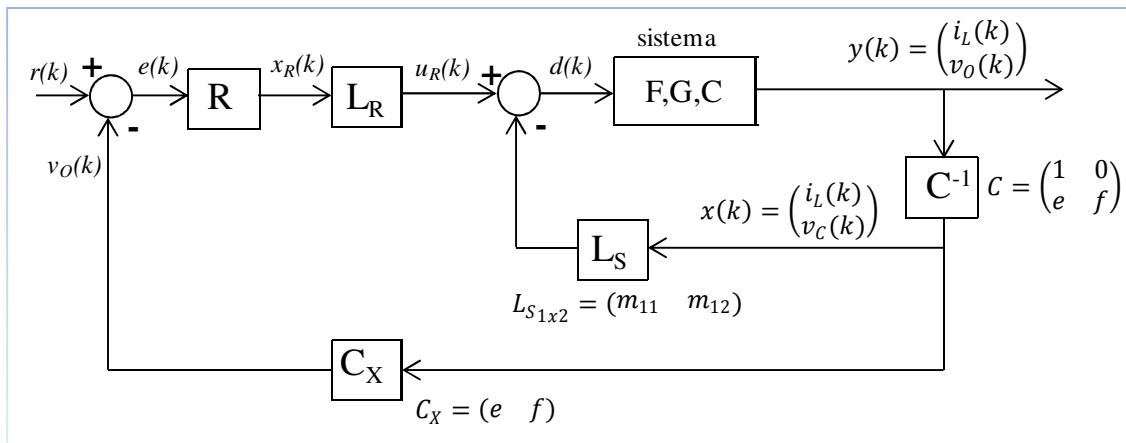

El vector de estado es realimentado mediante la ley de control  $L_S$  mientras que la variable  $v_o(k)$  a comparar con  $r(k)$  se obtiene mediante la matriz  $C_X$  operando a partir del vector de estado calculado mediante  $C^{-1}$  a partir de la salida medida. El esquema de control se muestra en la Fig 10.

Fig. 10. Esquema de control con integrador.

El esquema de control por realimentación de estado con integradores está descrito en [11].

Se plantea un nuevo sistema de orden 3 utilizando  $x_R(k)$  como nueva variable de estado, donde las ecuaciones de estado y salida son:

$$\begin{pmatrix} i_L(k+1) \\ v_C(k+1) \\ x_R(k+1) \end{pmatrix} = \begin{pmatrix} F & 0 \\ -G_R C_X & F_R \end{pmatrix} \begin{pmatrix} i_L(k) \\ v_C(k) \\ x_R(k) \end{pmatrix} + \begin{pmatrix} G \\ 0 \end{pmatrix} d(k) + \begin{pmatrix} 0 \\ G_R \end{pmatrix} r(k) \quad (3.3)$$

$$\begin{pmatrix} i_L(k) \\ v_o(k) \end{pmatrix} = (C \quad 0) \begin{pmatrix} i_L(k) \\ v_C(k) \\ x_R(k) \end{pmatrix}. \quad (3.4)$$

Que denotando con el subíndice  $i$  se expresan:

$$x_i(k+1) = F_i x_i(k) + G_i d(k) + G_{ref} r(k) \quad (3.5)$$

$$y_i(k) = C_i x_i(k). \quad (3.6)$$

Puesto que la acción  $d(k)$  puede ser expresada de la forma:

$$d(k) = -L_i x_i(k) = -(L_S \quad -L_R) x_i(k). \quad (3.7)$$

Sustituyendo en la ecuación de estado (3.5) se obtiene:

$$x_i(k+1) = (F_i - G_i L_i) x_i(k) + G_{ref} r(k). \quad (3.8)$$

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 14 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

Donde  $(F_i - G_i L_i)$  es la nueva matriz dinámica y sus valores propios (las raíces de  $|zI - F_i + G_i L_i|$ ) los polos del bucle cerrado de  $\frac{v_C(z)}{r(z)}$ ,  $\frac{i_L(z)}{r(z)}$  y  $\frac{x_R(z)}{r(z)}$ .

La asignación de polos se realiza mediante la función *place* en *Matlab* cuyo algoritmo está descrito en [12]. Este algoritmo requiere que con una entrada  $r(k)$  de dimensión 1x1 no se puede repetir ni siquiera un polo. El resultado es la ley de control  $L_i$ :

$$L_{i1x3} = (L_S \quad -L_R) \quad (3.9)$$

$$L_{S1x2} = (m_{11} \quad m_{12}). \quad (3.10)$$

Puesto que se deben de asignar 3 polos ya que el sistema es de orden 3, se opta por un sistema de segundo orden dominante cuasi críticamente amortiguado con un tiempo de respuesta:

$$tr = 0.5 \text{ ms.} \quad (3.11)$$

Siendo este tiempo  $tr$  coherente con el periodo  $T_P$  de la frecuencia amortiguada de la función de transferencia del convertidor visto en (2.25).

### 3.2 Simulación en números reales

La ley de control  $L_i$  y esquema de control presentados en 3.1 se testean utilizando el modelo conmutado descrito en 2.3. La finalidad de esta simulación es el alcanzar conclusiones que faciliten la implementación en FPGA y la comparación con otros tipos de control.

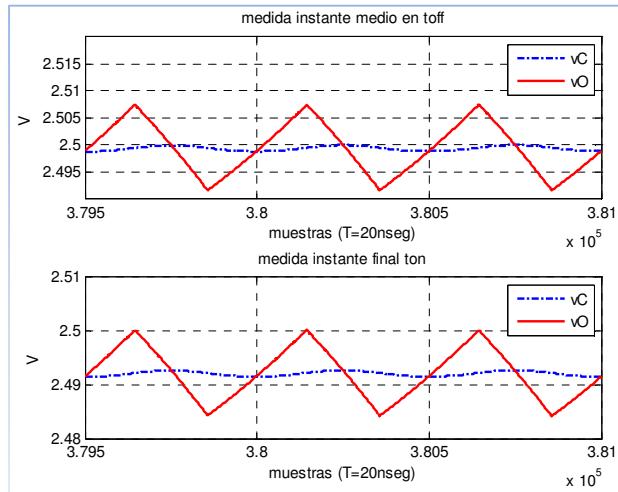

#### 3.2.1 Instante de muestreo

Como se ha visto en 2.3, se tienen  $N_C$  periodos  $T_{CLK}$  dentro de un periodo  $T_{SW}$ . Puesto que el modelo utilizado para el cálculo de la ley de control es un modelo promediado, lo ideal sería utilizar un vector de estado medido que fuera la media del estado en los  $N_C$  periodos  $T_{CLK}$  dentro de un periodo  $T_{SW}$ . Esto sería posible en simulación pero no lo es en la implementación en la FPGA, donde solamente se hace un muestreo del estado por periodo  $T_{SW}$ . La simulación sobre el modelo conmutado permite especificar en qué iteración en  $T_{CLK}$  de las  $N_C$  que componen un periodo  $T_{SW}$  se realiza el muestreo.

Lo ideal es que el estado muestreado sea lo más parecido posible al promediado del estado en  $T_{SW}$ . Esto se conseguiría muestreando en el instante medio del intervalo  $t_{OFF}$  si el sistema ha alcanzado el estacionario, para ello se utiliza un modulador *symmetric off time* como se describe en [13] cuyo punto central coincide con el instante medio del intervalo  $t_{OFF}$ . Se conseguiría lo mismo con un modulador *symmetric on time* muestreando en el instante medio del  $t_{ON}$ .

Se realizan simulaciones tomando la medida en el instante medio del intervalo  $t_{OFF}$  y tomando la medida en el instante final del intervalo  $t_{ON}$ . En la implementación práctica no es aconsejable ésta última opción ya que la conversión del ADC puede verse afectada por el ruido de la comutación del interruptor  $SW$ .

Ambas situaciones de muestreo se comparan en la Fig. 11.

Fig. 11. Comparación por instante de muestreo

Puede apreciarse cómo el control lleva a consigna a la salida en el instante de medida. La medida del estado en el instante medio  $t_{OFF}$  es claramente favorable, puesto que la medida corresponde con los valores medios  $V_C = V_O$ , si el convertidor ha alcanzado el estacionario.

### 3.2.2 Aproximación del estado por la salida

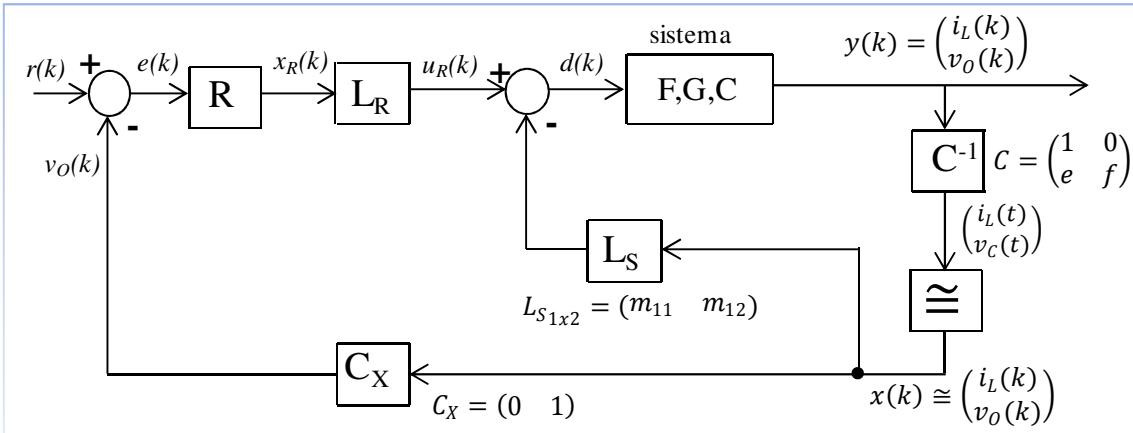

Ya que en el estacionario los valores medios de  $v_C(t)$  y  $v_O(t)$  son iguales con  $V_C = V_O$ , se simula sustituyendo la variable de estado  $v_C(k)$  por  $v_O(k)$ . El esquema se muestra en la Fig. 12.

Fig. 12. Esquema de control con integrador con aproximación de  $v_C(k)$  por  $v_O(k)$ .

Se realiza la misma asignación de polos en bucle cerrado que en 3.1. Se utiliza la matriz  $C_X = (0 \ 1)$  en la realimentación de  $v_O(k)$ . Además  $C_X$  interviene en la ecuación de estado (3.3) y por tanto en la ley de control calculada  $L_i$ . La matriz de salidas  $C$  sigue siendo la misma que en el caso de no aproximación e interviene en el cálculo de la ley de control. El vector de estado aproximado  $x(k) \cong \begin{pmatrix} i_L(k) \\ v_O(k) \end{pmatrix}$  se utiliza en el cálculo de la acción  $d(k)$  en lugar del vector de estado medido  $x(k) = \begin{pmatrix} i_L(k) \\ v_C(k) \end{pmatrix}$  utilizado en el caso de no aproximación.

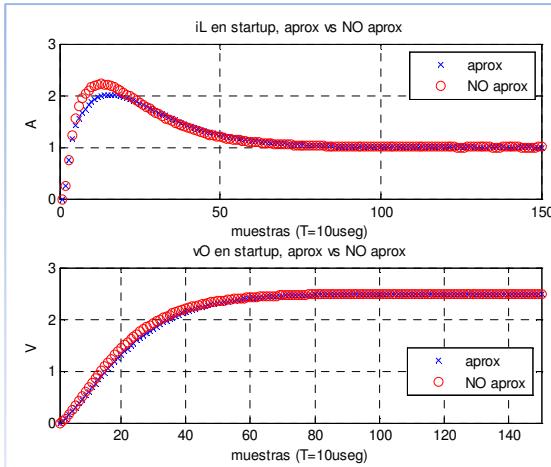

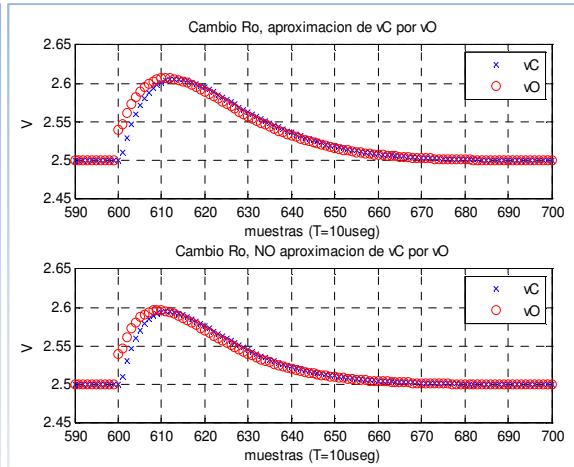

En la Fig. 13 se compara la salida en el *start-up* con y sin aproximación  $v_C$  por  $v_O$ . En la Fig. 14 se compara el transitorio debido a un cambio en la carga  $R_O = 2.5 \Omega$  a  $R_O = 5 \Omega$ .

Fig. 13. Comparación del *start-up* con y sin aproximación de  $v_C(k)$  por  $v_O(k)$ .

Fig. 14. Comparación del cambio en  $R_O$  con y sin aproximación de  $v_C(k)$  por  $v_O(k)$ .

Se puede comprobar que en ambos casos una dinámica muy similar, no sólo en el cambio de carga  $R_O$  sino también en el *start-up* y en el cambio de tensión de alimentación  $V_g$ . Las muestras de  $v_C(k)$  y  $v_O(k)$  difieren en el transitorio y se igualan en el permanente, ya que en el permanente los valores medios son iguales con  $V_C = V_O$ .

### 3.2.3 Efecto de antiwindup

La acción aplicada  $d(k)$  no es infinita sino que se encuentra limitada por un modelo de saturación tal que:

$$d_{min} = 0.1, d_{max} = 0.85. \quad (3.12)$$

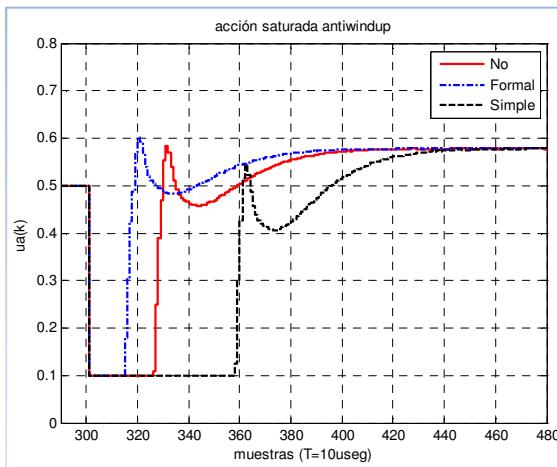

Por esta razón se analiza el efecto de un esquema de antiwindup que compense la integración del error cuando la acción permanece saturada cierto tiempo.

Aplicando la dinámica referida en (3.11) y la aproximación  $v_C$  por  $v_O$  descrita en 3.2.2, se comprueba en simulación que la relación de servicio  $d$  no se satura en el *start-up*, sin embargo si se satura en el cambio desde una situación en lazo abierto aplicando  $D_0$  a una situación de control en lazo cerrado. Es en este cambio donde se analiza el efecto de un esquema de antiwindup.

Se analizan tres situaciones

1. No se aplica antiwindup

2. Antiwindup simplificado. No se integra cuando la acción está saturada.

3. Esquema de antiwindup *formal* con acción de dimensión 1x1 como se describe en [14]. Se comprueba que el control por realimentación de estado tiene una dinámica similar a un control modo tensión con las especificaciones:

$$\text{Margen de fase } MF = 60^\circ, \text{ frecuencia de cruce } f_C = 5 \text{ kHz.} \quad (3.13)$$

Se aplica el tracking que se aplicaría a un control modo tensión con las especificaciones en

$$(3.13) \text{ seg\xedn } \frac{awu}{v}(s) = \frac{1}{s \cdot \sqrt{T_i \cdot T_d}}, \text{ se discretiza en } T_{SW} \text{ por } tustin.$$

La Fig. 15 muestra el esquema de antiwindup.

Fig. 15. Esquema de antiwindup.

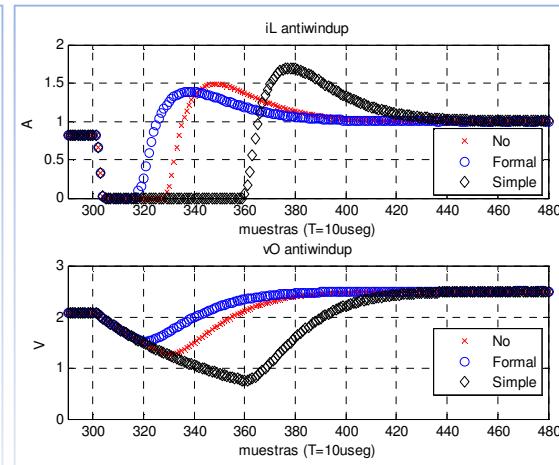

En el mencionado cambio de lazo abierto a lazo cerrado, la Fig. 16 muestra la acción saturada  $ua(k)$  mientras que la Fig. 17 muestra la corriente  $i_L(k)$  y la tensión  $v_O(k)$ .

Fig. 16. Comparación de la acción saturada con y sin antiwindup.

Fig. 17. Comparación de la salida con y sin antiwindup.

### 3.2.4 Comparación con control modo tensión

Se comparan en simulación el control por realimentación del estado con un control modo tensión de dinámica similar como lo es el especificado en (3.13). Las especificaciones de los controles son

Control modo tensión:

- 2º orden dominante subamortiguado, margen de fase  $MF = 60^\circ$ , frecuencia de cruce  $f_C = 5$  kHz, tiempo de respuesta  $tr = 0.12$  ms, polos dominantes en  $-26180 \pm 34907i$ .

- Compensador:

$$C(s) = K \frac{(1 + T_i s)}{T_i s} \frac{\left(1 + \frac{s}{w_Z}\right)}{\left(1 + \frac{s}{w_P}\right)}. \quad (3.14)$$

Para su cálculo se utiliza el *Método del factor k* desarrollado en [15].

- Se utiliza esquema de antiwindup *formal* de 3.2.3.

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 18 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

Control por realimentación del estado:

- 2º orden dominante críticamente amortiguado, frecuencia de cruce  $f_C = 725$  Hz, tiempo de respuesta  $tr = 0.5$  ms, polos dominantes aproximadamente en  $-9509$ .

- No se utiliza antiwindup. Aproximación de estado por la salida ( $v_C$  por  $v_O$ ).

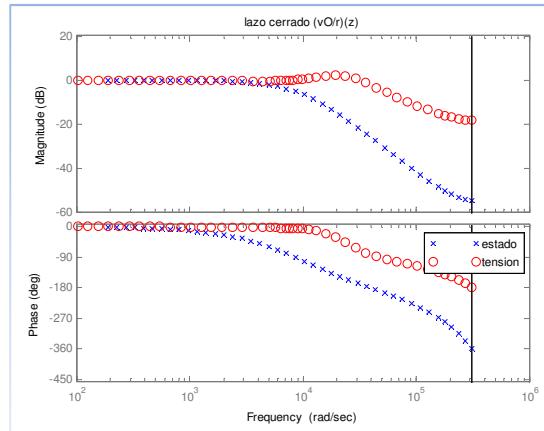

La Fig. 18 compara el *Bode* del lazo cerrado en discreto  $\frac{v_O(z)}{r(z)}$  de ambos controles.

Fig. 18. Comparación del lazo cerrado entre controles por realimentación del estado y modo tensión.

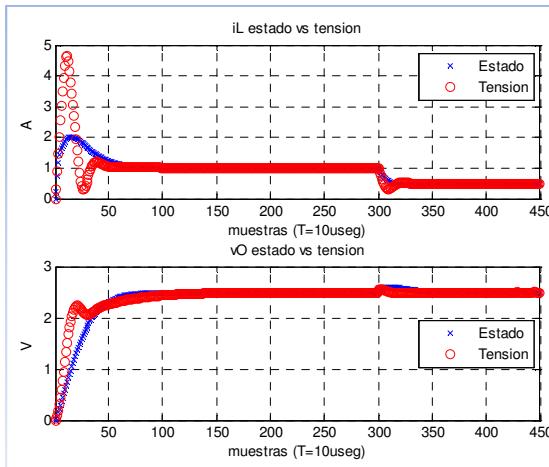

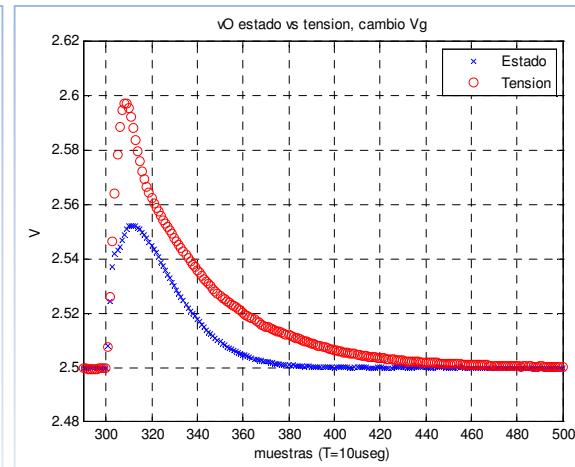

La Fig. 19 muestra un *start-up* y un cambio en la carga de  $R_O = 2.5 \Omega$  a  $R_O = 5 \Omega$ . La Fig. 20 compara ambos controles ante un cambio en la tensión de entrada  $V_g$  de 5 V a 7 V:

Fig. 19. Comparación del *start-up* y cambio  $R_O$  entre controles por realimentación del estado y modo tensión.

Fig. 20. Comparación cambio en  $V_g$  entre controles por realimentación del estado y modo tensión.

Se observa cómo el control por realimentación del estado responde notablemente mejor en el *start-up*, también responde mejor en el cambio de alimentación  $V_g$ , en cambio el control modo tensión tiene mejor respuesta en el cambio de carga  $R_O$ .

En el control modo tensión se puede observar la acción saturada durante el *start-up*. No es así sin embargo en el control por realimentación de estado. Durante el *start-up*, desactivando el antiwindup en el control modo tensión se tendría sobrepasamiento en  $v_O(t)$ , e incluso con el antiwindup activado el pico de corriente  $i_L(t)$  durante esta fase de *start-up* es muy superior al del control por realimentación de estado.

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 19 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

El control por realimentación del estado presenta una mayor sencillez en cuanto al uso de muestras previas utilizadas para el cálculo de la acción  $d(k)$  en la iteración  $k$ . El control por realimentación del estado utiliza una única muestra previa para el integrador, mientras que el control modo tensión utiliza cuatro muestras previas (dos para el error y otras dos para la relación de servicio).

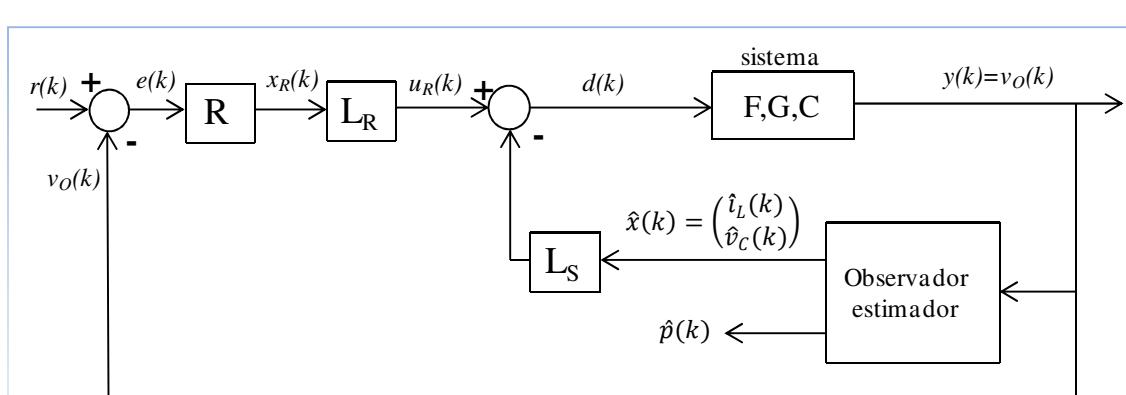

### 3.2.5 Esquema de control con observador

Se realiza la simulación de un esquema de control por realimentación del estado basado en un observador total de estado y perturbación. La ventaja de este esquema es la aplicación de un control por realimentación del estado sin medir la corriente por la bobina  $i_L(t)$ , además del filtrado inherente en un observador. En [16] se describen esquemas de control basados en observadores.

Se introduce una perturbación  $p(k)$  subtractiva de la acción  $d(k)$ . De esta forma  $p(k)$  suma los efectos de todas las posibles perturbaciones que afectan a  $d(k)$ , como son la variación en la tensión de alimentación  $Vg$  y la variación en la carga  $R_O$ . Así con  $q = 1$  perturbaciones y una matriz de entradas de la perturbación:

$$G_P = -G. \quad (3.15)$$

Con  $n = 2$  variables de estado  $x(k) = \begin{pmatrix} i_L(k) \\ v_C(k) \end{pmatrix}$ ,  $m = 1$  entradas  $d(k)$ , con  $p = 1$  salidas  $y(k) = v_O(k)$ , se plantea el modelo de estado de pequeña señal en discreto:

$$x(k+1) = Fx(k) + Gd(k) + G_P p(k) \quad (3.16)$$

$$y(k) = Cx(k). \quad (3.17)$$

Donde la matriz de salidas  $C$  coincide con la matriz  $C_X$ :

$$C = C_X = (e \quad f). \quad (3.18)$$

La Fig. 21 muestra el esquema de control con observador

Fig. 21. Esquema de control con observador.

El observador estimador de estado y perturbación es de orden 3 y su vector de estado es el error en la estimación del vector de estado del sistema y la estimación de la perturbación:

$$x^*(k) = \begin{pmatrix} \tilde{i}_L(k) \\ \tilde{v}_C(k) \\ \hat{p}(k) \end{pmatrix} = \begin{pmatrix} \tilde{x}(k) \\ \hat{p}(k) \end{pmatrix}. \quad (3.19)$$

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 20 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

La asignación de polos del observador se realiza mediante la función *place*, aplicando una dinámica de segundo orden dominante cuasi críticamente amortiguado y un tiempo de respuesta del observador *tro* relacionado con el tiempo de respuesta del lazo cerrado del esquema de integradores *tr* (3.11):

$$tro = \frac{tr}{5}. \quad (3.20)$$

La matriz dinámica del observador se descompone en las matrices  $F_{OP}$  y  $C_{OP}$ :

$$F_{OP} = \begin{pmatrix} F & -G_P \\ 0 & I \end{pmatrix}_{3 \times 3} \quad (3.21)$$

$$C_{OP} = (CF - CG_P)_{1 \times 3}. \quad (3.22)$$

Las matrices  $F_{OP}$  y  $C_{OP}$  intervienen en la asignación de polos mediante la función *place*, obteniéndose la ley del observador  $L_{OP}$ :

$$L_{OP} = \begin{pmatrix} L_O \\ L_P \end{pmatrix}_{3 \times 1} \quad (3.23)$$

$$L_O = \begin{pmatrix} n_{11} \\ n_{21} \end{pmatrix}_{2 \times 1}. \quad (3.24)$$

El vector de estado estimado  $\hat{x}(k)$  interviene en el cálculo de la acción  $d(k)$  mientras que la entrada del integrador  $x_R(k)$  sigue siendo el error  $e(k)$  de la referencia  $r(k)$  respecto a  $v_O(k)$ . La acción saturada  $ua(k)$  presentada en 3.2.3 es utilizada en el cálculo del vector de estado predicho  $\bar{x}(t)$ .

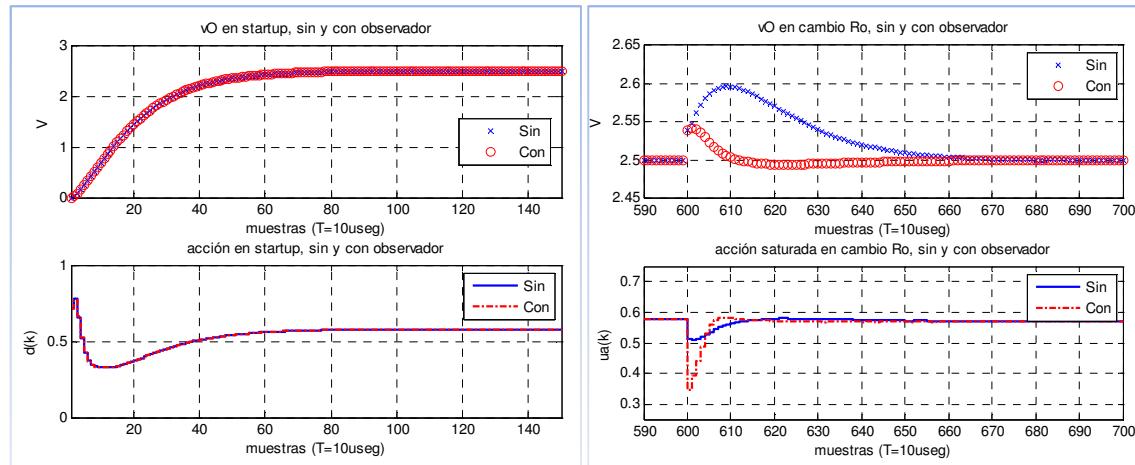

En simulación se compara el control con observador y el control por realimentación de estado sin observador, en este último no se aplica la aproximación de  $v_C$  por  $v_O$ . El control con observador ofrece una dinámica del estado muy similar al control sin observador sobre todo en *start-up* y cambio en alimentación  $Vg$ . Sin embargo puede observarse una acción saturada  $ua(k)$  bastante diferente en el cambio de carga  $R_O$ .

La Fig. 22 compara ambos controles en un *start-up* y la Fig. 23 los compara en un cambio en la carga de  $R_O = 2.5 \Omega$  a  $R_O = 5 \Omega$ .

Fig. 22. Comparación del *start-up* con y sin observador.

Fig. 23. Comparación del cambio en  $R_O$  con y sin observador.

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 21 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

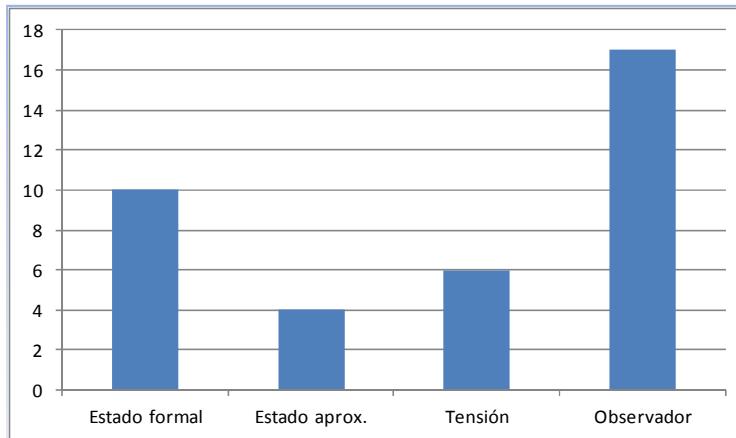

### 3.2.6 Comparativa por número de productos

Puesto que la realización de un producto consume recursos de hardware en la FPGA, se considera de interés comparar el número de productos por ciclo de conmutación en  $T_{SW}$  entre los controles presentados hasta ahora. Para esta comparación en ninguno de ellos se aplica antiwindup. Se muestra en la Fig. 24 y las leyendas significan lo siguiente

- Estado formal: visto en 3.1.

- Estado aprox.: aproximación de  $v_C$  por  $v_O$ , visto en 3.2.2.

- Tensión: compensador (3.14), visto en 3.2.4.

- Observador: observador estimador de orden total de estado y perturbación, visto en 3.2.5.

Fig. 24. Comparación por número de productos.

Para la dinámica especificada en (3.11), las prestaciones ofrecidas por el control por realimentación del estado utilizando la aproximación de  $v_C$  por  $v_O$  son muy similares a las del mismo control sin la mencionada aproximación. Sin embargo con la aproximación se tiene una gran sencillez en el cálculo. Mediante el observador se consigue una dinámica similar al control por realimentación del estado con la ventaja de no ser necesaria la medida de  $i_L$ . Como contrapartida la complejidad en el cálculo es mucho mayor.

### 3.3 Simulación en coma fija

Adoptando simplificaciones según las simulaciones realizadas hasta ahora, se realiza una simulación en coma fija definiendo los formatos numéricos de las variables. Se comprueba que con la resolución elegida en el ADC y en el PWM no hay ciclos límite y se alcanza el error cuantizado cero, esa misma resolución es la utilizada en la FPGA.

#### 3.3.1 Simplificaciones adoptadas

Se adoptan las siguientes simplificaciones:

- Instante de muestreo: punto medio de intervalo  $t_{OFF}$ , visto en 3.2.1.

- Aproximación de  $v_C$  por  $v_O$ , visto en 3.2.2.

- No se aplica antiwindup, visto en 3.2.3.

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 22 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

### 3.3.2 Formatos numéricos

La resolución adoptada en el ADC es de 8 bits y se consideran los valores de  $i_L(k)$ ,  $v_O(k)$  y  $r(k)$  como normalizados a fondo de escala y cuantizados. El formato numérico utilizado es  $< u, 8, 8 >$ .

La tensión de referencia y de fondo de escala del ADC es:

$$V_{FS} = 3.3 \text{ V.} \quad (3.25)$$

El fondo de escala de tensión es:

$$FE_V = V_{FS} = 3.3 \text{ V.} \quad (3.26)$$

La ganancia del sensor de corriente se expresa como el producto de la resistencia de medida por la ganancia del amplificador:

$$R_{SENSE} = 0.05 \Omega, G_{INA} = 50 \rightarrow G_I = R_{SENSE} * G_{INA} = 2.5 \text{ V/A.} \quad (3.27)$$

El fondo de escala de corriente es:

$$FE_I = \frac{V_{FS}}{G_I} = 1.32 \text{ A.} \quad (3.28)$$

Según (2.39) el módulo del contador digital en el modulador es  $N_C$ , así la resolución del PWM es:

$$q_{PWM} = 1/N_C = 0.002. \quad (3.29)$$

El número de bits del contador en el modulador debe ser mayor que  $\log_2(N_C)$ :

$$n_{PWM} > \log_2(N_C) = 8.9 \rightarrow n_{PWM} = 9. \quad (3.30)$$

El *duty command* se denota como  $d_C(k)$  y es el entero a comparar con el contador del modulador digital, teniendo en cuenta que  $ua(k)$  es la acción  $d(k)$  saturada como se mostró en Fig. 15:

$$d_C(k) = ua(k) * N_C, \text{ con } ua(k) \in [d_{min}, d_{max}]. \quad (3.31)$$

Como para representar  $d_C(k)$  se precisan  $n_{PWM}$  bits, se utiliza el formato  $< u, 9, 0 >$ .

La FPGA utilizada dispone de multiplicadores hardware de 18 bits, por esta razón las señales y coeficientes que intervienen en multiplicaciones se codifican en 18 bits en la escala necesaria.

Como las variables de entrada se consideran normalizadas a fondo de escala y por tanto están en el rango  $[0, 1]$ , en algún punto posterior en el esquema de bloques es necesario volver a realizar un producto por el correspondiente fondo de escala. Este producto se integra en la codificación de coeficientes.

Por simulación en reales no cuantizados se obtienen los rangos que llegan a alcanzar las variables  $d(k)$  y  $x_R(k)$ , esto permite establecer el formato numérico en que se representan:

$$x_R(k) \in [0, 60], d(k) \in (-4, 1]. \quad (3.32)$$

Se utilizan 6 cuantizadores tanto en la codificación de coeficientes como en la cuantización de variables, para ello se utilizan las funciones *quantize* y *quantizer* de *Matlab*.

El *duty command* calculado  $d_C(k)$  por el control en coma fija se aplica al modelo conmutado descrito en 2.3, de la misma forma que se ha hecho en las simulaciones en números reales presentadas a lo largo del capítulo 3. De esta manera se comprueba en simulación el correcto funcionamiento del control en coma fija con los formatos numéricos utilizados.

En [17] se lleva a cabo un estudio detallado de codificación y aritmética digital.

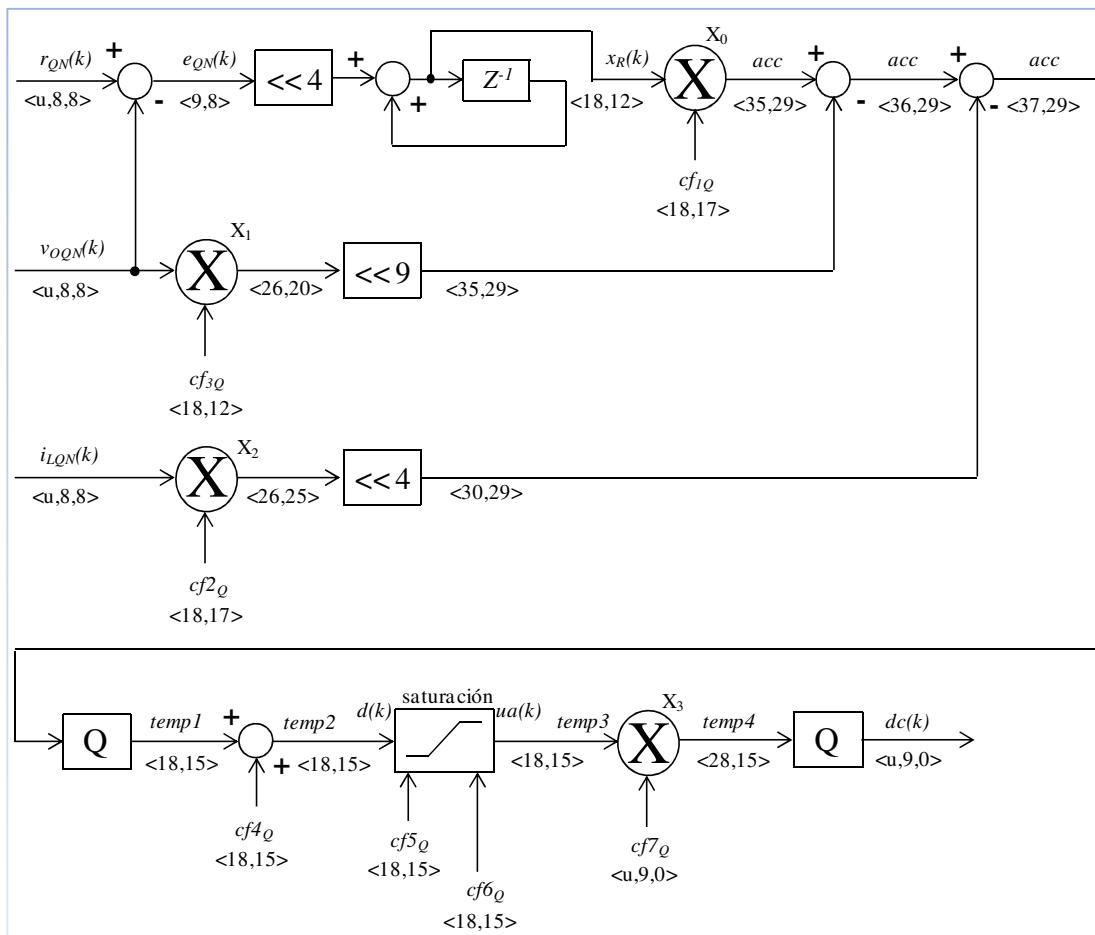

La Fig. 25 muestra el esquema de control en coma fija.

Fig. 25. Esquema de control en coma fija.

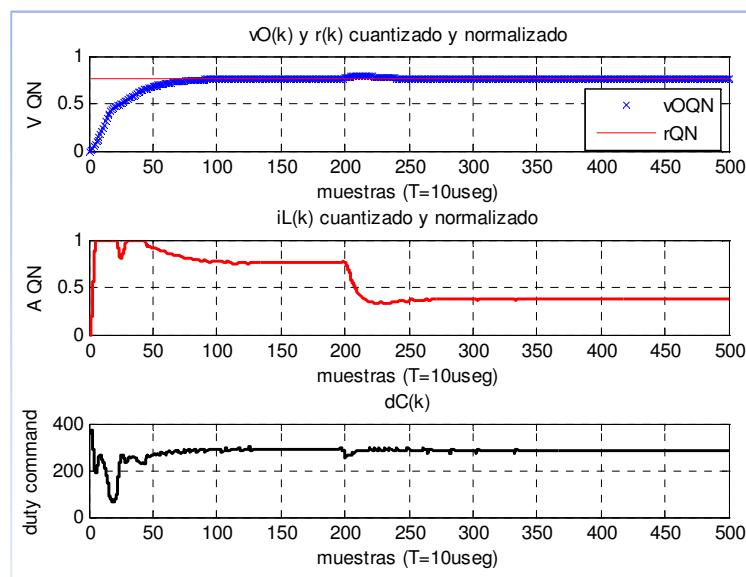

La Fig. 26 muestra la salida cuantizada y normalizada, además del *duty command* en un *start-up* y en un cambio en la carga de  $R_O = 2.5 \Omega$  a  $R_O = 5 \Omega$ .

Fig. 26. Salida cuantizada y normalizada, *duty command*.

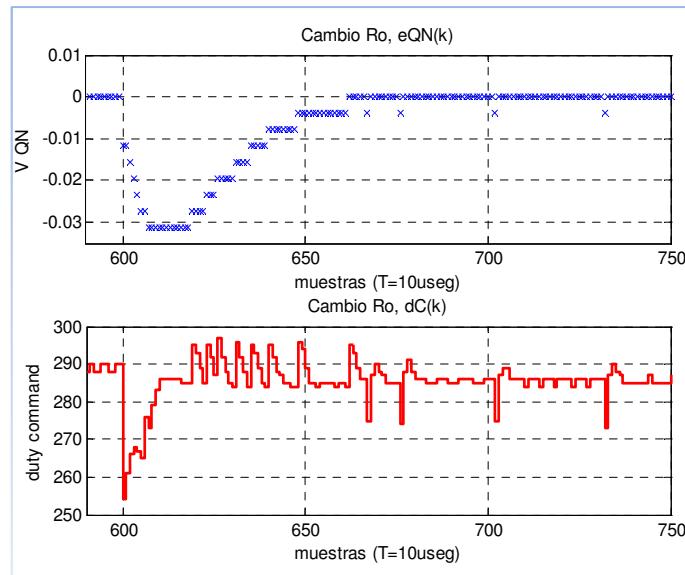

Ante un cambio en la carga de  $R_O = 2.5 \Omega$  a  $R_O = 5 \Omega$ , la Fig. 27 muestra la evolución de  $e_{QN}(k)$  y de  $d_C(k)$  donde puede observarse la obtención del error cuantizado cero y la ausencia de ciclos límite.

Fig. 27. Error cuantizado y normalizado,

*duty command*

La Fig. 28 muestra  $i_L(k)$  y  $v_O(k)$  durante el mismo transitorio de cambio en la carga de  $R_O = 2.5 \Omega$  a  $R_O = 5 \Omega$ .

Fig. 28. Salida con control en coma fija.

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 25 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

## 4 IMPLEMENTACIÓN EN FPGA

### 4.1 Testbench en VHDL

Se realiza un testbench en VHDL no sintetizable para testear el código VHDL sintetizable en la FPGA. Son necesarios dos modelados no sintetizables en VHDL, uno para el convertidor *Buck* y otro para el ADC. Para validar estos modelados se realiza una simulación del control en números reales en testbench no sintetizable.

#### 4.1.1 Modelado del convertidor conmutado

Utilizando los coeficientes  $a, b, c, d, e$  y  $f$  presentados en la 2.2.1 se obtiene el modelo de estado en continuo para cada intervalo  $t_{ON}, t_{OFF}$  y  $\Delta$ .

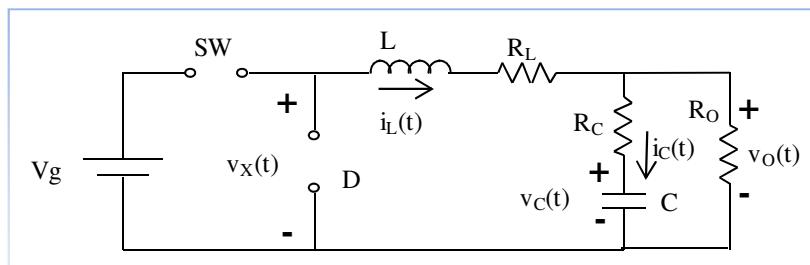

Durante los intervalos  $t_{ON}$  y  $t_{OFF}$  se aplica la ecuación dinámica (4.1) y de salida (4.2). La tensión de entrada  $v_X(t)$  toma el valor de  $V_g$  durante  $t_{ON}$  y de  $-V_F$  durante  $t_{OFF}$ . Las ecuaciones dinámica y de salida son:

$$\begin{pmatrix} \frac{di_L(t)}{dt} \\ \frac{dv_C(t)}{dt} \end{pmatrix} = \begin{pmatrix} a & b \\ c & d \end{pmatrix} \begin{pmatrix} i_L(t) \\ v_C(t) \end{pmatrix} + \begin{pmatrix} 1 \\ 0 \end{pmatrix} v_X(t) \quad (4.1)$$

$$v_O(t) = (e \quad f) \begin{pmatrix} i_L(t) \\ v_C(t) \end{pmatrix}. \quad (4.2)$$

Durante el intervalo  $\Delta$  se aplica la ecuación de estado (4.3) y de salida (4.4), la tensión de entrada  $v_X(t)$  es nula:

$$\begin{pmatrix} \frac{di_L(t)}{dt} \\ \frac{dv_C(t)}{dt} \end{pmatrix} = \begin{pmatrix} 0 & 0 \\ 0 & d \end{pmatrix} \begin{pmatrix} i_L(t) \\ v_C(t) \end{pmatrix} + \begin{pmatrix} 0 \\ 0 \end{pmatrix} v_X(t) \quad (4.3)$$

$$v_O(t) = (0 \quad f) \begin{pmatrix} i_L(t) \\ v_C(t) \end{pmatrix}. \quad (4.4)$$

(4.1) y (4.3) se discretizan en  $T_{CLK}$  utilizando el método *Euler hacia delante* obteniendo expresiones analíticas en función de la resistencia de carga  $R_O$ . Estas expresiones analíticas descritas en VHDL no sintetizable constituyen el modelo del convertidor conmutado.

Se utiliza la señal  $cG1$  como salida del modulador, ésta es utilizada por el modelado del convertidor para aplicar la ecuación de estado correspondiente a  $t_{ON}, t_{OFF}$  o  $\Delta$ . En [18] se describen alternativas de modelado en VHDL de convertidores conmutados.

#### 4.1.2 Modelado del conversor ADC

Se utilizan dos conversores ADC para la lectura de  $v_O(t)$  y  $i_L(t)$ , aunque son de 12 bits se utilizan con un número de bits  $n = 8$  tal y como se analizó en 3.3.2. Los conversores son de lectura serie mediante las señales  $SDATA$  y  $SDATA\_IL$  compartiendo las señales de selección  $nCS$  y clock  $SCLK$ .

La tensión cuantizada por bit viene dada por:

$$V_{LSB} = V_{FS} / 2^n. \quad (4.5)$$

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 26 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

Siendo  $V_{IN}$  la tensión de entrada, el resultado de la conversión en  $n$  bits es  $q$ :

$$q = \text{round} \left( \frac{V_{IN}(2^n - 1)}{V_{FS} - V_{LSB}} \right). \quad (4.6)$$

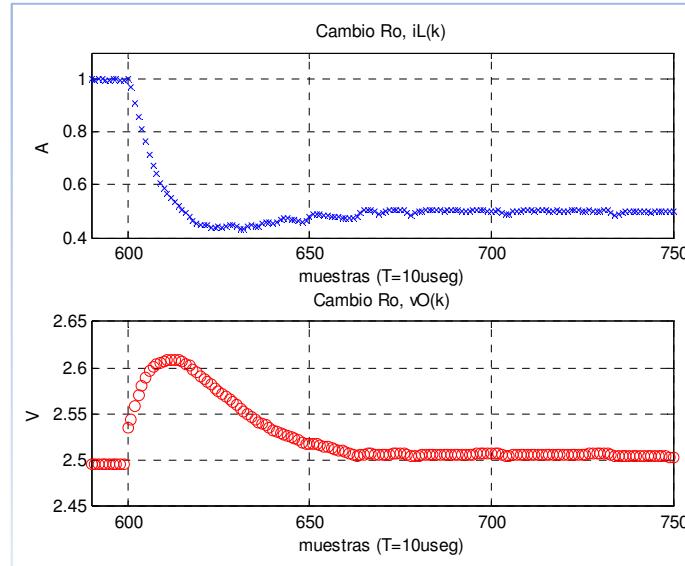

$G_I$  es la ganancia del sensor de corriente explicada en (3.27). La Fig. 29 muestra esquemáticamente el conexionado de los dos conversores ADC.

Fig. 29. Conversores ADC.

La señal *cCONV\_START* es activada por el modulador. Indica el instante en que se realiza el muestreo. El conversor ADC utilizado *ADCS7476* activa el modo *hold* con el flanco de bajada de la señal *nCS*. Las señales *VO\_ctr* y *IL\_ctr* capturan los valores de  $v_o(k)$  y  $i_L(k)$  que emplea el modelado VHDL del control en reales.

El resultado  $q$  de la conversión se almacena en las señales *conv\_aux* y *conv\_aux\_IL*, desde estas señales se copia con el retardo modelado en *TCONV* en las señales de 12 bits *DATA* y *DATA\_IL*. Éstas son argumentos de los *procedures* *write\_serial(...)* y *write\_serial\_IL(...)* que modelan el protocolo de lectura de datos del conversor ADC, respondiendo a la actividad en las líneas *nCS* y *SCLK* generada por el VHDL sintetizable.

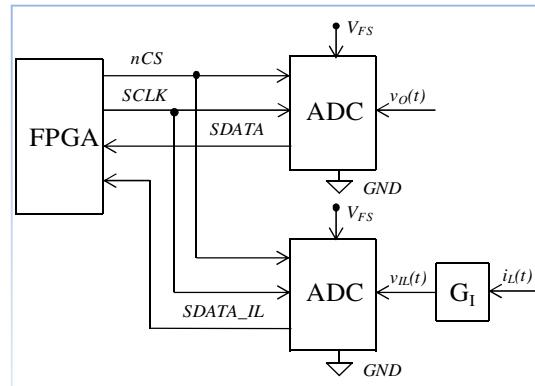

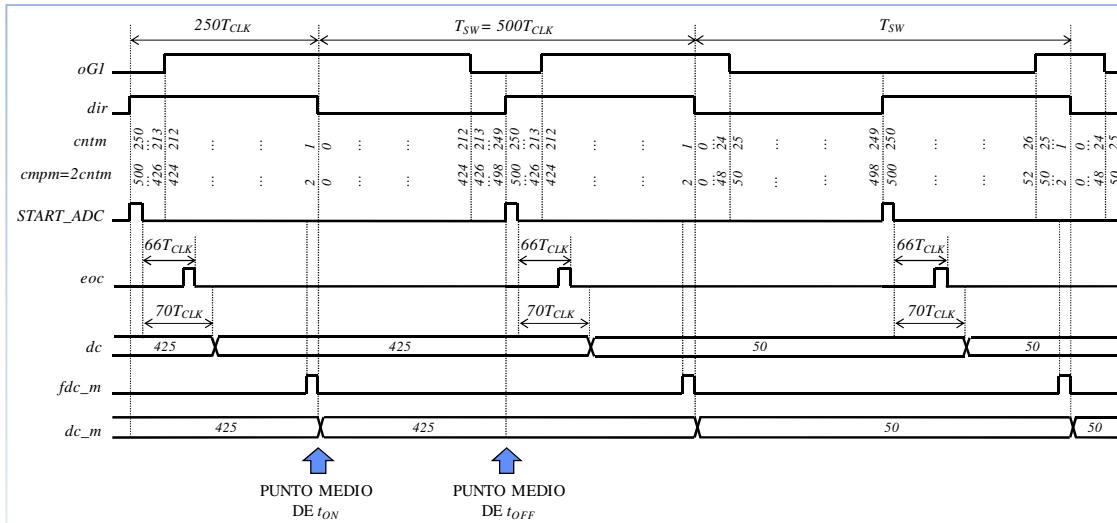

#### 4.1.3 Modelado del modulador

Se realiza el modelado en VHDL no sintetizable de un modulador *symmetric off time* con el fin de realizar una simulación del control en números reales en testbench. Como se analizó en 3.2.1, en este tipo de modulador su punto central coincide con el instante medio del intervalo  $t_{OFF}$ , donde se inicia la lectura de los conversores ADC.

En (2.39) se establece el módulo del contador digital  $N_C$  y en (3.29) la resolución  $q_{PWM}$  del PWM. El contador digital se realiza mediante la señal de 8 bits *CNTm*, la señal *DuCm* representa el *duty command* como se analizó en (3.31), la señal *DIRm* es el sentido de conteo del contador, la variable *dCNTm* establece el estado de la señal *cG1*, siendo ésta utilizada en el modelado del convertidor conmutado. La señal *cCONV\_START* inicia la lectura de los conversores ADC y la señal *cal\_DuCm* inicia el cálculo de un nuevo *duty command*.

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 27 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

La Fig. 30 ilustra el funcionamiento del modulador.

Fig. 29. Cronograma del modulador *symmetric off time*.

#### 4.1.4 Modelado del control en números reales

El modelado del modulador activa la señal *cal\_DuCm* dos ciclos de reloj después del muestreo del estado en las señales *VO\_ctr* e *IL\_ctr*. En el flanco de subida de *cal\_DuCm* se calcula el nuevo valor de *duty command*, se aplica saturación y redondeo en la conversión a una señal *DuCm* de tipo *std\_logic\_vector* de 9 bits que es comparada con el contador *CNTm* en el modelado del modulador.

#### 4.1.5 Simulación en números reales

Con la finalidad de testear el modelado del convertidor comutado y del conversor ADC, se realiza una simulación en números reales en lazo cerrado en VHDL en testbench no sintetizable, utilizando el modulador y control modelados.

La señal *nba* permite mantener el convertidor en bucle abierto y comparar el periodo de la frecuencia amortiguada del convertidor modelado en testbench con el periodo  $T_p$  (2.25) de la  $w_p$  obtenida en 2.2.2. Las formas de onda obtenidas son muy similares a las obtenidas en simulación en *Matlab* y se puede comprobar que el control alcanza la consigna.

## 4.2 Descripción en VHDL sintetizable

Dejando activos únicamente en el testbench presentado en 4.1 el modelado del convertidor comutado y del conversor ADC, se dispone de una herramienta donde testear el código VHDL sintetizable a implementar en la FPGA. Se desarrolla el control de los conversores ADC, modulador *symmetric off time*, control en coma fija e interfaz de usuario y visualización en visualizador de 7 segmentos. Finalmente se

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 28 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

realiza una simulación del control en coma fija en lazo cerrado comprobándose la obtención del error cuantizado cero y la ausencia de ciclos límite.

#### 4.2.1 Control del conversor ADC

El conexionado de los conversores ADC se ha descrito en 4.1.2 y en Fig. 29. Se comparten las señales de selección *nCS* y de clock *SCLK*, las señales de lectura serie son *SDATA* y *SDATA\_IL*.

La frecuencia máxima en la señal *SCLK* es  $f_{SCLK_{MAX}} = 20$  MHz, para conseguir este requerimiento se divide por dos  $f_{CLK}$  en la señal *enck*, esta se utiliza para hacer evolucionar una máquina de estados a partir de la cual se obtiene una señal *SCLK* de frecuencia  $f_{SCLK} = 12.5$  MHz.

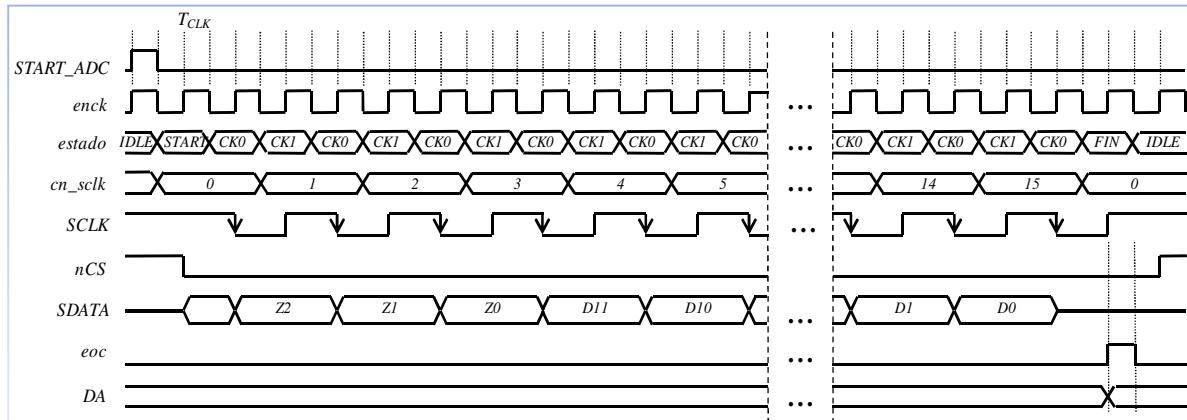

El modulador activa la señal *START\_ADC* de duración un ciclo de reloj en el punto medio del intervalo  $t_{OFF}$ , con ello se inicia la secuencia de lectura de un dato del conversor ADC. Para el control de la secuencia se utiliza una máquina de estados en la señal *estado* cuyos estados son *IDLE*, *START*, *CK0*, *CK1* y *FIN*. Tras la activación de la señal *nCS*, el conversor entrega 15 bits de datos en los siguientes 15 flancos de bajada de la señal *SCLK*, entregando el dato *D0* en el decimo quinto flanco de bajada. Para una mayor robustez las señales *nCS* y *SCLK* son registradas y no simplemente combinacionales.

Las señales *reg* y *reg\_IL* son los registros de desplazamiento de 15 bits donde se realiza el registro bit a bit de las señales de datos *SDATA* y *SDATA\_IL*. En 3.3.2 se estableció que el control utiliza muestras de  $v_o(k)$  y  $i_L(k)$  cuantizadas en 8 bits, por ello terminado el registro de los 15 bits en el estado *FIN* se realiza un truncado a 8 bits en las señales *DA* y *DA\_IL*. Un ciclo de reloj después y en el mismo estado *FIN*, se activa la señal *eoc* de duración un ciclo de reloj indicando al control que se dispone de una nueva muestra de estado.

La duración de una lectura del conversor ADC es de  $66 \cdot T_{CLK}$ . La lectura de los dos conversores se realiza de forma concurrente. La Fig. 31 muestra el cronograma para la lectura de  $v_o(k)$ .

Fig. 31. Cronograma de control del conversor ADC.

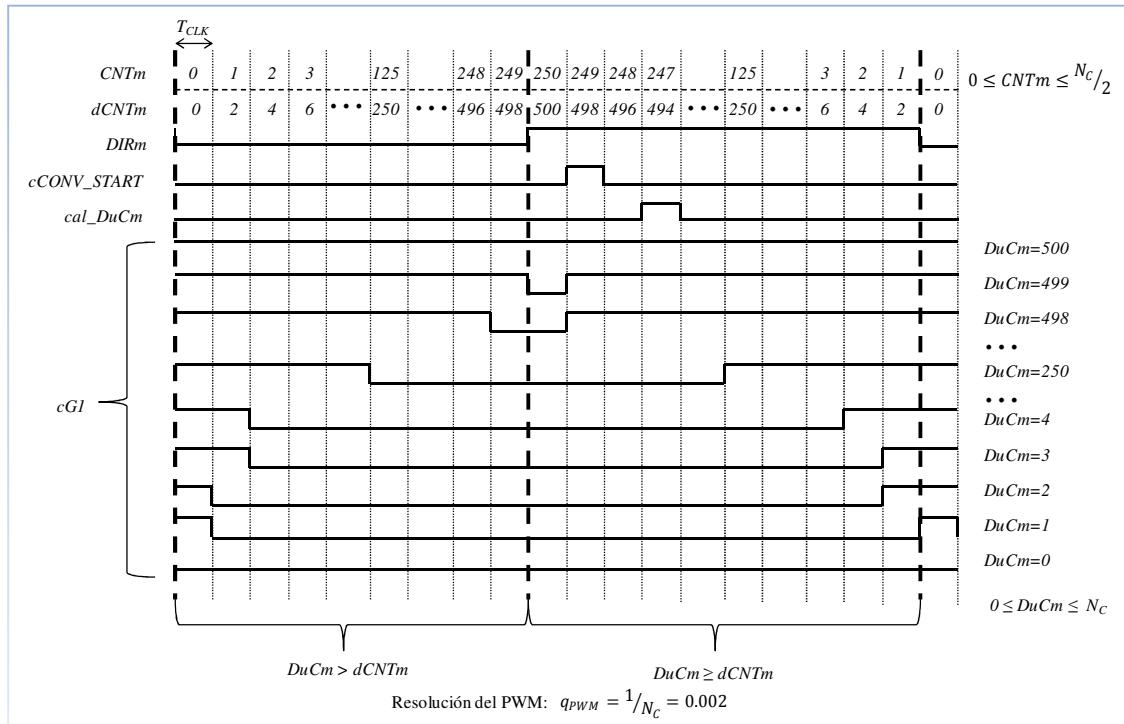

#### 4.2.2 Modulador

El módulo del contador digital  $N_C$  se definió en (2.39) y el número de bits  $n_{PWM}$  de este contador se definió en (3.30). En (3.31) se explicó que aplicando el modelo de saturación a la relación de servicio, el *duty command* se compara con el contador estableciendo el valor de salida PWM.

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 29 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

La señal registrada  $oGI$  es la salida del modulador, esta se copia a la señal  $G1$  de salida de la FPGA. La señal  $dir$  controla el sentido de conteo del contador  $cntm$ . La señal  $START\_ADC$  es activada durante un ciclo de reloj en el punto medio del  $t_{OFF}$ , indica el inicio de la secuencia de lectura del ADC. La señal  $fdc\_m$  es activada durante un ciclo de reloj en el punto medio del  $t_{ON}$  e indica el registro en la señal  $dc$ ,  $dc\_m$  es el entero a comparar con el contador  $cntm$ .

En 4.2.1 se analizó que la lectura del ADC se prolonga durante  $66 \cdot T_{CLK}$  desde la activación de  $START\_ADC$  en el punto medio del  $t_{OFF}$ , a estos hay que añadir  $4 \cdot T_{CLK}$  dedicados por el control al cálculo del *duty command* (ver 4.2.3) y su registro en  $dc$ . Puesto que el posterior registro en  $dc\_m$  se realiza en el punto medio del  $t_{ON}$  esto supone que se dispone de  $\binom{N_c}{2} \cdot T_{CLK}$  para la lectura del ADC y cálculo del control, así pues se cumple:

$$(66 + 4) \cdot T_{CLK} = 70 \cdot T_{CLK} < \binom{N_c}{2} \cdot T_{CLK} = 250 \cdot T_{CLK}. \quad (4.7)$$

La anchura del mínimo *duty command* es de  $50 \cdot T_{CLK}$  debido a la saturación de la acción  $d_{min}$  como se expuso en (3.12), registrando en el punto medio del  $t_{ON}$  se elimina la posibilidad de que la señal PWM cambie de forma inmediata tras hacer el nuevo registro de *duty command*.

La Fig. 32 describe el funcionamiento del modulador.

Fig. 32. Modulador *symmetric off time*.

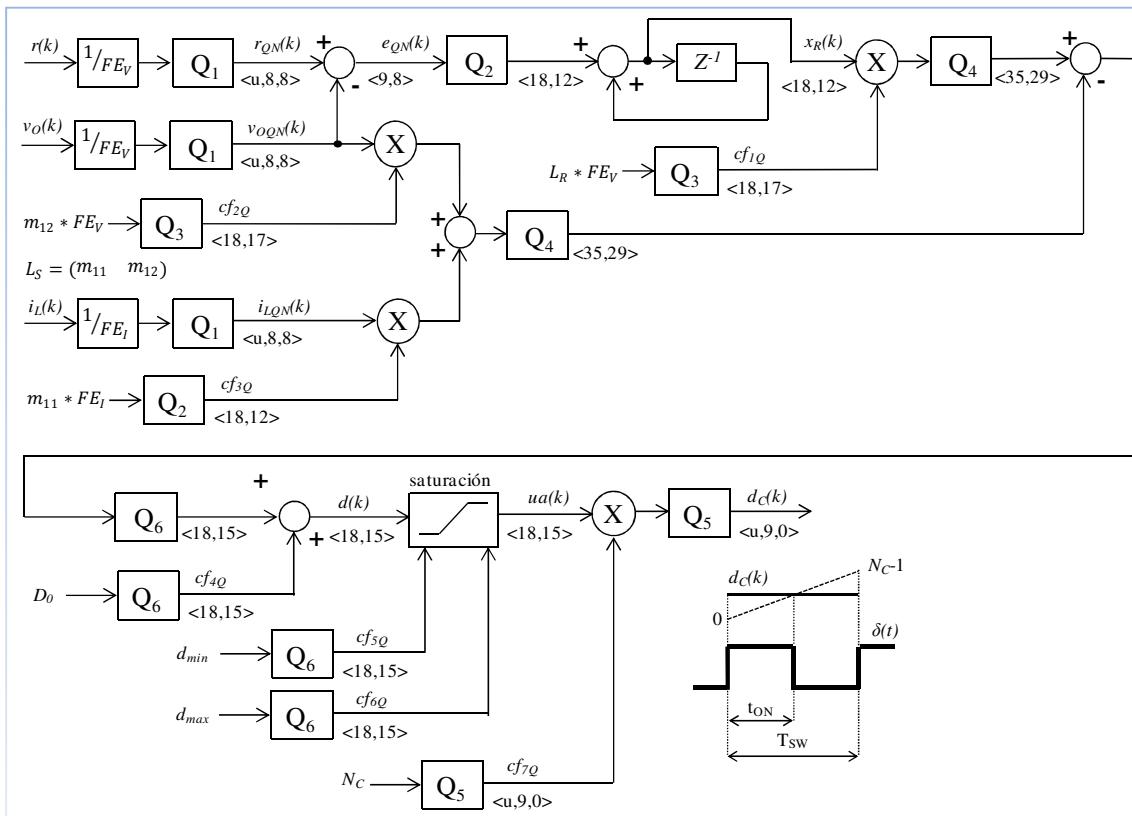

#### 4.2.3 Control y formatos numéricos

Se describe en VHDL sintetizable el esquema de control por realimentación de estado aplicando la aproximación de  $v_C(k)$  por  $v_O(k)$ . La única muestra previa necesaria es la del integrador  $x_R(k-1)$ . Los rangos del integrador  $x_R(k)$  y de la acción no saturada  $d(k)$  se conocen por simulación como se vió en (3.32).

Como se explicó en 3.3.2 las variables  $i_L(k)$  y  $v_O(k)$  se consideran normalizadas a fondo de escala, estas se tienen en las señales  $DA$  y  $DA\_iL$  como salida del ADC. Operando con  $r(k)$  y  $v_O(k)$  se calcula el error en la señal combinacional  $e$ .

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 30 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

La FPGA utilizada dispone de multiplicadores hardware de 18 bits, por ello las señales y coeficientes que participan en productos están codificados en 18 bits a la escala necesaria. Los coeficientes  $cf1Q$ ,  $cf2Q$ ,  $cf3Q$ ,  $cf4Q$ ,  $cf5Q$ ,  $cf6Q$  y  $cf7Q$  son los presentados en Fig. 25 codificados en enteros.

En la simulación en coma fija descrita en 3.3.2 se ha obtenido el número real representado  $\hat{U}_R$  por medio de la función *quantize*, además se obtiene el entero  $U$  que representa a  $\hat{U}_R$  con la expresión:

$$U = \frac{\hat{U}_R}{2^{-Q}} \quad (4.8)$$

Siendo  $Q$  la escala a la que está representado el número real  $U_R$ . Se introduce un error  $\varepsilon$  de cuantificación que dependerá del número de bits utilizados para representar el número,  $\varepsilon$  se expresa como:

$$\varepsilon = U_R - \hat{U}_R. \quad (4.9)$$

En VHDL el entero  $U$  se convierte en un objeto de tipo *signed* utilizando la correspondiente función de conversión:

```

constant cf1: signed(17 downto 0) := conv_signed(37229, 18); --

s,18,2^-17, 0.284034729

```

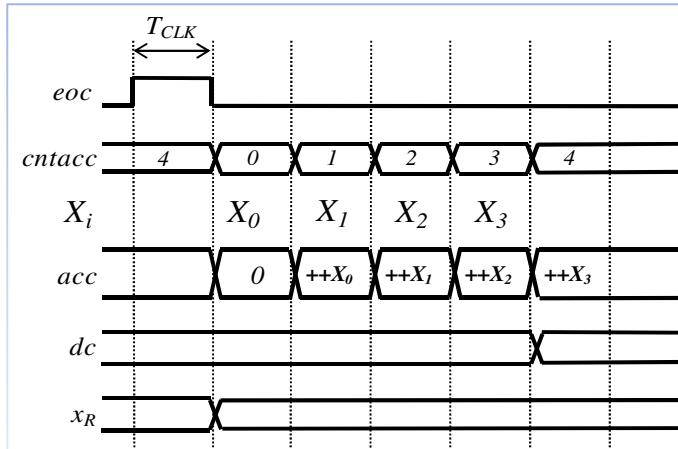

En el esquema de control de Fig. 33 se realizan 4 productos, estos se efectúan de manera que únicamente se ejecuta un producto por ciclo  $T_{CLK}$ . La señal  $acc$  actúa de acumulador y en ella son acumulados los cuatro productos. Esta secuencia se controla mediante el contador  $cntacc$  de módulo 4, por ello el control demora  $4 \cdot T_{CLK}$  en realizar el cálculo del *duty command* y registrarlo en la señal  $dc$  de 9 bits.

Fig. 33. Esquema de control en coma fija en VHDL sintetizable.

|                                             |                                                                                         |                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|

| Alumno:<br>Roberto Velázquez<br>NIA: 327988 | Memoria Trabajo de Fin de Máster                                                        | Página 31 de 52 |

|                                             | Control digital de un convertidor <i>Buck</i> mediante realimentación lineal del estado |                 |

En los productos denotados como  $X_i$  en Fig. 33, el subíndice  $i$  indica el valor del contador  $cntacc$  durante el ciclo de reloj en el que se efectúa el producto  $X_i$ .

Cuando  $eoc$  está activa y con anterioridad al inicio de la secuencia acumulativa se registra el integrador  $x_R$ , en este ciclo de reloj las señales  $DA$  y  $DA_{iL}$  resultado de la lectura de los ADC ya han sido registradas, como se muestra en Fig. 31. La Fig. 34 muestra la secuencia acumulativa en  $acc$  según el contador  $cntacc$ .

Fig. 34. Acumulador.

#### 4.2.4 Interfaz de usuario

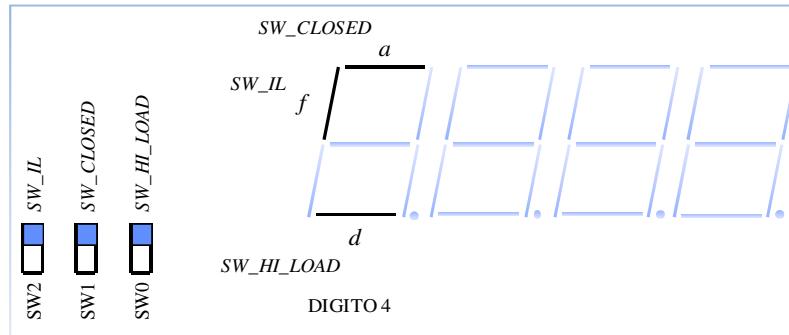

Se realiza el código VHDL sintetizable que permite una interacción con el usuario mediante los interruptores y visualizadores de 7 segmentos de la tarjeta de evaluación de la FPGA. Se utilizan los interruptores SW0, SW1 y SW2. Se utilizan cuatro visualizadores, en los tres primeros se visualiza  $v_o(t)$  o  $i_L(t)$  con una precisión de dos decimales, el cuarto es usado para mostrar información adicional activando algunos de sus segmentos.

A partir de las señales  $DA$  y  $DA_{iL}$  resultado de la lectura de los conversores ADC, mediante tabla combinacional se obtienen las señales de 12 bits  $DO$  y  $DO_{iL}$  codificadas en BCD. Siendo  $n = 8$  el número de bits del conversor ADC como se analizó en 3.3.2, la tabla combinacional tiene un total de  $2^n$  valores. Para visualizar corriente en centésimas de amperio, con  $q$  resultado de la conversión y  $FE_I$  fondo de escala de corriente definido en (3.28), cada valor de la tabla se calcula con la expresión:

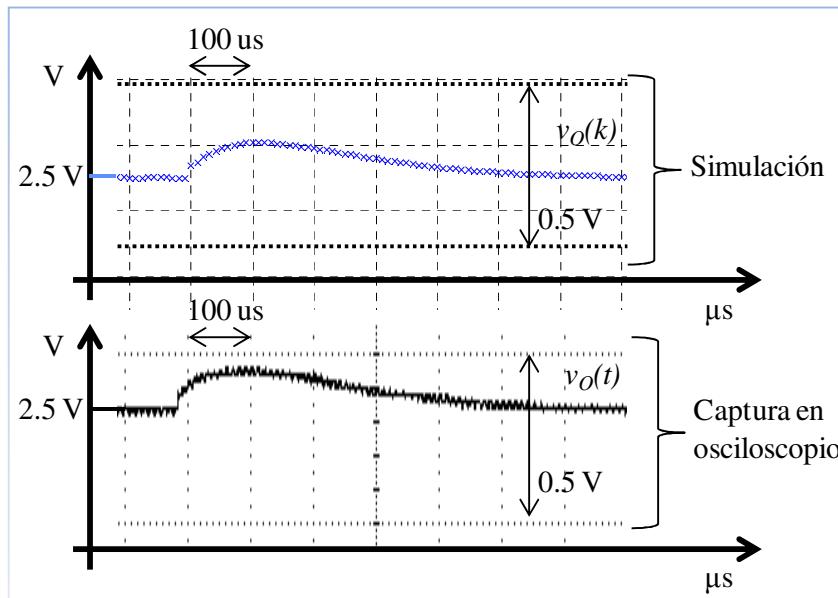

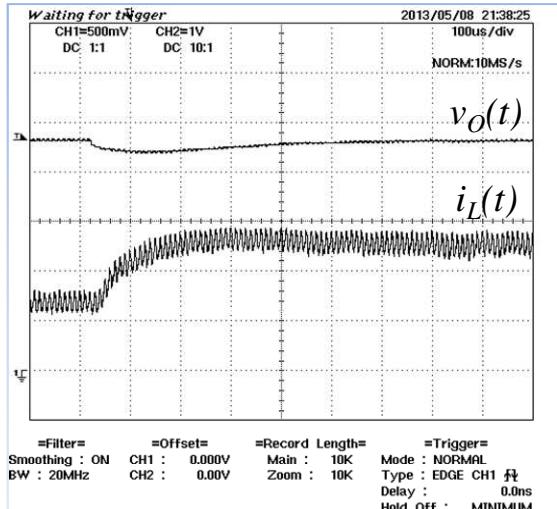

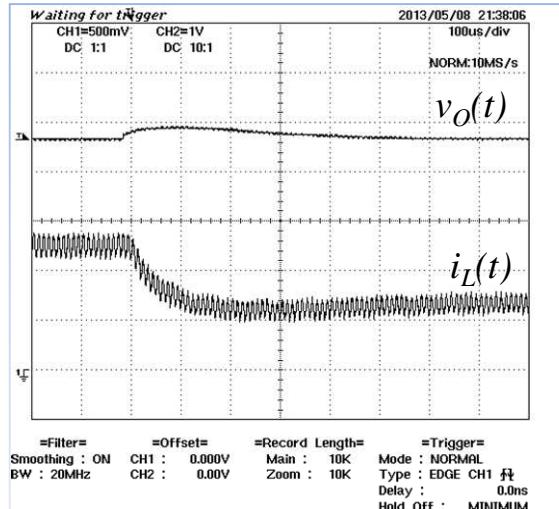

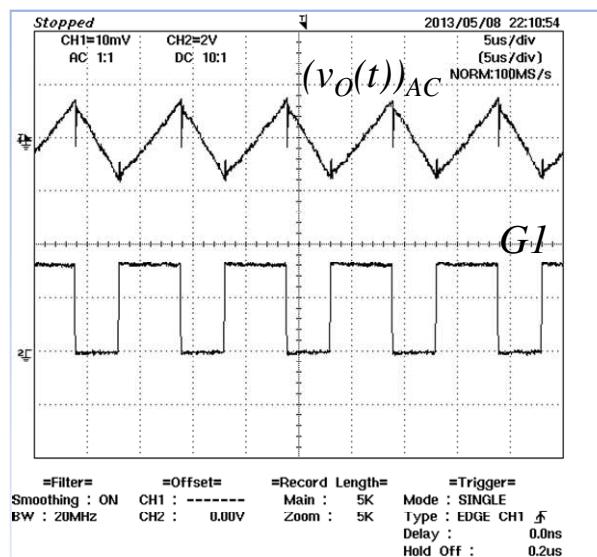

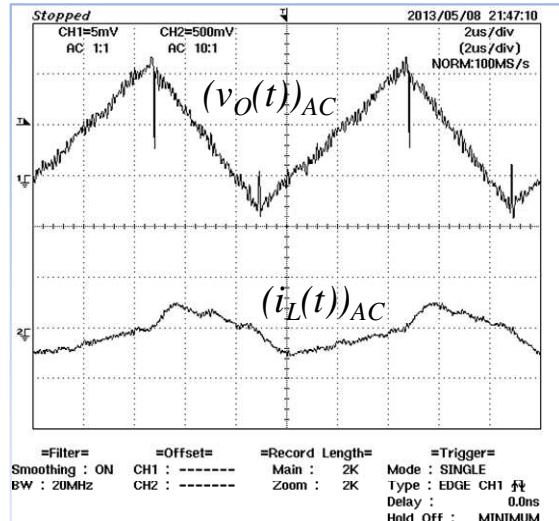

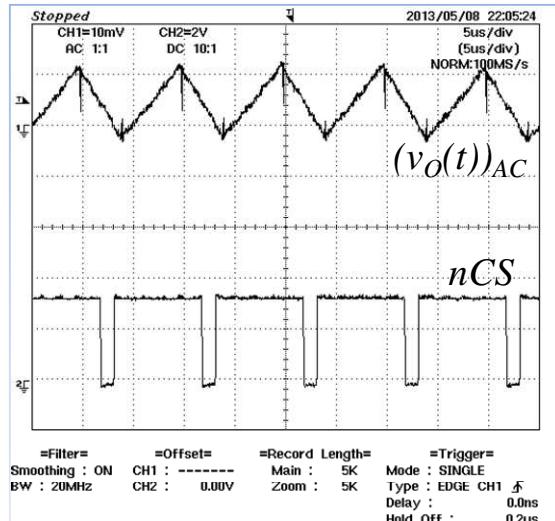

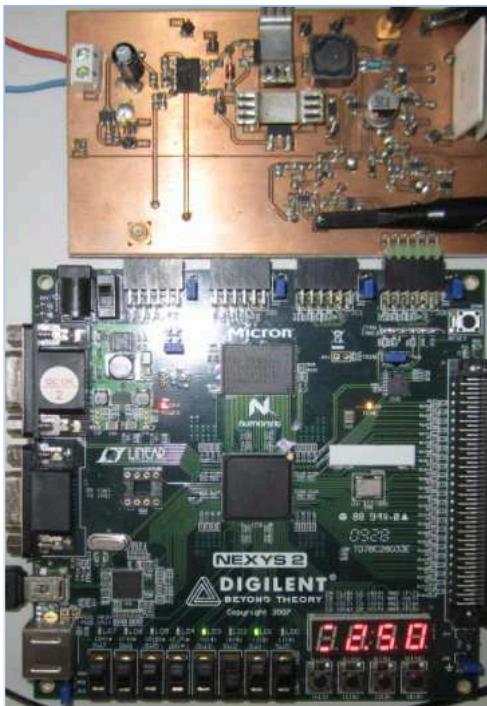

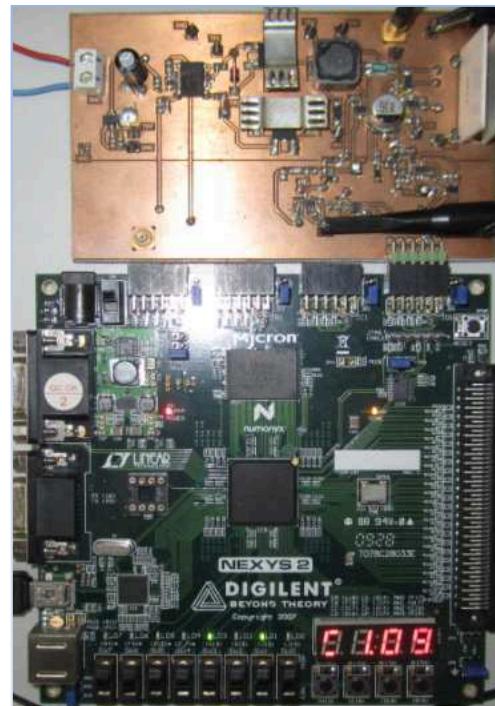

$$I_{IN} = \text{round}(100 \cdot q \cdot FE_I). \quad (4.10)$$