## Trabajo Fin de Máster

Control en FPGA de un convertidor reductor en modo corriente de pico

Autor

José Manuel Iguaz Navarro

Director/es

José Ignacio Artigas

Luis Ángel Barragán

EINA

2013

## Listado de símbolos y acrónimos

**( $i_L$ )<sub>Av</sub>**: Corriente media por la bobina del convertidor.

**( $i_L$ )<sub>max</sub>**: Corriente máxima por la bobina del convertidor.

**( $i_L$ )<sub>min</sub>**: Corriente mínima por la bobina del convertidor.

**( $V_o$ )<sub>max</sub>**: Tensión máxima a la salida del convertidor.

**( $V_o$ )<sub>min</sub>**: Tensión mínima a la salida del convertidor.

**A/D**: Analógico Digital.

**ACC**: Acumulador de la celda de multiplicación y acumulación del regulador.

**BCD**: *Binary Coded Decimal*.

**C**: Condensador del filtro de salida del convertidor.

**C<sub>1</sub>**: Condensador del primer filtro paso bajo a la salida del control.

**C<sub>2</sub>**: Condensador del segundo filtro paso bajo a la salida del control.

**CH1**: Canal 1 del osciloscopio usado para realizar las medidas experimentales.

**CH2**: Canal 2 del osciloscopio usado para realizar las medidas experimentales.

**D/A**: Digital Analógico.

**D**: Ciclo de servicio.

**EINA**: Escuela de Ingeniería y Arquitectura.

**EMC**: *Electromagnetic Compatibility*.

**ESR**: *Equivalent Serial Resistance*.

**f<sub>c</sub>**: frecuencia de cruce del sistema a controlar.

**FM**: Ganancia del modulador.

**F<sub>max</sub>**: Fase máxima aportada por el regulador.

**FPGA**: *Field Programmable Gate Array*.

**f<sub>sw</sub>**: Frecuencia de conmutación del convertidor.

**G<sub>i</sub>**: Función de transferencia de corriente del convertidor.

**i<sub>L</sub>**: Corriente en la bobina L.

**$i_o$** : Corriente a la salida del convertidor.

**$I_{REF}$** : Corriente de referencia del control.

**K**: Constante del regulador tipo II-b.

**L**: Bobina del filtro de salida del convertidor.

**MAC**: Multiplicación y acumulación.

**Matlab**: *Matrix laboratory*.

**$m_e$** : Pendiente de la rampa de compensación.

**MF**: Margen de fase del sistema en lazo cerrado.

**$m_{off}$** : Pendiente de la corriente en el estado *off* del transistor.

**$m_{on}$** : Pendiente de la corriente en el estado *on* del transistor.

**MOSFET**: *Metal Oxide-Semiconductor Field-Effect Transistor*.

**PAF**: Proporcional en Avance de Fase.

**PCB**: *Printed Circuit Board*.

**$P_{D_{cond}}$** : Pérdidas del diodo de libre circulación del convertidor en conducción.

**$P_{D_{sw}}$** : Pérdidas del diodo de libre circulación del convertidor en conmutación.

**PMOD**: *Peripheral Module*.

**PRF**: Proporcional en Retraso de Fase.

**$P_{T_{cond}}$** : Pérdidas del transistor MOSFET del convertidor en conducción.

**$P_{T_{sw}}$** : Pérdidas del transistor MOSFET del convertidor en conmutación.

**PWM**: *Pulse Width Modulation*.

**Q**: Designación para el transistor del convertidor.

**q**: Número de bits de la parte decimal de una señal tipo signed.

**R**: Regulador tipo II-b.

**$R_1$** : Resistencia del primer filtro paso bajo a la salida del control..

**$R_2$** : Resistencia del segundo filtro paso bajo a la salida del control.

**$R_c$** : Resistencia interna serie del condensador (ESR).

**$R_{DS(on)}$** : Resistencia en conducción del transistor MOSFET del convertidor.

**R<sub>i</sub>**: Ganancia de la medida de corriente.

**R<sub>L</sub>**: Resistencia de la carga del convertidor.

**s**: variable continua del campo transformado de Laplace.

**SMD**: *Surface Mounted Device*.

**T<sub>A</sub>**: Temperatura ambiente del sistema.

**T<sub>A</sub>**: Temperatura ambiente.

**t<sub>adc</sub>**: tiempo requerido por el conversor A/D para la conversión de datos.

**T<sub>CLK</sub>**: Periodo del reloj interno de la FPGA.

**t<sub>GC</sub>**: tiempo requerido por el regulador para realizar sus operaciones.

**T<sub>sw</sub>**: Periodo de conmutación del convertidor.

**V<sub>C</sub>**: Tensión en el condensador C.

**V<sub>D</sub>**: Tensión en conducción del diodo de libre circulación del convertidor.

**VHDL**: *VHSIC Hardware Description Language*.

**V<sub>i</sub>**: Tensión a la entrada del convertidor.

**V<sub>L</sub>**: Tensión en la bobina L.

**V<sub>o</sub>**: Tensión a la salida del convertidor.

**V<sub>REF</sub>**: Tensión de referencia del control.

**V<sub>sat</sub>**: Tensión de saturación del transistor MOSFET del convertidor.

**w**: Número total de bits de una señal tipo signed.

**w<sub>p</sub>**: Frecuencia angular del polo del regulador tipo II-b.

**w<sub>z</sub>**: Frecuencia angular del cero del regulador tipo II-b.

**z**: variable del campo transformado en tiempo discreto.

**Z<sub>o</sub>**: Impedancia equivalente a la salida del convertidor.

**θ<sub>JAD</sub>**: Impedancia térmica unión ambiente del diodo de libre circulación del convertidor.

**θ<sub>JAT</sub>**: Impedancia térmica unión ambiente del transistor MOSFET del convertidor.

**Δi<sub>o</sub>**: Rizado de corriente en la bobina del convertidor.

**Δv<sub>o</sub>**: Rizado de tensión a la salida del convertidor.

# Contenido

|       |                                                    |    |

|-------|----------------------------------------------------|----|

| 1     | Introducción .....                                 | 7  |

| 1.1   | Objetivo del trabajo .....                         | 7  |

| 1.2   | Estado del arte .....                              | 7  |

| 1.3   | Descripción general del sistema desarrollado ..... | 9  |

| 2     | Diseño del control .....                           | 11 |

| 2.1   | Modelado del convertidor .....                     | 11 |

| 2.2   | Control por corriente de pico .....                | 12 |

| 2.3   | Modelado del control .....                         | 13 |

| 2.3.1 | Lazo de corriente .....                            | 13 |

| 2.3.2 | Lazo de tensión .....                              | 14 |

| 2.4   | Ajuste del regulador mediante Matlab .....         | 15 |

| 2.5   | Implementación en Matlab/Simulink .....            | 16 |

| 2.5.1 | Modelo continuo .....                              | 16 |

| 2.5.2 | Modelo discreto .....                              | 19 |

| 3     | Implementación en FPGA .....                       | 25 |

| 3.1   | Modelo del hardware no sintetizable en VHDL .....  | 25 |

| 3.2   | Diseño del control digital en VHDL .....           | 26 |

| 3.2.1 | Control ADC .....                                  | 27 |

| 3.2.2 | Regulador tipo II-b .....                          | 28 |

| 3.2.3 | Rampa digital de compensación .....                | 29 |

| 3.2.4 | Conversor DA sigma-delta de segundo orden .....    | 29 |

| 3.2.5 | Biestable RS .....                                 | 30 |

| 3.2.6 | Arranque del convertidor suave (Soft start) .....  | 30 |

| 3.3   | Resultados simulación en Modelsim .....            | 30 |

| 4     | Resultados experimentales .....                    | 33 |

| 5     | Conclusiones y trabajo futuro .....                | 37 |

|       | Anexos .....                                       | 39 |

| 1.    | Diseño del convertidor .....                       | 39 |

| 2.    | Modelado del convertidor .....                     | 43 |

| 3.    | Funcionamiento del control .....                   | 47 |

| 4.    | Modelado del control .....                         | 53 |

| 5.    | Simulación del control en Matlab/Simulink .....    | 57 |

|    |                                                              |    |

|----|--------------------------------------------------------------|----|

| 6. | Discretización del modelo del buck y del filtro pasivo ..... | 69 |

| 7. | Código VHDL del control y del hardware del buck .....        | 71 |

| 8. | Diseño de la PCB del convertidor .....                       | 87 |

|    | Bibliografía.....                                            | 95 |

# 1 Introducción

## 1.1 Objetivo del trabajo

El control en modo corriente de pico de convertidores continua-continua implementa dos lazos, uno interno de corriente y otro externo de tensión. Es uno de los más utilizados en las fuentes de alimentación conmutadas ya que limita la corriente de forma inherente y mejora la regulación respecto al control en modo tensión.

La mayor parte de los controles en modo corriente de pico se implementan analógicamente. El objetivo del presente trabajo es realizar un control digital de un convertidor reductor en modo corriente de pico. Este control incluye la técnica de control en modo tensión que ha sido visto en la asignatura "Control Digital de Etapas Electrónicas de Potencia" y complementa la formación recibida en el máster.

El control digital se describirá en VHDL y se implementará en una FPGA. Deberá incluir una rampa de compensación para que el funcionamiento sea estable para ciclo de trabajo mayor o igual que 0.5. El regulador digital elegido para el lazo externo de tensión será de tipo II. Su función de transferencia presenta un cero y dos polos, uno de los polos se posiciona en el origen para asegurar error de posición nulo.

Uno de los retos en la implementación de un control digital en modo corriente de pico es la comparación entre la rampa de compensación y la corriente por el inductor. Esta corriente cambia desde un valor mínimo hasta su valor máximo cada ciclo de conmutación. Una implementación digital de la comparación entre la rampa de compensación y la corriente, requeriría muestrear la corriente con un conversor A/D de gran ancho de banda. Por consiguiente, en este trabajo se analizarán alternativas que sean válidas para su implementación en FPGA.

Una vez diseñado e implementado el control, se elegirán los componentes del convertidor reductor y se diseñará una placa de circuito impreso para su implementación. Por último, se realizarán medidas experimentales y se compararán con las simulaciones obtenidas.

## 1.2 Estado del arte

Los convertidores continua-continua son sistemas variantes en el tiempo y su comportamiento es no lineal. Para poder realizar el diseño de controles lineales, modelos promediados de dichos convertidores han sido desarrollados en [1], pp. 187-213, mediante los que se ha obtenido un modelo lineal, a partir de la determinación de su función de transferencia en pequeña señal. Para ello la pequeña señal es considerada sobre el valor promedio de las variables en un periodo de conmutación.

A la hora de realizar un control sobre un convertidor de potencia, es necesario saber si la corriente se va a anular en algún momento o no. Con esta premisa, se tienen modelos promediados para modo de conducción continuo (CCM) y para modo de conducción discontinuo (DCM). En ambos modos el ciclo de servicio es la acción de entrada al modelo del

convertidor. Estando en CCM, aparte de la dependencia de las no idealidades de los componentes del convertidor, la relación existente entre la tensión de salida y la de entrada del convertidor depende del ciclo de servicio. En DCM depende dicho ciclo, de la frecuencia de conmutación y de la carga.

En cuanto al modo de controlar los convertidores existen dos variantes básicas al respecto, el control en modo tensión y el control en modo corriente. En función del modo de control, la función de transferencia a extraer relaciona distintas variables. En el control de tensión la relación se da entre el ciclo de servicio y la tensión de salida, mientras que en el control de corriente se da entre el ciclo de servicio y la corriente que circula por la bobina del convertidor.

En [1], pp. 187-213, se presenta el control tradicional en modo tensión, el cual tiene una única realimentación con la tensión de salida. En [2] y en [3] se ha desarrollado una variante del control de tensión mediante la realimentación lineal del estado. El control por realimentación del estado toma mayor importancia cuando el convertidor a controlar no es estable realimentando únicamente en tensión, un caso de este tipo se desarrolla en [4].

El control en modo corriente puede realizarse mediante la técnica basada en el control de la corriente media, la cual se describe en [5], en [6] y en [7].

En [8] se desarrolla un control mixto de tensión y corriente que ofrece un mejor comportamiento que un control PI convencional.

En [9] se implementa un manejo del convertidor buck con varios modos de control según la evolución del convertidor, mejorando la respuesta frente a la aplicación de un solo modo de control de corriente o de tensión.

En ese contexto, se plantea otro posible control de corriente basado en la regulación del pico de la misma en modo CCM. En [1], pp. 439-473, se describe el control tradicional en modo corriente de pico, en el que se necesitan dos lazos de realimentación, uno de la tensión de salida y otro de la corriente por la bobina. Este control presenta la desventaja del doble lazo de realimentación frente al control de tensión y una inestabilidad para un ciclo de servicio superior o igual a 0.5, siendo necesaria la inclusión de una rampa adicional de compensación, para poder variar el ciclo de servicio en todo su rango.

En [1], pp. 449-473, en [10], en [11] y en [12], se plantea como realizar la extracción de la función de transferencia del convertidor en modo corriente de pico, aproximándola a un primer orden, presentando una clara ventaja ante el segundo orden resultante del control de tensión, de cara a la determinación del regulador que interviene en el mismo.

La mayoría de los controles en modo corriente de pico, se suelen realizar de manera analógica [13], implementando tanto el regulador como la rampa de compensación mediante integrados electrónicos y elementos pasivos. Por este motivo, la implementación analógica presenta un elevado coste en el diseño de la placa de circuito impreso del convertidor, siendo una clara desventaja en este aspecto.

Una solución a este problema se describe en [14], donde el regulador y la rampa de compensación se han realizado de manera digital, pudiendo diseñar tantas veces como se

desea ambos elementos. Dicha solución presenta inconvenientes frente al control analógico, siendo uno de ellos la resolución finita del control digital frente a la resolución infinita del analógico. Otra de las desventajas que presenta, es la inclusión de un conversor DA hardware de gran ancho de banda para reconstruir la referencia de corriente compensada, lo que implica un aumento en el coste del diseño del convertidor.

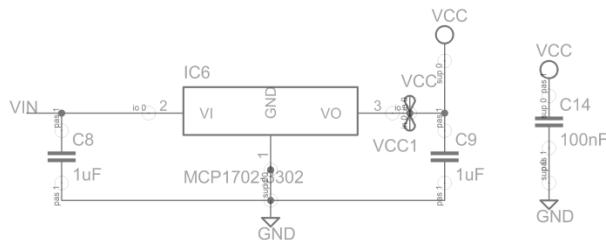

En el presente trabajo se propone una alternativa al conversor DA hardware, mediante la implementación de un conversor DA sigma-delta ( $\Sigma\Delta$ ) de segundo orden digital en FPGA, el cual se ha modelado como viene explicado en [15]. Para reconstruir la señal proporcionada por el conversor, bastará con incluir un filtro paso bajo pasivo, que en comparación con el conversor DA hardware resulta más económico.

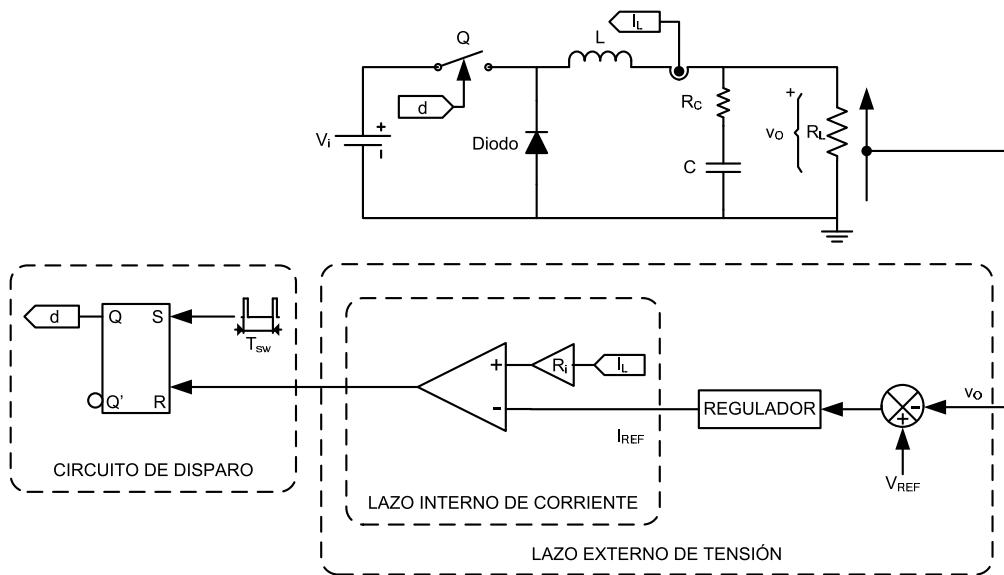

### 1.3 Descripción general del sistema desarrollado

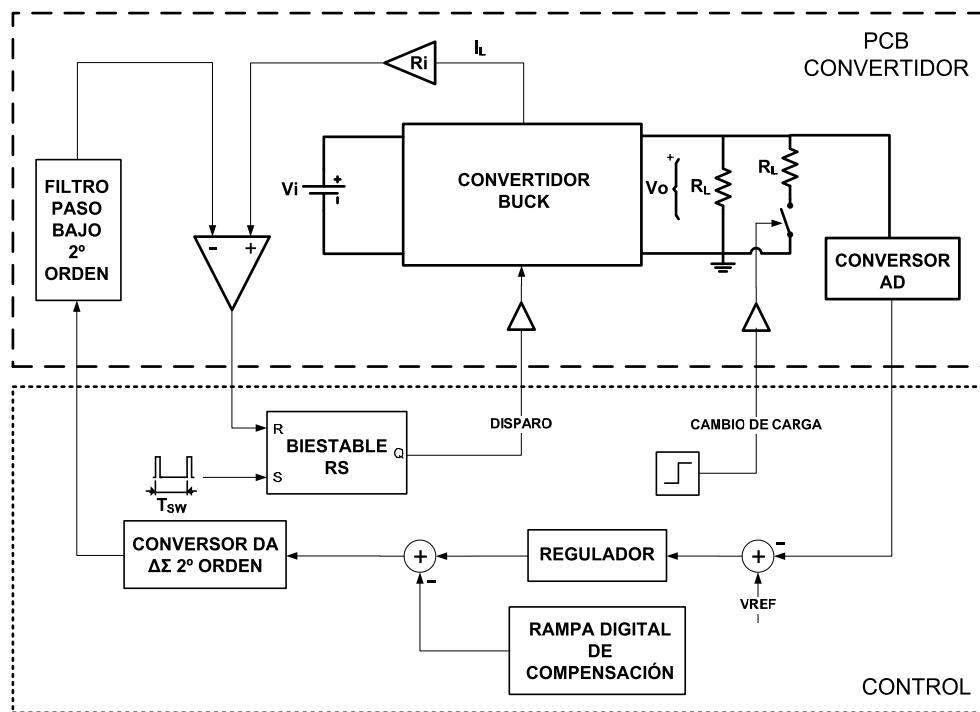

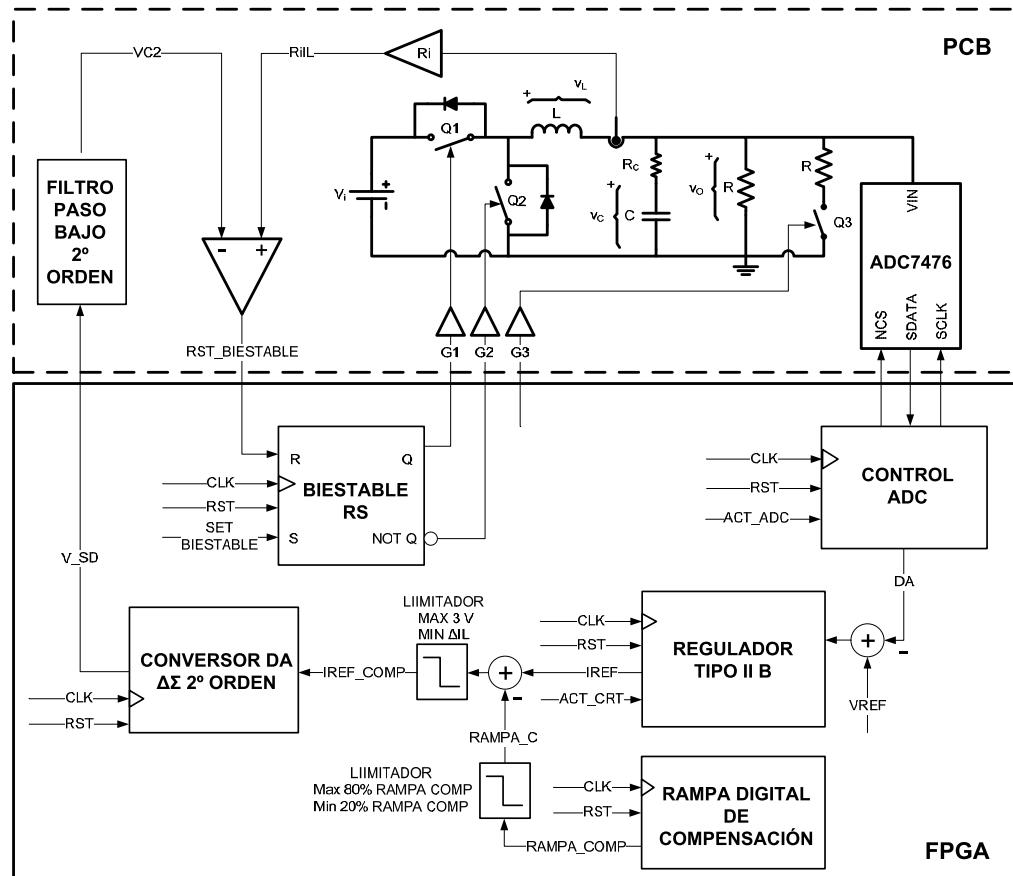

En términos generales, el sistema desarrollado en el presente trabajo se observa en la Figura 1.

Figura 1 Diagrama de bloques genérico del trabajo realizado (Software y hardware).

Analizándola se observan dos partes importantes:

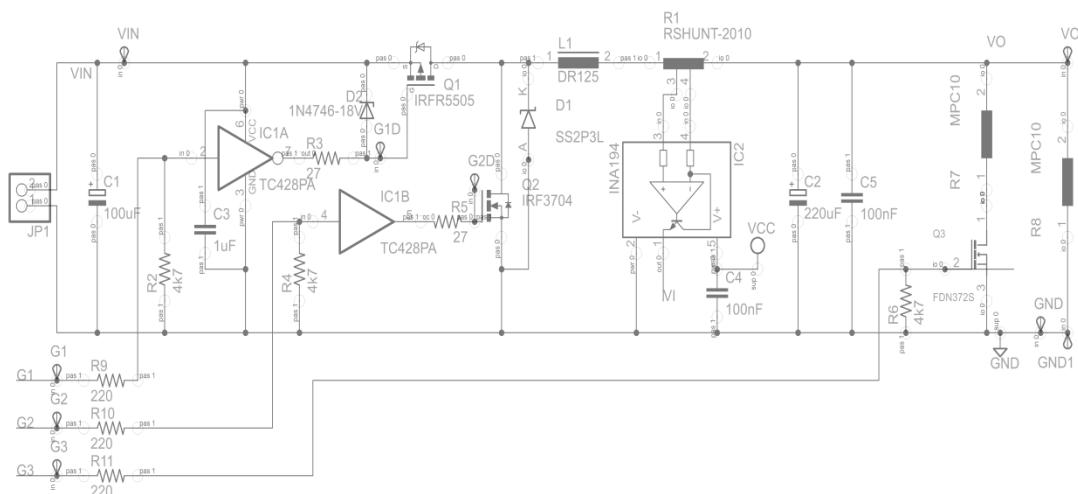

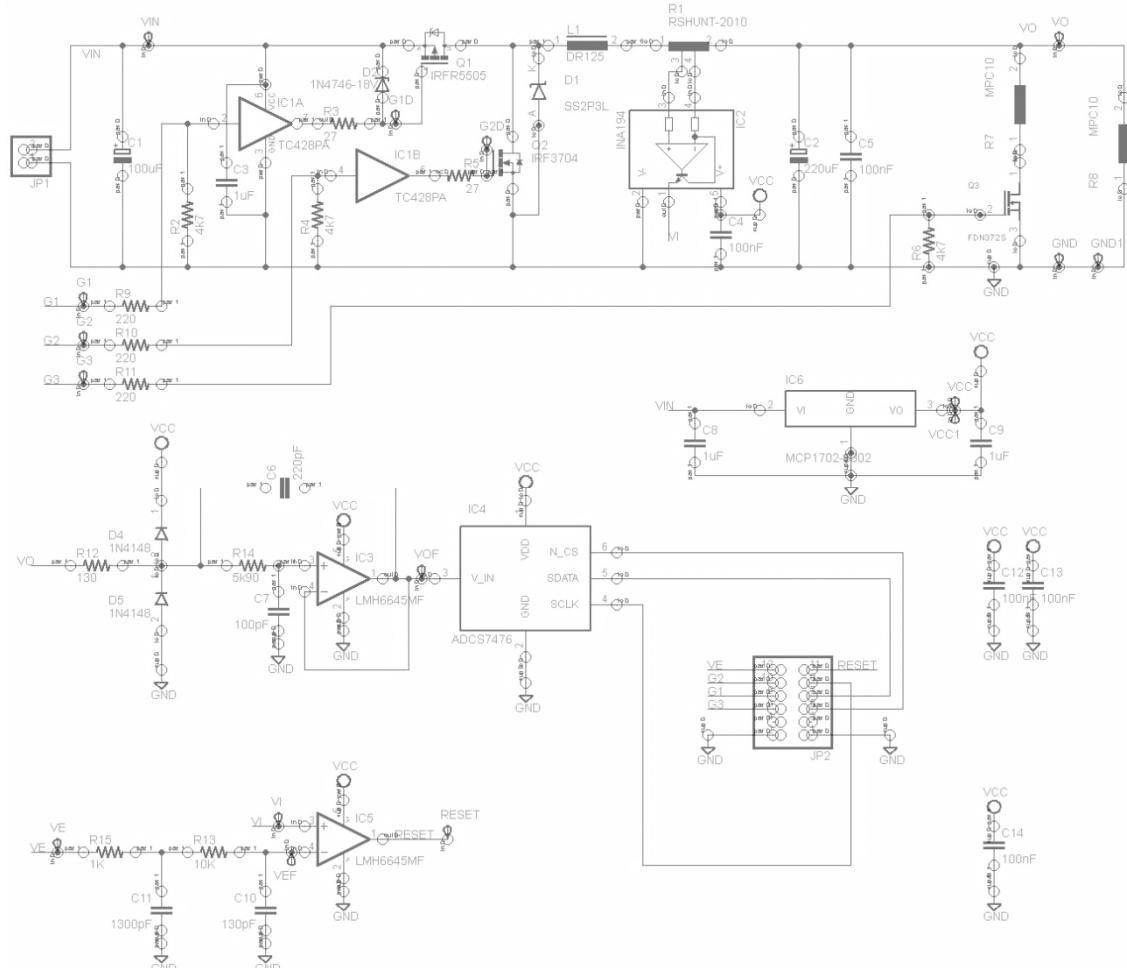

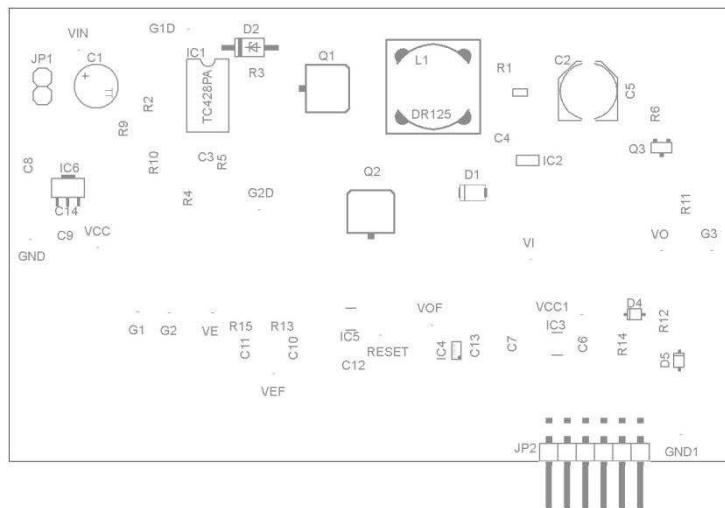

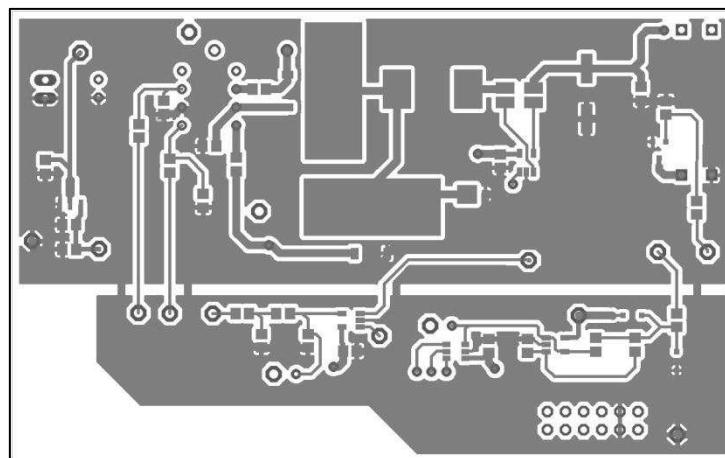

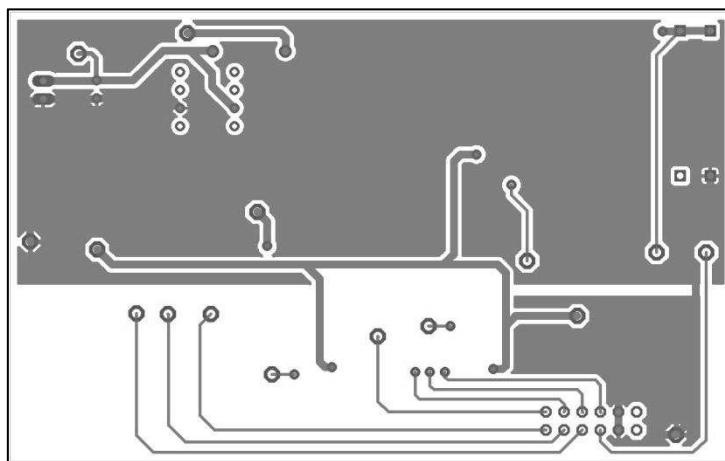

- **PCB CONVERTIDOR**

Representa la placa de circuito impreso realizada en el anexo 8. Está formada por un convertidor buck, un conversor A/D para leer la tensión de salida ( $V_o$ ), la medida de la corriente por la bobina ( $R_i \cdot I_L$ ), un filtro paso bajo que reconstruya la corriente de referencia procedente del conversor  $\Sigma\Delta$  y un comparador cuyas entradas son las corrientes citadas. En el diseño también se ha incluido la posibilidad de realizar cambios de carga a la mitad de su valor, en el instante que se desee.

- **CONTROL**

Representa la placa de una FPGA modelo Nexys 2, a la que se va a conectar la PCB diseñada, para poder realizar el control en lazo cerrado del convertidor.

El control se ha descrito en el apartado 2.2, se ha modelado junto con el convertidor en los apartados 2.3 y 2.1 respectivamente. En el apartado 2.5, ambos se han definido en Matlab para ajustar el regulador. Después se ha realizado el control y el convertidor en la herramienta SimPowerSystems de Matlab. Finalmente, en el apartado 3.2 se ha implementado el control en VHDL, se ha simulado en la herramienta Modelsim y se ha programado la FPGA.

## 2 Diseño del control

Para diseñar el control en modo corriente de pico de un convertidor buck, se han seguido los siguientes pasos:

1. Modelado en pequeña señal del convertidor.

2. Análisis del funcionamiento del control del convertidor.

3. Modelado en pequeña señal del control del convertidor.

4. Ajuste del regulador del control mediante Matlab.

### 2.1 Modelado del convertidor

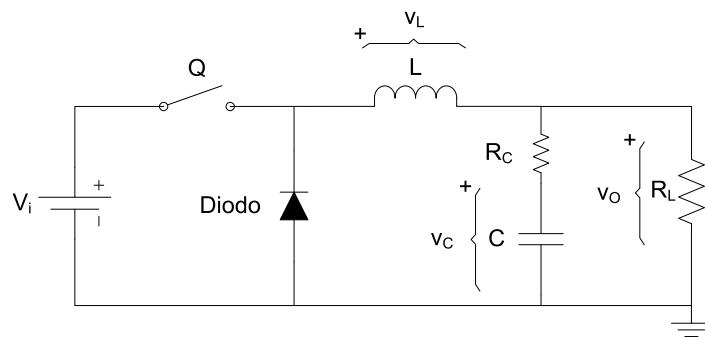

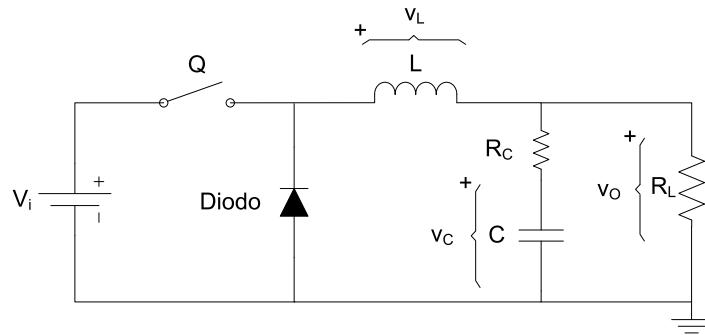

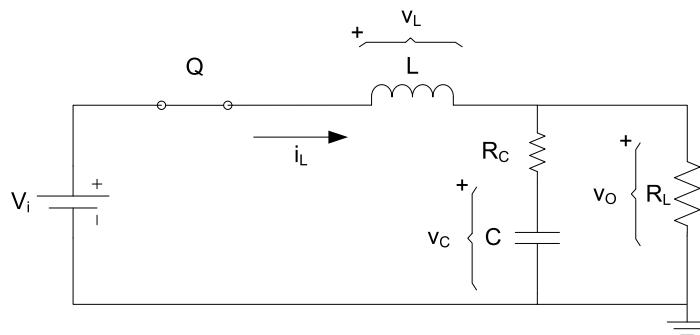

La Figura 2 muestra el circuito típico de un convertidor buck con carga resistiva.

Figura 2 Convertidor buck con carga resistiva.

Los parámetros correspondientes a los componentes del convertidor de la Figura 2, diseñado en el anexo 1, son los siguientes: tensión de entrada  $V_i = 5$  V, tensión de salida  $V_O = 2.5$  V,  $L = 68 \mu\text{H}$ ,  $C = 220 \mu\text{F}$ , resistencia serie equivalente del condensador  $R_C = 25 \text{ m}\Omega$ , resistencia de carga  $R_O = 5 \Omega$  y la frecuencia de conmutación  $f_{sw} = 100 \text{ kHz}$ .

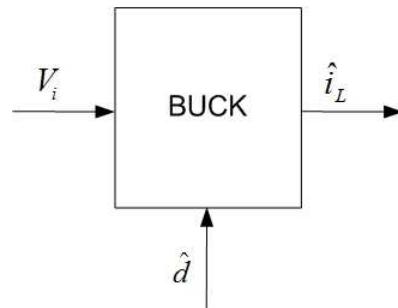

Para modelarlo se ha partido de la idea genérica de su función de transferencia (Figura 3).

Figura 3 Modelo genérico en pequeña señal del convertidor.

Para ello, se han determinado las dinámicas que rigen el funcionamiento del convertidor en los distintos estados del transistor, se han perturbado las variables que intervienen en las mismas en torno a un punto en estado estacionario y se ha extraído el modelo en pequeña señal.

Finalmente, se ha determinado la función de transferencia pasando el resultado al campo transformado de Laplace (1).

$$G_i(s) = \frac{\hat{i}_L}{\hat{d}} = V_i \cdot \frac{1 + C \cdot (R_L + R_C) \cdot s}{(R_L + R_C) \cdot L \cdot C \cdot s^2 + (R_L \cdot R_C \cdot C + L) \cdot s + R_L}. \quad (1)$$

El desarrollo matemático para la obtención de la misma se muestra en el anexo 2.

## 2.2 Control por corriente de pico

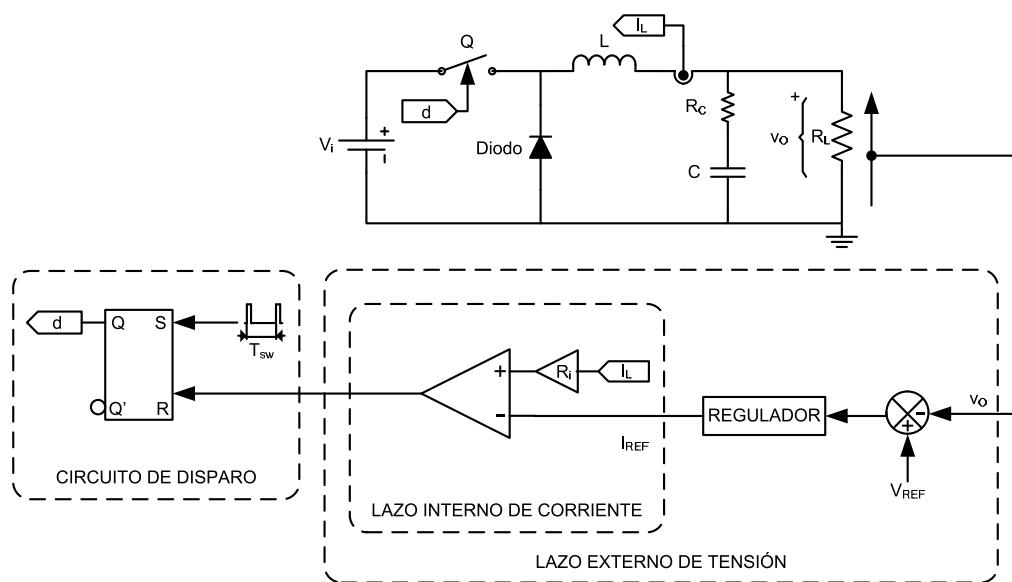

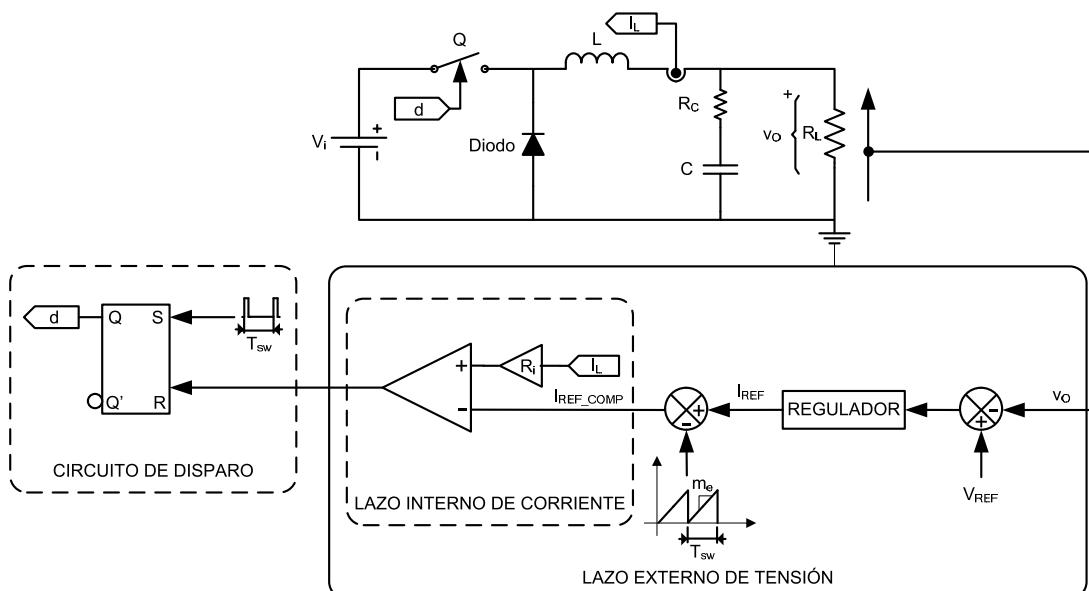

Como viene explicado en [1], pp. 439-489, el control por corriente de pico se basa en el esquema de la Figura 4.

Figura 4 Diagrama del control modo corriente de pico.

El control está formado por:

- **Lazo externo de tensión:** Este contiene un regulador con el que se controla la tensión de salida ( $V_O$ ) a una referencia dada ( $V_{REF}$ ), proporcionando una referencia para el lazo interno de corriente ( $I_{REF}$ ).

- **Lazo interno de corriente:** En este se realiza la comparación entre la referencia de corriente y la corriente medida, siendo su salida activa cada vez que la corriente supere la de referencia.

- **Circuito de disparo:** Formado por un biestable RS que se activa (S) con un pulso al principio de cada periodo de conmutación ( $T_{sw}$ ), comutando el transistor a *on* e incrementando de este modo la corriente por la bobina. Cuando dicha corriente supera la de referencia, la salida del comparador resetea (R) el biestable, pasando a *off* el transistor, lo cual origina un decremento en la corriente.

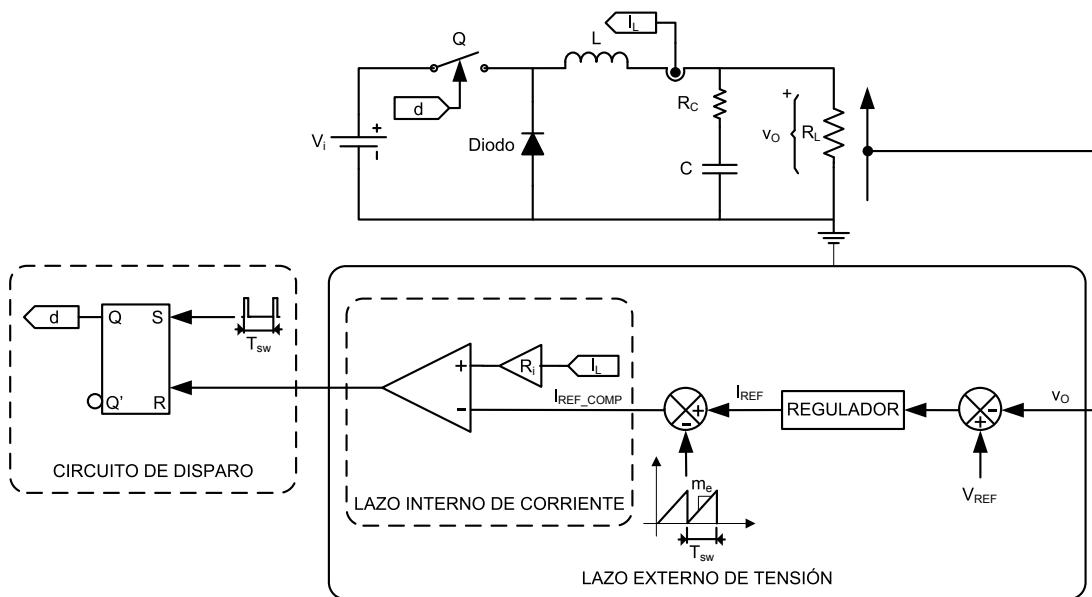

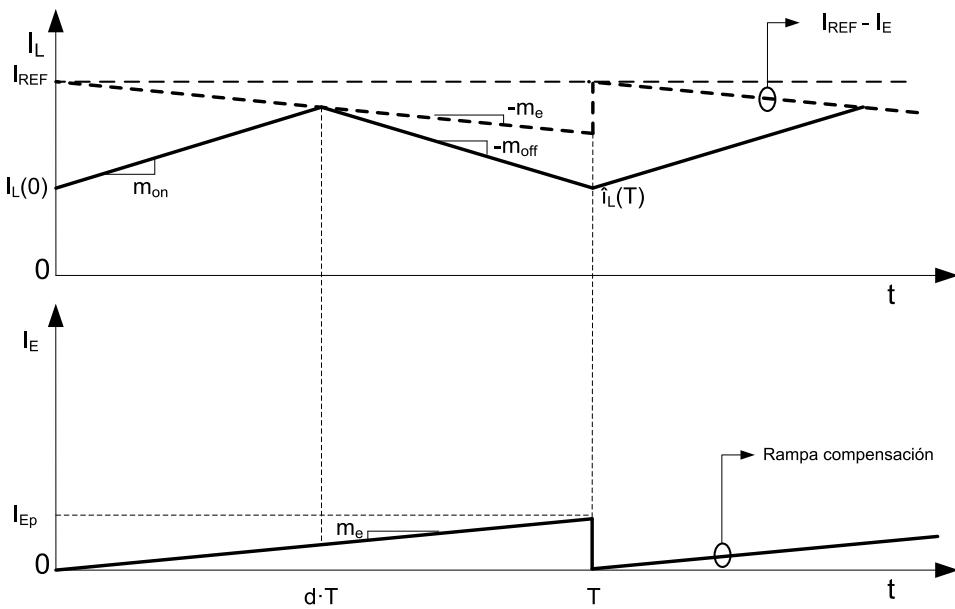

El problema que presenta el control de corriente de pico es su inestabilidad para un ciclo de servicio igual o superior a 0.5. Para mitigarlo y poder variar el ciclo en todo su rango (0<D<1), hay que incluir una rampa de compensación de corriente a la salida del regulador (Figura 5).

El valor de pico de la rampa ( $A_{rampa}$ ) se ha definido en términos de su pendiente ( $m_e$ ) y el periodo de conmutación ( $T_{sw}$ ).

$$A_{rampa} = m_e \cdot T_{sw} \quad (2)$$

La elección del valor de la pendiente, así como el desarrollo del funcionamiento del control en detalle, se han desarrollado en el anexo 3.

Figura 5 Diagrama del control modo corriente de pico con rampa de compensación.

## 2.3 Modelado del control

### 2.3.1 Lazo de corriente

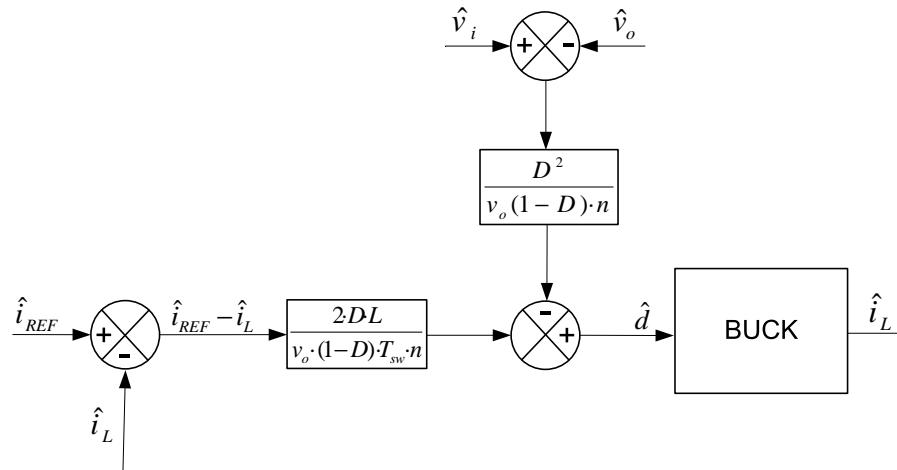

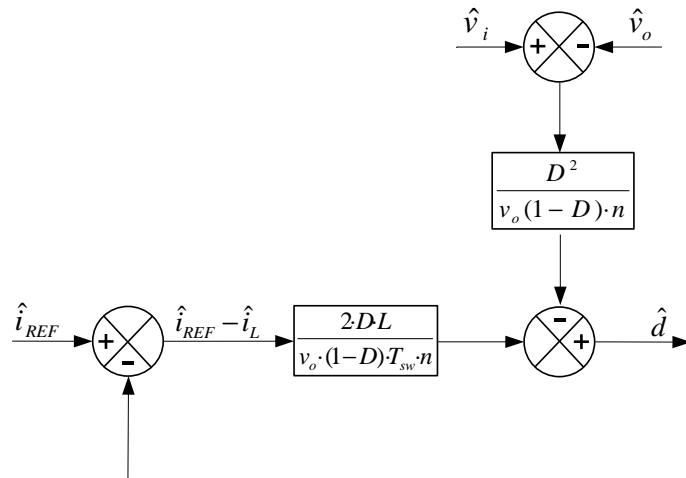

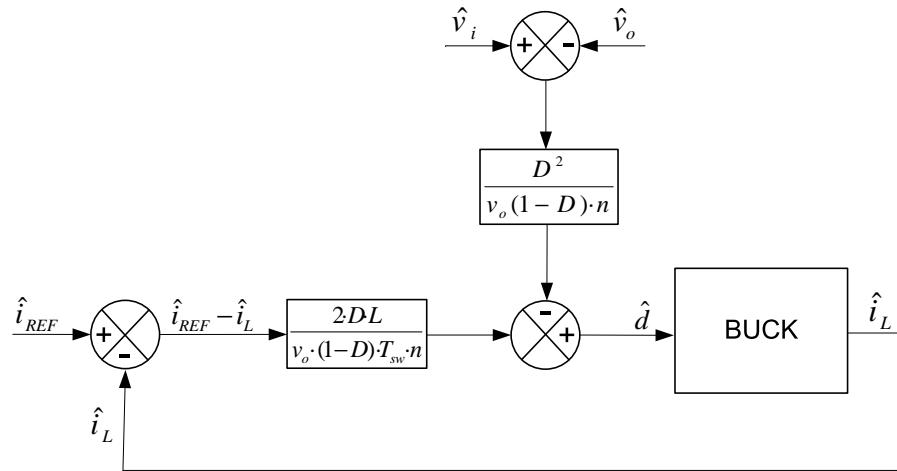

Tal como se ha desarrollado en el anexo 4, analizando el lazo de corriente en términos de pequeña señal, se ha determinado la relación existente entre el ciclo de servicio y la diferencia entre la corriente de referencia y la medida en la bobina, considerando la rampa de compensación y la compensación de posibles perturbaciones en  $V_i$  y  $v_o$  (3).

$$\hat{d} = \frac{2 \cdot D \cdot L}{v_o \cdot (1 - D) \cdot T_{sw} \cdot n} \cdot (\hat{I}_{REF} - \hat{I}_L) - \frac{D^2}{v_o \cdot (1 - D) \cdot n} (\hat{v}_i - \hat{v}_o) \quad (3)$$

Donde D es el ciclo de servicio nominal del convertidor:

$$D = \frac{V_o}{V_i} \quad (4)$$

Y el parámetro  $n$  es:

$$n = \left(1 + 2 \cdot \frac{m_e}{m_{on}}\right) \quad (5)$$

Siendo  $m_{on}$  la pendiente de la corriente cuando el transistor está en *on*.

Con la relación definida anteriormente en este apartado y la función de transferencia del convertidor definida en el apartado 2.1, se ha elaborado el diagrama de bloques de lazo de corriente (Figura 6).

Figura 6 Diagrama de bloques control de corriente y función de transferencia del buck.

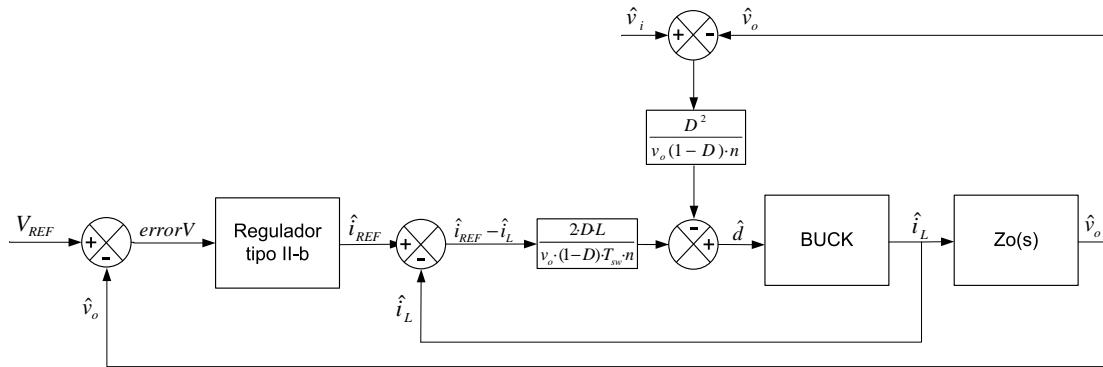

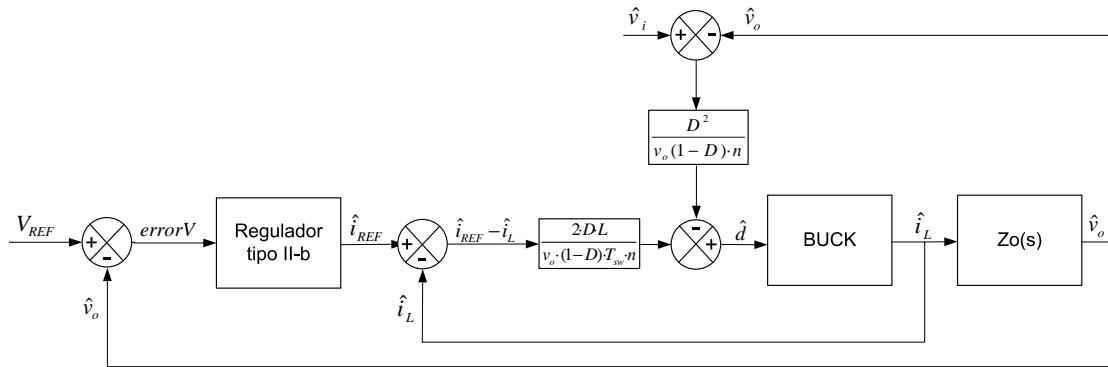

### 2.3.2 Lazo de tensión

El siguiente paso es incluir el lazo de control de tensión. Para ello, se ha determinado  $v_o$  (6) a partir de la impedancia equivalente del condensador y la carga ( $Z_o$ ) y la corriente por la inductancia.

$$\hat{v}_o = \hat{i}_L \cdot Z_o(s) = \hat{i}_L \cdot \frac{(R_C \cdot C \cdot s + 1) \cdot R_L}{(R_C + R) \cdot C \cdot s + 1} \quad (6)$$

Se desea obtener un error de posición nulo de tensión y un margen de fase (MF) mínimo de 60 grados a la frecuencia de cruce del sistema ( $f_c$ ). Como se explica en [14], el regulador a incluir es de tipo II-b y su expresión viene dada por:

$$R(s) = K \cdot \frac{1}{s} \cdot \frac{1 + \frac{s}{w_z}}{1 + \frac{s}{w_p}} \quad (7)$$

Mediante la constante  $K$  del regulador, se ha ajustado  $f_c$  una década por debajo de  $f_{sw}$ . Al incluir un integrador para anular el error de posición, se añade una fase de menos 90 grados a lo largo de todo el rango de frecuencias, pudiendo inestabilizar el sistema. Para obtener el margen de fase deseado y asegurar la estabilidad del sistema, se ha diseñado un PAF-PRF con el cero ( $w_z$ ) y el polo ( $w_p$ ) que forman el regulador tipo II-b respectivamente.

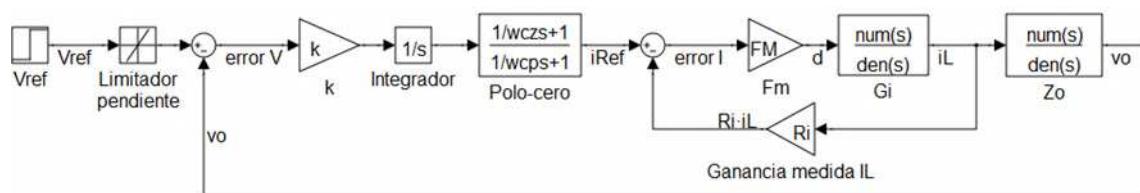

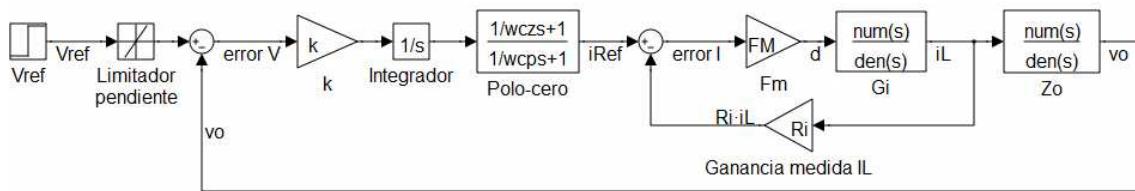

La Figura 7 muestra el diagrama de bloques que modela el comportamiento y el control por corriente de pico del convertidor buck.

Figura 7 Diagrama de bloques del control modo pico corriente completo.

El ajuste del regulador se ha realizado mediante la herramienta Sisotool de Matlab en el siguiente punto, donde se han desestimado las posibles perturbaciones en  $V_i$ , ya que esta se ha obtenido de una fuente de alimentación comercial. También se han despreciado posibles perturbaciones en  $v_o$ , ya que su rizado es despreciable frente a su valor medio, tal y como se ha determinado en el anexo 1.

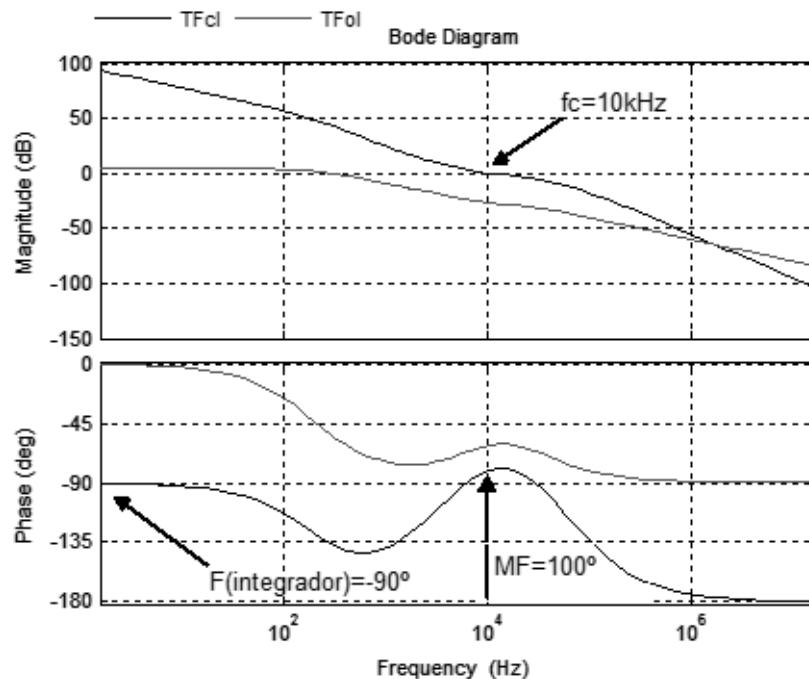

## 2.4 Ajuste del regulador mediante Matlab

Para determinar el regulador, se ha analizado el comportamiento del sistema en lazo cerrado en términos de la función de transferencia en lazo abierto del sistema. Dicha ganancia de lazo, se ha definido como el producto de las funciones de transferencia que se disponen en cascada (excluyendo signo -).

Partiendo del diagrama de la Figura 7, en Matlab se ha definido la ganancia del modulador:

$$FM = \frac{2 \cdot D \cdot L}{v_o \cdot (1 - D) \cdot T_{sw} \cdot n} \quad (8)$$

A partir de esta y la función de transferencia del convertidor buck ( $G_i$ ), se ha definido la función de transferencia del lazo de corriente, considerando la ganancia de la medida de la misma ( $R_i$ ):

$$TFi = FM \cdot \frac{G_i(s)}{(1 + R_i \cdot FM \cdot G_i(s))} \quad (9)$$

Con esta función, se ha definido la ganancia de lazo sin regulador:

$$TFol = FM \cdot \frac{G_i(s)}{(1 + R_i \cdot FM \cdot G_i(s))} \cdot Z_o(s) \quad (10)$$

Esta ganancia representa el comportamiento del sistema en lazo abierto, que comparada con la ganancia de lazo cerrado, servirá para ver la aportación del regulador al sistema.

La ganancia de lazo cerrado se ha definido como:

$$TF_{cl} = TF_{ol} \cdot R(s) \quad (11)$$

El regulador diseñado con Sisotool resulta:

$$R(s) = 282743 \cdot \frac{1}{s} \cdot \frac{1 + s/13333}{1 + s/500000} \quad (12)$$

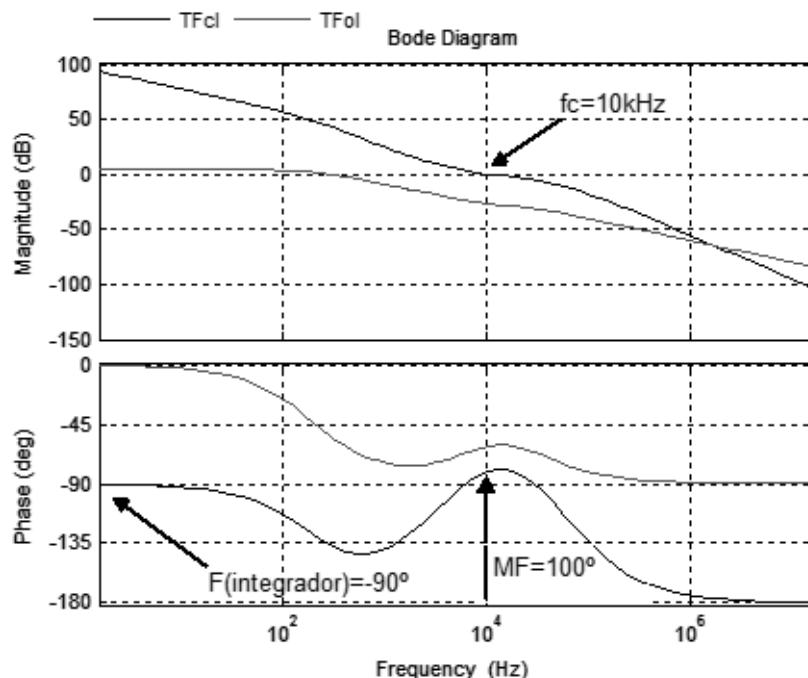

La Figura 8 muestra el diagrama de bode resultante del sistema en lazo abierto y lazo cerrado. En lazo cerrado se ha obtenido un margen de fase de  $100^\circ$  en  $f_c$ , asegurando la estabilidad del sistema.

Figura 8 Diagrama de Bode del sistema en lazo abierto y en lazo cerrado.

## 2.5 Implementación en Matlab/Simulink

### 2.5.1 Modelo continuo

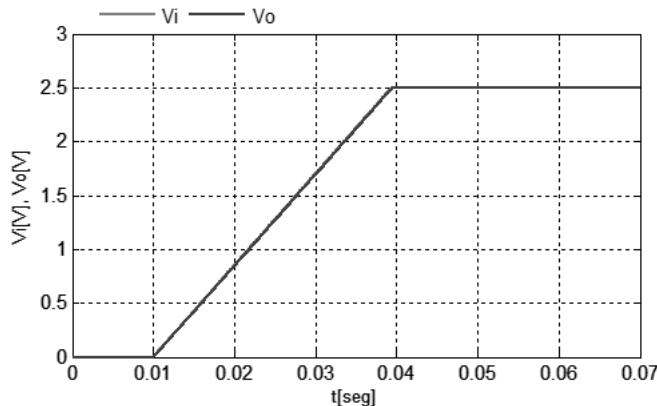

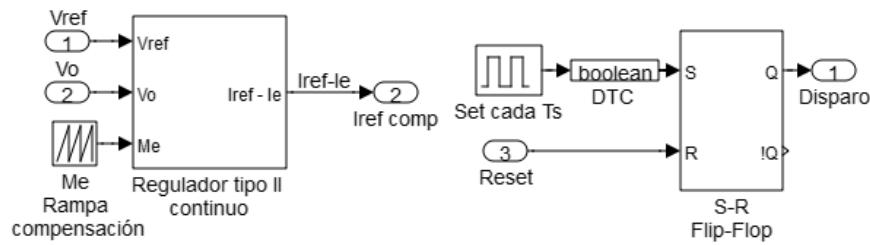

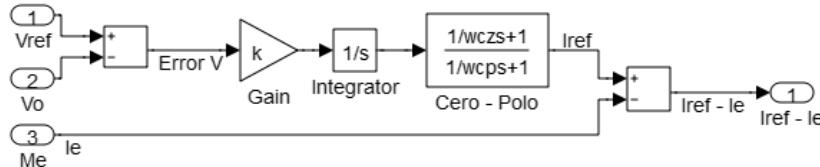

La Figura 9 muestra en control en modo continuo, modelado en la herramienta Simulink de Matlab.

Figura 9 Diagrama de bloques modelo continuo (buck y control) en Simulink.

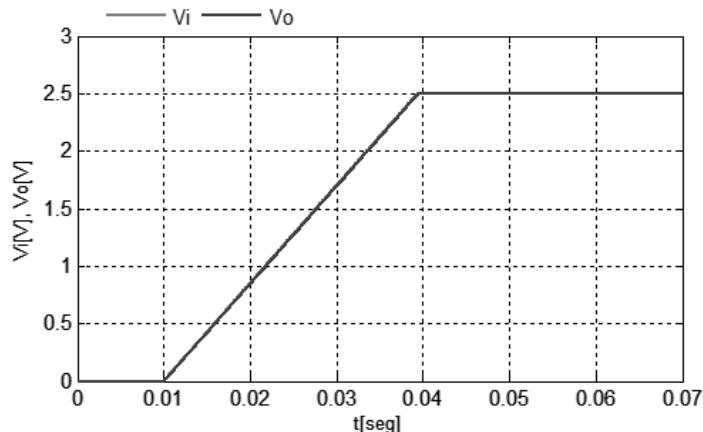

La Figura 10 muestra el resultado de la simulación de la respuesta del sistema controlado, ante una referencia de tensión en rampa 2.5 voltios de amplitud.

Figura 10 Respuesta del control de corriente ante referencia de tensión en rampa.

El sistema tiene una buena respuesta, siendo su error de posición nulo en régimen permanente.

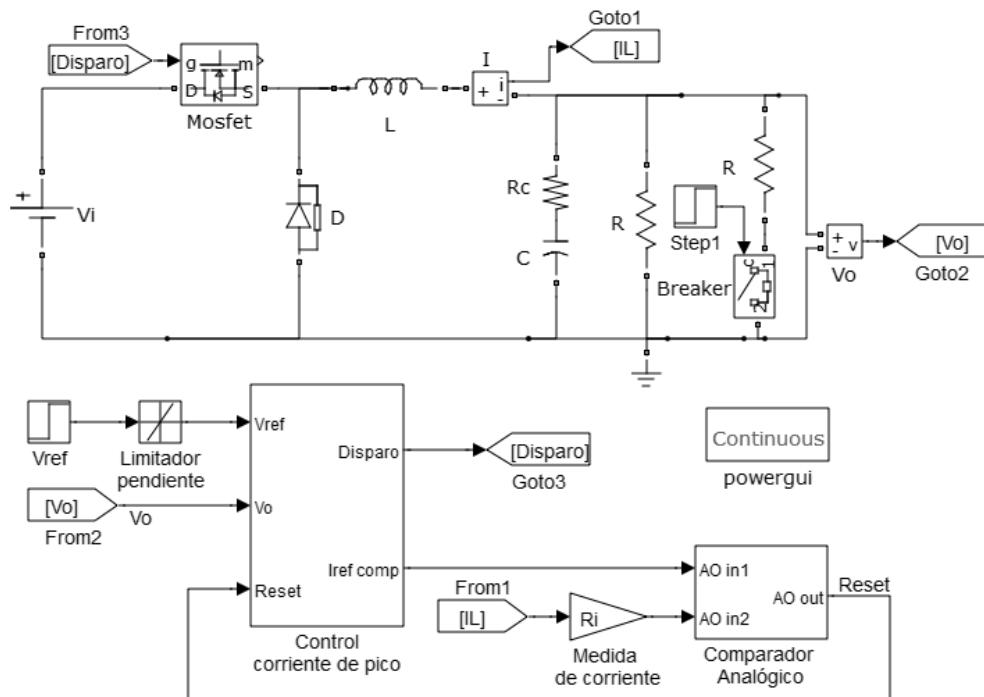

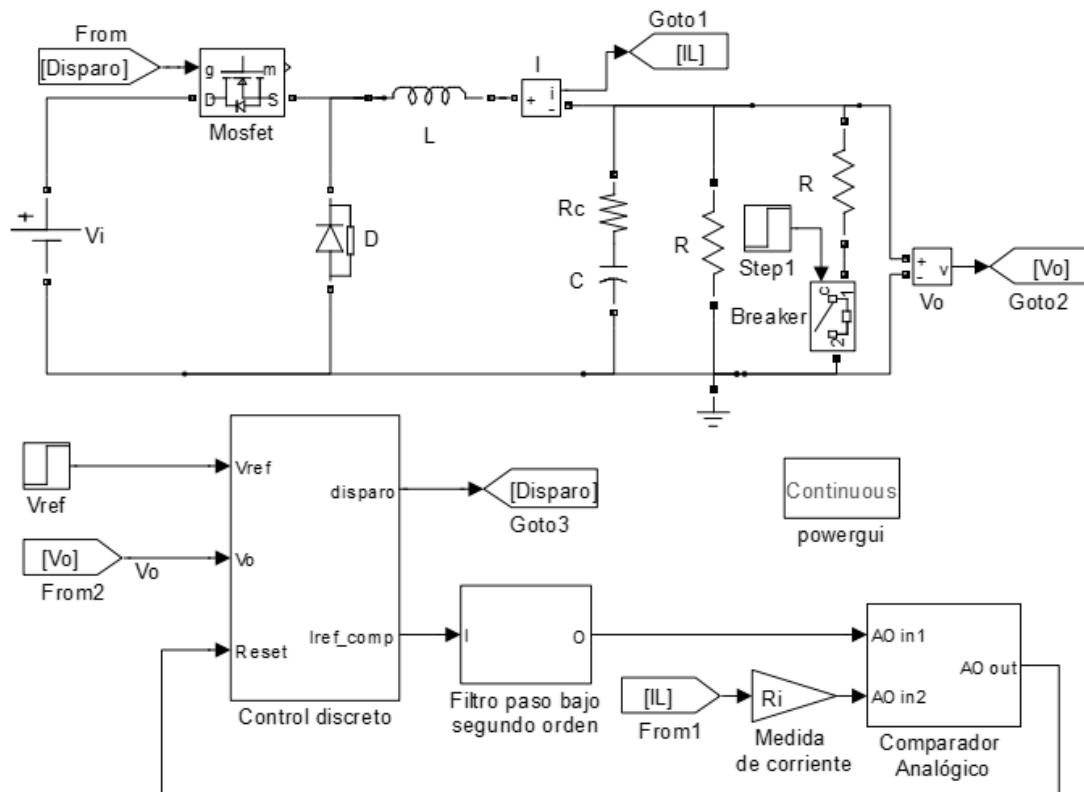

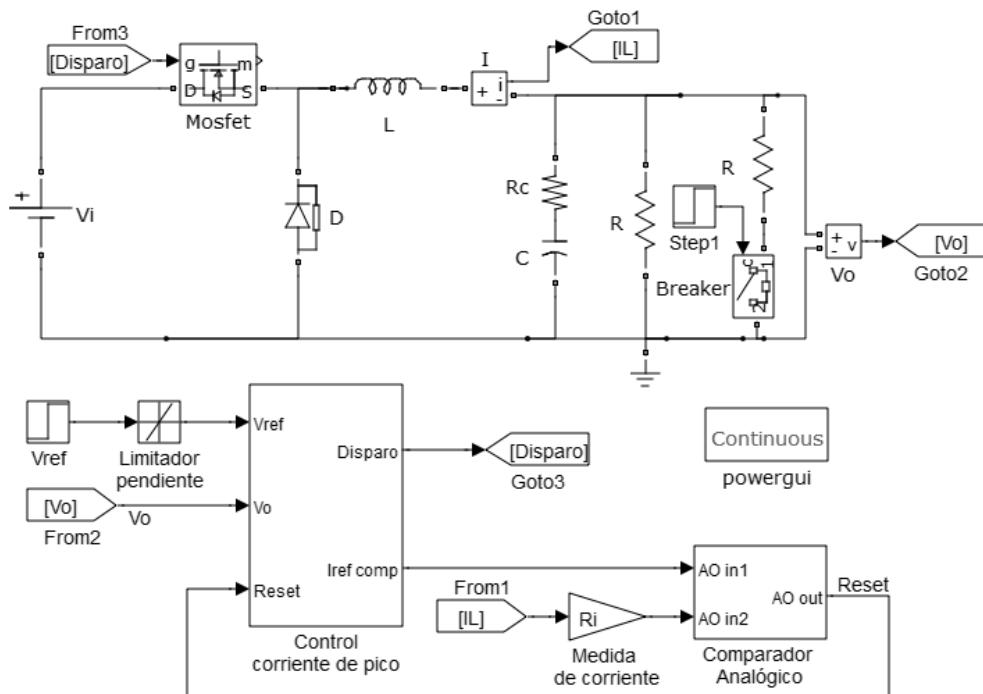

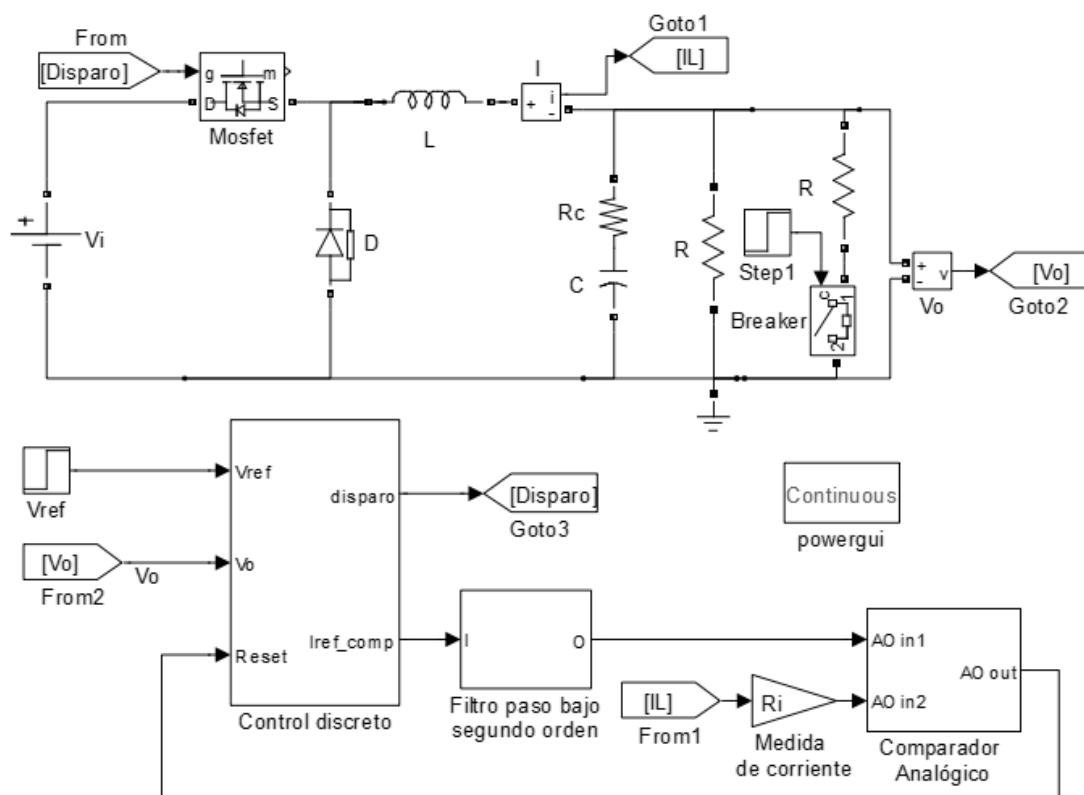

Dado el buen funcionamiento del regulador, se ha modelado el convertidor buck con bloques de la herramienta SimPowerSystems de Simulink y su correspondiente control en modo continuo. En la Figura 11 se observa la etapa de electrónica de potencia, a la que se le ha incluido un interruptor (Breaker) y una resistencia del mismo valor que la de carga, en paralelo con la misma, con el fin de imponer cambios de carga y ver la estabilidad que el regulador proporciona al control. En la parte de control, al igual que en la Figura 9, se ha limitando la pendiente de subida de la tensión de referencia, evitando de este modo sobre oscilaciones indeseadas en el inicio del control.

Figura 11 Convertidor buck en bloques de SimpowerSystems y control continuo en Simulink

El detalle del control de la Figura 11 se muestra a continuación:

Figura 12 Control por corriente de pico continuo detallado en Simulink.

Figura 13 Regulador continuo detallado y compensación en Simulink.

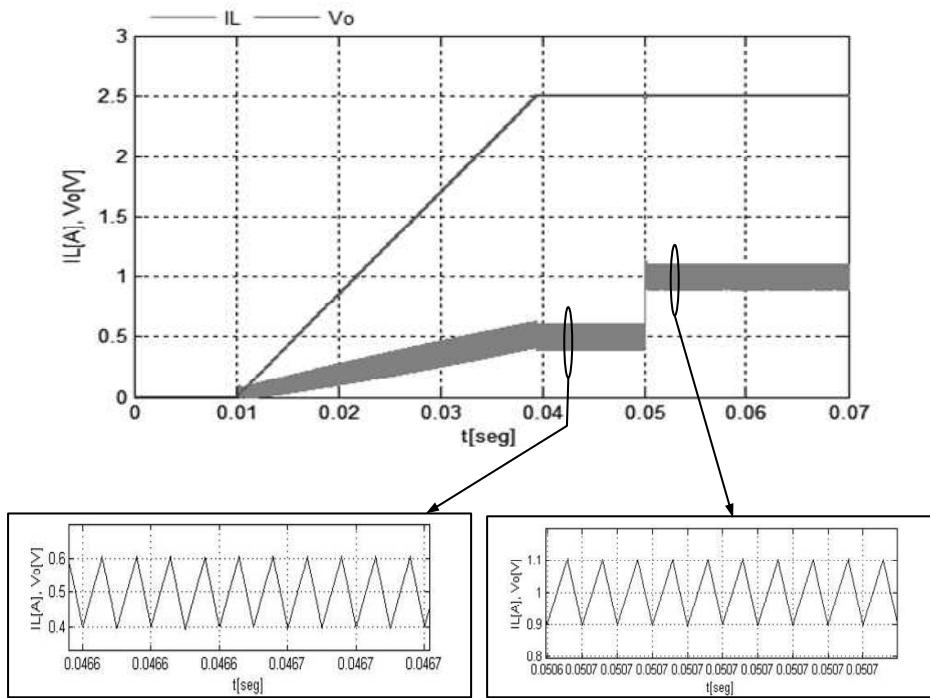

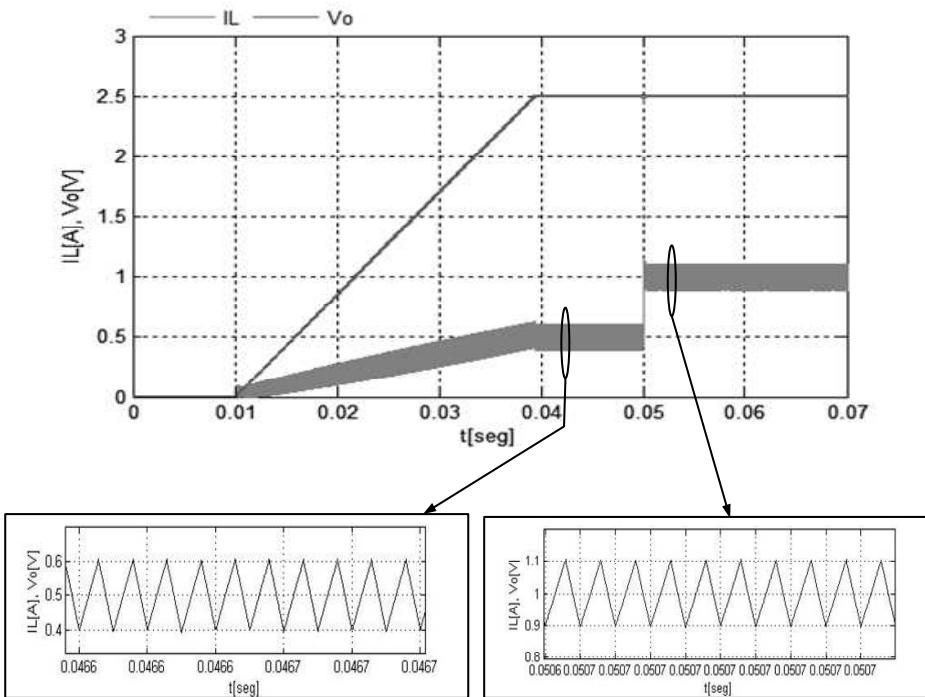

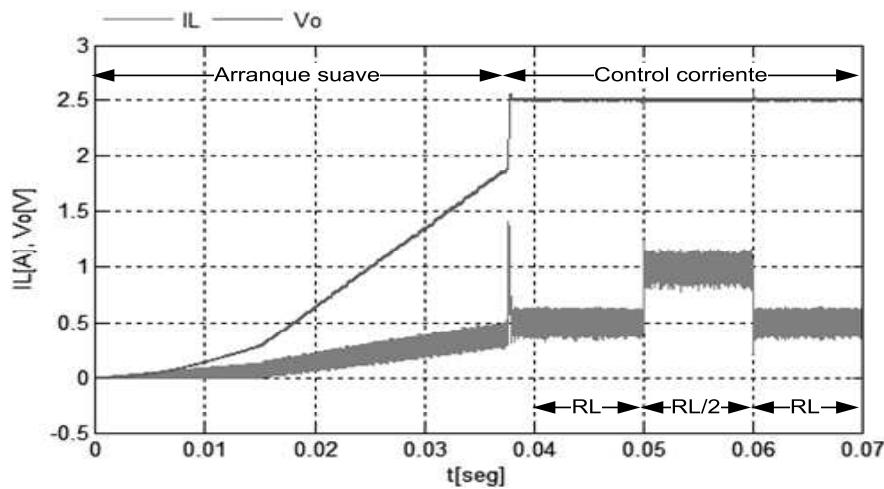

Analizando el resultado de la simulación de la Figura 14, se observa que en  $t=0.01$  segundos se ha realizado un arranque suave del convertidor, alcanzando la tensión de salida deseada en  $t=0.04$  segundos. En  $t=0.05$  segundos se ha realizado un cambio de carga a la mitad de su valor, ante el cual el control se comporta de manera adecuada, estableciendo la corriente sin apenas sobre oscilación y manteniendo la tensión de salida constante.

Figura 14 IL y Vo ante cambio a mitad de carga con control continuo.

La corriente antes del cambio de carga tiene un valor medio de 0.5 amperios, siendo su rizado de 0.2 amperios. Al darse el cambio de carga, existe una leve sobre oscilación de 0.2 amperios sobre el valor medio en régimen permanente, el cual asciende a 1 amperio con el mismo rizado.

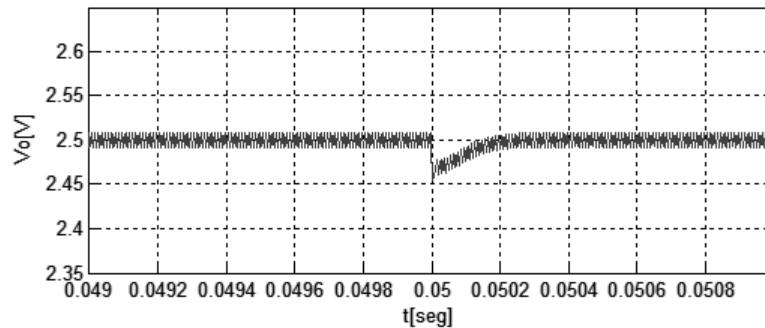

La tensión en el cambio desciende hasta un mínimo de 2.45 voltios, adquiriendo la tensión de referencia en aproximadamente 200  $\mu$ s.

Figura 15 Evolución de la tensión ante un cambio de carga a mitad de su valor.

## 2.5.2 Modelo discreto

La Figura 16 muestra el convertidor y el control discreto del mismo.

Figura 16 Convertidor buck en bloques de SimpowerSystems y control discreto en Simulink.

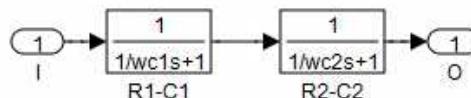

A la salida del control se ha incluido un filtro paso bajo, para reconstruir la señal digital de la corriente de referencia compensada. Para modelar el filtro, se han definido las frecuencias de corte de los dos filtros paso bajo de primer orden que lo forman. Ambas frecuencias se han ajustado por simulación en 750 kHz.

El regulador se ha discretizado mediante el método de transformación bilineal (13), usando la función c2d de Matlab.

$$R(z) = \frac{b_0 + b_1 \cdot z^{-1} + b_2 \cdot z^{-2}}{1 + a_1 \cdot z^{-1} + a_2 \cdot z^{-2}} \quad (13)$$

Los coeficientes del mismo son:

- $(b_2, b_1, b_0) = (-14.14, 2, 16.16)$

- $(a_2, a_1) = (-0.4286, -0.5714)$

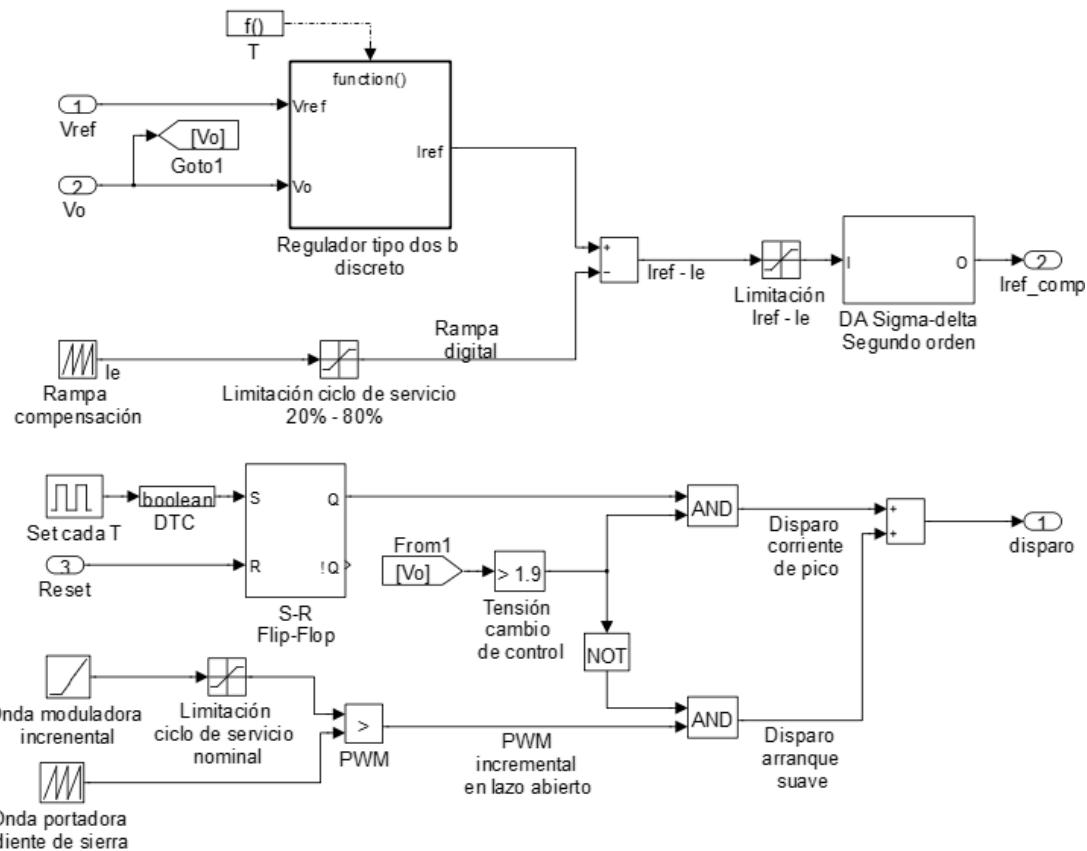

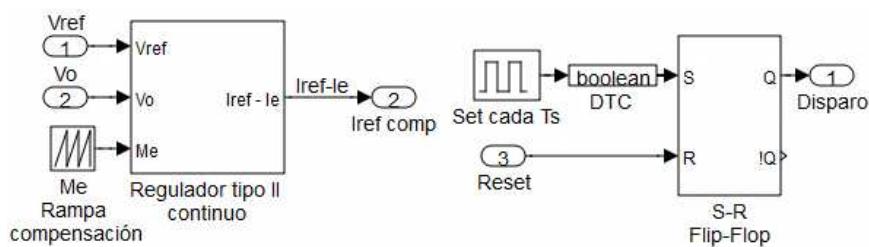

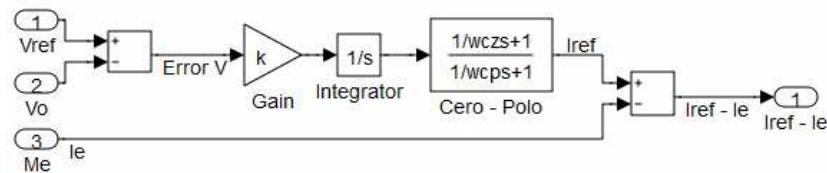

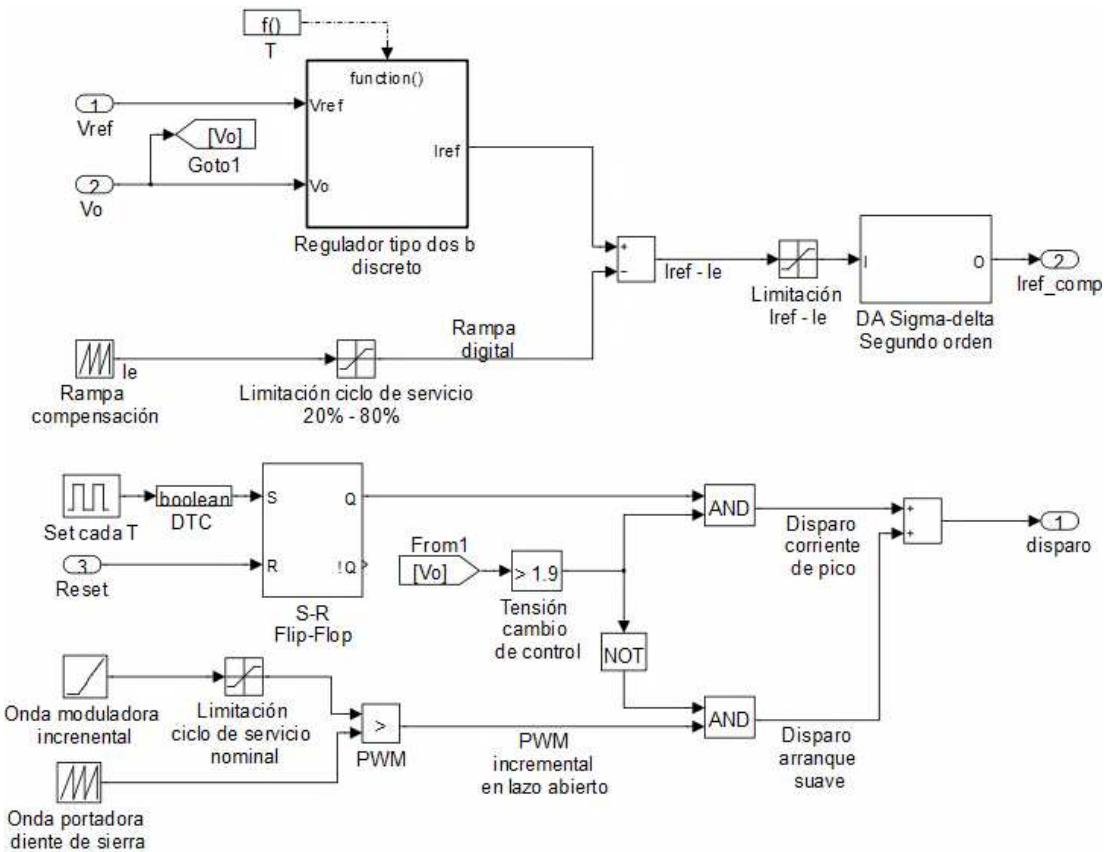

Dentro del bloque de control discreto (Figura 17), el regulador se ha muestreado cada  $T_{sw}$ , dado el pequeño rizado de tensión a la salida. A la referencia establecida por el regulador, se le ha restado una rampa digital de compensación, obteniendo la referencia digital de corriente compensada. La conversión digital analógica, se ha llevado a cabo mediante un conversor DA sigma delta ( $\Sigma\Delta$ ) de segundo orden, razón por la cual el filtro paso bajo es de segundo orden.

Figura 17 Modelo detallado del control discreto del convertidor.

Una problemática que ha surgido a raíz de la inclusión del  $\Sigma\Delta$  en el control, es que las amplitudes de corriente en el arranque son demasiado pequeñas. Por esta razón, se ha implementado un arranque suave del convertidor mediante una modulación PWM, con un incremento progresivo del ciclo de servicio. A partir de un valor de tensión a la salida, donde la corriente adquiere una amplitud aceptable para el conversor, se ha desactivado el control PWM y se ha activado el de corriente de pico. De esta manera se ha realizado un cambio automático de control de manera similar a la desarrollada en [9].

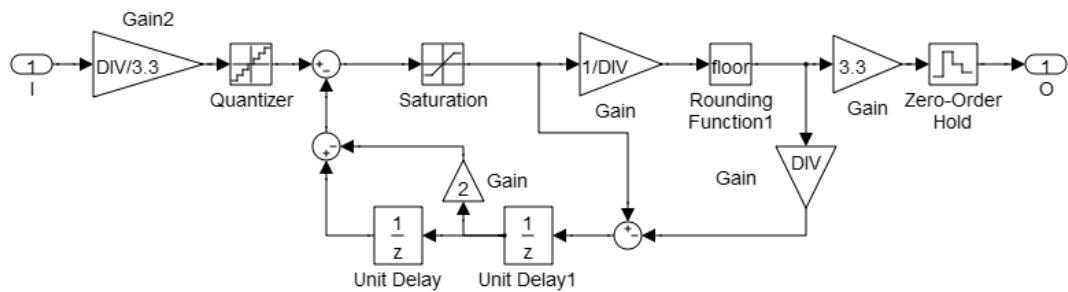

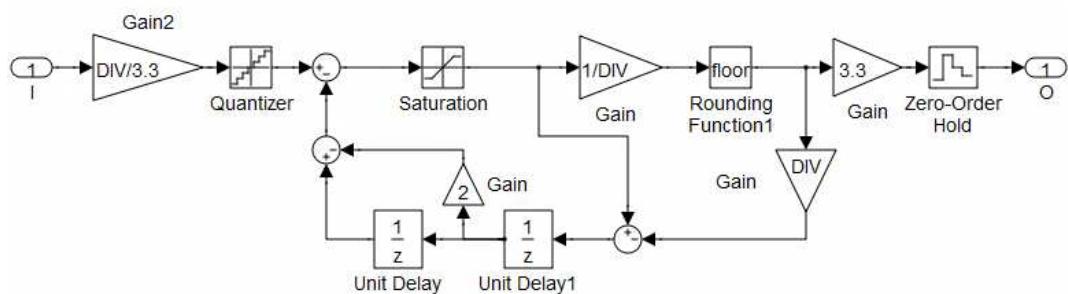

Otro aspecto a resaltar por la inclusión del  $\Sigma\Delta$  y su posterior filtrado, es la limitación del ciclo de servicio, para dar tiempo a que la señal sea reconstruida por completo. La limitación se ha realizado recortando el valor de la amplitud de la rampa de compensación, ya que al compararse con la corriente medida, resetea el biestable que impone el ciclo de servicio en cada periodo de conmutación. Para un correcto funcionamiento del conversor se ha limitado el ciclo de servicio entre 0.2 y 0.8, es decir, se ha recortado la rampa entre un 20% y un 80% de su amplitud. El citado conversor se ha modelado según [15] y su implementación en Simulink es:

Figura 18 Modelo del conversor DA sigma-delta de segundo orden en Simulink.

La entrada al conversor se ha pasado de su valor real a entero de la siguiente manera:

$$I_{entero} = I_{real} \cdot \frac{DIV}{V_{FS}} = I_{real} \cdot \frac{2^{n-1}}{V_{FS}} \quad (14)$$

Siendo  $n$  el numero de bits del dato a convertir (9 bits) y  $V_{FS}$  la tensión de fondo de escala del conversor (3.3 voltios). Después se ha cuantizado el dato con un intervalo:

$$q = \frac{V_{FS}}{DIV} = \frac{V_{FS}}{2^{n-1}} \quad (15)$$

El dato se ha limitado entre 0 y  $(2^n-1)$  y se ha convertido a binario dividiéndolo por DIV. El bit mas significativo (MSB) del dato se ha llevado a la salida, realimentando los bits menos significativos (LSBs) con valor entero, que a través de la función de transferencia de ruido del conversor (NTF) (16) se ha suministrado a la salida del cuantizador.

$$\text{NTF}(z) = 1 - \left(1 - \frac{1}{z}\right)^2 = \frac{1}{z} \cdot \left(2 - \frac{1}{z}\right) \quad (16)$$

Siendo la frecuencia de muestreo de NTF igual a la máxima del reloj de la FPGA ( $f_{CLK}=50MHz$ ), en la salida se obtiene una señal digital de un bit a esa frecuencia, la cual contiene la información binaria del dato. Mediante un cambio de escala a  $V_{FS}$  y un mantenedor de orden cero muestreado a  $f_{CLK}$ , se ha reconstruido la señal y con el filtro paso bajo a la salida del control, se ha obtenido la referencia de corriente compensada a la frecuencia de conmutación.

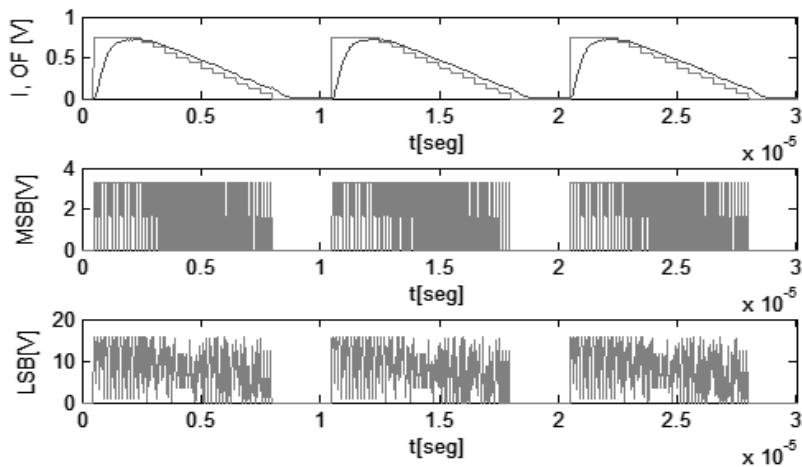

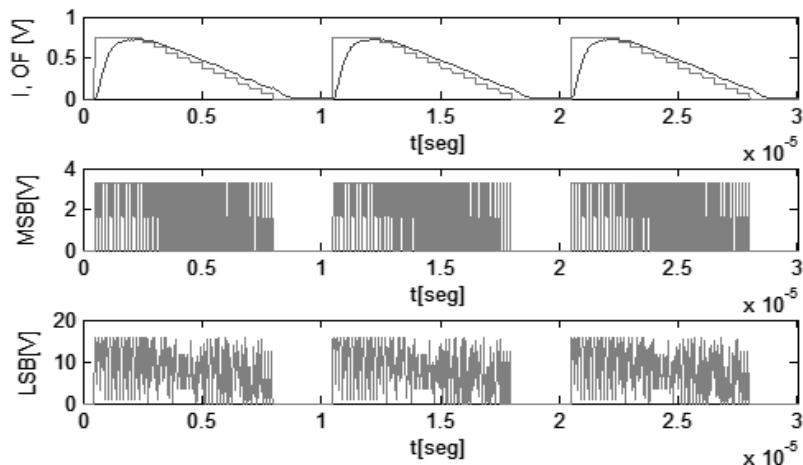

La Figura 19 muestra el comportamiento de las señales del conversor ante una referencia compensada de 0.7 voltios de amplitud. Arriba se observa la señal cuantizada y la rampa reconstruida y filtrada, en medio se aprecia el bit más significativo a la salida y abajo se ve el ruido realimentado.

Figura 19 Señal cuantizada (I) vs salida filtrada (OF) (arriba), MSB (medio) y ruido realimentado (LSBs) (abajo).

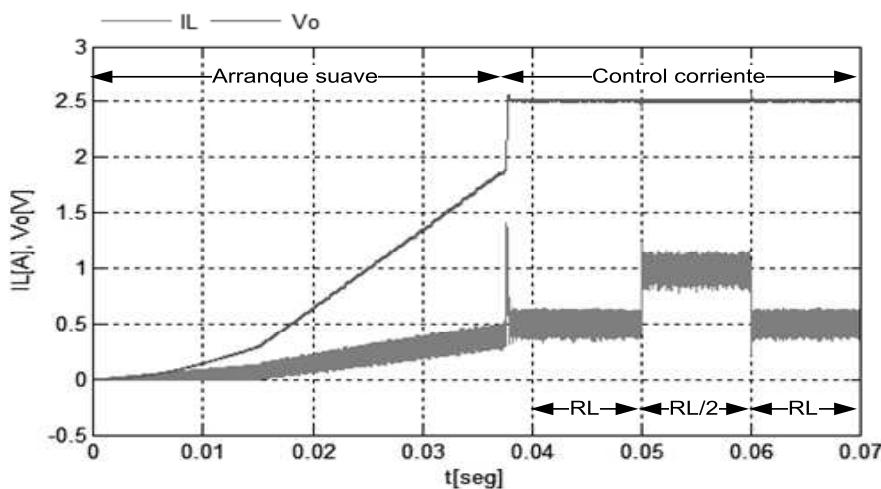

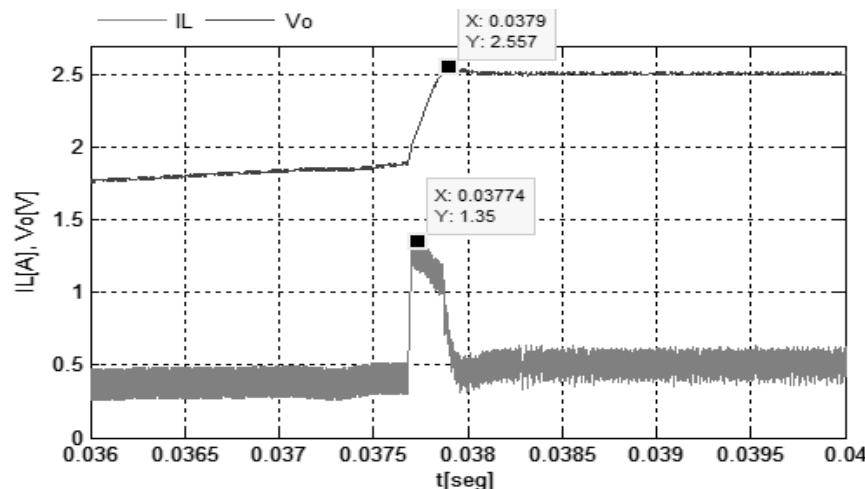

En la Figura 20 se observa el arranque suave el convertidor y al llegar la tensión de salida a 1.9 voltios, se impone el control por corriente. Actuando el control por corriente, en  $t=0.05$  segundos se produce un cambio de carga a la mitad de su valor y en  $t=0.06$  segundos se vuelve a establecer el valor de carga completa.

Figura 20 IL y  $V_o$  ante cambios de carga con control discreto

Figura 21 Detalle IL y  $V_o$  en el cambio de control.

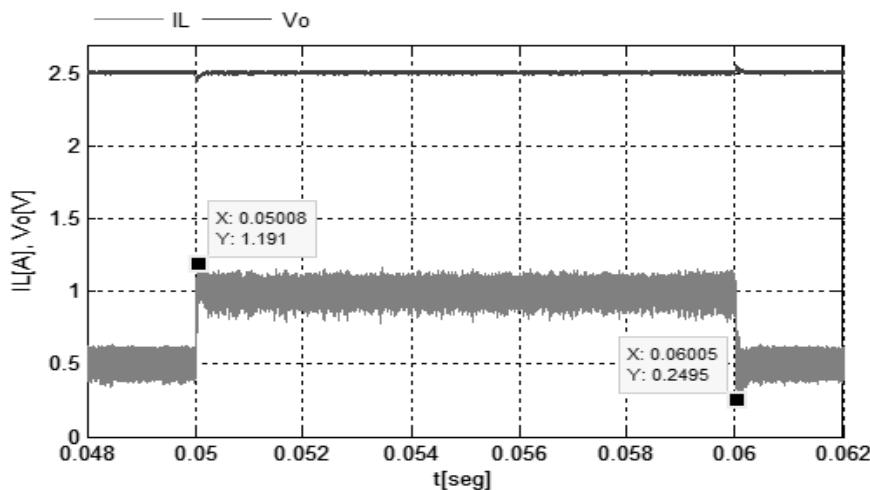

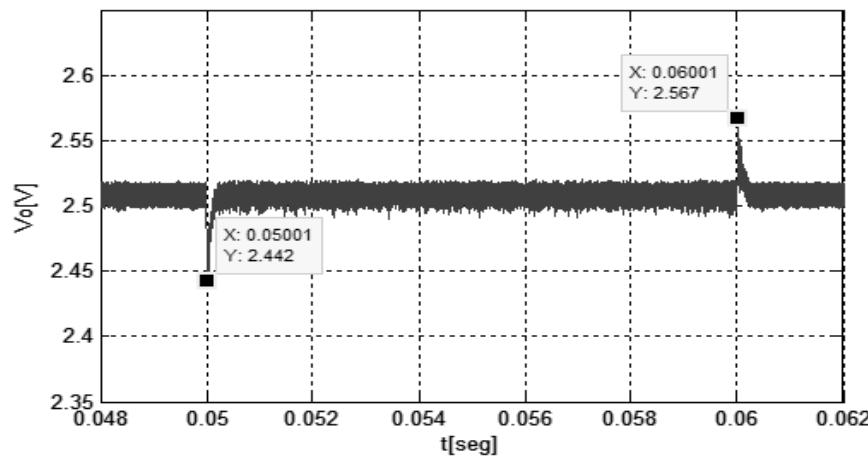

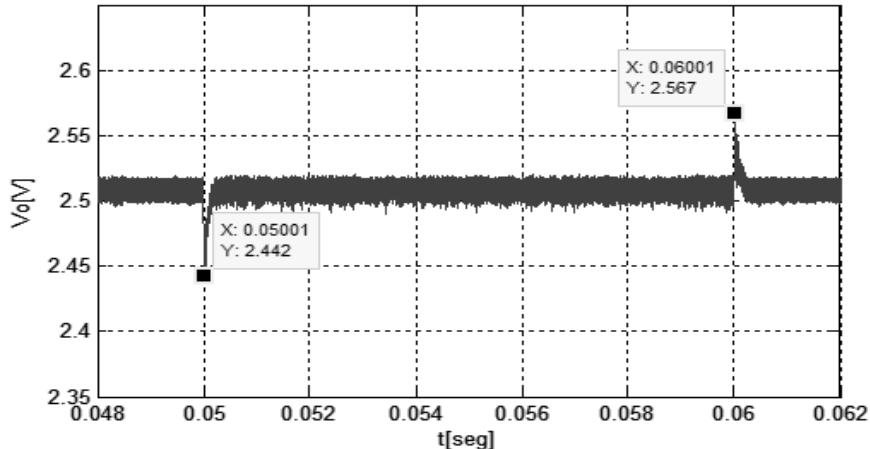

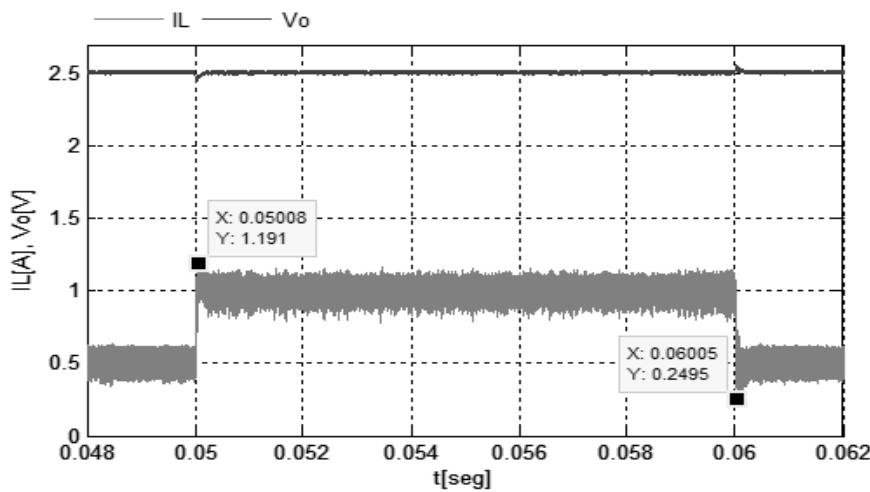

Analizando los cambios de carga en la Figura 22, se observa que al reducir la carga a la mitad de su valor, la corriente tiene un máximo de 1.19 amperios. Por el contrario, al establecer de nuevo la carga completa, la corriente tiene un mínimo en 0.25 amperios. El rizado de la corriente es de 0.2 amperios, independientemente de la carga impuesta.

Figura 22 Detalle IL y Vo en los cambios de carga en el control de corriente.

La tensión en el primer cambio desciende hasta 2.44 voltios, mientras que en el segundo cambio asciende hasta 2.57 voltios, alcanzando el valor de referencia en aproximadamente 200  $\mu$ s en ambos cambios.

Figura 23 Detalle Vo en los cambios de carga.

En el anexo 5 se han detallado la realización de los modelos y las simulaciones que se han presentado a lo largo de este apartado, con los archivos de inicialización necesarios para el correcto funcionamiento de los mismos.

### 3 Implementación en FPGA

La Figura 24 muestra el diagrama de bloques del control digital basado en FPGA, con las conexiones entre la placa Nexys2 modelo Spartan 3E 1200 de Digilent y la PCB del convertidor.

Figura 24 Diagrama de bloques del control digital en FPGA.

Para la verificación del diseño del control en FPGA, se va a seguir la estrategia de simular en VHDL todo el sistema en lazo cerrado, lo que requiere modelar en VHDL no sintetizable todos los bloques de la PCB que van conectados a la FPGA. El código sintetizable del control en FPGA y la descripción comportamental del hardware no sintetizable de la PCB, se encuentran en el anexo 7.

#### 3.1 Modelo del hardware no sintetizable en VHDL

La parte hardware no sintetizable se ha modelado en un test bench en VHDL, mediante el software de programación ISE 10.1 de Xilinx. Los bloques que forman el hardware se describen a continuación:

- **Convertidor buck**

Éste se ha modelado al igual que en [16]. Para ello se han discretizado las ecuaciones diferenciales lineales que modelan el convertidor determinadas en el anexo 2 ((50), (51), (52) y

(53)), mediante el algoritmo de integración numérica de Euler hacia adelante, transformándolas en ecuaciones en diferencias lineales.

Para la discretización se ha usado un paso de cálculo ( $T_s$ ) suficientemente pequeño para seguir la respuesta natural del sistema, siendo 20 nanosegundos en este caso. El desarrollo matemático de la discretización del convertidor se observa en el anexo 6.

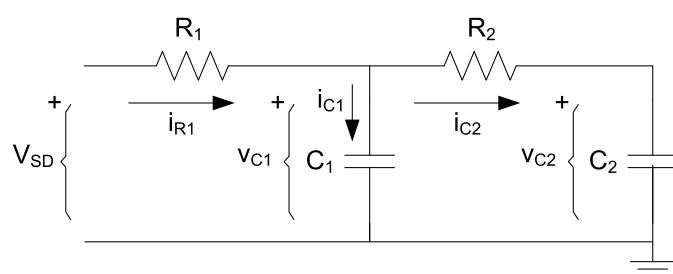

- **Filtro paso bajo de segundo orden**

En este caso se han extraído las ecuaciones diferenciales que modelan el comportamiento lineal del filtro. La discretización de las mismas se ha realizado del mismo modo que el convertidor buck y el desarrollo matemático se observa en el anexo 6.

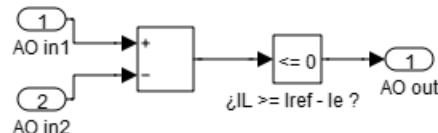

- **Comparador analógico**

Este se ha realizado comparando la corriente medida ( $R_i \cdot I_L$ ) y la señal a la salida del filtro pasivo ( $V_{C2}$ ). La señal **RST\_BIESTABLE** se activa cuando  $R_i \cdot I_L > V_{C2}$ .

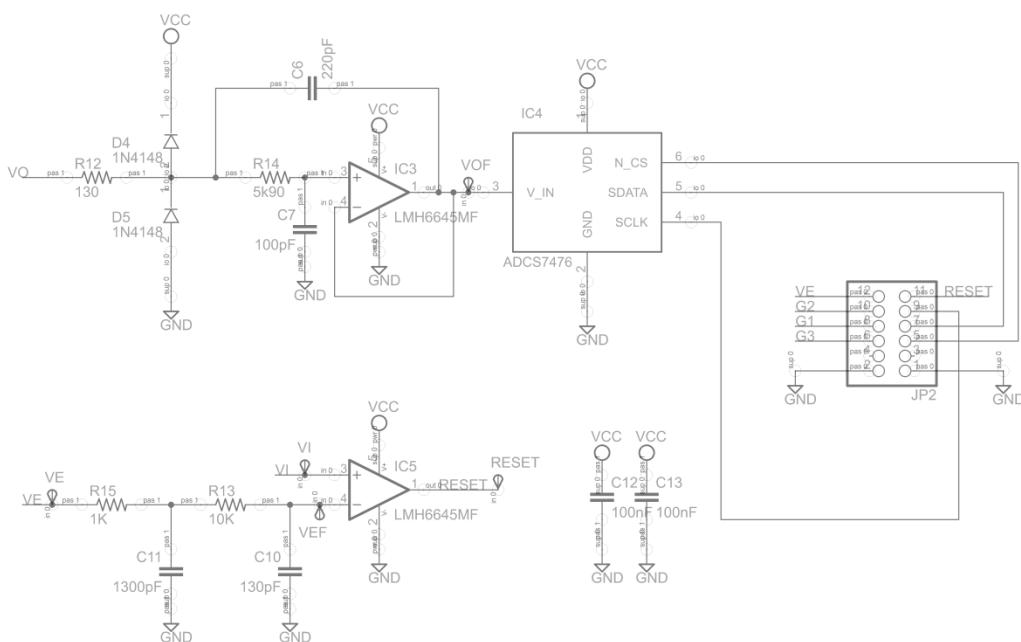

- **Conversor A/D**

Representa el comportamiento de la salida (SDATA) del conversor ADC7476 en función de las entradas (NCS y SCLK). En el apartado 3.2.1 se ha controlado el conversor en función de sus entradas, para poder leer la tensión a salida del conversor.

## 3.2 Diseño del control digital en VHDL

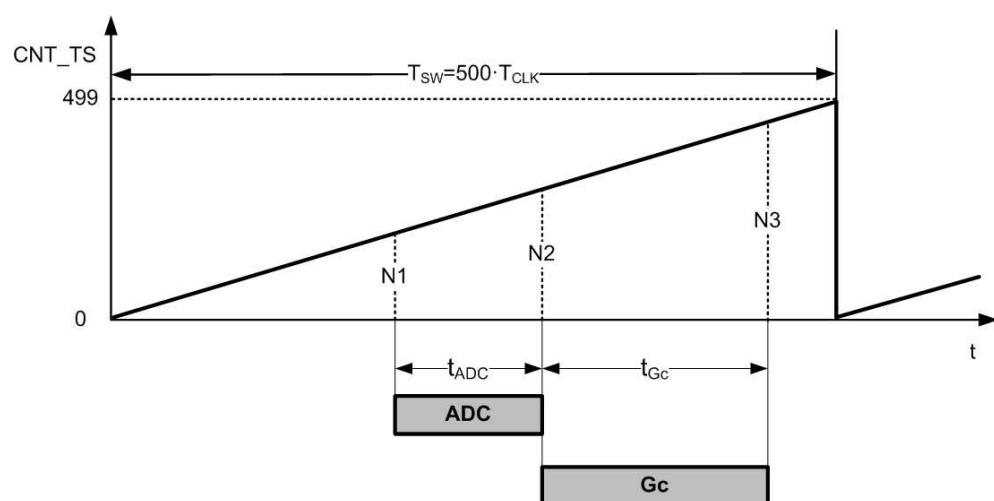

Para realizar el diseño del control se ha usado un reloj (CLK) de 50MHz para la FPGA, con lo que se han necesitado 500 ciclos de reloj en cada periodo de conmutación. Para determinar dichos ciclos se ha realizado un contador ascendente de 9 bits (CNT\_TS).

Figura 25 Planificación temporal del control sobre el contador CNT\_TS.

En la Figura 25 se pueden observar dos tiempos para implementar el control sobre CNT\_TS. Uno es  $t_{ADC}$ , tiempo que le cuesta realizar la conversión de un valor analógico a uno digital al conversor ADC y el otro es  $t_{Gc}$ , tiempo que le cuesta al controlador realizar las operaciones

para regular la tensión de salida del convertidor. Al llegar a N3 se ha actualizado el ciclo de servicio para el siguiente periodo de conmutación.

A partir de CNT\_TS se ha detectado el tiempo de inicio de la conversión (N1) y el propio para el regulador (N2), activando las señales ACT\_ADC y ACT\_CRT respectivamente, para habilitar cada bloque en su debido momento (Figura 24).

### 3.2.1 Control ADC

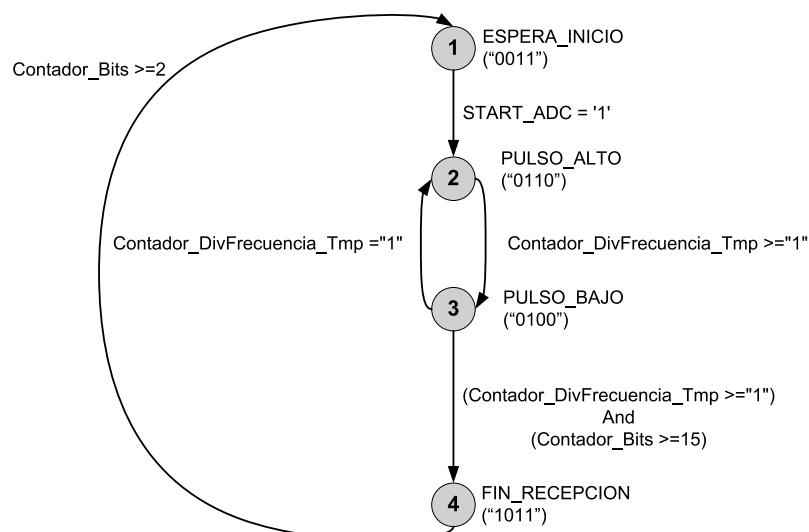

En este apartado se ha realizado el control del conversor analógico digital ADCS7476, de 12 bits salida serie. El dato de salida del ADC deberá ser convertido de serie SDATA a paralelo DA de 8 bits. En este, para realizar el envío y la recepción de datos hay que cumplir una serie de tiempos, los cuales vienen definidos en la hoja de datos del fabricante.

Dicho protocolo se ha realizado mediante una máquina de estados, la cual se puede ver el esquema de la Figura 26. Además se utilizará un contador para llevar la cuenta del número de bits que se han recibido (CONTADOR\_BITS) y otro contador para fijar el número de ciclos que se permanece en cada estado (CONTADOR\_DIV\_FRECUENCIA).

Figura 26 Máquina de estados para el control del proceso de comunicación con el ADC.

El valor de codificación de los estados se utiliza para dar valor a las señales de salida nCS y SCLK. De esta forma a cada bit de los valores utilizados para la codificación de los estados, se le asigna una señal de salida. Los valores de las salidas asignados para cada estado se pueden ver en la Tabla 1.

|         |              | ESTADOS                    |                         |                         |                            |

|---------|--------------|----------------------------|-------------------------|-------------------------|----------------------------|

|         |              | 1) ESPERA_INICIO<br>"0011" | 2) PULSO_ALTO<br>"0110" | 3) PULSO_BAJO<br>"0100" | 4) FIN RECEPCION<br>"1011" |

| SALIDAS | nCS (bit 0)  | 1                          | 0                       | 0                       | 1                          |

|         | SCLK (bit 1) | 1                          | 1                       | 0                       | 1                          |

Tabla 1 Valores que toman las señales de salida para los distintos estados de la máquina de estados.

### 3.2.2 Regulador tipo II-b

El dato DA obtenido del conversor y el resto de señales que intervienen en el control, tienen formato  $\langle w, q \rangle$ , donde  $w$  es el número de bits totales del dato y  $q$  el número de bits de la parte fraccionaria del mismo.

En este caso el dato del conversor ( $\langle 8,0 \rangle$ ) se suministra a una referencia VREF ( $\langle 8,0 \rangle$ ) establecida, con la que proporcionar el error al regulador.

Como se ha comentado en el apartado 3.2, las operaciones aritméticas del regulador (13) se van a distribuir en ciclos de reloj, de tal forma que en cada uno se realice una operación de multiplicación y acumulación (MAC). La Tabla 2 muestra las operaciones de la unidad MAC.

| Ciclo | X      | Y        | ACC                               |

|-------|--------|----------|-----------------------------------|

| N2    | $b_0$  | $e(k)$   | $ACC \leftarrow X \times Y$       |

| N2+1  | $b_1$  | $e(k-1)$ | $ACC \leftarrow ACC + X \times Y$ |

| N2+2  | $b_2$  | $e(k-2)$ | $ACC \leftarrow ACC + X \times Y$ |

| N2+3  | $-a_1$ | $d(k-1)$ | $ACC \leftarrow ACC + X \times Y$ |

| N2+4  | $-a_2$ | $d(k-2)$ | $ACC \leftarrow ACC + X \times Y$ |

Tabla 2 Operación de la unidad MAC

Para realizar la unidad MAC se ha diseñado un contador ascendente de tres bits (CNT\_CICLOS\_CRT), para realizar las operaciones del regulador en su debido momento.

Para almacenar el error actual  $e(k)$  ( $e_0$ ), el error anterior  $e(k-1)$  ( $e_1$ ) y el error anterior anterior  $e(k-2)$  ( $e_2$ ), se ha diseñado un registro de desplazamiento con tres biestables. Por otro lado, se ha realizado un registro de desplazamiento con dos biestables, para almacenar el ciclo de servicio anterior  $d(k-1)$  ( $d_1$ ) y el ciclo de servicio anterior anterior  $d(k-2)$  ( $d_2$ ).

Para hacer sintetizable el código, se ha trabajado con coma fija mediante señales y constantes de tipo signed, de manera que las operaciones sean con números enteros con signo. Al igual que en el tema 4 de [17], se ha determinado el formato de cada una de las señales y constantes, quedando recogidas en la Tabla 3.

| Señal           | Formato $\langle w, q \rangle$ |        |

|-----------------|--------------------------------|--------|

| $e_0, e_1, e_2$ | $\langle 9, 0 \rangle$         |        |

| $d, d_1, d_2$   | $\langle 20, 10 \rangle$       |        |

| ACC             | $\langle 41, 27 \rangle$       |        |

| Constante       | Formato $\langle w, q \rangle$ | Valor  |

| $b_0$           | $\langle 18, 13 \rangle$       | 87327  |

| $b_1$           | $\langle 18, 13 \rangle$       | 10813  |

| $b_2$           | $\langle 18, 13 \rangle$       | -76431 |

| $-a_1$          | $\langle 18, 17 \rangle$       | -74895 |

| $-a_2$          | $\langle 18, 17 \rangle$       | -56177 |

Tabla 3 Formato de las constantes y señales en coma fija.

El resultado de la celda MAC ( $d$ ), se ha almacenado en la señal de salida del regulador (IREF) de 9 bits ( $\langle 8,0 \rangle$ ).

### 3.2.3 Rampa digital de compensación

La amplitud de la rampa digital de compensación se ha determinado en el anexo 5, siendo 0.7 voltios aproximadamente. Para diseñarla en VHDL, se ha dividido por cuatro el contador CNT\_TS, dado que el valor máximo de éste equivale a 3.3 voltios (máxima tensión a la salida de los pines de la FPGA).

La rampa obtenida (RAMPA\_COMP (<7,0>)) se ha limitado entre un 20% y un 80% de su amplitud. El resultado de dicha limitación se ha almacenado en la señal RAMPA\_C (<7,0>), que se ha sustraído a IREF, resultando la señal de entrada al conversor  $\Sigma\Delta$  (IREF\_COMP (<8,0>)).

IREF\_COMP también ha sido limitada a un valor máximo equivalente a 3 voltios, evitando de este modo la saturación del  $\Sigma\Delta$ , ya que el valor máximo a la entrada del mismo son 3.3 voltios. El límite inferior se ha establecido en un valor equivalente a 0.4 voltios, siendo este el valor de la medida del rizado de la corriente, asegurando el modo de conducción continua del convertidor.

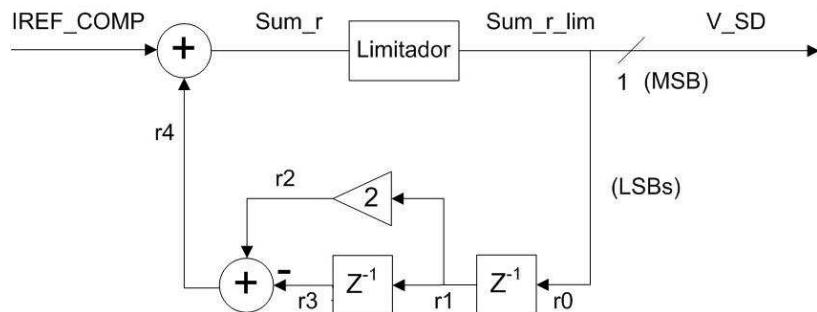

### 3.2.4 Conversor DA sigma-delta de segundo orden

Para realizar en VHDL el conversor sigma delta, se ha partido del modelo que aparece en [15]. La Figura 27 muestra dicho modelo con las señales que intervienen en la conversión:

Figura 27 Modelo del conversor sigma delta de segundo orden.

Los formatos de las señales se recogen en la siguiente tabla

| Señal             | Formato $<w, q>$ |

|-------------------|------------------|

| $IREF\_COMP$      | $< 9, 0 >$       |

| $Sum_r, r_4$      | $< 11, 0 >$      |

| $Sum_r\_lim, r_2$ | $< 10, 0 >$      |

| $r_0, r_1, r_3$   | $< 9, 0 >$       |

| $V\_SD$           | $< 1, 0 >$       |

Tabla 4 Formato de las señales que intervienen en el conversor sigma delta.

Para implementar el conversor se ha realizado un registro de desplazamiento cada ciclo de CLK con dos biestables para determinar  $r_1$  y  $r_3$ . Por otra parte se ha limitado la señal  $Sum\_r$  a  $2^{n_{Sum\_r\_lim}} - 1$  bits, para evitar desbordamientos en el lazo de realimentación.

### 3.2.5 Biestable RS

La salida del biestable RS (Q) se ha diseñado en función de sus señales de control. SET\_BIESTABLE ha de activar dicha salida cada  $T_{sw}$  y se ha obtenido a partir del período calculado en el apartado 3.2. RST\_BIESTABLE ha de desactivar la salida y procede de la comparación analógica de RAMPA\_SD reconstruida (VC2) y la corriente medida en la bobina ( $R_i \cdot I_L$ ).

### 3.2.6 Arranque del convertidor suave (Soft start)

Para realizar el arranque del convertidor se ha incrementado el ciclo de servicio (d) en una unidad, cada periodo de conmutación. Dicho incremento se ha limitado al valor del ciclo de servicio nominal ( $D=0.5$ ), el cual equivale a la mitad del valor máximo de CNT\_TS, ya que su máximo corresponde a todo un periodo de conmutación ( $D=1$ ). Cuando el dato proporcionado por el conversor supere el equivalente a 1.9 voltios, se implantará el control de corriente.

## 3.3 Resultados simulación en Modelsim

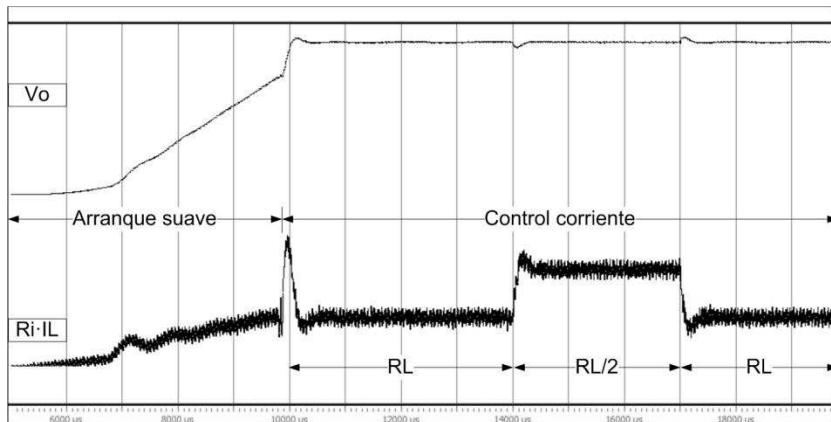

El funcionamiento del control, se ha simulado sobre el test bench mediante la herramienta Modelsim. La Figura 28 muestra la simulación completa realizada.

Figura 28 Simulación del control VHDL en Modelsim.

Figura 29 Detalle del cambio de control y funcionamiento del control de corriente.

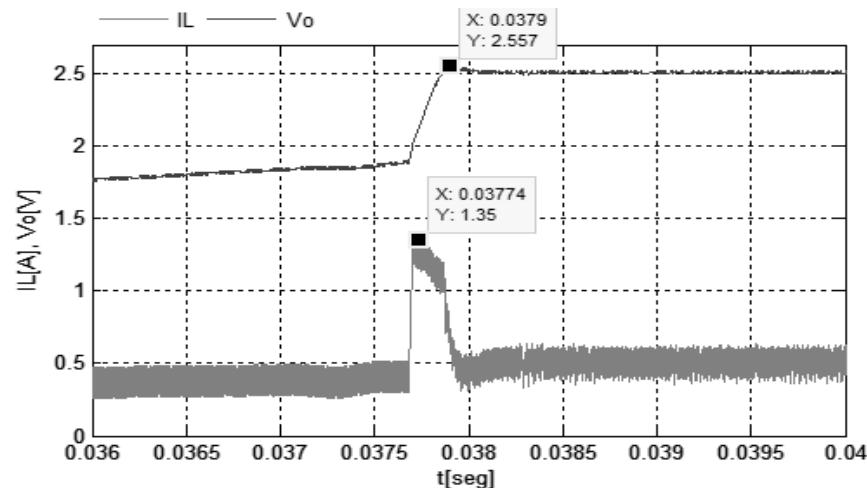

La Figura 29 muestra el detalle del cambio de control, donde la corriente adquiere un pico máximo de:

$$(i_L)_{max} = \frac{(R_i \cdot i_L)_{max}}{R_i} = \frac{2.7}{2} = 1.35 A \quad (17)$$

Su valor medio en régimen permanente:

$$(i_L)_{Av} = \frac{(R_i \cdot i_L)_{Av}}{R_i} = \frac{1}{2} = 0.5 A \quad (18)$$

Y el rizado de la misma es:

$$\Delta i_L = \frac{\Delta(R_i \cdot i_L)}{R_i} = \frac{0.4}{2} = 0.2 A \quad (19)$$

Por otra parte, la tensión adquiere un valor máximo en el cambio de 2.57 voltios, con un error de posición nulo en régimen permanente.

La Figura 30 muestra la respuesta del control ante cambios en la carga del convertidor.

Figura 30 Detalle del funcionamiento del control de corriente ante cambios de carga.

Al reducir la carga a la mitad de su valor la corriente tiene un máximo de:

$$(i_L)_{max} = \frac{(R_i \cdot i_L)_{max}}{R_i} = \frac{2.4}{2} = 1.2 A \quad (20)$$

El rizado de la misma es:

$$\Delta i_L = \frac{\Delta(R_i \cdot i_L)}{R_i} = \frac{0.4}{2} = 0.2 A \quad (21)$$

Y su valor medio en régimen permanente:

$$(i_L)_{Av} = \frac{(R_i \cdot i_L)_{Av}}{R_i} = \frac{2}{2} = 1 A \quad (22)$$

La tensión en este caso cae hasta un mínimo de 2.41 voltios y se recupera al valor establecido en la referencia en aproximadamente 200  $\mu s$ .

Al establecer la carga en su valor inicial la corriente tiene un mínimo de:

$$(i_L)_{max} = \frac{(R_i \cdot i_L)_{max}}{R_i} = \frac{0.6}{2} = 0.3 \text{ A} \quad (23)$$

La tensión en este caso asciende hasta un máximo de 2.6 voltios y se establece en el valor de la referencia en aproximadamente 200  $\mu\text{s}$ .

## 4 Resultados experimentales

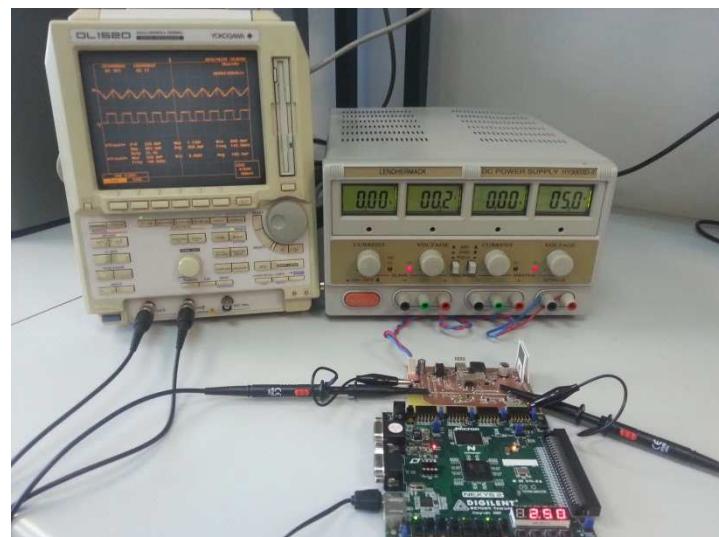

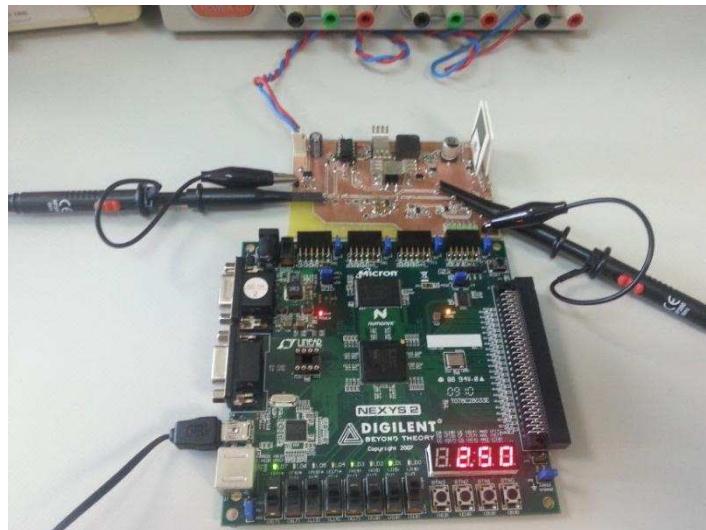

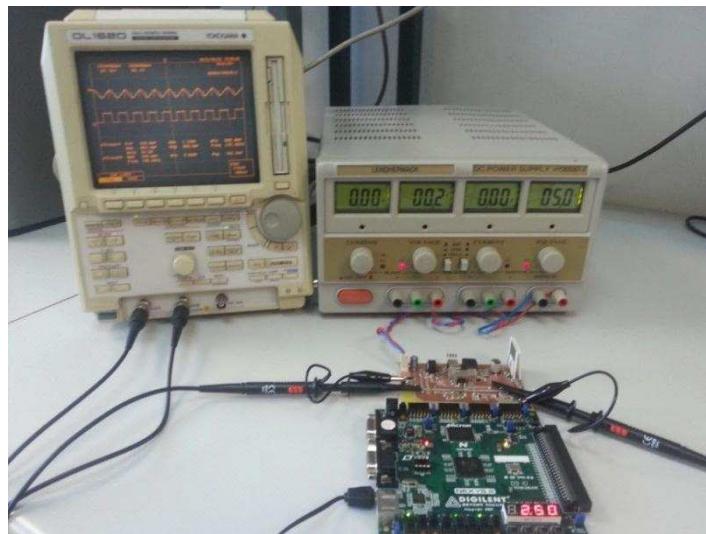

Para la comprobar el funcionamiento del control de manera experimental, la PCB se ha conectado a la placa Nexys2 a través de uno de sus conectores PMOD. Mediante el software de programación para FPGA ISE 10.1 de Xilinx, se han asignado las señales que intervienen en el control a los pines del citado conector.

Figura 31 Montaje experimental del convertidor (arriba) y la tarjeta Nexys 2 (abajo).

En la Figura 32 se observa el montaje realizado para la obtención de medidas experimentales mediante el osciloscopio y la tensión de salida en el visualizador BCD 7 segmentos de la tarjeta Nexys 2.

Figura 32 Montaje para la obtención de medidas experimentales.

Para obtener los resultados experimentales se ha usado un osciloscopio Yokowawa modelo DL1520, con el que medir las señales. Para obtener la tensión de entrada continua con la que alimentar a la tarjeta diseñada, se ha trabajado con una fuente de alimentación Lenchermack.

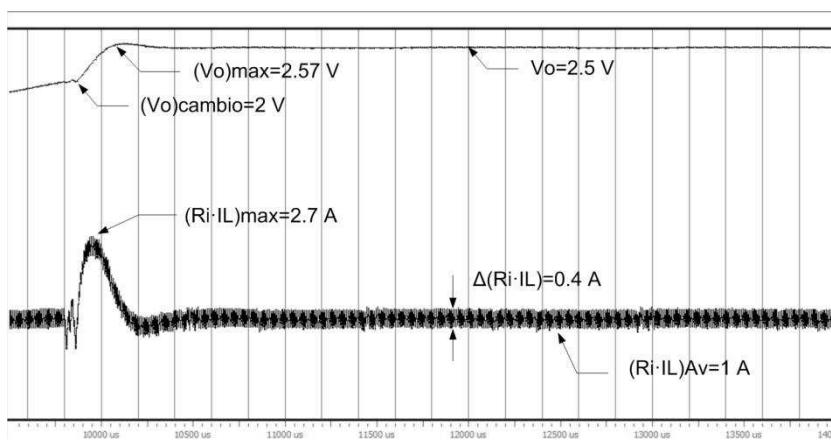

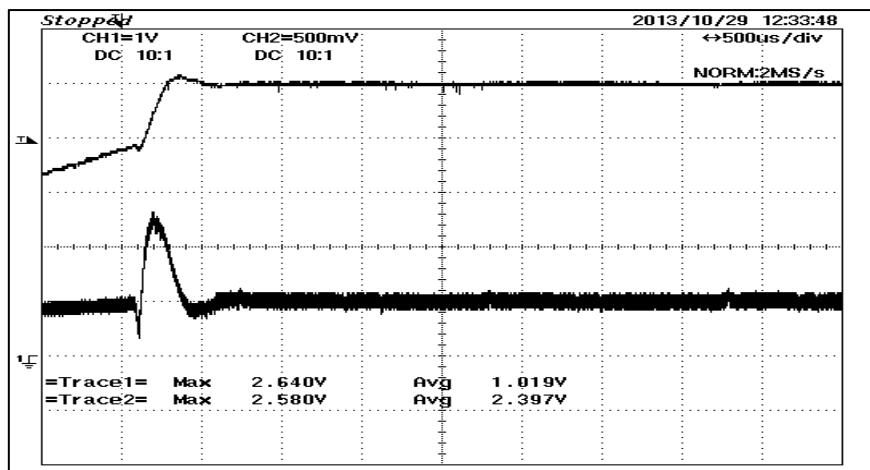

La Figura 33 muestra la captura de las formas de onda de la tensión a la salida (CH2) y la medida de la corriente (CH1) en el cambio de control.

La corriente tiene un pico cuyo valor máximo es:

$$(i_L)_{max} = \frac{2.64}{2} = 1.32 A \quad (24)$$

Su valor medio en régimen permanente es:

$$(i_L)_{Av} = \frac{1}{2} = 0.5 A \quad (25)$$

Y el rizado de la misma es:

$$\Delta i_L = \frac{0.4}{2} = 0.2 A \quad (26)$$

La tensión a la que se produce el cambio es 1.9 voltios, su valor máximo es 2.58 voltios y en régimen permanente es 2.5 voltios.

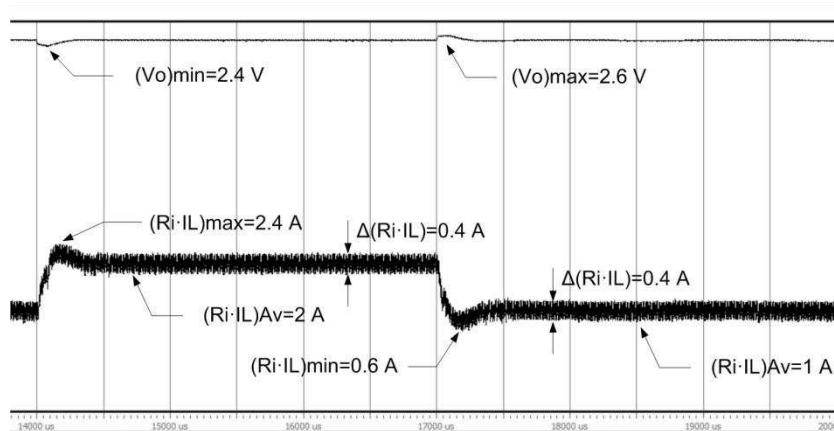

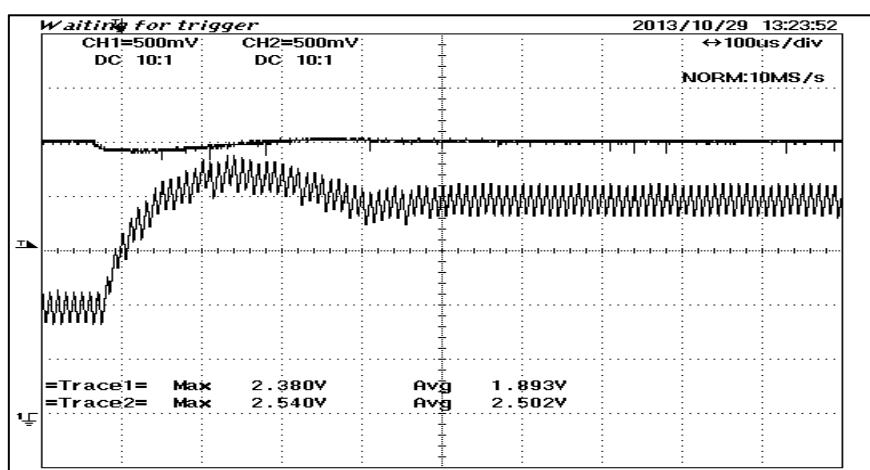

La Figura 34 muestra las mismas medidas en el momento de un cambio de carga a la mitad de su valor.

Figura 34 Captura de  $V_o$  e  $R_i \cdot i_L$  en el cambio de carga a la mitad de su valor.

La corriente tiene un valor máximo de:

$$(i_L)_{max} = \frac{2.38}{2} = 1.19 A \quad (27)$$

Su valor medio en régimen permanente es:

$$(i_L)_{Av} = \frac{1.9}{2} = 0.95 A \quad (28)$$

Y el rizado de la misma es:

$$\Delta i_L = \frac{0.4}{2} = 0.2 A \quad (29)$$

La tensión carga decrece hasta 2.38 voltios, alcanzando de nuevo la tensión de referencia en aproximadamente 200  $\mu$ s.

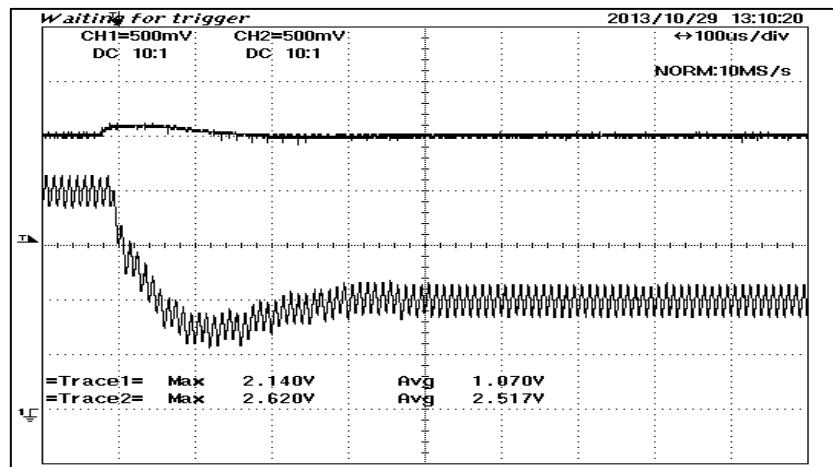

La Figura 34 muestra el momento de un cambio de carga a la totalidad de su valor.

Figura 35 Captura de  $V_o$  e  $R_i \cdot IL$  en el cambio de carga a la totalidad de su valor.

La corriente tiene un valor mínimo de:

$$(i_L)_{min} = \frac{0.6}{2} = 0.3 A \quad (30)$$

Su valor medio en régimen permanente es:

$$(i_L)_{Av} = \frac{1}{2} = 0.5 A \quad (31)$$

Y el rizado de la misma es:

$$\Delta i_L = \frac{0.4}{2} = 0.2 A \quad (32)$$

La tensión aumenta hasta 2.62 voltios, alcanzando de nuevo la tensión de referencia en aproximadamente 200  $\mu$ s.

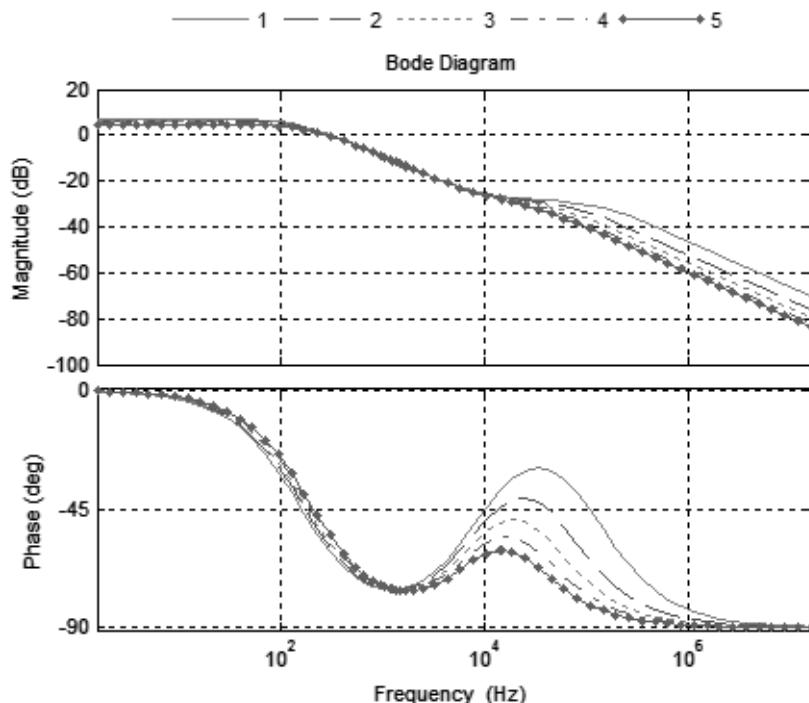

La Tabla 5 muestra la comparación entre los resultados obtenidos en Simulink, los obtenidos en Modelsim y las medidas experimentales, siendo prácticamente idénticos.

|                                            |                    | Simulink    | Modelsim    | Medida experimental |

|--------------------------------------------|--------------------|-------------|-------------|---------------------|

| <b>Cambio de control</b>                   | $(i_L)_{\max}$     | 1.34 A      | 1.35 A      | 1.32 A              |

|                                            | $(V_o)_{\max}$     | 2.55 V      | 2.57 V      | 2.58 V              |

| <b>Control de corriente</b>                | $(i_L)_{Av}$       | 0.5 A       | 0.5 A       | 0.5A                |

|                                            | $\Delta i_L$       | 0.2 A       | 0.2 A       | 0.2 A               |

| <b>Cambio de carga</b><br><b>RL → RL/2</b> | $(i_L)_{\max}$     | 1.19        | 1.2 A       | 1.19 A              |

|                                            | $(i_L)_{Av}$       | 1 A         | 1 A         | 0.95 A              |

|                                            | $\Delta i_L$       | 0.2 A       | 0.2 A       | 0.2 A               |

|                                            | $(V_o)_{\min}$     | 2.45 V      | 2.41 V      | 2.38 V              |

|                                            | $t_{recuperación}$ | 200 $\mu$ s | 200 $\mu$ s | 200 $\mu$ s         |

| <b>Cambio de carga</b><br><b>RL/2 → RL</b> | $(i_L)_{\min}$     | 0.25 A      | 0.3 A       | 0.3 A               |

|                                            | $(V_o)_{\max}$     | 2.57 V      | 2.6 V       | 2.62 V              |

|                                            | $t_{recuperación}$ | 200 us      | 200 $\mu$ s | 200 $\mu$ s         |

Tabla 5 Comparativa de resultados de la simulación de Si mulinkm, Modelsim y las medidas experimentales.

## 5 Conclusiones y trabajo fututo

De los objetivos marcados al principio del presente trabajo, se han llevado a cabo todos y cada uno de ellos.

En primer lugar se ha realizado una modelización matemática del convertidor y su control, con la que se ha diseñado un regulador a través de Matlab, cumpliendo una serie de especificaciones para que el sistema sea estable.

Diseñado el regulador, se ha implementado el convertidor y el control de corriente con señales continuas, con la herramienta SimPowerSystems de Simulink, obteniendo resultados satisfactorios. Despues se ha realizado un control discreto en la herramienta citada, de cara a la implementación en FPGA, donde se ha discretizado el regulador, se ha modelado el conversor  $\Sigma\Delta$  digital y el filtro paso bajo, siendo los resultados muy similares a los del modelo continuo.

Dado el correcto funcionamiento del control en simulación, se ha realizado el control en VHDL y se ha comprobado mediante la herramienta Modelsim que el funcionamiento del mismo es idéntico al implementado en Matlab. Siendo así, se ha programado la FPGA y se ha realizado el control sobre la PCB diseñada en este trabajo.

Por último se han realizado medidas experimentales de las señales del control, obteniendo unos resultados prácticamente idénticos a los extraídos en las simulaciones.

De cara a un futuro, la PCB diseñada se ha dejado en el departamento de electrónica y comunicaciones de la universidad de Zaragoza, por si se realizara otro tipo de control en el que sean necesarios los lazos de realimentación de tensión y corriente. También cabe la posibilidad de poder realizar el control de un buck síncrono.

Otra posibilidad es la enseñanza del control por corriente de pico en la asignatura "Control Digital de Etapas Electrónicas de Potencia", impartida en el máster en ingeniería electrónica de la universidad de Zaragoza.

## Anexos

### 1. Diseño del convertidor

La Figura 36 muestra el circuito típico de un convertidor buck con carga resistiva. En dicho circuito, se puede apreciar la consideración de la resistencia interna del condensador, de cara a la modelización del mismo.

Figura 36 Convertidor buck con carga resistiva.

Para realizar su diseño, al igual que en [18], se han partido de las siguientes especificaciones:

| Parámetro                                        | Símbolo        | Valor    |

|--------------------------------------------------|----------------|----------|

| Tensión de entrada                               | $V_i$          | 5 V      |

| Tensión de salida,                               | $V_o$          | 2.5 V    |

| Corriente de salida                              | $I_o$          | 1 A      |

| Rizado de la tensión de salida                   | $\Delta V_o$   | < 50 mV  |

| Tensión de saturación del transistor             | $V_{sat}$      | 0.11 V   |

| Resistencia en conducción del transistor         | $R_{DS(on)}$   | 0.11 Ω   |

| Impedancia térmica unión ambiente del transistor | $\theta_{JAT}$ | 110 °C/W |

| Tensión en conducción del diodo                  | $V_D$          | 0.5 V    |

| Impedancia térmica unión ambiente del diodo      | $\theta_{JAD}$ | 115 °C/W |

| Frecuencia de conmutación                        | $f_{sw}$       | 100 kHz  |

| Temperatura ambiente                             | $T_A$          | 50 °C    |

Tabla 6 Especificaciones de partida para el diseño del convertidor buck.

#### ▪ Ciclo de servicio

Con los datos de partida lo primero que se ha determinado es el ciclo de servicio nominal en modo de conducción continua:

$$D = \frac{V_o}{V_i} = \frac{2.5}{5} = 0.5 \quad (33)$$

#### ▪ Filtro de salida (L-C)

##### Bobina (L)

El valor de la bobina, se ha elegido para mantener la operación en modo continuo hasta un 10% de la corriente de salida nominal.

El valor del rizado pico a pico de dicha corriente es:

$$\Delta I_O = 2 \cdot 0.1 \cdot I_O = 2 \cdot 0.1 \cdot 1 = 0.2 \text{ A} \quad (34)$$

El rizado de la corriente se puede definir en función de la tensión en la bobina ( $V_L$ ), el tiempo de conmutación a on del transistor ( $t_{on}$ ) y el propio valor de la bobina ( $L$ ).

$$\Delta I_O = \frac{V_L \cdot t_{on}}{L} = \frac{V_L \cdot D}{L \cdot f_{sw}} \quad (35)$$

La tensión en la bobina es:

$$V_L = V_i - V_{sat} - V_o = 5 - 0.11 - 2.5 = 2.39 \text{ V} \quad (36)$$

Despejando  $L$  de (35) y sustituyendo los valores determinados en (33), (34) y (36), resulta:

$$L = \frac{V_L \cdot D}{\Delta I_O \cdot f_{sw}} = \frac{2.39 \cdot 0.5}{0.2 \cdot 100 \cdot 10^3} = 59.75 \mu\text{H} \quad (37)$$

Este valor corresponde al mínimo para asegurar la conducción continua, por lo que se ha elegido una bobina EPCOS modelo B82477P4683M000 de 68  $\mu\text{H}$ .

### Condensador (C)

El condensador, se ha elegido para limitar el rizado de la tensión de salida ( $\Delta V_O$ ) definido en las especificaciones de la Tabla 6. Los tres elementos que contribuyen al rizado son: la resistencia equivalente serie (ESR), La inductancia equivalente serie (ESL) y el propio valor del condensador (C). Suponiendo que todo el rizado de corriente circula por el condensador y approximando ESR a cero, el valor del condensador es:

$$C = \frac{\Delta I_O}{8 \cdot f_{sw} \cdot \Delta V_O} = \frac{0.2}{8 \cdot 100 \cdot 10^3 \cdot 50 \cdot 10^{-3}} = 5 \mu\text{F} \quad (38)$$

Suponiendo que la capacidad es muy grande, el ESR necesario para limitar el rizado a 50 mV es:

$$ESR = \frac{\Delta V_O}{\Delta I_O} = \frac{0.05}{0.2} = 250 \text{ m}\Omega \quad (39)$$

La capacidad debe elegirse al menos 10 veces mayor a la mínima calculada en (38), con un ESR entre el 10% y el 50% del máximo calculado y con una tensión de al menos 1.5  $\cdot V_i$ .

En este caso se ha elegido un condensador Panasonic modelo EEEFP1V221AP de 220  $\mu\text{F}$ , 35 V, el cual posee una ESR de 25  $\text{m}\Omega$  a 100kHz.

### ▪ Transistor (Q)

El transistor elegido para el diseño es un MOSFET canal P, de International Rectifier, modelo IRFR5505PBF. La elección de un canal P simplifica el circuito de disparo del mismo, minimizando los componentes a utilizar.

Para determinar la temperatura que se alcanza en la unión del transistor, se han calculado las pérdidas en conducción:

$$P_{Tcond} = R_{DS(on)} \cdot I_O^2 \cdot D = 0.11 \cdot 1^2 \cdot 0.5 = 55 \text{ mW} \quad (40)$$

Y en conmutación:

$$P_{Tsw} = 0.5 \cdot V_i \cdot I_O \cdot (t_r + t_f) \cdot f_{sw} = 0.5 \cdot 5 \cdot 1 \cdot (28 + 16) \cdot 10^{-9} \cdot 10^5 = 11 \text{ mW} \quad (41)$$

Las pérdidas totales en el transistor son:

$$P_T = P_{Tcond} + P_{Tsw} = 55 \cdot 10^{-3} + 11 \cdot 10^{-3} = 66 \text{ mW} \quad (42)$$

Con estas pérdidas,  $\theta_{JAT}$  y  $T_A$  se ha calculado la temperatura de la unión:

$$T_J = T_A + \theta_{JAT} \cdot P_T = 50 + 110 \cdot 66 \cdot 10^{-3} = 57.26 \text{ }^{\circ}\text{C} \quad (43)$$

En teoría no es necesaria la inclusión de un dissipador para el transistor, ya que la temperatura en la unión no supera la máxima permitida por el fabricante ( $T_{Jmax}=150\text{ }^{\circ}\text{C}$ ). En la práctica por motivos de seguridad se ha incluido un dissipador FISCHER ELEKTRONIK modelo FK 244 08 D PAK, con una impedancia térmica de  $31.5 \text{ }^{\circ}\text{C/W}$ .

#### ■ Diodo

El diodo conduce cuando el transistor se encuentra en corte proporcionando un camino de circulación a la corriente por la bobina. El elegido para ello es un diodo VISHAY modelo SS2P3L, este cumple con las características necesarias para el funcionamiento como diodo de libre circulación en convertidor buck. Dichas características son una baja caída de tensión en conducción para minimizar pérdidas y rapidez en su recuperación en inversa.

La temperatura que se alcanza en la unión del diodo, se ha determinado a partir de las pérdidas en el mismo:

$$P_{Dcond} = V_D \cdot I_O \cdot (1 - D) = 0.5 \cdot 1 \cdot (1 - 0.5) = 250 \text{ mW} \quad (44)$$

Con estas pérdidas,  $\theta_{JAD}$  y  $T_A$  se ha calculado la temperatura de la unión:

$$T_J = T_A + \theta_{JAD} \cdot P_T = 50 + 115 \cdot 250 \cdot 10^{-3} = 78.75 \text{ }^{\circ}\text{C} \quad (45)$$

No es necesaria la inclusión de un dissipador para el diodo, ya que la temperatura en la unión no supera la máxima permitida por el fabricante ( $T_{Jmax}=150\text{ }^{\circ}\text{C}$ ).

## 2. Modelado del convertidor

Para modelar el convertidor buck en pequeña señal y obtener la función de transferencia del mismo, se han seguido por orden los siguientes pasos:

- 1) Extraer las dinámicas de la etapa mediante un análisis de ecuaciones de estado.

- 2) Perturbar las variables del sistema que intervienen en las dinámicas, en torno a un punto en estado estacionario.

- 3) Linealizar y obtener el modelo en pequeña señal.

- 4) Paso al campo transformado de Laplace y obtención de la función de transferencia.

### 1) Análisis de ecuaciones de estado

Las dinámicas citadas corresponden a la bobina y al condensador que forman la etapa. Hay dos posibles configuraciones de la etapa en función del estado del transistor, por consiguiente dos dinámicas de corriente de la bobina y otras dos de tensión del condensador.

- **Transistor ON, diodo OFF.**

Figura 37 Circuito resultante con S ON y D OFF.

Analizando la etapa por mallas resulta:

$$v_L = L \cdot \frac{di_L}{dt} = V_i - v_o \quad (46)$$

Analizando la etapa por nudos resulta:

$$i_C = C \cdot \frac{dv_C}{dt} = i_L - i_o = i_L - \frac{v_o}{R_L} \quad (47)$$

Rescribiendo (47) queda:

$$\frac{v_o - v_C}{R_C} = i_L - \frac{v_o}{R_L} \quad (48)$$

Despejando  $v_o$  de (48):

$$v_o = \frac{R_L \cdot R_C \cdot i_L + v_C \cdot R_L}{R_L + R_C} \quad (49)$$

Sustituyendo (49) en (46), se ha despejado la dinámica de la corriente:

$$\frac{di_L}{dt} = \frac{V_i}{L} - i_L \cdot \frac{R \cdot R_C}{L \cdot (R + R_C)} - v_C \cdot \frac{R}{L \cdot (R + R_C)} \quad (50)$$

Análogamente, sustituyendo (49) en (47), se ha despejado la dinámica de la tensión:

$$\frac{dv_C}{dt} = i_L \cdot \frac{R}{C \cdot (R + R_C)} - v_C \cdot \frac{1}{C \cdot (R + R_C)} \quad (51)$$

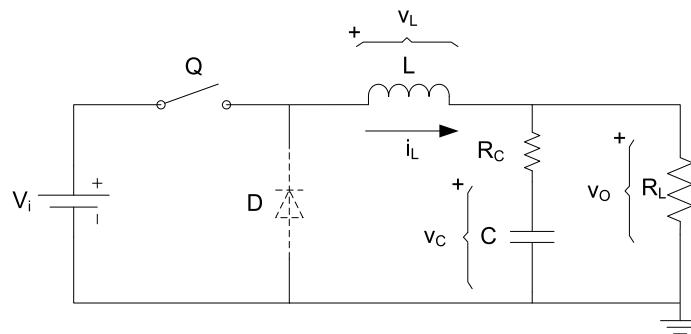

■ **Transistor OFF, diodo ON**

Figura 38 Circuito resultante con S OFF y D ON.

En este caso la dinámica de la corriente es la misma que la obtenida en (50), con la salvedad que la tensión de entrada es nula ( $V_i = 0$ ), despreciando la caída de tensión de conducción del diodo.

$$\frac{di_L}{dt} = -i_L \cdot \frac{R_L \cdot R_C}{L \cdot (R_L + R_C)} - v_C \cdot \frac{R_L}{L \cdot (R_L + R_C)} \quad (52)$$

La dinámica de la tensión en este caso es idéntica a la de (51).

$$\frac{dv_C}{dt} = i_L \cdot \frac{R_L}{C \cdot (R_L + R_C)} - v_C \cdot \frac{1}{C \cdot (R_L + R_C)} \quad (53)$$

Rescribiendo la dinámica de la corriente en función del ciclo de servicio (D):

$$\begin{aligned} \frac{di_L}{dt} = & D \cdot \left( \frac{V_i}{L} - i_L \cdot \frac{R_L \cdot R_C}{L \cdot (R_L + R_C)} - v_C \cdot \frac{R_L}{L \cdot (R_L + R_C)} \right) + \\ & (1 - D) \cdot \left( -i_L \cdot \frac{R_L \cdot R_C}{L \cdot (R_L + R_C)} - v_C \cdot \frac{R_L}{L \cdot (R_L + R_C)} \right) \end{aligned} \quad (54)$$

Desarrollando:

$$\frac{di_L}{dt} = D \cdot \frac{V_i}{L} - i_L \cdot \frac{R_L \cdot R_C}{L \cdot (R_L + R_C)} - v_C \cdot \frac{R_L}{L \cdot (R_L + R_C)} \quad (55)$$

Análogamente, la dinámica de la tensión:

$$\frac{dv_C}{dt} = D \cdot \left( i_L \cdot \frac{R_L}{C \cdot (R_L + R_C)} - v_C \cdot \frac{1}{C \cdot (R_L + R_C)} \right) + (1 - D) \cdot \left( i_L \cdot \frac{R_L}{C \cdot (R_L + R_C)} - v_C \cdot \frac{1}{C \cdot (R_L + R_C)} \right) \quad (56)$$

Desarrollando:

$$\frac{dv_C}{dt} = i_L \cdot \frac{R_L}{C \cdot (R_L + R_C)} - v_C \cdot \frac{1}{C \cdot (R_L + R_C)} \quad (57)$$

## 2) Perturbación de variables

Suponiendo una tensión de entrada constante ( $\hat{v}_i \cong 0$ ), las variables perturbadas son las siguientes:

$$D \rightarrow (D + \hat{d}), i_L \rightarrow (i_L + \hat{i}_L), v_C \rightarrow (v_C + \hat{v}_C) \quad (58)$$

Sustituyendo las perturbaciones en (55) resulta:

$$\frac{d(i_L + \hat{i}_L)}{dt} = (D + \hat{d}) \cdot \frac{V_i}{L} - (i_L + \hat{i}_L) \cdot \frac{R_L \cdot R_C}{L \cdot (R_L + R_C)} - (v_C + \hat{v}_C) \cdot \frac{R_L}{L \cdot (R_L + R_C)} \quad (59)$$

Sustituyendo las perturbaciones en (57) queda:

$$\frac{d(v_C + \hat{v}_C)}{dt} = (i_L + \hat{i}_L) \cdot \frac{R_L}{C \cdot (R_L + R_C)} - (v_C + \hat{v}_C) \cdot \frac{1}{C \cdot (R_L + R_C)} \quad (60)$$

## 3) Modelo de pequeña señal

Para la obtención del modelo de pequeña señal se han desarrollado las ecuaciones de las dinámicas perturbadas, despreciando los términos de continua y los términos de segundo orden. Es decir, se han obtenido las dinámicas considerando únicamente los términos de primer orden ((61) y (62)).

$$\frac{d\hat{i}_L}{dt} = \hat{d} \cdot \frac{V_i}{L} - \hat{i}_L \cdot \frac{R_L \cdot R_C}{L \cdot (R_L + R_C)} - \hat{v}_C \cdot \frac{R_L}{L \cdot (R_L + R_C)} \quad (61)$$

$$\frac{d\hat{v}_C}{dt} = \hat{i}_L \cdot \frac{R_L}{C \cdot (R_L + R_C)} - \hat{v}_C \cdot \frac{1}{C \cdot (R_L + R_C)} \quad (62)$$

## 4) Función de transferencia

A la hora de extraer la función de transferencia que modele el convertidor, debido al control corriente de pico que se va a implementar, el interés está en la relación existente entre la corriente ( $\hat{i}_L$ ) y el ciclo de servicio ( $\hat{d}$ ).

Para extraer la función de transferencia se han pasado las ecuaciones del modelo de pequeña señal al campo transformado de Laplace. De este modo (61) y (62) quedan:

$$s \cdot \hat{i}_L = \hat{d} \cdot \frac{V_i}{L} - \hat{i}_L \cdot \frac{R_L \cdot R_C}{L \cdot (R_L + R_C)} - \hat{v}_C \cdot \frac{R_L}{L \cdot (R_L + R_C)} \quad (63)$$

$$s \cdot \hat{v}_C = \hat{i}_L \cdot \frac{R_L}{C \cdot (R_L + R_C)} - \hat{v}_C \cdot \frac{1}{C \cdot (R_L + R_C)} \quad (64)$$

Despejando  $\hat{v}_C$  de (64) resulta:

$$\hat{v}_C = \hat{i}_L \cdot \frac{R_L}{1 + C \cdot (R_L + R_C) \cdot s} \quad (65)$$

Sustituyendo (65) en (63) queda:

$$s \cdot \hat{i}_L = \hat{d} \cdot \frac{V_i}{L} - \hat{i}_L \cdot \frac{R_L \cdot R_C}{L \cdot (R_L + R_C)} - \hat{i}_L \cdot \frac{R_L}{1 + C \cdot (R_L + R_C) \cdot s} \cdot \frac{R_L}{L \cdot (R_L + R_C)} \quad (66)$$

Desarrollando y agrupando términos, se obtiene la función de transferencia deseada:

$$\frac{\hat{i}_L}{\hat{d}} = V_i \cdot \frac{1 + C \cdot (R_L + R_C) \cdot s}{(R_L + R_C) \cdot L \cdot C \cdot s^2 + (R_L \cdot R_C \cdot C + L) \cdot s + R_L \cdot} \quad (67)$$

### 3. Funcionamiento del control

Como viene explicado en [1], pp. 439-489, el control por corriente de pico se basa en el esquema de la Figura 39.

Figura 39 Diagrama del control modo corriente de pico.

Dicho control está formado por:

- **Lazo externo de tensión:** Este contiene un regulador con el que se controla la tensión de salida ( $V_o$ ) a una referencia dada ( $V_{REF}$ ), proporcionando una referencia para el lazo interno de corriente ( $I_{REF}$ ).

- **Lazo interno de corriente:** En este se realiza la comparación entre la referencia de corriente y la corriente medida, siendo su salida activa cada vez que la corriente supere la de referencia.

- **Circuito de disparo:** Formado por un biestable RS que se activa (S) con un pulso al principio de cada periodo de conmutación ( $T_{sw}$ ), comutando el transistor a *on* e incrementando de este modo la corriente por la bobina. Cuando dicha corriente supera la de referencia, la salida del comparador resetea (R) el biestable, pasando a *off* el transistor, lo cual origina un decremento en la corriente.

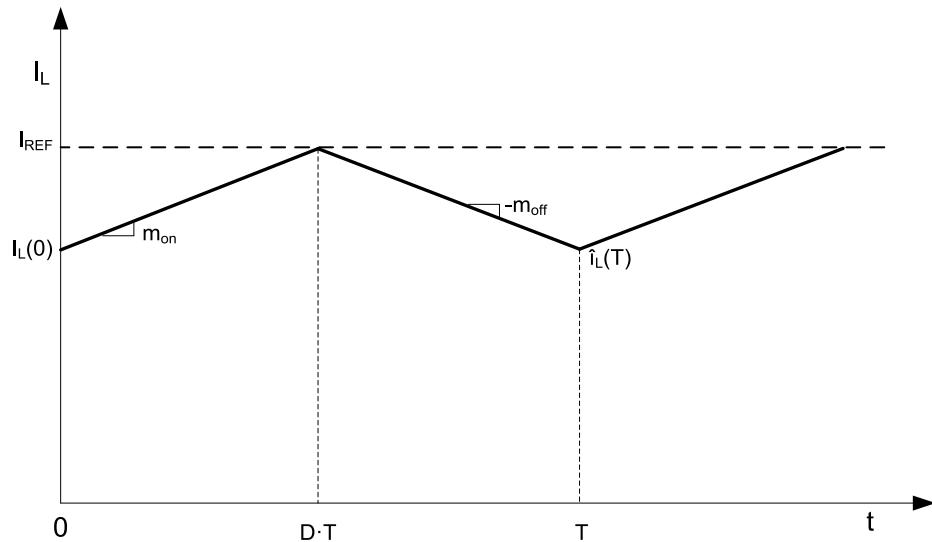

Estando en conducción continua, la forma de onda de la corriente se asemeja a la mostrada en la Figura 40.

Figura 40 Forma de onda de corriente por la bobina.

Las expresiones que definen las pendientes de la corriente en ambos intervalos son:

$$m_{on} = \frac{V_i - v_o}{L} \quad (68)$$

$$m_{off} = \frac{v_o}{L} \quad (69)$$

En el primer intervalo ( $t_{on}$ ) la corriente viene dada por la siguiente expresión:

$$I_L(d \cdot T) = I_{REF} = I_L(0) + m_{on} \cdot d \cdot T \quad (70)$$

En el segundo intervalo ( $t_{off}$ ) la corriente viene dada por la siguiente expresión:

$$I_L(T) = I_L(d \cdot T) - m_{off} \cdot d' \cdot T \quad (71)$$

Sustituyendo (70) en (71) resulta:

$$I_L(T) = I_L(0) + m_{on} \cdot d \cdot T - m_{off} \cdot d' \cdot T \quad (72)$$

En situación de estado estacionario se da la siguiente igualdad:

$$I_L(T) = I_L(0) \quad (73)$$

Por consiguiente:

$$m_{on} \cdot D \cdot T - m_{off} \cdot D' \cdot T = 0 \quad (74)$$

Rescribiendo la ecuación se obtiene:

$$\frac{m_{off}}{m_{on}} = \frac{D}{D'} \quad (75)$$

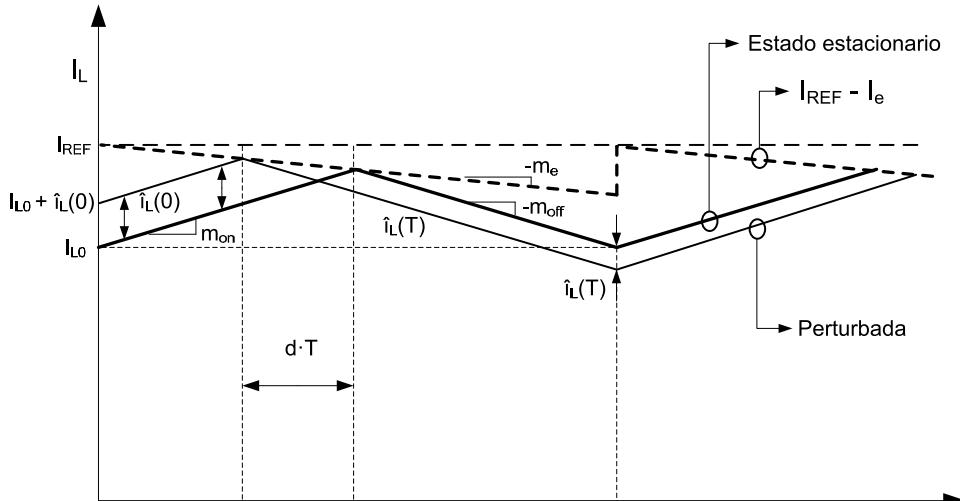

Si se introduce una pequeña perturbación en la corriente  $I_L(0)$ :

$$I_L(0) = I_{L0} + \hat{i}_L(0) \quad (76)$$

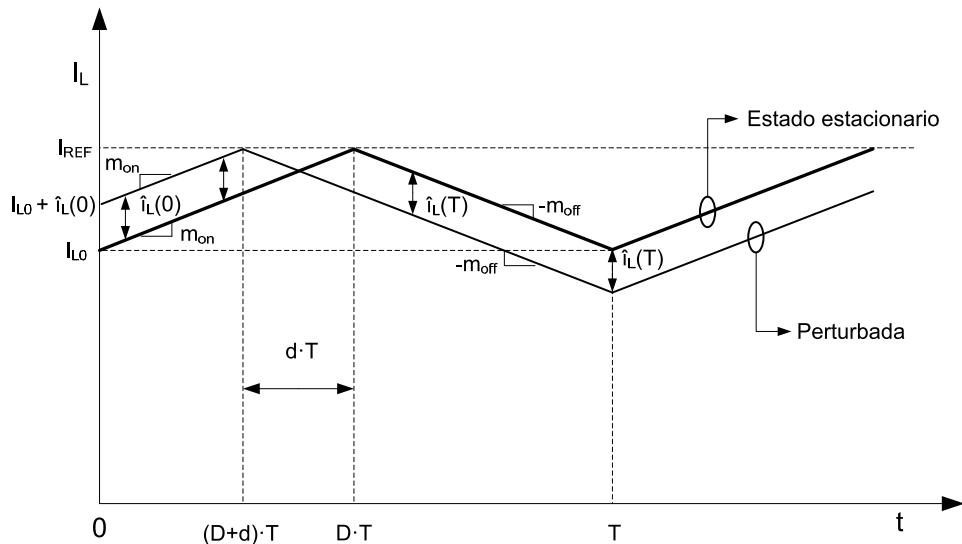

La Figura 41 compara el efecto inicial de la perturbación y la forma de onda sin perturbar en estado estacionario.

Figura 41 Efecto inicial al perturbar la corriente vs. Corriente en estado estacionario.

Los valores de las perturbaciones  $\hat{i}_L(0)$  e  $\hat{i}_L(T)$  se han determinado analizando el intervalo comprendido entre  $(D+d) \cdot T$  y  $D \cdot T$ . La Figura 42 muestra el detalle de la Figura 41 en el intervalo citado.

Figura 42 Detalle en el intervalo  $(D+d) \cdot T$  y  $D \cdot T$

Partiendo de la definición de pendiente de una recta entre dos puntos, se han determinado ambas perturbaciones:

$$\hat{i}_L(0) = -m_{on} \cdot \hat{d} \cdot T \quad (77)$$

$$\hat{i}_L(T) = m_{off} \cdot \hat{d} \cdot T \quad (78)$$

Al dividir (77) entre (78) y despejar  $\hat{i}_L(T)$  resulta:

$$\hat{i}_L(T) = \hat{i}_L(0) \cdot \left( -\frac{m_{off}}{m_{on}} \right) = \hat{i}_L(0) \cdot \left( -\frac{D}{D'} \right) \quad (79)$$

Para el segundo periodo:

$$\hat{i}_L(2 \cdot T) = \hat{i}_L(T) \cdot \left(-\frac{D}{D'}\right) = \hat{i}_L(0) \cdot \left(-\frac{D}{D'}\right)^2 \quad (80)$$

Para el enésimo periodo:

$$\hat{i}_L(n \cdot T) = \hat{i}_L((n-1) \cdot T) \cdot \left(-\frac{D}{D'}\right) = \hat{i}_L(0) \cdot \left(-\frac{D}{D'}\right)^n \quad (81)$$

Analizando el módulo de la corriente

$$|\hat{i}_L(n \cdot T)| \rightarrow \begin{cases} 0, & \text{si } \left|\frac{D}{D'}\right| < 1 \text{ Estable} \\ \infty, & \text{si } \left|\frac{D}{D'}\right| > 1 \text{ Inestable} \end{cases} \quad (82)$$

De (82) se deduce que para un ciclo de servicio por debajo de 0.5, la perturbación desaparece con el paso de los periodos, asegurando la estabilidad del control. Por el contrario, para un ciclo de servicio igual o mayor a 0.5 la perturbación tiende a infinito, produciéndose inestabilidad en el control.

Para mitigar este problema y poder variar el ciclo en todo su rango ( $0 < D < 1$ ), hay que incluir una rampa de compensación de corriente. La Figura 43 muestra el control de la Figura 39 con la rampa de compensación añadida.

Figura 43 Diagrama del control modo corriente de pico con rampa de compensación

Figura 44 Forma de onda de corriente por la bobina con rampa de compensación.

El transistor comutará a off si:

$$I_L(d \cdot T) = I_{REF} - I_E(d \cdot T) \quad (83)$$

Figura 45 Efecto inicial al perturbar la corriente vs. Corriente en estado estacionario

Si del mismo modo que en la Figura 41 se introduce una pequeña perturbación en la corriente  $I_L(0)$ , el efecto inicial de la perturbación que se presenta se observa en la Figura 45.

Realizando un estudio de la perturbación periodo por periodo análogo al comprendido entre la (77) y (82), las perturbaciones resultan:

$$\hat{i}_L(0) = -\hat{d} \cdot T(m_{on} + m_e) \quad (84)$$

$$\hat{i}_L(T) = -\hat{d} \cdot T(m_e - m_{off}) \quad (85)$$

Para el primer periodo la corriente perturbada es:

$$\hat{i}_L(T) = \hat{i}_L(0) \cdot \left( -\frac{m_{off} - m_e}{m_{on} + m_e} \right) \quad (86)$$

Para el enésimo periodo:

$$\hat{i}_L(T) = \hat{i}_L((n-1) \cdot T) \cdot \left( -\frac{m_{off} - m_e}{m_{on} + m_e} \right) = \hat{i}_L(0) \cdot \left( -\frac{m_{off} - m_e}{m_{on} + m_e} \right)^n \quad (87)$$

Definiendo el parámetro alpha como:

$$\alpha = -\frac{m_{off} - m_e}{m_{on} + m_e} = -\frac{1 - m_e/m_{off}}{m_{on}/m_{off} + m_e/m_{off}} = \frac{1 - m_e/m_{off}}{D'/D + m_e/m_{off}} \quad (88)$$

Se deduce que:

$$|\hat{i}_L(n \cdot T)| \rightarrow \begin{cases} 0, & \text{si } |\alpha| < 1 \text{ Estable} \\ \infty, & \text{si } |\alpha| > 1 \text{ Inestable} \end{cases} \quad (89)$$

Valores que se suelen escoger de  $m_e$  son:

$$\begin{aligned} m_e &= m_{off} \\ m_e &= \frac{1}{2} \cdot m_{off} \end{aligned} \quad (90)$$

En este caso se ha escogido la primera de las opciones, siendo un punto de partida en las simulaciones del anexo 5.

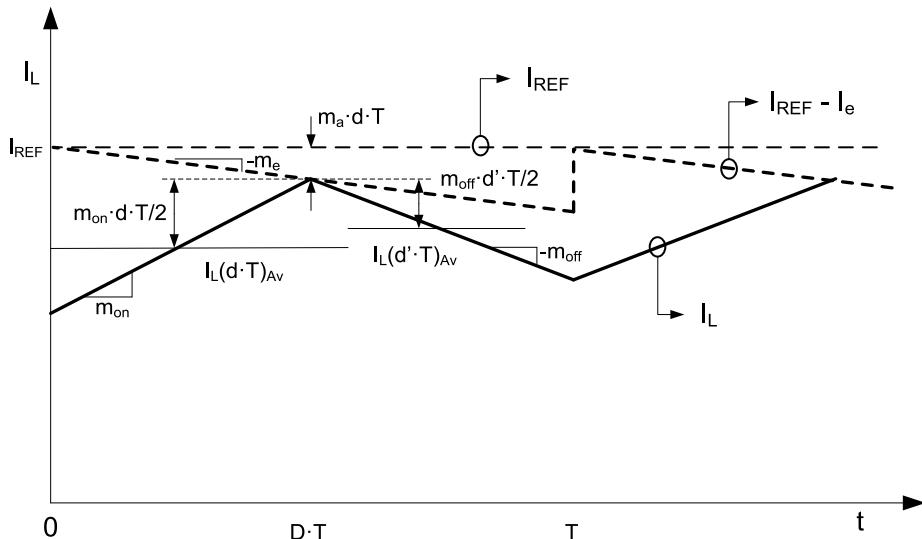

## 4. Modelado del control

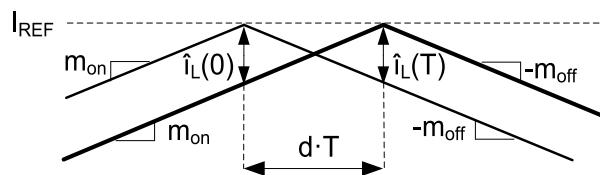

El modelo del control de corriente en pequeña señal, incluyendo la rampa de compensación, se ha extraído analizando la forma de onda de corriente por la bobina ( $I_L$ ) y las formas de onda que intervienen en el control ( $I_{REF}$  e  $I_e$ ), tal y como se muestra en la Figura 46.

Figura 46 Forma de onda de corriente por la bobina con rampa de compensación.

De la Figura 46 se puede deducir la siguiente igualdad:

$$I_L + m_{on} \cdot \frac{D \cdot T}{2} = i_{REF} - m_e \cdot D \cdot T \quad (91)$$

Las variables perturbadas en torno a un punto de trabajo en estado estacionario son:

$$\begin{aligned} D &\rightarrow (D + \hat{d}), I_L \rightarrow (i_L + \hat{i}_L), i_{REF} \rightarrow (i_{REF} + \hat{i}_{REF}) \\ m_{on} &\rightarrow (m_{on} + \hat{m}_{on}), m_{off} \rightarrow (m_{off} + \hat{m}_{off}) \end{aligned} \quad (92)$$

De este modo (91) queda:

$$i_L + \hat{i}_L + (m_{on} + \hat{m}_{on}) \cdot \frac{(D + \hat{d}) \cdot T}{2} = i_{REF} + \hat{i}_{REF} - m_e \cdot (D + \hat{d}) \cdot T \quad (93)$$

Desarrollando, agrupando y despreciando los términos de segundo orden y de continua queda:

$$\hat{i}_L + m_{on} \cdot \frac{\hat{d} \cdot T}{2} + \hat{m}_{on} \cdot \frac{D \cdot T}{2} = \hat{i}_{REF} - m_e \cdot \hat{d} \cdot T \quad (94)$$

Llegado a este punto se puede modelar la relación entre el ciclo de servicio y la diferencia entre la referencia de corriente con rampa de compensación y la corriente medida en la bobina:

$$\hat{i}_{REF} - \hat{i}_L = m_e \cdot \hat{d} \cdot T + m_{on} \cdot \frac{\hat{d} \cdot T}{2} + \hat{m}_{on} \cdot \frac{D \cdot T}{2} \quad (95)$$

Desarrollando:

$$\left( \frac{2 \cdot (\hat{i}_{REF} - \hat{i}_L)}{m_{on}} \right) = \left( 1 + \frac{2 \cdot m_e}{m_{on}} \right) \cdot \hat{d} \cdot T + \hat{m}_{on} \cdot \frac{D \cdot T}{m_{on}} \quad (96)$$

Definiendo factor n como:

$$n = \left( 1 + \frac{2 \cdot m_e}{m_{on}} \right) \quad (97)$$

Sustituyendo (97) en (96) y despejando la perturbación del ciclo de servicio resulta:

$$\hat{d} = \left( \frac{2 \cdot (\hat{i}_{REF} - \hat{i}_L)}{m_{on} \cdot n \cdot T} \right) - \hat{m}_{on} \cdot \frac{D}{m_{on} \cdot n} \quad (98)$$

Conocido el valor de  $m_{on}$ :

$$m_{on} = \frac{V_i - v_o}{L} \quad \left\{ \begin{array}{l} \text{Desarrollando: } m_{on} = \frac{v_o \cdot (1-D)}{D \cdot L} \\ \text{Perturbando } V_i \text{ y } v_o: \hat{m}_{on} = \frac{\hat{v}_i}{L} - \frac{\hat{v}_o}{L} \end{array} \right. \quad (99)$$

Sustituyendo los resultados de (99) en (98) y desarrollando se obtiene la relación de la citada anteriormente con la compensación de posibles perturbaciones en  $V_i$  y  $v_o$ :

$$\hat{d} = \frac{2 \cdot D \cdot L}{v_o \cdot (1-D) \cdot T_{sw} \cdot n} \cdot (\hat{i}_{REF} - \hat{i}_L) - \frac{D^2}{v_o \cdot (1-D) \cdot n} (\hat{v}_i - \hat{v}_o) \quad (100)$$

De este modo se puede realizar un diagrama de bloques de control de corriente como el que se muestra en la Figura 47.

Figura 47 Diagrama de bloques resultante del control de corriente.

Una vez obtenido el anterior diagrama se ha ido construyendo modularmente el resto del control. En el anexo 2, se ha determinado la función de transferencia que relaciona el ciclo de servicio y la corriente por la bobina. Añadiendo dicha función al diagrama de la Figura 47 resulta:

Figura 48 Diagrama de bloques control de corriente y función de transferencia del buck.

El siguiente paso es la inclusión del lazo de control de tensión. Para ello se ha determinado la tensión en la carga (101) a partir de la impedancia equivalente a la salida del convertidor y la corriente por la inductancia.

$$\hat{v}_o = \hat{i}_L \cdot Z_o(s) = \hat{i}_L \cdot \frac{(R_C \cdot C \cdot s + 1) \cdot R}{(R_C + R) \cdot C \cdot s + 1} \quad (101)$$

Se desea obtener un error de posición nulo de tensión y un margen de fase mínimo de 60 grados a la frecuencia de cruce del sistema. Como se explica en [14], el regulador a incluir en el sistema para cumplir dichas condiciones, es de tipo II-b y su expresión viene dada por:

$$H(s) = K \cdot \frac{1}{s} \cdot \frac{1 + \frac{s}{w_z}}{1 + \frac{s}{w_p}} \quad (102)$$

La frecuencia de cruce del sistema ( $f_c$ ), se ha ajustado mediante la ganancia  $K$  del regulador una década por debajo de la frecuencia de conmutación. El hecho de incluir un integrador para anular el error de posición, añade una fase de menos 90 grados a lo largo de todo el rango de frecuencias, pudiendo inestabilizar el sistema a la frecuencia de cruce. Para obtener el margen de fase deseado a dicha frecuencia y asegurar la estabilidad del sistema, se ha diseñado un PAF-PRF con el cero ( $w_z$ ) y el polo ( $w_p$ ) que forman el regulador tipo II-b respectivamente.

La Figura 49 muestra el diagrama de bloques que modela el comportamiento y el control por corriente de pico del convertidor buck.

Figura 49 Diagrama de bloques del control modo pico corriente completo.

El ajuste del regulador se ha realizado mediante la herramienta Sisotool de Matlab en el anexo 5, donde se han desestimado las posibles perturbaciones en  $V_i$ , ya que esta se ha obtenido de una fuente de alimentación comercial. También se han despreciado posibles perturbaciones en  $v_o$ , ya que su rizado es despreciable frente a su valor medio, tal y como se ha determinado en el anexo 1.

## 5. Simulación del control en Matlab/Simulink