## Trabajo Fin de Máster

Diseño de un ecualizador en tiempo continuo para

aplicaciones en comunicaciones serie de alta

velocidad

Autor/es

Diego Pérez Sanz

Director/es

Concepción Aldea Chagoyen

José María García del Pozo Faldos

Escuela de Ingeniería y Arquitectura de la Universidad de Zaragoza

2013

## RESUMEN

### DISEÑO DE UN ECUALIZADOR EN TIEMPO CONTINUO PARA APLICACIONES EN COMUNICACIONES SERIE DE ALTA VELOCIDAD

En este proyecto se propone como objetivo principal el diseño e implementación de arquitecturas de ecualización en tiempo continuo para aplicaciones en comunicaciones serie de alta velocidad.

Para ello se abordará un estudio teórico y revisión bibliográfica de soluciones de bajo coste para la transmisión de alta capacidad por fibra óptica. De los diferentes subsistemas que componen la arquitectura del receptor, este trabajo se centrará en el amplificador de transimpedancia y en el ecualizador necesario para aumentar el ancho de banda de los bloques anteriores, permitiendo la obtención de arquitecturas más eficaces del *front-end* analógico del receptor de fibra óptica, minimizando de esta manera los efectos que impactan seriamente sobre la sensibilidad y velocidad total del sistema.

Se llevará a cabo la caracterización experimental del prototipo T2-GDE-2013. Para ello será necesario abordar en primer lugar una primera fase consistente en la unión de un fotodiodo S5973 de Hamamatsu con el prototipo del TIA en un encapsulado DIP. Posteriormente se llevará a cabo la caracterización experimental de este bloque. Estas actividades implican la familiarización con la instrumentación necesaria y el proceso específico de medida.

Una vez determinada la respuesta del TIA se procederá al diseño de un ecualizador con elementos discretos. En dicho diseño se abordará en primer lugar la elección de una topología adecuada a las necesidades particulares del T2-GDE-2013. Una vez determinada la arquitectura se procederá a la selección de componentes prestando especial atención a los elementos activos. La caracterización del bloque propuesto se realizará en dos fases: 1) mediante simulación, haciendo uso de programas como *Matlab* u *OrCAD* y 2) experimentalmente, mediante el diseño y montaje de PCBs mediante *Eagle* o *PCAD*.

La última fase del proyecto consistiría en estudiar la posible migración de la topología discreta, objeto del estudio anterior, a un proceso de integración monolítico, para su posible utilización en receptores multiestándar en las bandas de transmisión de hasta 10 Gbps.

**Palabras Clave:** Ecualizador, Fibra Óptica de Plástico (POF), Amplificador de Transimpedancia (TIA), Comunicaciones Serie, Diseño PCBs.

## ÍNDICE

|                                                                                               |    |

|-----------------------------------------------------------------------------------------------|----|

| Lista de parámetros.....                                                                      | 5  |

| Lista de acrónimos .....                                                                      | 6  |

| 1.    Introducción .....                                                                      | 7  |

| 1.1.    Interés y objetivos del proyecto .....                                                | 8  |

| 1.2.    Descripción del proyecto y metodología .....                                          | 9  |

| 1.3.    Herramientas utilizadas.....                                                          | 9  |

| 2.    Sistemas de comunicaciones por fibra óptica .....                                       | 10 |

| 2.1.    Arquitectura de un sistema de comunicaciones por fibra óptica .....                   | 10 |

| 2.2.    Limitaciones de las fibras.....                                                       | 11 |

| 2.3.    Limitaciones del fotodetector .....                                                   | 14 |

| 2.4.    Amplificador de transimpedancia.....                                                  | 17 |

| 3.    Caracterización experimental del prototipo T2-GDE-2013.....                             | 21 |

| 3.1.    Descripción del TIA T2-GDE-2013 .....                                                 | 21 |

| 3.2.    Técnica de ensamblaje del fotodetector .....                                          | 22 |

| 3.3.    Comportamiento y caracterización experimental del sistema TIA+PD .....                | 23 |

| 4.    Diseño del ecualizador en tiempo continuo .....                                         | 29 |

| 4.1.    Técnicas de ecualización.....                                                         | 29 |

| 4.2.    Análisis tecnológico .....                                                            | 31 |

| 4.3.    Ecualizador BJT active shunt peaking .....                                            | 32 |

| 4.3.1.    Diseño del ecualizador BJT <i>active shunt peaking</i> .....                        | 32 |

| 4.3.2.    Implementación del ecualizador BJT <i>active shunt peaking</i> .....                | 35 |

| 4.3.3.    Implementación del ecualizador BJT <i>active shunt peaking</i> para alta frecuencia | 38 |

| 4.4.    Ecualizador BJT <i>pasive shunt peaking</i> .....                                     | 41 |

| 4.4.1.    Diseño del ecualizador <i>pasive shunt peaking</i> .....                            | 41 |

| 4.4.2.    Implementación del ecualizador BJT <i>pasive shunt peaking</i> .....                | 43 |

| 5.    Conclusiones .....                                                                      | 49 |

| 5.1.    Conclusiones generales .....                                                          | 49 |

| 5.2.    Líneas futuras .....                                                                  | 49 |

| 6.    Referencias.....                                                                        | 51 |

| ANEXO I: diagramas de ojos .....                                                              | 53 |

| ANEXO II: MATLAB .....                                                                        | 55 |

| ANEXO III: TIA.....                                                                           | 56 |

| ANEXO IV: estructuras de ecualizadores con MOSFET .....                                       | 64 |

|                                   |    |

|-----------------------------------|----|

| ANEXO V: planos .....             | 69 |

| ANEXO VI: <i>datasheets</i> ..... | 76 |

## **Lista de parámetros**

|                |                                                           |

|----------------|-----------------------------------------------------------|

| $\beta$        | Ganancia en corriente                                     |

| $\Phi$         | Diámetro                                                  |

| $\lambda$      | Longitud de onda                                          |

| $A_N$          | Apertura numérica                                         |

| $BW$           | Ancho de banda                                            |

| $BW_n$         | Ancho de banda del ruido referido a la entrada            |

| $C_{BC}$       | Capacidad parásita base-colector de un transistor bipolar |

| $C_{BE}$       | Capacidad parásita base-emisor de un transistor bipolar   |

| $C_{PD}$       | Capacidad de deplexión de un fotodiodo                    |

| $g_m$          | Transconductancia                                         |

| $H_i$          | Función de transferencia                                  |

| $I_C$          | Corriente de colector                                     |

| $I_D$          | Corriente de drenador                                     |

| $I_{DK}$       | Corriente de oscuridad de un fotodiodo                    |

| $I_{n, A}^2$   | Ruido referido a la entrada del amplificador operacional  |

| $I_{n, IN}^2$  | Ruido referido a la entrada del TIA                       |

| $I_{n, PIN}^2$ | Ruido producido por el fotodiodo                          |

| $I_{n, RF}^2$  | Ruido térmico                                             |

| $I_{PIN}$      | Corriente generada por un fotodiodo PIN                   |

| $k$            | Constante de Boltzman                                     |

| $L$            | Longitud del canal de un transistor MOS                   |

| $n$            | Índice de refracción                                      |

| $q$            | Carga eléctrica del electrón                              |

| $R_B$          | Resistencia de base de un transistor bipolar              |

| $s$            | Frecuencia compleja                                       |

| $T$            | Temperatura                                               |

| $T_R$          | Transresistencia                                          |

| $V_{BE}$       | Voltaje base-emisor                                       |

| $V_{CE}$       | Voltaje colector-emisor                                   |

| $V_{DD}$       | Voltaje de alimentación                                   |

| $V_{DS}$       | Voltaje drenador-fuente                                   |

| $V_{GS}$       | Voltaje puerta-fuente                                     |

| $V_R$          | Voltaje en inversa                                        |

| $V_{TH}$       | Tensión umbral de transistores MOS                        |

| $W$            | Anchura del transistor MOS                                |

## **Lista de acrónimos**

|       |                                                            |

|-------|------------------------------------------------------------|

| AC    | <i>Alternating current</i>                                 |

| BER   | <i>Bit error rate</i>                                      |

| BERT  | <i>Bit error rate test</i>                                 |

| BJT   | <i>Bipolar junction transistor</i>                         |

| BW    | <i>Bandwidth</i>                                           |

| CD    | <i>Common drain</i>                                        |

| CG    | <i>Common gate</i>                                         |

| CMOS  | <i>Complementary metal oxide semiconductor</i>             |

| CSIC  | Consejo superior de investigaciones científicas            |

| DC    | <i>Direct current</i>                                      |

| DCA   | <i>Digital communications analyzer</i>                     |

| DIP   | <i>Dual inline package</i>                                 |

| DUT   | <i>Device under test</i>                                   |

| EMI   | <i>Electromagnetic interference</i>                        |

| EQ    | <i>Equalizer</i>                                           |

| EQ-CT | <i>Continuous time equalizer</i>                           |

| EQ-P  | <i>Passive equalizer</i>                                   |

| FIR   | <i>Finite impulse response</i>                             |

| GI    | <i>Graded index</i>                                        |

| GOF   | <i>Glass optic fiber</i>                                   |

| HAN   | <i>Home area network</i>                                   |

| HBT   | <i>Heterojunction bipolar transistor</i>                   |

| HFET  | <i>Heterostructure field effect transistor</i>             |

| HDTV  | <i>High definition television</i>                          |

| IDE   | <i>Integrated development environment</i>                  |

| ISI   | <i>Interference inter symbol</i>                           |

| LA    | <i>Limiter amplifier</i>                                   |

| LAN   | <i>Local area network</i>                                  |

| NMOS  | <i>N-channel metal oxide semiconductor</i>                 |

| MOS   | <i>Metal oxide semiconductor</i>                           |

| PCB   | <i>Printed circuit board</i>                               |

| PD    | <i>Photodiode</i>                                          |

| PIN   | <i>PN junction with isolated region</i>                    |

| PMOS  | <i>P-channel metal oxide semiconductor</i>                 |

| POF   | <i>Plastic optic fiber</i>                                 |

| PRBS  | <i>Pseudorandom binary sequence</i>                        |

| RCLED | <i>Resonant cavity light emitting diode</i>                |

| RX    | <i>Receiver</i>                                            |

| SI    | <i>Step index</i>                                          |

| SMA   | <i>Subminiature version A</i>                              |

| SMD   | <i>Surface mounted device</i>                              |

| SMF   | <i>Single mode fiber</i>                                   |

| SNR   | <i>Signal to noise ratio</i>                               |

| SPICE | <i>Simulation program with integrated circuit emphasis</i> |

| TIA   | <i>Transimpedance amplifier</i>                            |

| TX    | <i>Transmitter</i>                                         |

| VCSEL | <i>Vertical cavity surface emitting laser</i>              |

## 1. Introducción

En los últimos años se ha producido un enorme crecimiento de las comunicaciones de datos a medida que los dispositivos ofrecen más prestaciones. Además, los usuarios esperan tener los mismos servicios de banda ancha en áreas como trabajo, hogar y vehículo. Hoy en día, en nuestros hogares encontramos múltiples conexiones eléctricas de todo tipo y en cualquier habitación, desde la línea telefónica hasta el cable coaxial de la televisión. Este último, con varias décadas de historia, presenta ciertas dificultades para adaptarse a la actual demanda de televisión en alta definición. Las actuales emisiones en HDTV requieren una velocidad de datos de casi 3 Gb/s por canal. Estos sistemas de transmisión convencionales presentan problemas a estas velocidades para longitudes grandes y son complicados de instalar.

Los sistemas de comunicaciones basados en fibra óptica de vidrio (GOF) soportan velocidades de transmisión muy superiores y ofrecen una total inmunidad frente a interferencias de tipo electromagnético. Sin embargo, la instalación de estos sistemas es complicada y costosa, lo que la hace inaccesible a la mayoría de usuarios.

La fibra óptica de plástico (POF) es una alternativa más económica y flexible tanto a los sistemas de fibra óptica de vidrio como a la transmisión por hilo de cobre, especialmente en redes de comunicaciones de corta distancia (redes LAN), por su mayor ancho de banda (BW), robustez y menor coste.

| POF | Cable de Cobre                      | Fibra de vidrio                         |

|-----|-------------------------------------|-----------------------------------------|

|     | Inmunidad total al EMI              | Conexiones optoelectrónicas más simples |

|     | Empleo de canalizaciones existentes | Diodos (RCLED) o láser (VCSEL)          |

|     | Cables más delgados                 | Solución más económica                  |

**Tabla 1. Tabla comparativa de prestaciones de las POF**

Entre las ventajas que ofrece la POF podemos citar: flexibilidad, ligereza, robustez, inmunidad al ruido electromagnético y una fácil conectividad, que permite una instalación rápida y sencilla por el propio usuario sin requerir de personal especializado.

Pese a no ser tan rápida como la GOF, presenta una velocidad máxima considerable (hasta varios Gbps) que proporciona un salto cualitativo comparada con el par de cobre tradicional (100Mbps). [ZIE08] y [ANT10].

**Fig. 1 Fibra óptica de plástico (POF)**

### 1.1. Interés y objetivos del proyecto

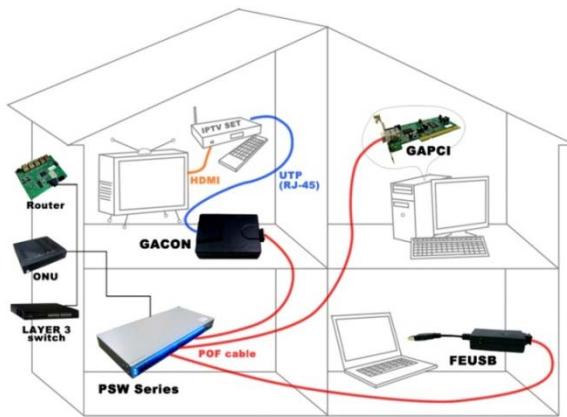

Debido a las características expuestas anteriormente, cada vez está más extendido el uso de estos sistemas tanto en los hogares (HAN), Fig. 2, como en equipos de control automático, en entornos de fabricación ruidosos y en la industria automovilística. A nivel de usuario nos permitirán crear redes internas de alta velocidad en nuestras casas, pudiendo utilizar las canalizaciones eléctricas ya instaladas sin perder rendimiento, al no verse afectadas por el ruido electromagnético [KOO11].

Fig. 2 Fibra óptica de plástico (POF)

El bajo coste y la mayor robustez de la POF conlleva unas limitaciones importantes, como son su elevada atenuación y distorsión de la señal.

La principal desventaja de la SI-POF (*Step-Index POF*) es el bajo valor del producto longitud-ancho de banda (45MHz·100 m) debido a la dispersión cromática y modal [ZIE08] que sufre la señal al viajar por la fibra. Como los niveles de interferencia intersímbolo (ISI) aumentan considerablemente conforme la velocidad de transmisión o *bitrate* supera el ancho de banda (BW) del canal, la tasa de error de transmisión (BER) puede ser inaceptable para un determinado estándar de comunicación.

Otra limitación radica en el tipo de fotodiodos empleados en estos sistemas de comunicación, diodos PIN de áreas grandes y con capacidades parásitas intrínsecas elevadas [SÄC05]. Estas limitaciones imponen serias restricciones en diseño del receptor del sistema de comunicaciones.

Si buscamos soluciones económicas para sistemas de comunicaciones de corta distancia, una buena elección será el uso de POF para el canal de fibra, pero siendo necesario aplicar técnicas de ecualización para conseguir anchos de banda a precios competitivos con sistemas convencionales como el cobre [BAN08], [DON10] y [GIM11].

El objetivo de este trabajo fin de máster (TFM) será corregir las limitaciones frecuenciales en un receptor de POF mediante el diseño y desarrollo de un ecualizador en tiempo continuo para aplicaciones en comunicaciones serie de alta velocidad.

## 1.2. Descripción del proyecto y metodología

En este TFM se busca implementar un ecualizador en tiempo continuo que sea capaz de corregir las limitaciones frecuenciales que presenta un sistema óptico basado en POF aumentando de esta manera el BW.

Para la realización del trabajo, en primer lugar se ha llevado a cabo un estudio teórico y una revisión bibliográfica, en particular, de soluciones de bajo coste para comunicaciones serie de alta velocidad centrándose en profundidad en las etapas preamplificadoras y técnicas de ecualización [AZN13], [GIM13b] y [SAN13]. A continuación se ha realizado una caracterización experimental del prototipo de amplificador de transimpedancia T2-GDE-2013 (TIA) más fotodiodo (PD), analizando su comportamiento e identificando su BW.

Una vez conocidas las limitaciones frecuenciales y vistas las diferentes opciones y técnicas existentes de ecualización, se ha pasado al análisis de la estructura elegida y a la posterior implementación del ecualizador en tiempo continuo con componentes discretos para la caracterización experimental del bloque utilizando instrumentación específica.

Finalmente se han extraído una serie de conclusiones evaluando todas las etapas involucradas en el trabajo y de donde se extraen líneas futuras de actuación.

## 1.3. Herramientas utilizadas

### SOFTWARE:

- MATLAB/SIMULINK: Herramienta de software matemático que ofrece un entorno de desarrollo integrado (IDE) con un lenguaje de programación propio. Utilizado como herramienta matemática, visual y de simulación para los estudios teóricos del TFM.

- OrCADPSpice AD: Programa utilizado para la simulación eléctrica de los circuitos mediante el uso de modelos *Spice* de los diferentes componentes.

- EAGLE: Programa de diseño por computador de placas de circuito impreso (PCB) a partir de la realización de esquemáticos.

### INSTRUMENTACIÓN:

- BERT N4906A, Agilent: Permite medir el BER (*Bit error ratio*) y genera señales PRBS (*Pseudorandom binary sequences*) que permiten obtener información sobre el sistema de transmisión.

- DCA 86100C, Agilent: Analizador de comunicaciones digitales que permite visualizar (diagramas de ojo) y analizar señales periódicas (PRBS).

- ZVL Rhode&Schwarz: Analizador de redes vectorial utilizado para obtener las respuestas frecuenciales del ecualizador.

- MSO9404A, Agilent: Osciloscopio con el que se han realizado diferentes medidas y pruebas en los circuitos.

## 2. Sistemas de comunicaciones por fibra óptica

### 2.1. Arquitectura de un sistema de comunicaciones por fibra óptica

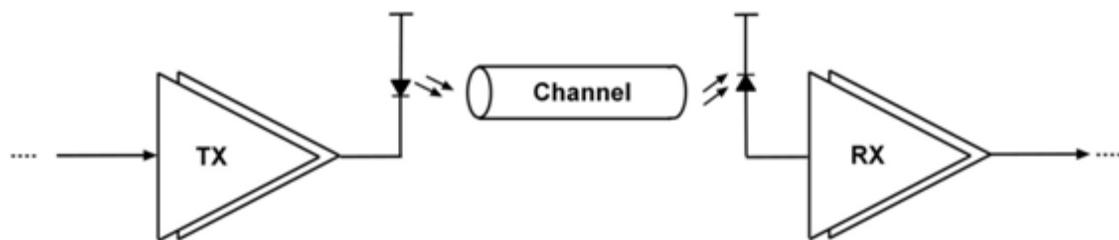

Un sistema de comunicaciones por fibra óptica está compuesto por tres bloques básicos: transmisor, fibra óptica y el receptor. En la Fig. 3 podemos observar el diagrama de bloques del sistema de comunicación óptica.

Fig. 3 Diagrama de bloques de un sistema de comunicación por fibra óptica

El emisor se encarga de procesar la información y convertir la señal de naturaleza eléctrica en una señal óptica. Esta señal óptica viaja a través de la fibra en forma de pulsos de luz hasta llegar al receptor. El receptor convierte la señal óptica recibida en una señal eléctrica nuevamente para su posterior procesado.

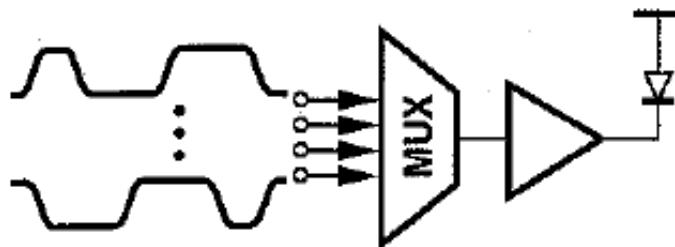

El diagrama de bloques conceptual del transmisor o emisor se describe en la Fig. 4 donde podemos encontrar el serializador, cuya función es combinar y preparar las líneas de datos de baja velocidad paralelas en una señal serie de alta velocidad, y el diodo láser, encargado de convertir las señales eléctricas en ópticas.

Fig. 4 Diagrama de bloques del transmisor [RAZ03]

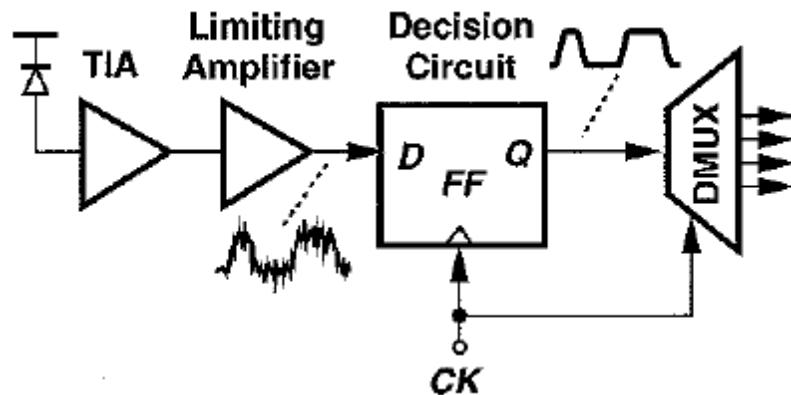

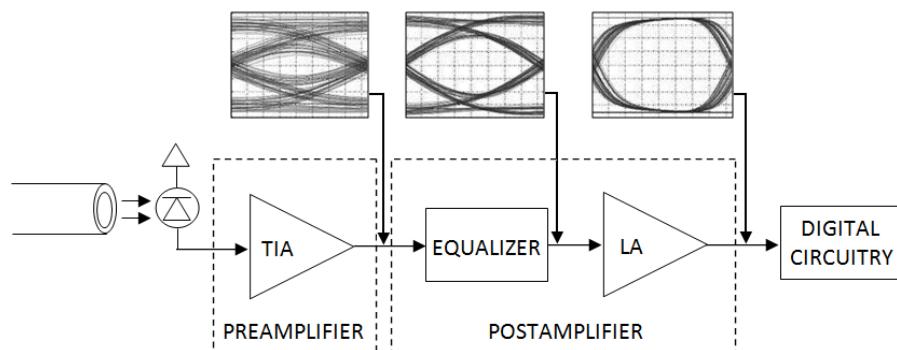

En el receptor, Fig. 5, nos encontramos en primer lugar el fotodetector o fotodiodo (PD), que es el encargado de transformar la señal luminosa en corriente eléctrica. El amplificador de transimpedancia (TIA) es la etapa encargada de convertir la corriente generada en el fotodiodo en voltaje, y por último, una etapa postamplificadora encargada de proporcionar valores digitales compatibles con la circuitería digital para el posterior acondicionado de la señal.

Fig. 5 Diagrama de bloques del receptor [RAZ03]

Como veremos más adelante, las limitaciones impuestas tanto por la fibra óptica como por el fotodiodo hacen necesario la presencia un ecualizador que compense las deficiencias en la transmisión y proporcione un ancho de banda adecuado a las velocidades requeridas con unos valores de ISI y BER determinados. Este será el objetivo principal de este trabajo.

## 2.2. Limitaciones de las fibras

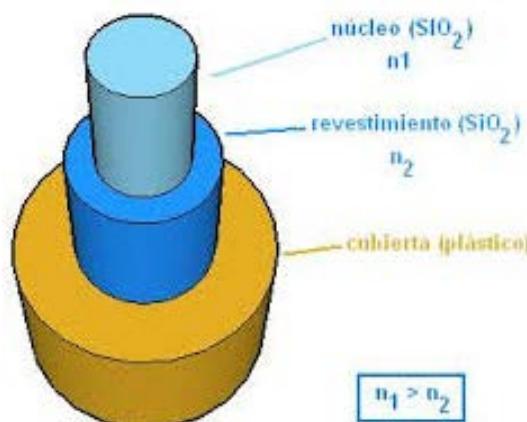

El canal por el que la señal óptica se propaga es fibra óptica. Existen dos grandes grupos de fibras: las fibras de plástico (POF) y las fibras de vidrio (GOF). Ambas poseen la misma estructura que está constituida por: un núcleo, una cubierta y un revestimiento [ZIE08].

El núcleo (o *core*) es la parte central de la fibra y por donde la luz que se quiere transmitir queda confinada debido a que su índice de refracción es mayor que el del material de la cubierta (o *cladding*), produciéndose un efecto de reflexión total interna y propagándose de esta manera la luz a través del medio. Por último, una tercera capa de recubrimiento (*jacket*) protege el núcleo y la cubierta. Las POFs tienen un *core* de diámetro de hasta 1 mm, frente a las 10  $\mu\text{m}$  que puede tener el núcleo de las GOFs.

Fig. 6 Imagen de la estructura de una fibra.

Las fibras ópticas se diferencian entre fibras monomodo (SMF) y fibras multimodo. El número de modos ( $V$ ) que puede propagarse en una fibra depende de su diámetro ( $\phi$ ) comparado con la longitud de onda de la luz ( $\lambda$ ) y la apertura numérica ( $A_N$ ), parámetro que determina el ángulo máximo de luz incidente:

$$V = \frac{2\pi\phi}{\lambda} A_N \quad (1)$$

Si  $V$  es menor que 2.405 solo se puede propagar un modo. En caso contrario se trata de una fibra multimodo.

Las fibras de plástico (POF) son generalmente fibras multimodo con grandes diámetros de núcleo y altas aperturas numéricas para facilitar el acoplamiento de la luz a la entrada y la salida. Esta es una de las ventajas más importantes de las POF, puesto que la tecnología de conexión que puede usarse es más económica que la usada para las fibras de vidrio.

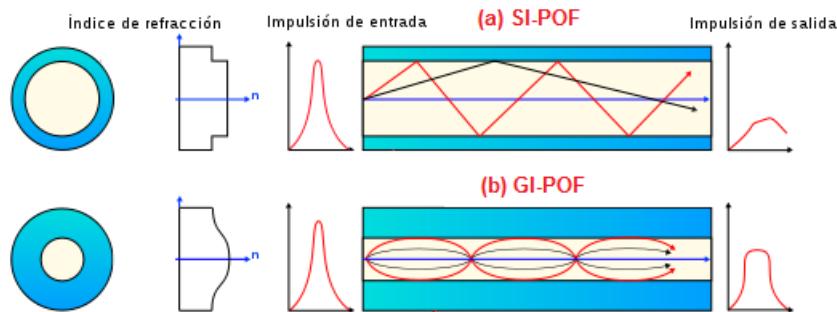

Otro aspecto diferenciador en las fibras ópticas es el perfil del índice de refracción de su núcleo, pudiendo ser de dos tipos: aquellos que presentan una estructura de salto de índice (SI) y los de perfil gradual (GI) [ZIE08].

Los principales problemas de la transmisión de fibra óptica son la dispersión y la atenuación que limitan el ancho de banda del sistema (BW) y la velocidad de transmisión de la POF.

La atenuación de la señal obliga a que la potencia de transmisión óptica sea elevada sobre todo cuando el canal va aumentando su longitud. La atenuación intrínseca de una POF es de aproximadamente 200 dB/Km, y este valor limita el uso de la POF a aplicaciones de corta distancia (pérdidas extrínsecas son aquellas debidas a malas conexiones o curvaturas de la fibra).

La dispersión es el fenómeno por el cual un pulso se ensancha a medida que se propaga a través de la fibra. Esto se debe a que los distintos modos de la luz viajan a distintas velocidades y llegan al receptor en diferentes instantes de tiempo. Los principales tipos de dispersión son: modal, cromática y de polarización [SAC05].

En la Fig. 7 se puede observar cómo se transforma un pulso de entrada al canal de transmisión por los efectos de atenuación y dispersión del medio óptico.

Fig. 7 Efectos de la transmisión en fibra óptica, atenuación y dispersión [GAR08].

El perfil de índice de refracción de una fibra determina la velocidad y el tiempo de retraso de todos los modos guiados. En general, las fibras GI (*graded index*) reducen el retraso modal. Sin embargo, producir estas fibras cuesta mucho, por lo tanto se utilizan fibras SI (*multistep index*), Fig. 8.

Fig. 8 Comparativa entre una SI-POF y una GI-POF [ARA10].

Estos efectos tienen que ser modelados cuando se describe la transmisión de la señal. Mientras que la distorsión en las fibras monomodo está causada principalmente por la dispersión cromática, la descripción de la dispersión en las fibras multimodo es considerablemente más compleja. No solo afecta la dispersión cromática, sino también la dispersión debida a que los diferentes modos se propagan a velocidades diferentes (dispersión multimodo). El tiempo de retraso entre los modos está determinado por el perfil de índice de refracción de la fibra y depende exclusivamente de la fibra.

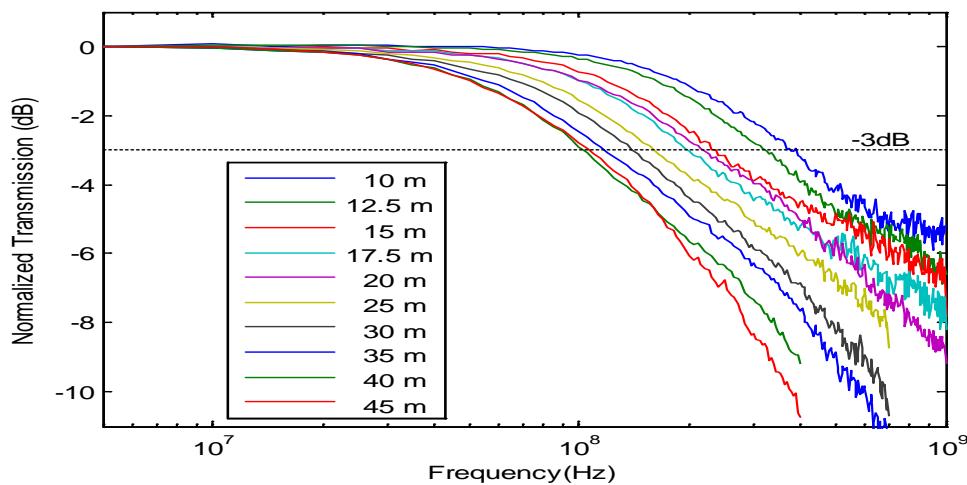

Cómo se reparte la potencia de la señal en los modos individuales, sin embargo, está determinado por el acoplamiento de la luz en la fibra. Analizando el efecto de la dispersión en el dominio de la frecuencia podemos modelar a una POF como un filtro paso-bajo, Fig. 9, siendo necesaria una ecualización que compense dicho comportamiento y permita aumentar su ancho de banda.

Fig. 9 Dependencia del comportamiento frecuencial de una POF (Mitsubishi GH) con su longitud.

La recuperación de la información de la señal de entrada y compensación de la limitación frecuencial en el pulso de salida de la fibra óptica es trabajo del bloque receptor.

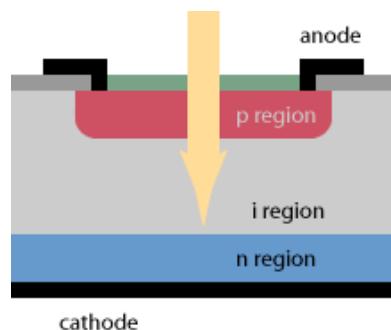

### 2.3. Limitaciones del fotodetector

El fotodetector es el primer elemento que conforma el *front-end* y es el encargado de transformar la señal óptica procedente de la fibra en corriente eléctrica. En comunicaciones de banda ancha mediante POF, el fotodetector más utilizado de entre todos los disponibles en el mercado es el fotodiodo PIN. Estos fotodiodos están fabricados con semiconductores de estado sólido, siendo el material más usado el silicio (Si) y consiste en una unión P-N con una capa de material semiconductor intrínseco entre los materiales P y N tal y como muestra la Fig. 10. Las principales ventajas son su reducido coste de fabricación y su relativa buena eficiencia en la longitud de onda de trabajo de la POF ( $\lambda \approx 660$  nm).

Fig. 10 Estructura física de un fotodiodo PIN.

Sus principales características son la *responsivity* (constante de proporcionalidad entre la corriente eléctrica generada y la potencia óptica incidente), el ruido y la capacidad de deplexión de la unión que determina la respuesta frecuencial del dispositivo. Estas magnitudes tienen un gran impacto en el comportamiento global del receptor.

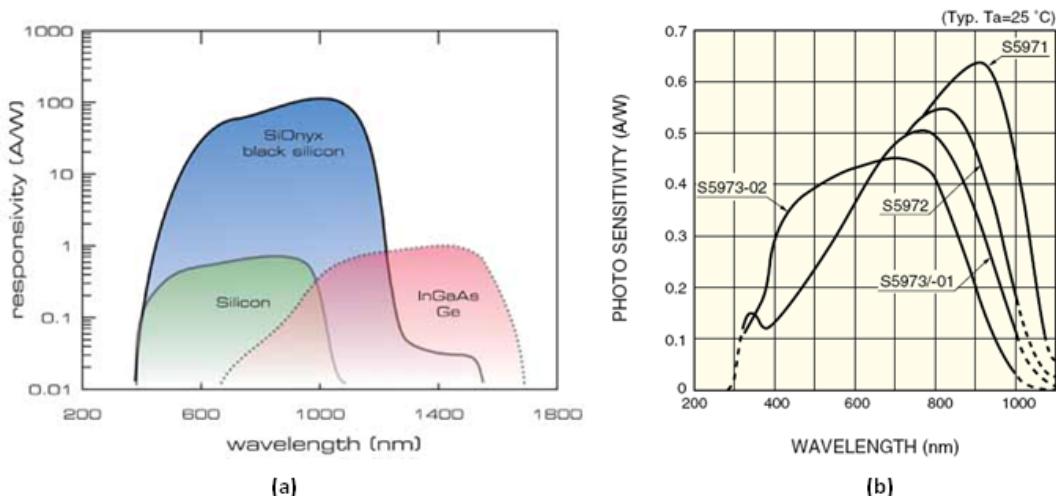

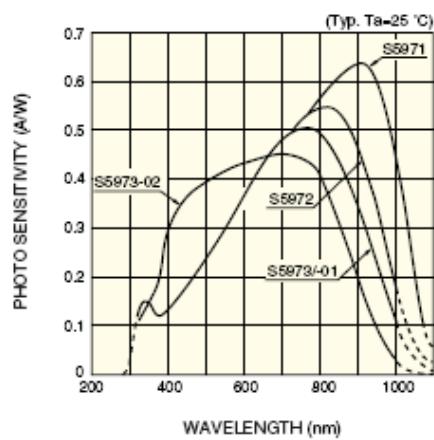

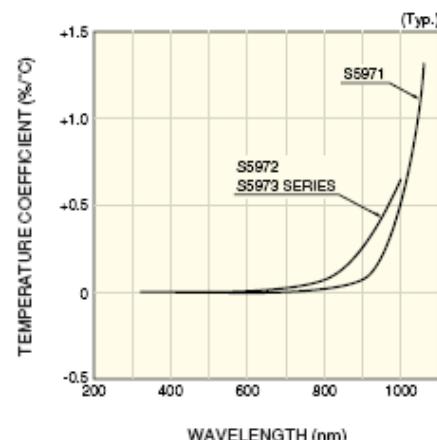

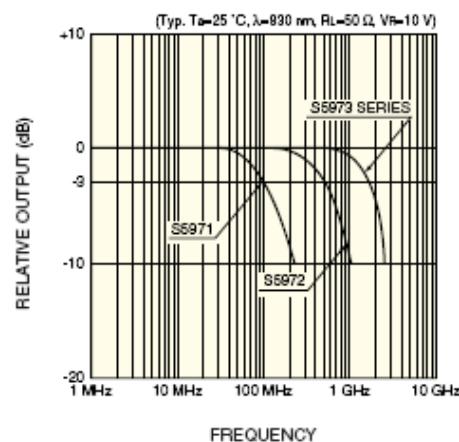

En la Fig. 11 (a), podemos ver una comparativa de la *responsivity* que ofrecen PD de diferentes materiales y el rango de longitudes de onda en los que pueden trabajar y en la Fig. 11 (b) para diferentes PD de una misma familia.

Fig. 11(a) Responsivity frente a longitud de onda de PD de diferentes materiales (b) Responsivity para la familia de PD S597X de Hamamatsu.

El principal ruido que genera el PD es el denominado ruido *shot*, compuesto por un número elevado de pulsos cortos (correspondientes a un par electrón-hueco creado por un fotón) distribuidos aleatoriamente en el tiempo, y cuyo valor *rms* viene dado por la siguiente expresión:

$$i^2_{n,PIN} = 2qI_{PIN}BW_n \quad (2)$$

Donde  $q$  es la carga eléctrica del electrón,  $I_{PIN}$  es la corriente de señal y  $BW_n$  es el ancho de banda en el que medimos el ruido de corriente [SÄC05].

Como se desprende de la ecuación (2) el ruido depende de la señal y es proporcional a su raíz cuadrada, de manera que si el nivel de señal aumenta, la relación señal-ruido (SNR) mejoraría con este aumento.

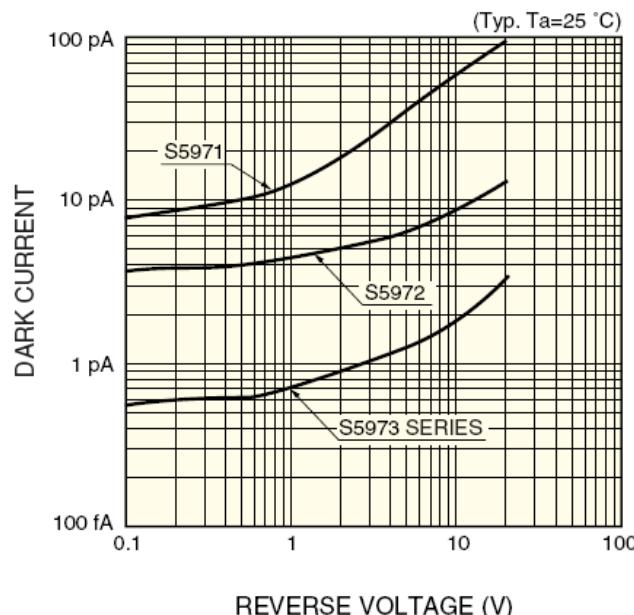

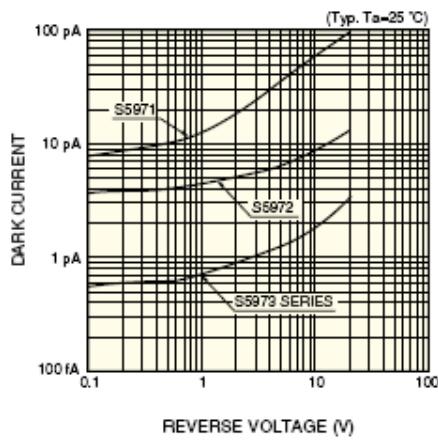

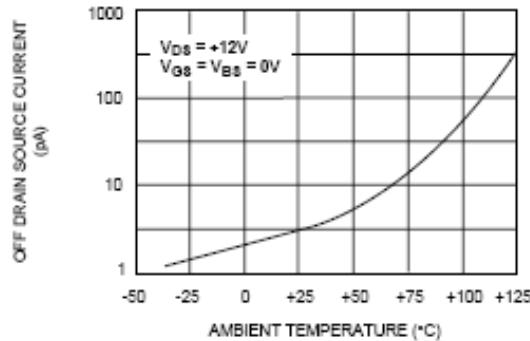

En condiciones de total oscuridad, el PD genera una pequeña señal de corriente denominada corriente de oscuridad  $I_{DK}$ , que depende del área de unión, de la temperatura y de la tensión inversa. Aunque el impacto de esta corriente en la señal así como el ruido asociado a ella se deben tener en cuenta en los cálculos, sus contribuciones suelen ser despreciadas en la mayoría de los casos.

$$i^2_{n,PIN} = 2q(I_{PIN} + I_{DK})BW_n \quad (3)$$

Normalmente, el valor de  $I_{DK}$  se puede despreciar de la ecuación frente a  $I_{PIN}$  ya que es muy bajo en comparación, normalmente en el orden de los pA. En la Fig. 12 vemos la dependencia de  $I_{DK}$  en la familia de PD S597X de Hamamatsu en función del voltaje inverso  $V_R$  del fotodiodo (necesario para el correcto funcionamiento del PD).

Fig. 12 Corriente de oscuridad de la familia de PD S597X de Hamamatsu en función del voltaje inverso

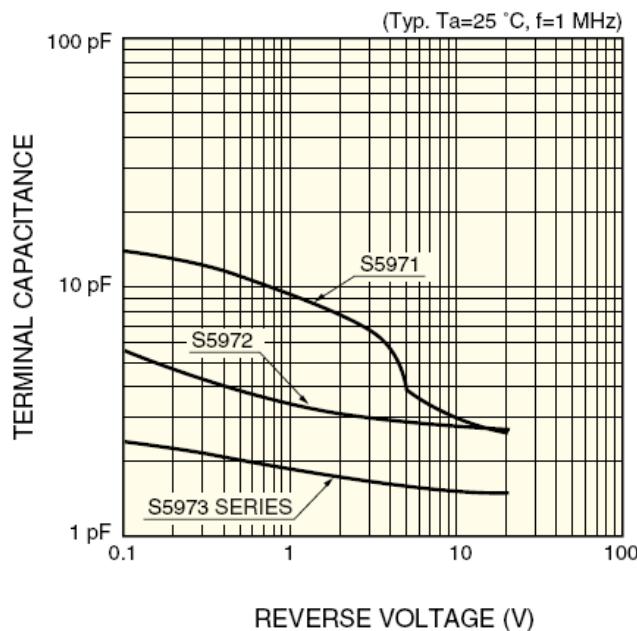

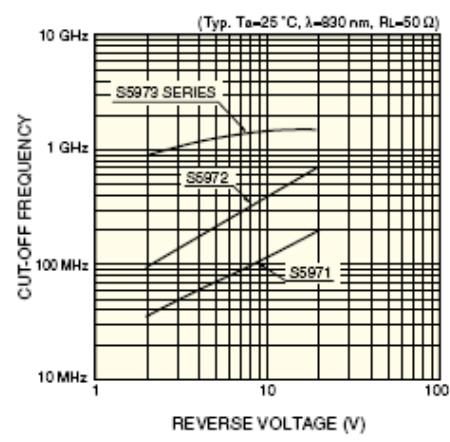

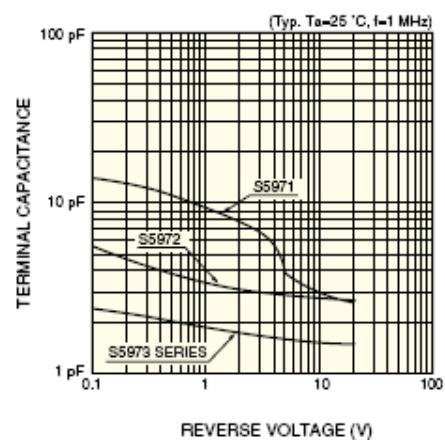

Por último, la respuesta frecuencial del fotodiodo viene limitada por la capacidad parásita asociada con la estructura del PD, la capacidad de deplexión  $C_{PD}$ . Su valor depende del área de unión, del valor de la tensión inversa  $V_R$  que se aplica al PD y de la distancia entre las regiones dopadas. A mayor  $V_R$  menor  $C_{PD}$  (Fig. 13), esta capacidad limita el BW del sistema al introducir una frecuencia de corte dependiente de  $C_{PD}$ .

Fig. 13 Dependencia de la capacidad de unión de la familia de PD S597X de Hamamatsu con  $V_R$ .

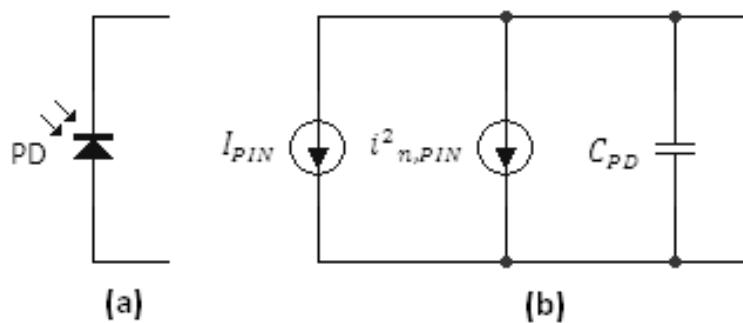

Incluyendo las componentes descritas anteriormente podemos considerar como modelo para caracterizar el fotodiodo polarizado en inversa el que ilustra la Fig. 14.

Fig. 14 Modelo equivalente del PD. (a) Símbolo (b) modelo equivalente.

Las limitaciones frecuenciales impuestas por la POF y el fotodetector hacen imprescindible que deban aplicarse ciertas técnicas de ecualización que permitan mejorar el ancho de banda y alcanzar las velocidades de transmisión adecuadas.

## 2.4. Amplificador de transimpedancia

La luz viajando a través de la fibra sufre pérdidas antes de alcanzar el fotodiodo como ha sido expuesto en puntos anteriores. El fotodiodo transforma la intensidad lumínica en una corriente proporcional, la cual es amplificada y convertida a tensión por un amplificador de transimpedancia (TIA) que constituye la primera etapa del *frontend* del receptor. El diseño de TIAs implica muchos compromisos entre ruido, BW, ganancia y potencia, suponiendo un verdadero reto tanto en tecnologías bipolar como en CMOS.

Veámoslo más detalladamente:

**Transimpedancia.** Es deseable diseñar un bloque que presente una transimpedancia lo más alta posible puesto que esto relaja los requisitos de ruido y la ganancia para el post amplificador.

**Ruido.** La corriente de ruido referida a la entrada es uno de los parámetros más críticos del TIA. A menudo, el ruido del TIA domina todas las demás fuentes de ruido y por lo tanto determina el rendimiento del receptor [SÄC05].

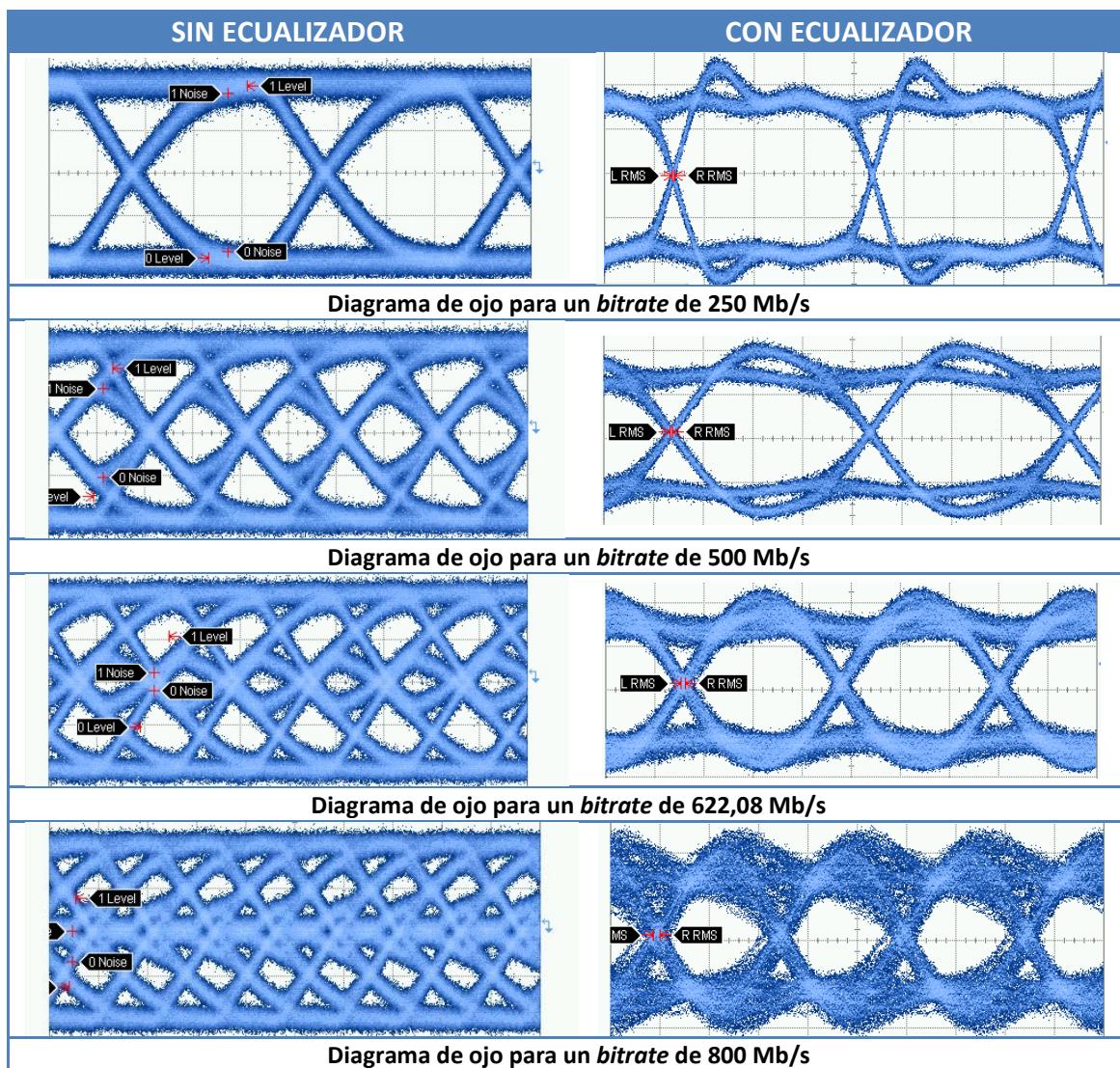

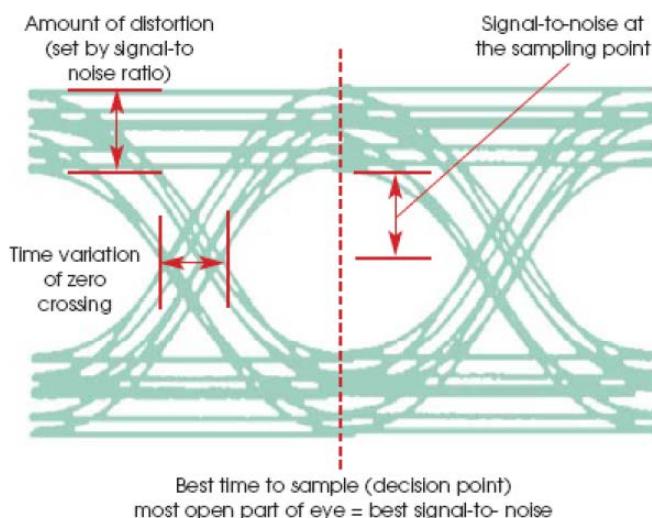

**BW.** Se busca que el BW sea lo más elevado posible, aunque un BW alto aumenta el ruido total integrado. Por otro lado, un BW limitado introduce ISI en las secuencias aleatorias, lo que se puede comprobar experimentalmente mediante diagramas de ojo (ANEXO I: diagramas de ojos), cerrando el ojo tanto verticalmente como horizontalmente.

Las dos implementaciones más comunes para la etapa preamplificadora son ([ING04], [RAZ03] y [SÄC05]):

- a) Modo tensión. La implementación más extendida es el amplificador de transimpedancia tipo *shunt-feedback*. Con esta opción el diseñador pretende obtener un óptimo equilibrio entre todas las magnitudes que determinan las prestaciones.

- b) Modo corriente. La implementación más extendida se basa en un amplificador de corriente como etapa previa seguida de una posterior conversión I-V realizada normalmente por un TIA. Esta opción presenta como principal ventaja el aumento de BW. Sin embargo esto se consigue incrementando el consumo y el ruido.

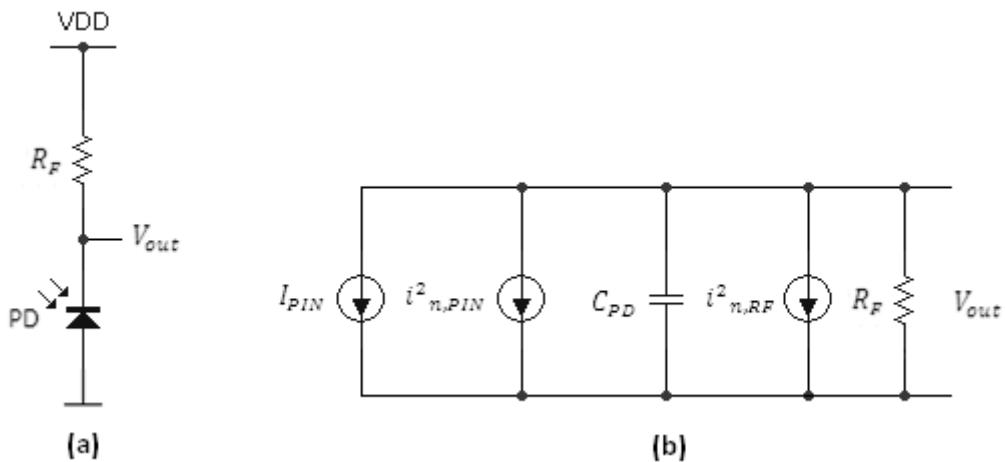

Antes de presentar las principales características de un amplificador de transimpedancia tipo *shunt-feedback* es conveniente analizar la topología más sencilla que realiza la conversión I-V, una resistencia, Fig. 15 (a), para conocer las principales limitaciones y el compromiso existente entre ellas.

Fig. 15 Amplificador de transimpedancia básico implementado con una resistencia (a) estructura (b) modelo equivalente

Considerando el modelo de pequeña señal de la figura Fig. 15 (b) en donde se incluye el ruido térmico generado por la resistencia,  $i^2_{n,RF}$ , se extraen los principales parámetros de este preamplificador:

$$T_R = \frac{V_{out}}{I} = R_F \quad (4)$$

$$BW = \frac{\omega_p}{2\pi} = \frac{1}{2\pi R_F C_{PD}} \quad (5)$$

$$i^2_{n,IN} = i^2_{n,PIN} + i^2_{n,RF} = 2q(I_{PIN} + I_{DK})BW_n + \frac{4kT}{R_F} \quad (6)$$

De las expresiones anteriores se desprende que si conseguimos un elevado ancho de banda (valores de resistencia pequeños) es a costa de perder ganancia y aumentar el ruido, y de forma análoga, para valores de resistencia elevada conseguimos aumentar la transimpedancia y disminuir el ruido pero el ancho de banda se reduce a valores inaceptables.

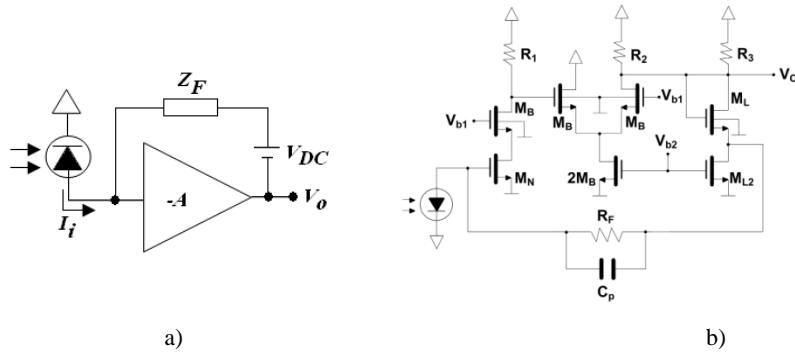

#### **Shunt Feedback TIA**

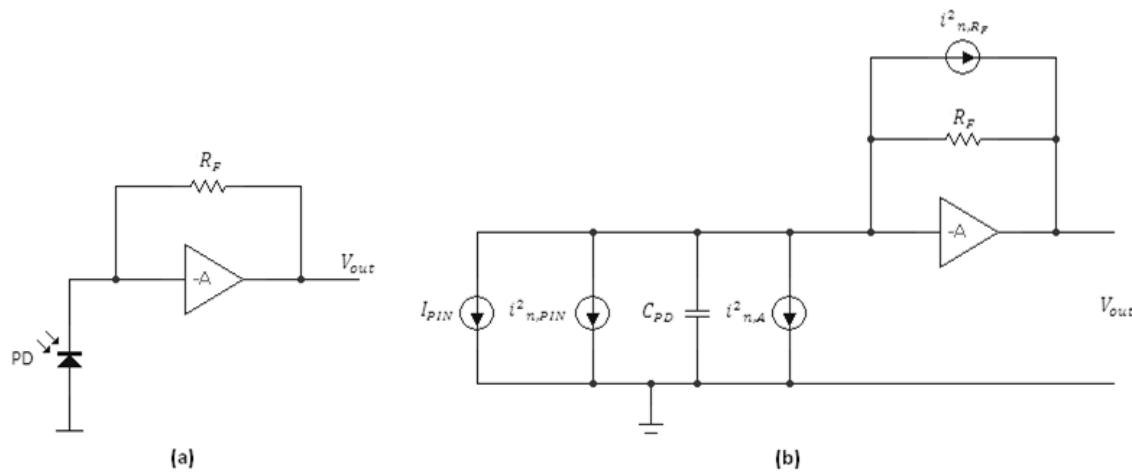

La topología *shunt-feedback* de la implementación en modo tensión es la opción elegida en este trabajo para convertir la intensidad del PD en un voltaje de salida. Se ha elegido esta opción ya que proporciona un buen compromiso entre  $T_R$  y  $BW$  combinados con un bajo nivel de ruido, y además presenta menor consumo que las alternativas en modo corriente.

La estructura está formada por una resistencia conectada en el lazo de realimentación negativa de un amplificador de ganancia A como muestra la Fig. 16 (a).

Fig. 16 (a) Estructura shunt-feedback del TIA (b) modelo equivalente del TIA más PD

Considerando el comportamiento del amplificador ideal con ganancia en lazo abierto A y considerando el modelo equivalente del PD de la Fig. 14, se obtienen las siguientes expresiones:

$$T_R = \frac{V_{out}}{I} = -\frac{AR_F}{A+1} \frac{1}{1 + \frac{R_F C_{PD}}{A+1} s} \quad (7)$$

dónde:

$$R_T = \frac{AR_F}{A+1} \quad (8)$$

$$\omega_P = \frac{A+1}{R_F C_{PD}} \quad (9)$$

Si la ganancia en lazo abierto del amplificador es suficientemente elevada ( $A \gg 1$ ), la transresistencia se aproxima al valor de  $R_F$ ,  $T_R = R_F$  a partir de (8).

La limitación frecuencial dependiente de los valores de  $R_F$  y  $C_{PD}$ , se ve compensada gracias a que la estructura *shunt-feedback* incrementa el valor del BW multiplicándolo por un factor  $(1+A)$ , aumentando así el ancho de banda del sistema.

$$BW = \frac{\omega_P}{2\pi} = \frac{1}{2\pi} \frac{A+1}{R_F C_{PD}} \quad (10)$$

En cuanto al ruido que introduce en el receptor el TIA más el fotodetector queda descrito en la ecuación (11).

$$i^2_{n,IN} = i^2_{n,PIN} + i^2_{n,R_F} + i^2_{n,A} \quad (11)$$

Donde  $i^2_{n,PIN}$  es la contribución de ruido aportada por el PD vista en el anterior apartado, ecuación (3),  $i^2_{n,R_F}$  es el ruido térmico producido por  $R_F$  cuyo valor viene dado por (12) y  $i^2_{n,A}$  es el valor del ruido producido por el amplificador referido a la entrada y que depende de su implementación.

$$i^2_{n,R_F} = \frac{4KT}{R_F} \quad (12)$$

Si queremos obtener una descripción más realista del sistema deberíamos considerar un modelo del amplificador que contemplara una dependencia frecuencial caracterizada por n polos (13).

$$A(s) = A_0 \left( \prod_{i=1}^n \left( \frac{1}{1 + \frac{s}{\omega_{Ai}}} \right) \right), \quad n \geq 2 \quad (13)$$

En este caso la función de transferencia  $T_R$  presentaría  $n+1$  polos. En la literatura encontramos ejemplos con  $n = 1$  [GDP11], con  $n = 2$  [SAN07] y hasta  $n = 3$  [GDP13]. Sin embargo, con un buen diseño de la estructura del amplificador de tensión, se pueden llevar estas contribuciones frecuenciales lo suficientemente lejos de las frecuencias de trabajo como para poder aproximar el TIA a un sistema de primer orden, ecuación (7). Con esta premisa, el diseño de un posible ecualizador será más fácilmente abordable.

### 3. Caracterización experimental del prototipo T2-GDE-2013

En este apartado se va a llevar a cabo la caracterización del prototipo de amplificador de transimpedancia *T2-GDE-2013*. El objetivo es poder conocer con exactitud las prestaciones frecuenciales del conjunto TIA más fotodiodo para la posterior toma de decisiones sobre la necesidad y especificaciones de un ecualizador.

Uno de los puntos previos más importantes será abordar el complejo proceso de colocar ambos componentes *on-chip* en un encapsulado DIP. Esto difiere de lo encontrado en trabajos preliminares [GDP10] y [GDP13], para partir de una situación más favorable en términos de elementos parásitos y pérdidas no deseadas.

#### 3.1. Descripción del TIA T2-GDE-2013

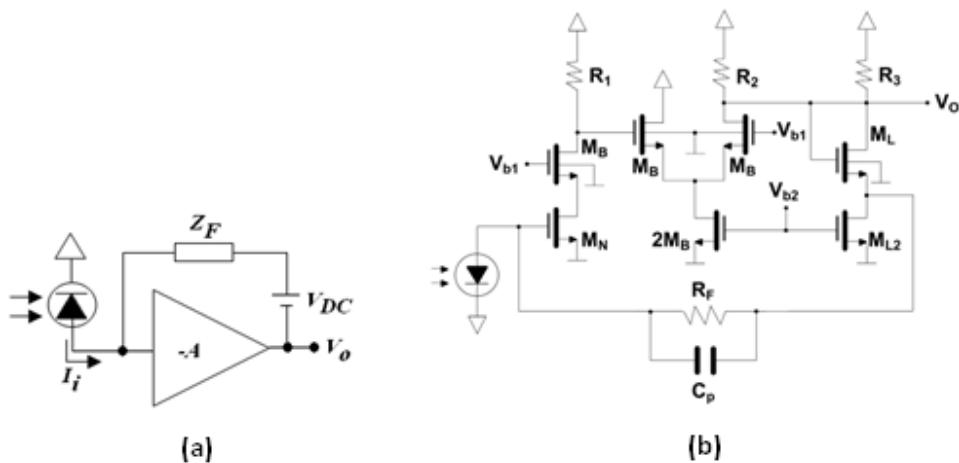

Las posibles topologías empleadas para implementar el amplificador de transimpedancia descrito en el punto 2.4 son muchas, desde la más sencilla, formada por una etapa en fuente común (CG) y un seguidor de tensión, hasta estructuras diferenciales que intentan eliminar el efecto de la alimentación y de la contaminación de ruido por sustrato [RAZ03].

En el caso que nos ocupa, el prototipo a caracterizar *T2-GDE-2013* presenta la implementación del TIA descrita en la Fig. 17 y consta de dos etapas: 1) etapa de entrada en fuente común con un transistor *cascode* y 2) etapa de salida de acople por fuente formada por una etapa en drenador común (CD) y una en puerta común (CG). El lazo de realimentación está formado por una resistencia  $R_F$  en serie con una fuente de tensión flotante y, un condensador de compensación, [GDP11]. Los valores de los componentes utilizados se encuentran detallados en el ANEXO III: TIA.

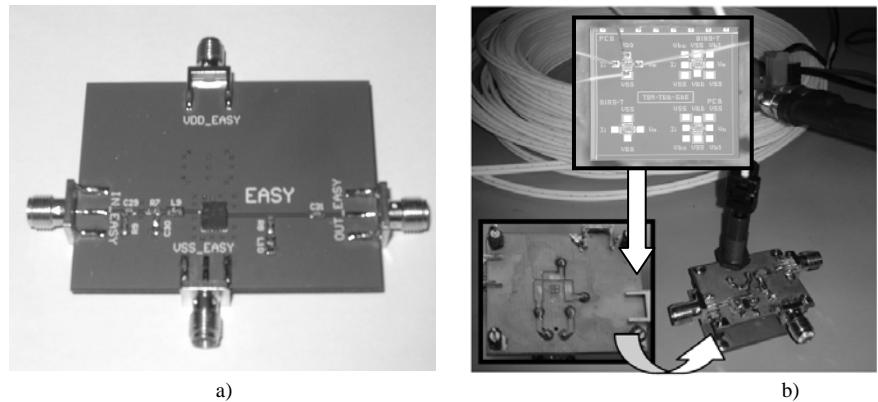

Fig. 17 (a) Esquemático del TIA (b) Implementación prototipo TIA T2-GDE-2013

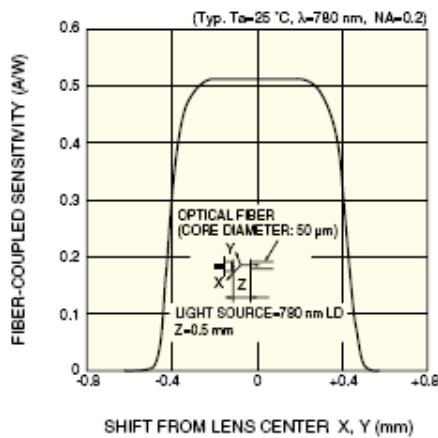

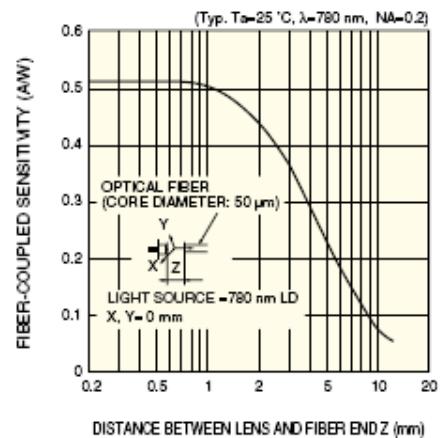

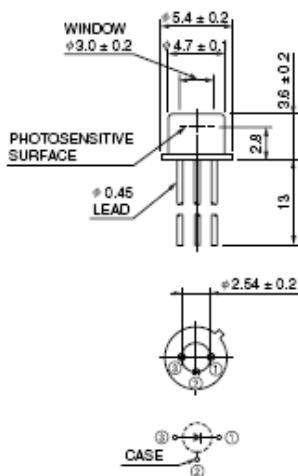

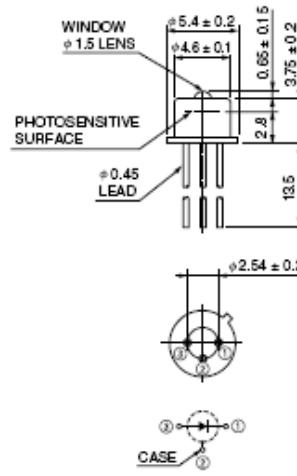

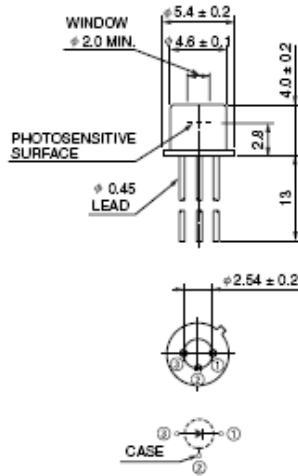

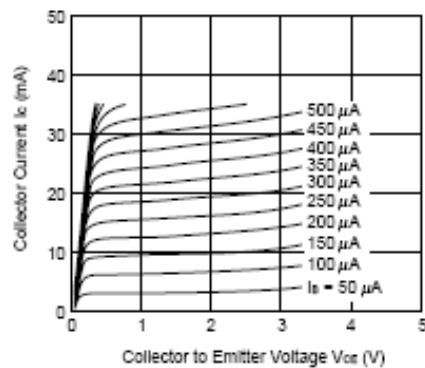

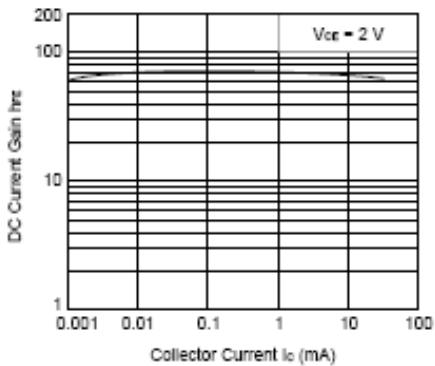

El fotodiodo elegido ha sido el S5973 de Hamamatsu por sus altas prestaciones (ver ANEXO VI: *datasheets*). Las principales características del S5973 son: buena *responsivity* con longitudes de onda entre 500 y 800 nm, un área activa de  $0.5 \text{ mm}^2$  y una capacidad parásita de deplexión de  $1.8 \text{ pF}$  (a 1V de polarización inversa del PD).

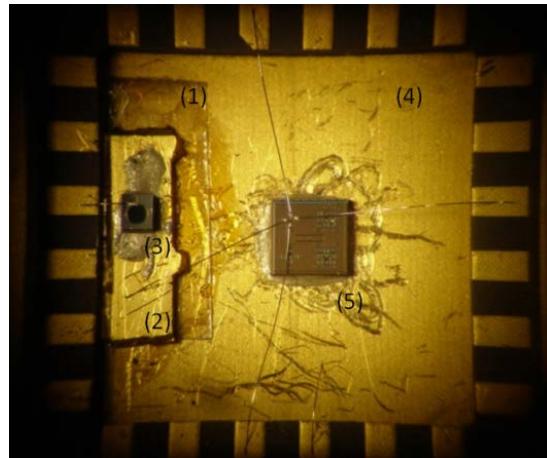

### 3.2. Técnica de ensamblaje del fotodetector

Como se ha indicado en la sección precedente, el primer paso para llevar a cabo la caracterización experimental del prototipo es abordar la disposición *on-chip* del TIA y el fotodiodo en un encapsulado DIP. Este proceso es complejo, laborioso y artesanal, habiendo muy poca información descrita en la literatura.

El fotodiodo es fijado al encapsulado utilizando el siguiente procedimiento:

1. Inicialmente se pega una lámina aislante de mica mediante *g-varnish*, Fig. 18 (1) al sustrato. El *g-varnish* es un adhesivo aislante de conductividad eléctrica nula y que soporta muy bien las altas temperaturas.

2. El segundo paso consiste en pegar una segunda lámina conductora de oro cuya función es realizar el contacto con el cátodo del PD, Fig. 18 (2), de la misma manera que hemos hecho con la película de mica.

3. Y finalmente, el fotodiodo se fija a la lámina de oro mediante *epoxy* de plata, Fig. 18 (3). El *epoxy* de plata es un adhesivo conductor eléctrico.

Los procesos llevados a cabo con *g-varnish* se hacen a temperatura ambiente. Sin embargo, aquellos realizados con *epoxy* de plata deben realizarse a una temperatura de 60°C y durante periodos de 7 horas. Este proceso se ha realizado en los laboratorios del CSIC bajo la supervisión del Dr. Agustín Camón.

El prototipo de TIA se fija mediante *epoxy* de plata repitiendo el proceso descrito con el fotodiodo.

El *bonding* entre los diferentes dispositivos se realiza en una máquina de puntas modelo HYBOND 572A y que opera bajo el principio de ultrasonidos. Este aparato presenta las prestaciones requeridas por nuestro sistema ya que permite hacer *bondings* en superficies mínimas de 25 µm x 25 µm.

El material del hilo utilizado es aluminio de alta pureza con diámetro de 25 µm y que permite una adhesión óptima a las diferentes superficies del conjunto. Nótese que el material de los PAD del PD, del TIA y del encapsulado DIP son totalmente diferentes entre sí, y por lo tanto se tuvieron que realizar numerosas pruebas para ver cuál de los materiales del laboratorio se ajustaba mejor a nuestras necesidades.

Fig. 18 Prototipo T2-GDE-2013, fotodiodo y TIA.

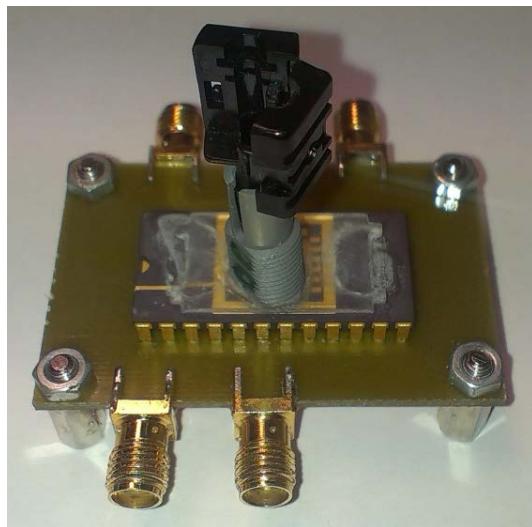

Finalmente, para las pruebas de laboratorio, se realizó una PCB con los diferentes conectores (SMA) de alimentación, tierra y salida (con *matching* a  $50\ \Omega$ ) así como una guía para la colocación de la fibra óptica, Fig. 19.

Fig. 19 PCB del prototipo T2-GDE-2013.

### 3.3. Comportamiento y caracterización experimental del sistema TIA+PD

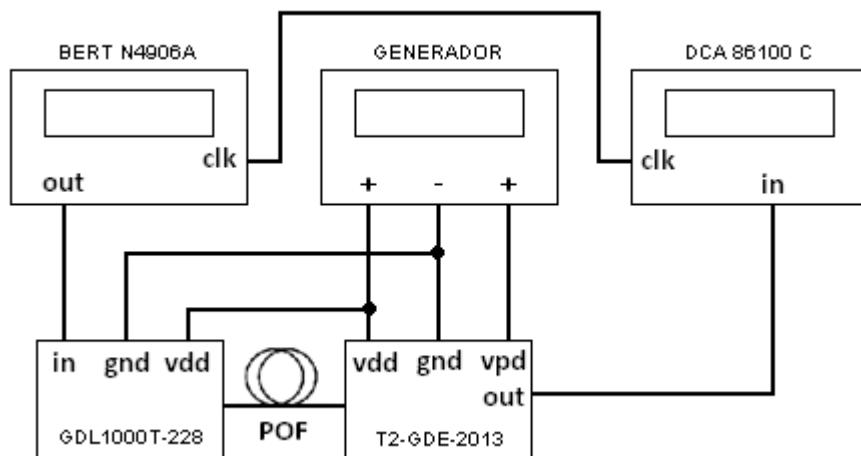

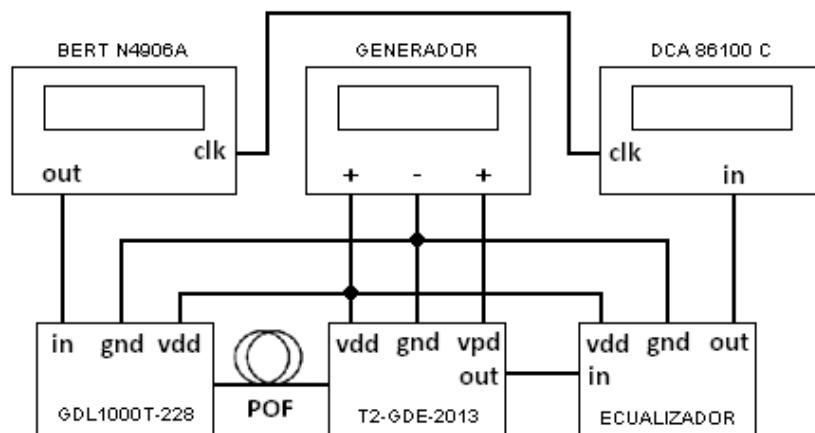

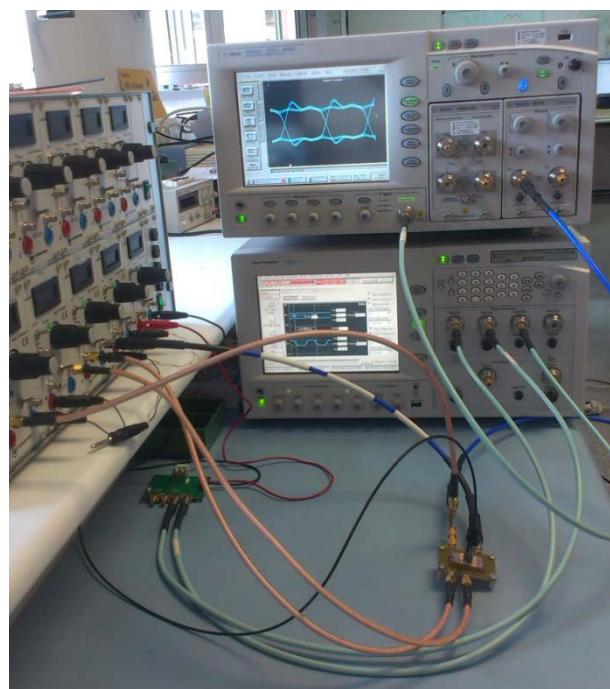

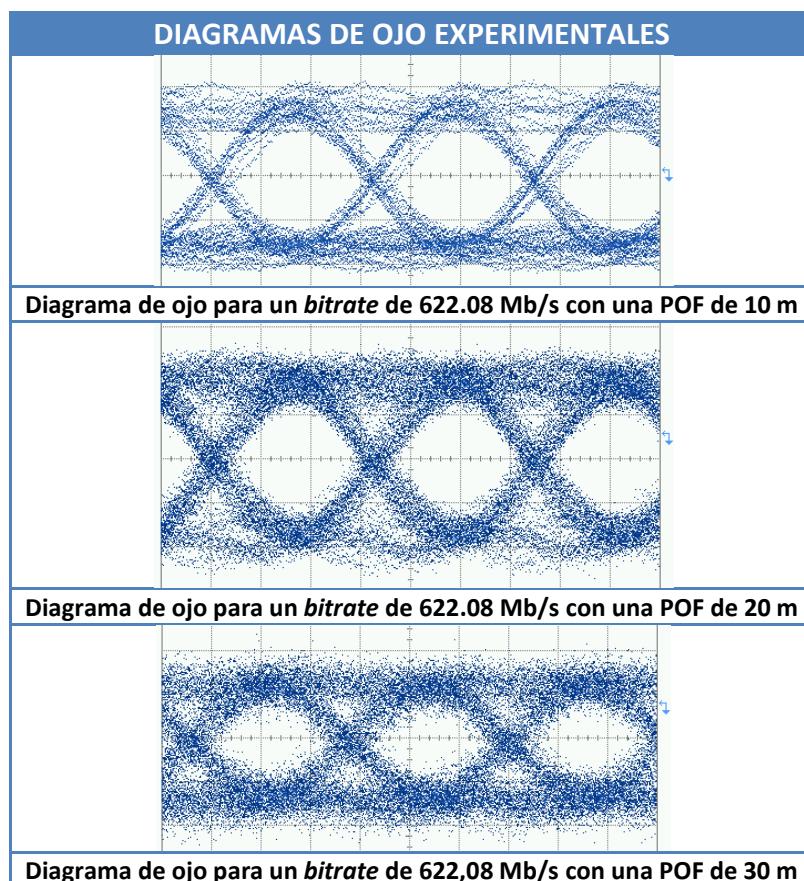

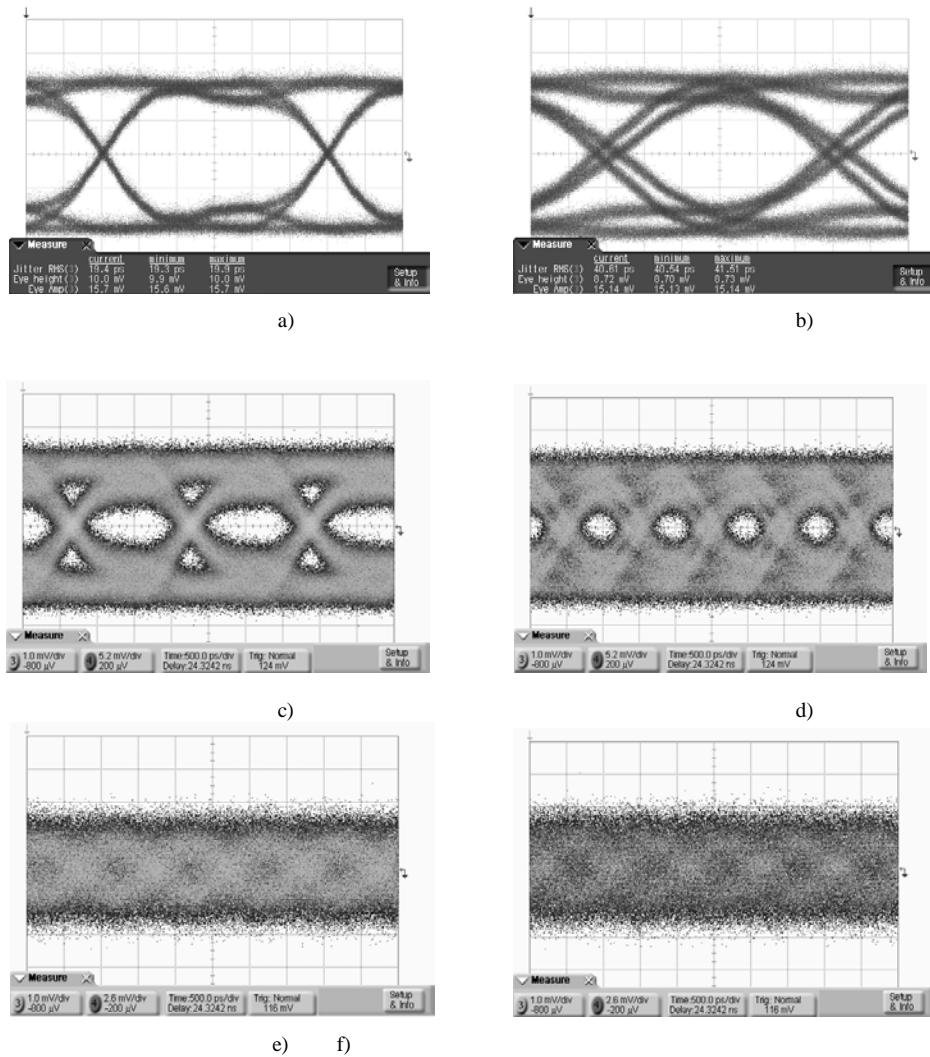

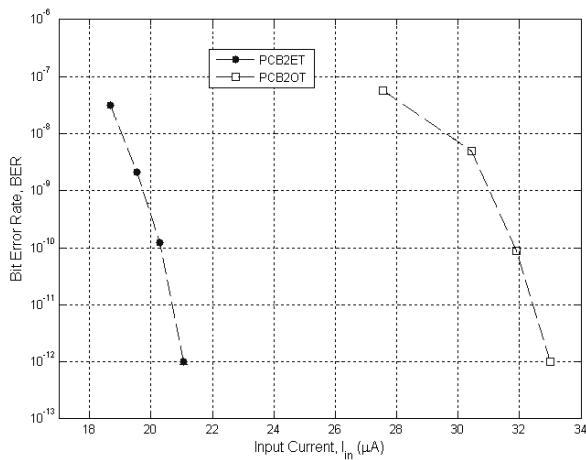

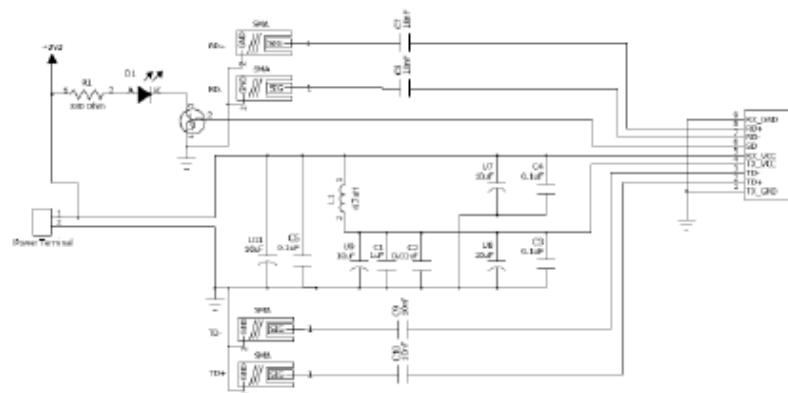

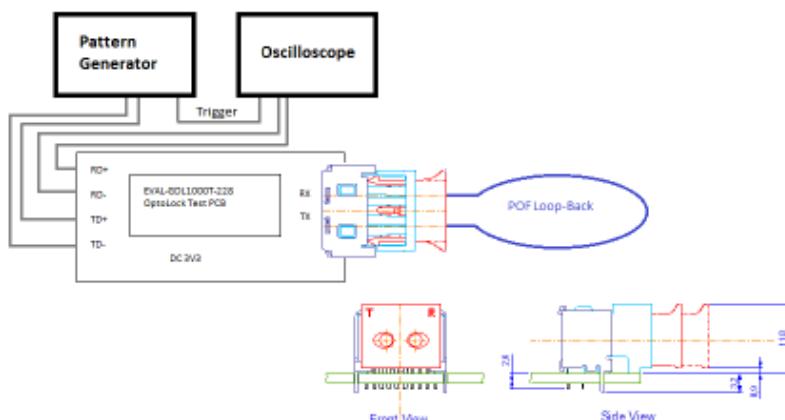

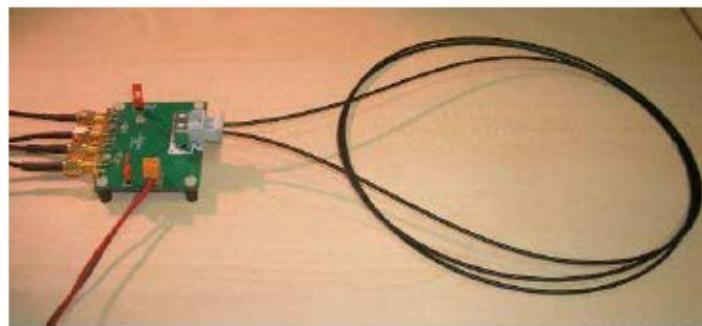

Para la caracterización experimental del prototipo se ha utilizado un *transceiver* comercial, el GDL1000T-228 de *Firecomms* (ver ANEXO VI: *datasheets*) y una fibra POF de longitud mínima. El patrón pseudoaleatorio de entrada ha sido generado por un *tester* de tasa de error de 3,6 Gb/s, N4906A BERT de *Agilent*. El análisis de la señal de salida del prototipo se ha realizado con un analizador de comunicaciones digitales, el DCA 86100 C de *Agilent*.

El diagrama conceptual del *setup* de medida para la caracterización del prototipo TIA+PD con el equipo descrito anteriormente se muestra en la Fig. 20, y en la Fig. 21 se muestra el *setup* montado en el laboratorio.

Fig. 20 *Setup* de medida conceptual del prototipo T2-GDE-2013

Fig. 21 *Setup* de medida en el laboratorio del prototipo T2-GDE-2013

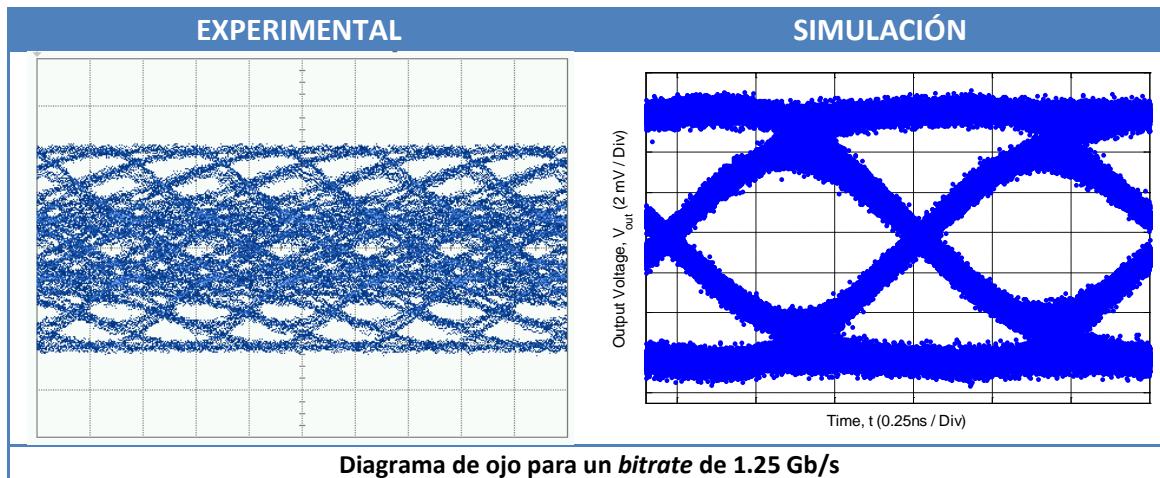

Los equipos utilizados para el test óptico del prototipo no permiten obtener el comportamiento frecuencial de forma directa a como se obtendría mediante el uso de un analizador de redes, pero sí de manera indirecta mediante la comparativa simulación/experimental de los diagramas de ojo. Esto se basa en el hecho de que hay una correlación directa entre la respuesta en frecuencia de un dispositivo y su diagrama de ojo, es decir, si los diagramas de ojos experimentales y de simulación coinciden, las respuestas frecuenciales en ambos casos también coincidirán.

Por ello, a continuación en la Tabla 2, se presentan los resultados de simulación del prototipo y los resultados experimentales obtenidos después de la caracterización, incluyendo el sistema de *test* para un *bitrate* de 1.25 Gb/s.

**Tabla 2 Comparación de diagrama de ojo esperado por simulación y experimental.**

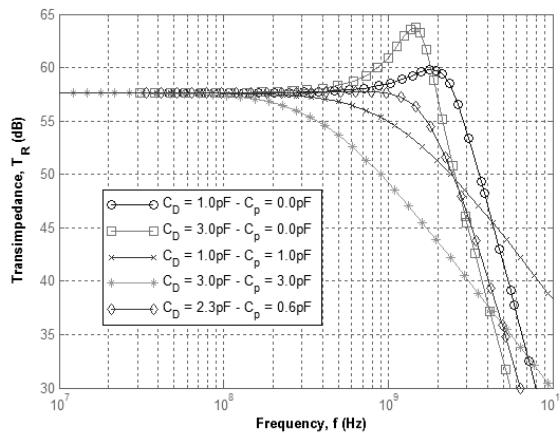

De los diagramas de ojos presentados en la tabla anterior se desprende que existe una diferencia clara entre los resultados experimentales y el comportamiento simulado del sistema. Si tenemos en cuenta el estudio previo realizado en el punto 2.4 atribuiremos esta diferencia al valor del parámetro  $C_{PD}$ .

Para estimar el valor de  $C_{PD}$  utilizado en la simulación, se tuvo en cuenta la capacidad de deplexión del PD, la capacidad parásita del proceso de fijación del PD al encapsulado y la capacidad parásita del *bonding*. La suma de estas capacidades daba un valor de 6,3 pF.

Los resultados experimentales nos dicen que esta capacidad estimada no se corresponde con la real. Para hallar una aproximación mejor del valor de  $C_{PD}$  y por tanto un valor del BW más ajustado al comportamiento real del prototipo, deberemos realizar de nuevo el estudio del comportamiento del sistema mediante la simulación de este modelo, de manera que llevaremos a cabo una comparativa experimental/simulación de los diagramas de ojo hasta que presenten comportamientos similares y poder obtener así valores más realistas de las capacidades presentes.

Con los valores obtenidos en la fabricación del TIA (ANEXO III: TIA) los de las hojas de características del PD S5973 (ANEXO VI: *datasheets*) y recogiendo otras capacidades existentes ( $C_{in}$  de entrada del TIA, capacidad de los conectores SMA, proceso de ensamblaje, etc) en un valor  $C_T$ , la ecuación (14) queda de la siguiente manera:

$$Z_T = \frac{V_{out}}{I_{PIN}} = \frac{602.2}{1 + 47.79C_T s} \quad (14)$$

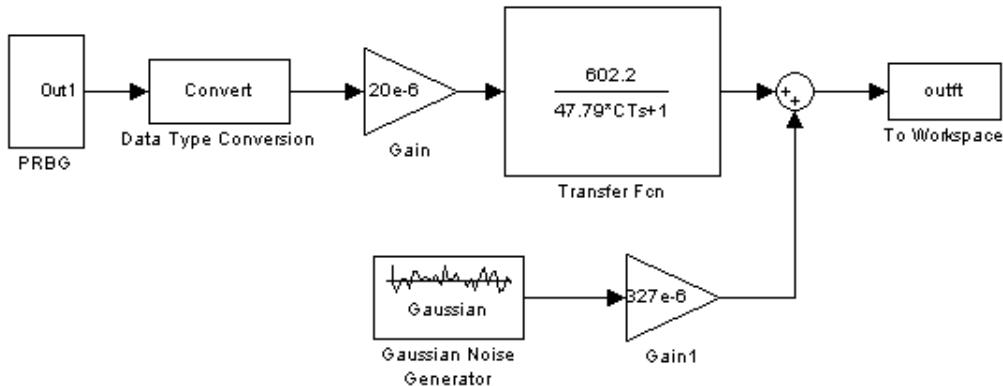

En la Fig. 22 se presenta el esquema de simulación en *Matlab/Simulink* donde se ha introducido el modelo descrito anteriormente y se ha adaptado la señal de entrada para reproducir las condiciones de la caracterización experimental.

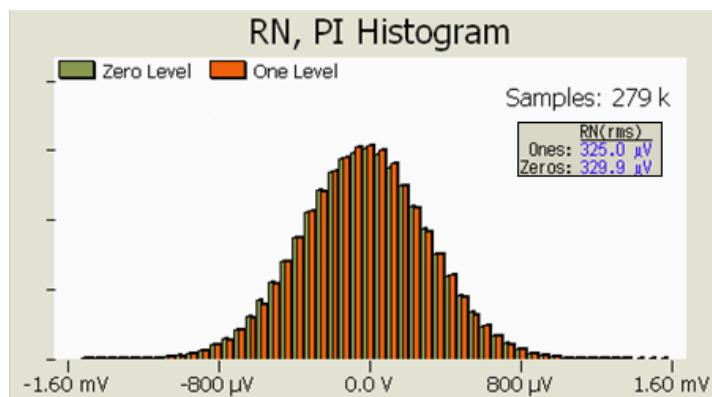

Dicho modelo incluye una señal de ruido equivalente a las medidas obtenidas con el DCA. Notar que la contribución del ruido total *rms* es de  $329.9 \mu V_{rms}$  y  $325 \mu V_{rms}$  cuando los estados son 0 y 1 respectivamente, Fig. 23:

Fig. 22 Esquema de simulación en *Matlab/Simulink* del prototipo T2-GDE-2013.

Fig. 23 Distribución del ruido en la salida del prototipo en función de los niveles lógicos

Para la visualización de los diagramas de ojo del modelo, se ha programado una función en *Matlab* disponible en el ANEXO II: *MATLAB*.

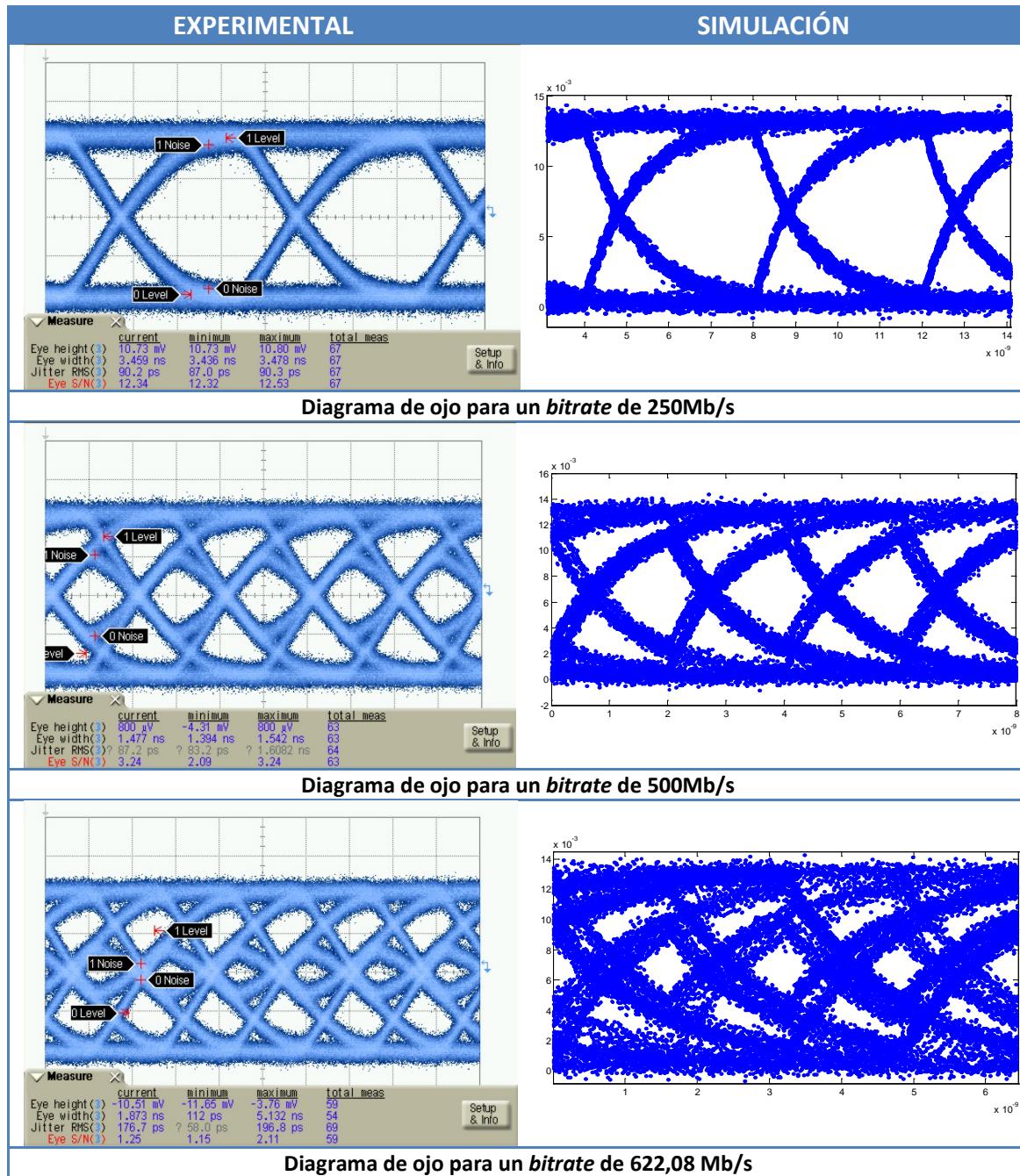

En la siguiente tabla, Tabla 3, se presenta la comparativa de los diagramas de ojo obtenidos con el *setup* de medida y los obtenidos mediante la simulación del modelo teórico descrito anteriormente a diferentes tasas de *bits*. Todos los resultados experimentales han sido obtenidos con la misma potencia óptica del láser, una secuencia PRBS de  $2^{31}-1$ , y una polarización en inversa del fotodiodo de 1,8 V.

Tabla 3. Comparativa de diagramas de ojo experimentales y simulación.

De la comparación de los diagramas de ojo, se puede verificar que el comportamiento del prototipo se puede describir mediante el modelo de primer orden propuesto debido a la concordancia entre los diagramas de ojo experimentales y de simulación, y esta concordancia entre los resultados de simulación y experimentales se alcanza cuando el valor de la capacidad total equivalente de la ecuación (10) es:

$$C_T = 22.2 \text{ pF}$$

Como resultado final, obtenemos que la limitación frecuencial debida al BW de este modelo, calculada mediante la ecuación (10), y equivalente al experimental, es:

$$BW \approx 150MHz.$$

Este elevado valor de  $C_T$ , que establece la limitación frecuencial, es la suma de varias contribuciones de capacidades parásitas difíciles de medir, como son: la capacidad creada por la mica en el proceso de fijación, la de entrada del TIA, la de los conectores SMA, la de las pistas de la PCB y la parásita del encapsulado DIP.

Esta información es de gran importancia a la hora de poder reducir la limitación frecuencial en futuros diseños minimizando las diferentes contribuciones de las capacidades parásitas.

Finalmente, debido a este bajo valor de BW, que impide que se alcancen las prestaciones deseadas de trabajo a altas frecuencias, se concluye que es necesaria una etapa ecualizadora capaz de subsanar las limitaciones frecuenciales del sistema.

## 4. Diseño del ecualizador en tiempo continuo

### 4.1. Técnicas de ecualización

Como se ha mostrado en capítulos anteriores las características no ideales del canal a menudo deterioran la calidad de la señal recibida y pueden causar errores en la recuperación de los datos. Esto se debe a que, en la práctica, el canal de comunicación se comporta como un filtro pasa-baja. Como consecuencia, las diferentes componentes frecuenciales de la señal transmitida sufrirán distinta atenuación (atenuación dependiente de la frecuencia) y experimentarán distinta distorsión de fase (distorsión dependiente de la frecuencia) cuando se propagan a través del canal. Además, el canal de transmisión también puede introducir ruido en la señal. La limitación de la anchura de banda del canal contribuye de manera decisiva al deterioro de la señal original, produciendo lo que se conoce como interferencia inter-símbolo (ISI).

Los anchos de banda de la mayoría de los canales de comunicación están por debajo de los GHz y está relacionado con la velocidad de transmisión. Para mantener una velocidad de comunicación elevada, la ecualización es necesaria con el fin de eliminar o reducir el ISI. Un ecualizador proporciona una respuesta frecuencial ‘inversa’ a la del canal, de tal forma que la respuesta frecuencia total es plana en el rango frecuencial de interés.

Atendiendo a la localización del ecualizador, podemos distinguir dos tipos de ecualización: ecualización del transmisor o pre-énfasis y ecualización del receptor. Ambas buscan enfatizar las componentes de alta frecuencia y/o reducir las componentes de baja frecuencia de la señal transmitida o recibida para compensar el efecto de que las componentes de alta frecuencia se ven más atenuadas que las componentes de baja frecuencia en su recorrido a través del canal.

En el transmisor:

El pre-énfasis se realiza en el transmisor. En algunos casos, aumenta las componentes de alta frecuencia, lo que puede ocasionar problemas de ruido. En otros casos, reduce la potencia de las componentes de baja frecuencia, lo que se conoce como de-énfasis. Quizás en términos de consumo de potencia y efectividad, la técnica más conveniente sea el de-énfasis. Sin embargo el uso de de-énfasis disminuye la potencia total transmitida, disminuyendo como resultado la relación señal-ruido (SNR) en el receptor.

La implementación de un ecualizador en el trasmisor es relativamente más fácil que en el receptor, sin embargo, puesto que el pre-énfasis se realiza en el transmisor, no tenemos en cuenta las características variables del canal.

No obstante, en algunas aplicaciones suele optarse por cierta ecualización en el transmisor para mejorar algo la calidad de la señal recibida, aunque luego sea necesaria una ecualización definitiva en el receptor.

En el receptor:

Dentro de esta técnica de implementación existen tres grandes grupos:

- Ecualizadores pasivos. Como ventaja presenta un consumo muy bajo, por el contrario, los bajos niveles de señal no hacen de los filtros pasivos una solución práctica. [MAX03]

- Ecualizadores en tiempo continuo. Presenta un buen compromiso entre consumo, coste y adaptabilidad.

- Ecualizadores digitales con Filtros FIR. Incumplen la condición de bajo coste y consumo. Realizan la ecualización adaptativa de forma eficiente pero aumenta la complejidad.

Por tanto, se llega a la conclusión de que la mejor solución para este trabajo es la técnica de ecualización en tiempo continuo en el receptor (EQ-CT), debido a su simplicidad que asegura un bajo consumo y coste. Dentro de la bibliografía, se presentan diferentes estructuras de ecualización en tiempo continuo [LU01], [RAD05], [OSH98] y [GIM13a].

A la hora de realizar el estudio teórico del comportamiento deseado del ecualizador para este trabajo, hay que tener en cuenta que debe ser capaz de corregir las limitaciones frecuenciales que sufre el sistema debidas a la fibra óptica y el conjunto PD más preamplificador (TIA).

Estas limitaciones frecuenciales se pueden modelar, de forma simplificada, como una función de transferencia con dos polos, ecuación (15), [GDP13].

$$H(s) = \frac{A}{\left(1 + \frac{s}{\omega_{POF}}\right)\left(1 + \frac{s}{\omega_{TIA}}\right)} \quad (15)$$

Por ello, nuestro ecualizador debe presentar un comportamiento frecuencial que compense a  $H(s)$ , es decir que presente dos ceros, donde  $A_{EQ}$  es la ganancia del ecualizador, ecuación (16). Haciendo esto, la respuesta total del sistema podrá modelarse mediante:

$$H_{EQ}(s) = A_{EQ} \left(1 + \frac{s}{\omega_1}\right) \left(1 + \frac{s}{\omega_2}\right) \quad (16)$$

$$H_{SISTEMA}(s) = H \cdot H_{EQ} = A A_{EQ} \frac{\left(1 + \frac{s}{\omega_1}\right) \left(1 + \frac{s}{\omega_2}\right)}{\left(1 + \frac{s}{\omega_{POF}}\right) \left(1 + \frac{s}{\omega_{TIA}}\right)} \quad (17)$$

$$H_{SISTEMA}(s) = A A_{EQ}, \text{ para } \omega_1 = \omega_{POF} \text{ y } \omega_2 = \omega_{TIA} \quad (18)$$

El polo introducido por el conjunto PD más TIA ( $\omega_{TIA}$ ) tiene un valor fijo que se ha calculado en la caracterización experimental del prototipo *T2-GDE-2013*, mientras que la limitación frecuencial introducida por la POF ( $\omega_{POF}$ ) será variable por lo que se requiere que el ecualizador sea adaptativo.

La topología elegida para la realización del ecualizador en tiempo continuo es la denominada *shunt peaking*. En la literatura podemos encontrar diferentes implementaciones para esta técnica de ecualización englobadas en dos grandes grupos: *active* y *passive* [ANA04], [RAD05] y [LU01]. En las secciones venideras se analizarán varias de ellas y se verá su eficiencia para el caso que nos ocupa.

### 4.2. Análisis tecnológico

Los elementos más importantes del diseño de un EQ-CT, son los componentes activos, en nuestro caso los transistores. Ya que en este trabajo se va a realizar una arquitectura discreta de ecualizador es importante realizar un estudio previo de las opciones existentes en el mercado a la hora de seleccionar estos componentes.

Para altas frecuencias se suelen utilizar tecnologías híbridas como silicio-germanio (SiGe), arseniuro de galio (GaAs) o fosfuro de indio (InP) que ofrecen transistores con estructuras de heterounión (HFET, HBT). El inconveniente de estos transistores es su difícil modelado teórico y un alto precio que choca con el requisito de bajo coste establecido para este trabajo.

Teniendo en cuenta estas limitaciones, la opción tecnológica más adecuada para el diseño del ecualizador será la tecnología de silicio. Dentro de este marco las posibilidades son dos, utilizar transistores MOSFET o transistores BJT.

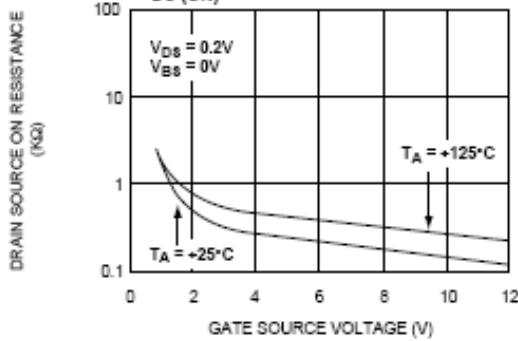

Los transistores MOSFET discretos disponibles en el mercado permiten un fácil modelado y presentan un coste bajo. Sin embargo, suelen estar diseñados para trabajar en aplicaciones de potencia y no tanto para pequeña señal y altas frecuencias, por lo que presentan serias limitaciones para nuestro ecualizador.

Por este motivo se ha decantado por la utilización de transistores BJT de silicio. Desde un punto de vista de diseño con componentes discretos los transistores elegidos siguen manteniendo los requerimientos de bajo coste y fácil modelado y además existe más variedad de transistores capaces de trabajar a frecuencias medias y altas.

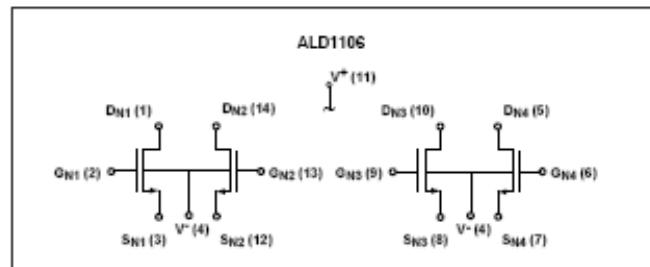

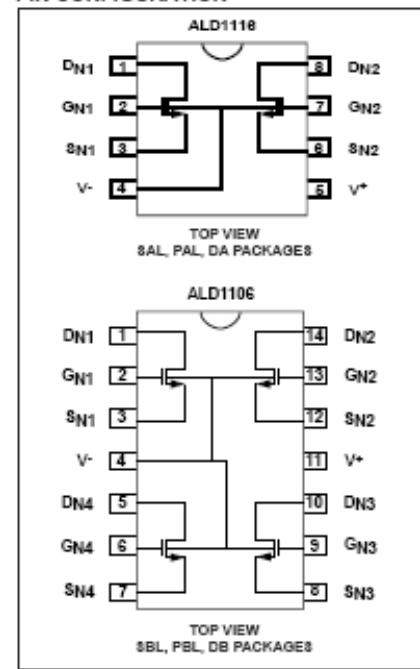

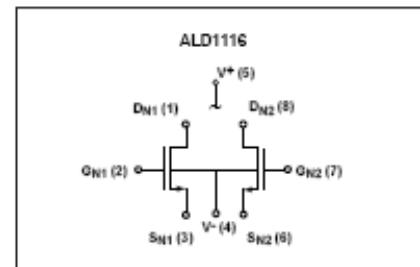

El primer problema que un diseñador se encuentra cuando utiliza estos dispositivos para la fabricación de un ecualizador discreto es la reducida variedad de topologías existentes en la literatura. Tras una exhaustiva búsqueda se observa que la inmensa mayoría de las arquitecturas están realizadas en tecnologías CMOS integradas. Una opción es el cambio de tecnología de estas topologías bien descritas y caracterizadas en la literatura.

Es interesante notar que este proceso de migración tecnológica no será directo ya que no sólo las características de los transistores empleados son diferentes sino que los criterios de diseño cambian de un sistema integrado a uno discreto.

En tecnologías integradas la tensión de alimentación es de un valor normalmente fijo dependiente de la longitud del canal y en un diseño discreto este parámetro suele dejar cierto grado de libertad. Por contra, las dimensiones físicas de los componentes activos son variables a determinar en un diseño integrado mientras que en uno discreto son parámetros fijos dependiente del fabricante.

Por otro lado, el coste de componentes pasivos discretos (condensadores, resistencias y bobinas) es muy reducido mientras que en tecnologías integradas aumenta ya que pueden ocupar grandes superficies de silicio.

Todo lo anterior pone de manifiesto la complejidad del proceso de migración tecnológica, el cual, suele conllevar un flujo de diseño diferente al habitualmente utilizado. El flujo de diseño en este escenario comienza con la migración desde un sistema integrado a uno discreto dentro de la misma tecnología para posteriormente pasar a utilizar componentes de la nueva tecnología elegida. Este último paso es crucial para verificar que el comportamiento de la topología bajo estudio es similar al original, ya que suelen aparecer nuevos compromisos de diseño.

Este proceso previo queda descrito en el ANEXO IV. En dicho anexo se presenta una topología habitualmente utilizada en circuitos integrados CMOS, pero diseñada con elementos discretos. La concordancia entre resultados teóricos y experimentales de dicha estructura permite concluir que el comportamiento del bloque se sigue manteniendo y que podría ser apto para una migración tecnológica discreta. En la sección 4.3 se abordará este punto en profundidad.

### 4.3. Ecualizador BJT active shunt peaking

Tal y como se ha expuesto en la sección anterior, los transistores discretos MOSFET comerciales para nuestra aplicación no presentan las prestaciones necesarias, por lo que vamos a presentar como alternativa una migración de la topología *active shunt peaking* en tecnología FET (ANEXO IV) a bipolar.

#### 4.3.1. Diseño del ecualizador BJT *active shunt peaking*

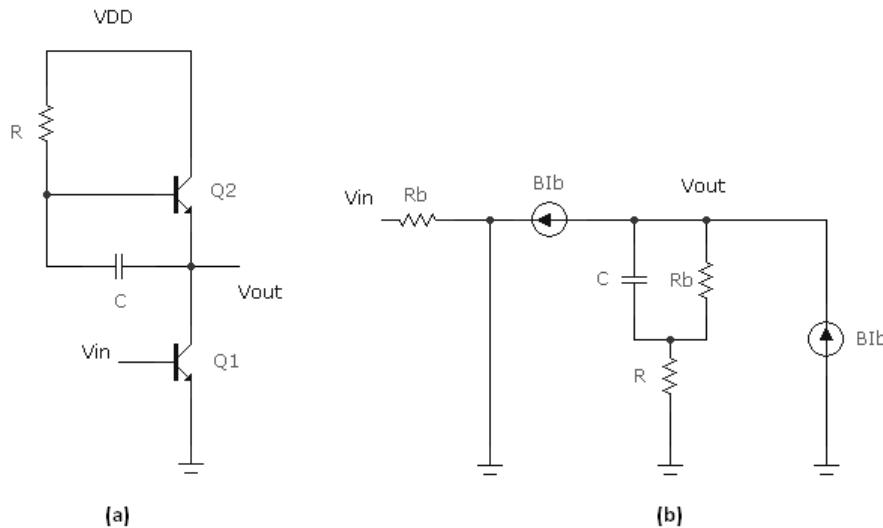

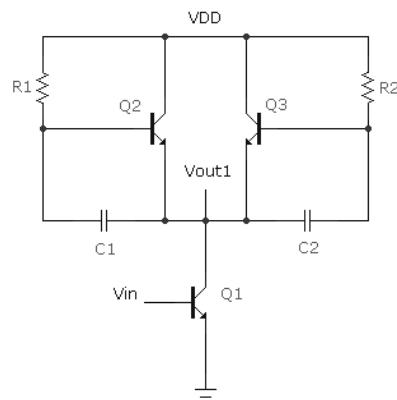

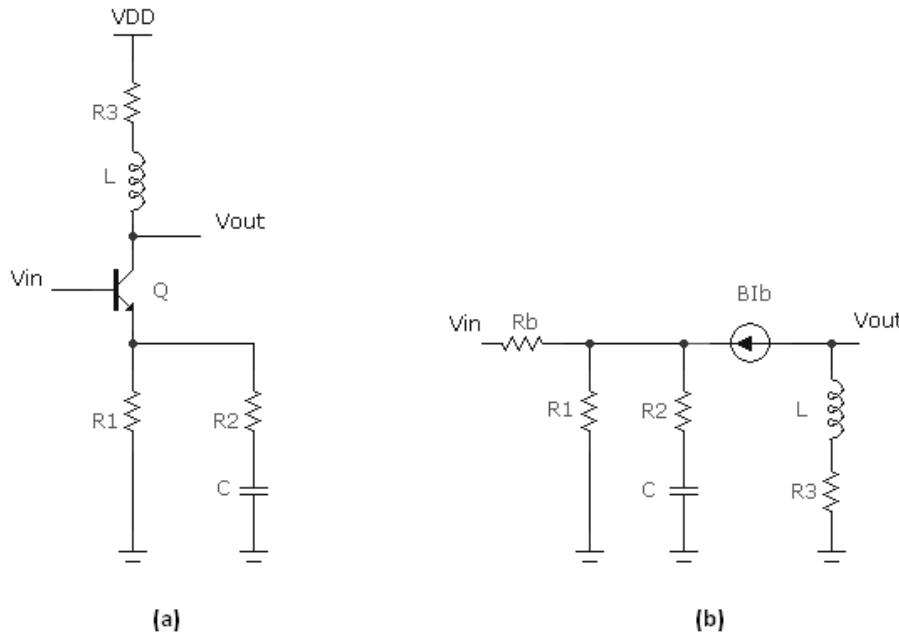

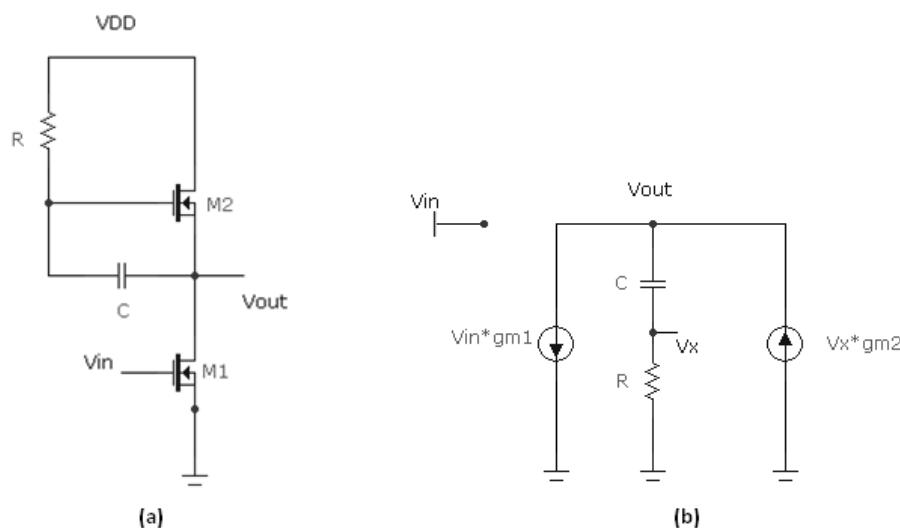

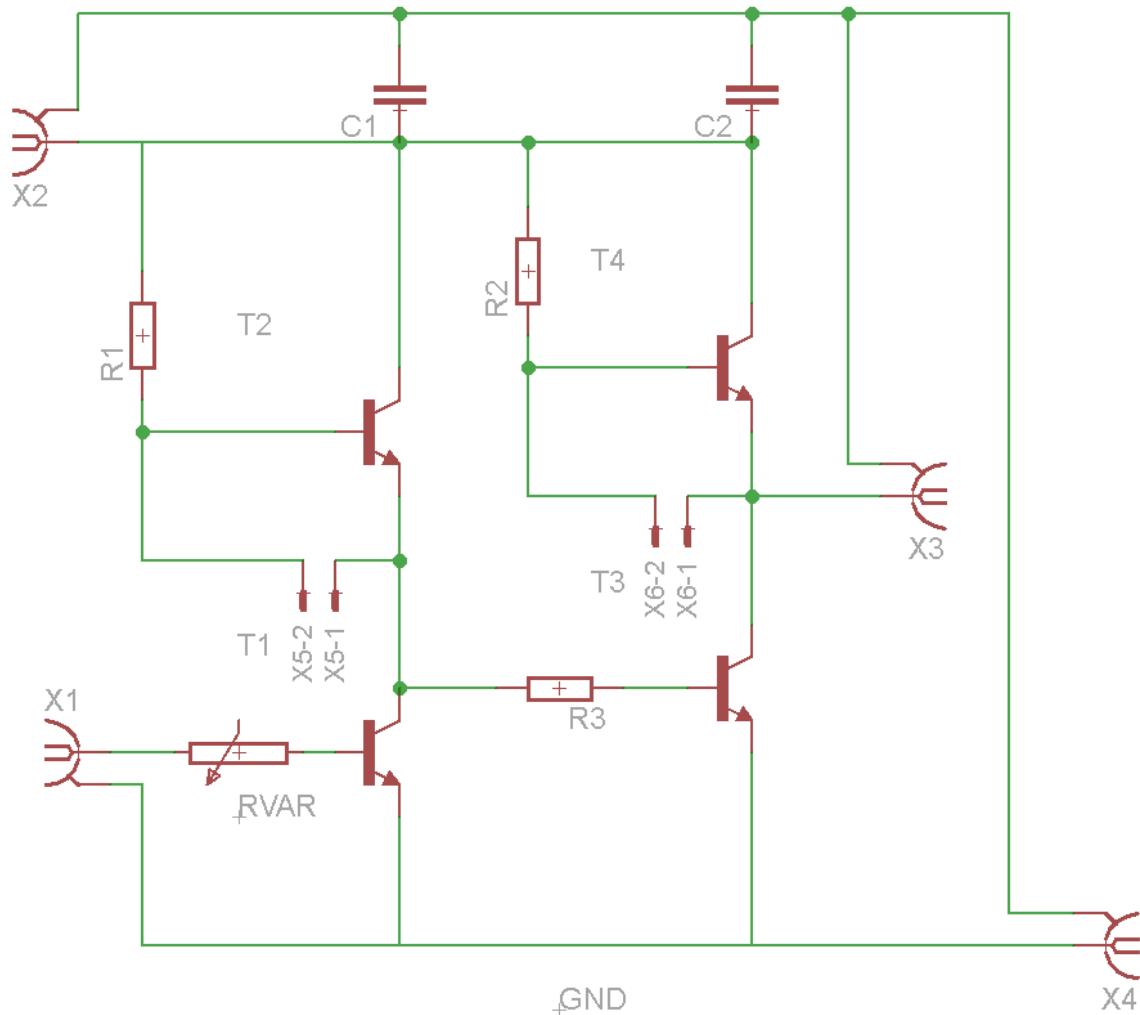

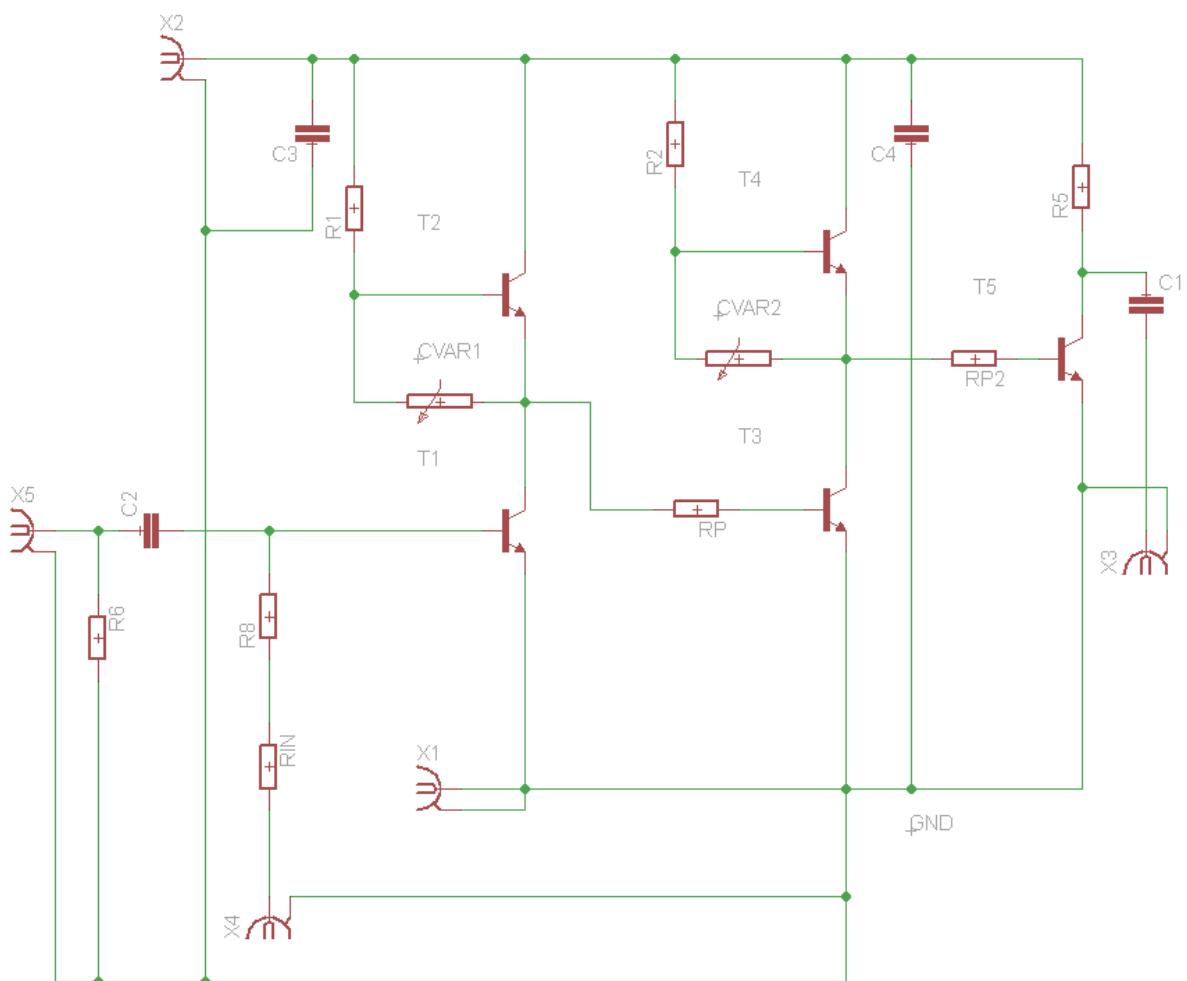

Para ello se usará la misma metodología desarrollada en el ANEXO IV comenzando con el estudio del comportamiento teórico de la estructura ecualizadora con transistores bipolares. La estructura propuesta es la mostrada en la Fig. 24 (a).

Fig. 24 (a) Arquitectura EQ-CT active shunt peaking BJT (b) Circuito equivalente para pequeña señal

El modelo equivalente en AC para pequeña señal, es el mostrado en la Fig. 24 (b), aplicando la teoría de análisis lineal, la función de transferencia que describe el bloque es la presentada en la ecuación (19):

$$\frac{V_o}{V_i} = \frac{-\beta (R + R_b)}{R_{IN} (\beta + 1)} \frac{\frac{R * R_b * C}{R + R_b} s + 1}{\frac{R_b * C}{\beta + 1} s + 1} \quad (19)$$

$$\text{Cero: } \omega_Z = \frac{R_1 + R_b}{R_1 * R_b * C_1}$$

$$\text{Polo: } \omega_P = \frac{\beta + 1}{R_b * C_1}$$

Los motivos de elección de esta estructura básica están basados en: 1) la topología contiene únicamente 2 elementos activos y es relativamente fácil de modelar, 2) es una estructura con mínimos requerimientos en tensión de alimentación, 3) presenta un número reducido de fuentes de ruido y 4) todos los componentes son elementos de bajo coste.

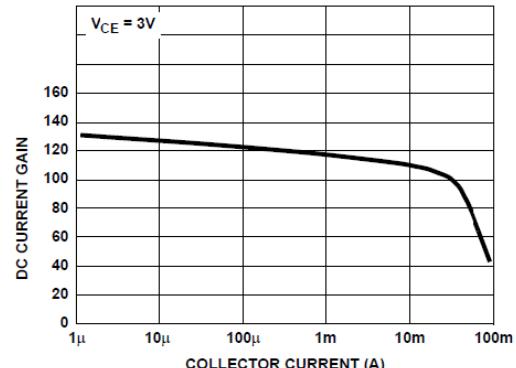

En la ecuación (19) aparecen un polo y un cero. Estos dependen de los parámetros característicos del transistor  $R_b$  y  $\beta$ , y por lo tanto, se requiere un compromiso entre las condiciones de operación en zona activa y la elección de  $R$  y  $C$ .

En la ecuación (16) del análisis teórico de un ecualizador no aparece ningún polo, pero como se puede ver en la ecuación (19), en un ecualizador real aparece un polo que determina el BW del ecualizador. Este polo permite fijar el ancho de banda del bloque limitando así la contribución de ruido.

Para fijar y limitar los valores de  $I_B$ , se colocará una resistencia  $R_{IN}$  en la base del transistor Q1, esta resistencia aparecerá en la ganancia de la función de transferencia.

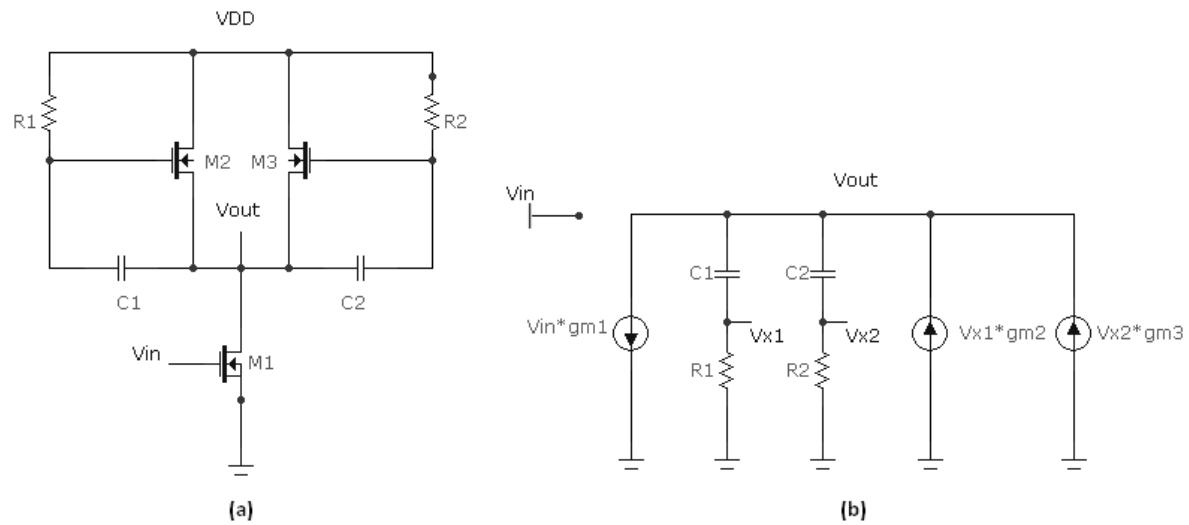

Esta estructura por sí misma no es suficiente para compensar las limitaciones frecuenciales del sistema PD+TIA, ecuación (15), ya que sólo posee un cero. Para introducir el segundo cero se ha seguido la misma metodología y los mismos análisis para las configuraciones de la estructura *active shunt peaking* que en el ANEXO IV. En el caso de la configuración de dos arquitecturas *active shunt peaking* en paralelo con transistores bipolares, Fig. 25, aparecen los mismos problemas y limitaciones que los presentados por los transistores MOSFET por lo que se descarta su elección.

Fig. 25 Dos estructuras *active shunt peaking* en paralelo con BJT

Mediante la estructura en cascada de dos ecualizadores *active shunt peaking* con transistores bipolares, Fig. 26 (a), se consigue el objetivo deseado. Debido al uso de transistores bipolares, el análisis y los resultados son más complejos que en el caso de los MOSFET y se deben incluir algunas modificaciones al circuito.

Fig. 26 (a) Dos estructuras *active shunt peaking* con BJT en cascada (b) Circuito equivalente para pequeña señal

El análisis en AC para pequeña señal, Fig. 26 (b), proporciona la siguiente función de transferencia:

$$\frac{V_o}{V_i} = \frac{\beta^2(R_1 + R_b)(R_2 + R_b)}{R_{IN}(\beta + 1)(R_1 + R_b + (R_b + R_p)(\beta + 1))} . \quad (20)$$

$$\frac{\left( \frac{R_1 * R_b * C_1}{R_1 + R_b} s + 1 \right) \left( \frac{R_2 * R_b * C_2}{R_2 + R_b} s + 1 \right)}{\left( \frac{R_b * C_2}{\beta + 1} s + 1 \right) \left( \frac{R_b * (R_1 + R_b + R_p) * C_1}{R_1 + R_b + (R_b + R_p)(\beta + 1)} s + 1 \right)}$$

$$\text{Ceros: } \omega_{Z1} = \frac{R_1 + R_b}{R_1 * R_b * C_1}, \quad \omega_{Z2} = \frac{R_2 + R_b}{R_2 * R_b * C_2}$$

$$\text{Polos: } \omega_{P1} = \frac{R_1 + R_b + (R_b + R_p)(\beta + 1)}{R_b * (R_1 + R_b + R_p) * C_1}, \quad \omega_{P2} = \frac{\beta + 1}{R_b * C_2}$$

Se obtienen dos ceros independientes mediante la adecuada elección de  $R_1$ ,  $R_2$ ,  $C_1$  y  $C_2$ . En uno de los polos aparece una dependencia con  $R_1$  y  $R_p$  por lo que se deben elegir estos valores junto al de  $C_1$  de forma que el polo esté suficientemente lejos de las frecuencias de trabajo. La ganancia del sistema se puede controlar modificando los valores de las resistencias de la estructura. Ya que  $R_1$ ,  $R_2$  y  $R_p$  están comprometidos por el valor de los polos, ceros y las condiciones de polarización, queda libre el valor de  $R_{IN}$  para establecer la ganancia que se desee.

Realizando el análisis en DC para asegurar el modo de operación en activa de los transistores, obtenemos restricciones en los grados de libertad del valor de los elementos resistivos de la primera red *active shunt peaking* al tener que ser un valor fijo la suma  $R_p + R_1$ .

Si tenemos en cuenta que una de las compensaciones frecuenciales será siempre la misma, la que impone el conjunto TIA más fotodiodo, se fijará la primera red ecualizadora de la Fig. 26 (a) para compensar este conjunto. La limitación frecuencial de la fibra se compensará con la segunda red ecualizadora.

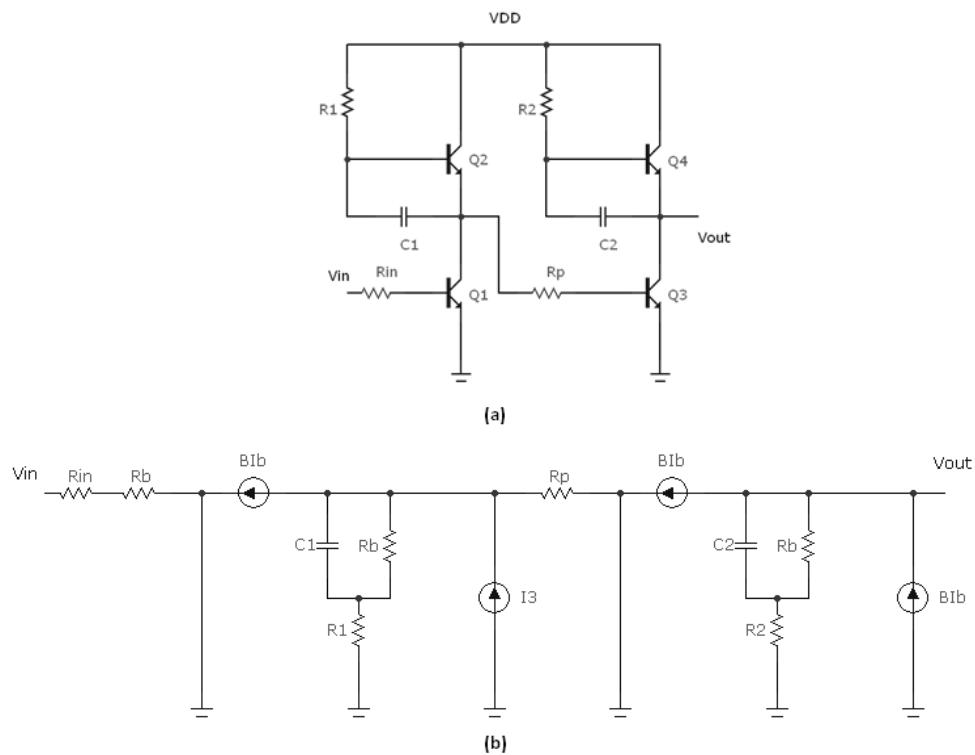

#### 4.3.2. Implementación del ecualizador BJT *active shunt peaking*

Una vez elegida la estructura *active shunt peaking* en cascada con transistores bipolares se abordará un proceso de simulación eléctrica y posterior fabricación de prototipo utilizando transistores discretos sencillos ampliamente conocidos. El objetivo de este prototipo será la verificación de su correcto comportamiento frecuencial (a bajas frecuencias) como paso previo a abordar el diseño más complejo del ecualizador de alta frecuencia.

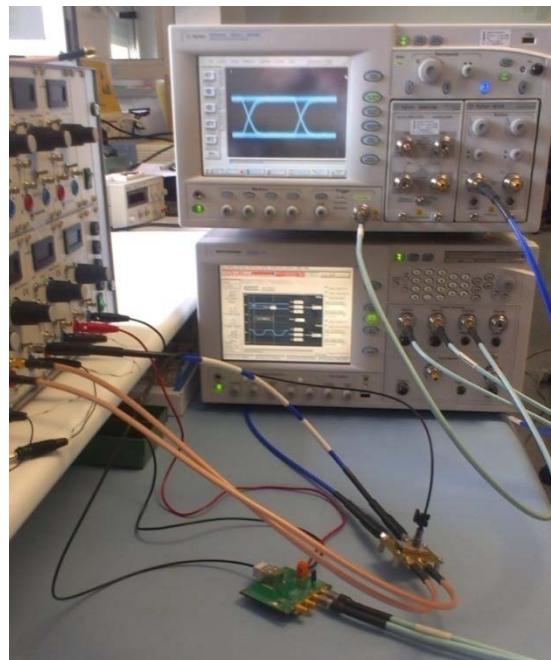

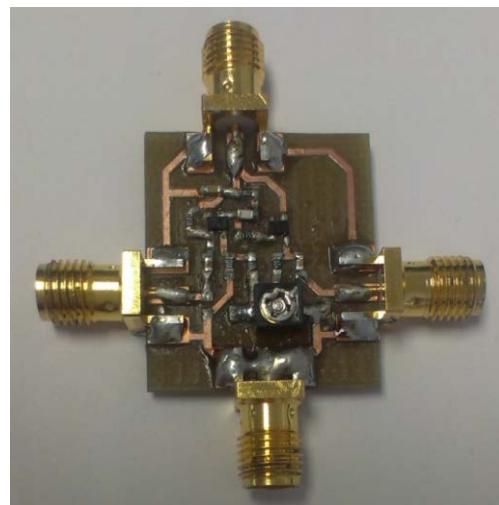

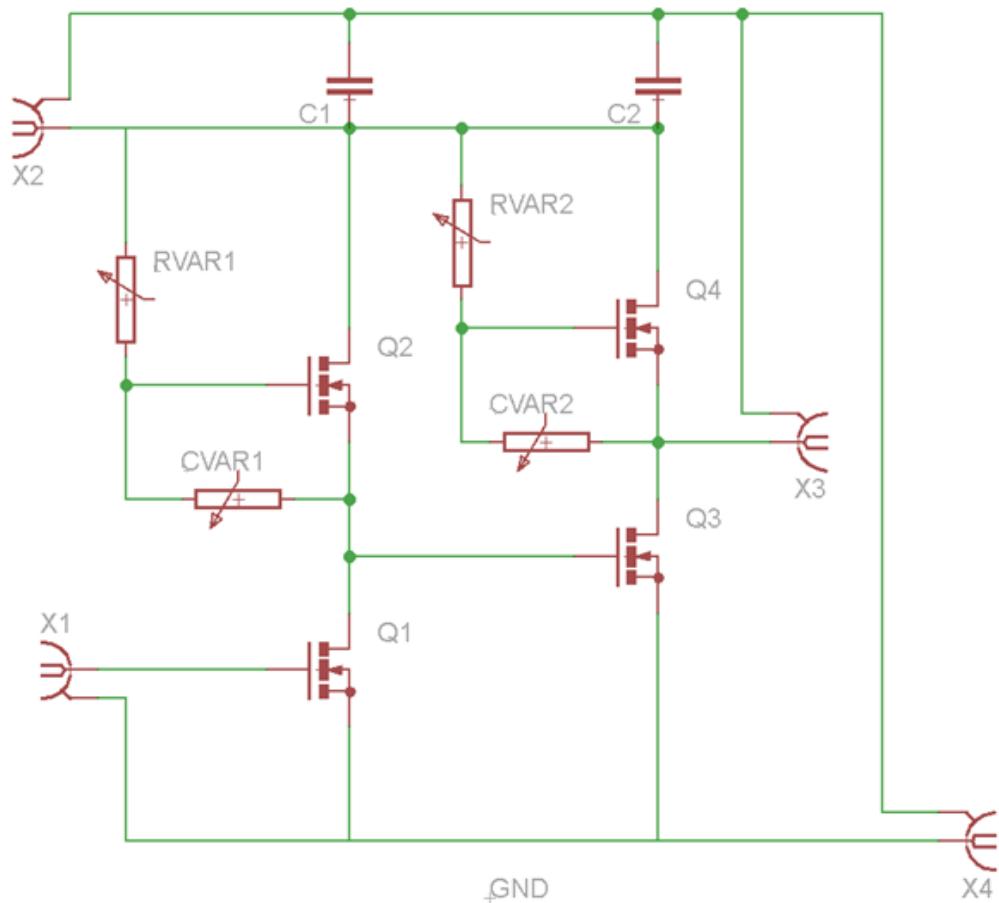

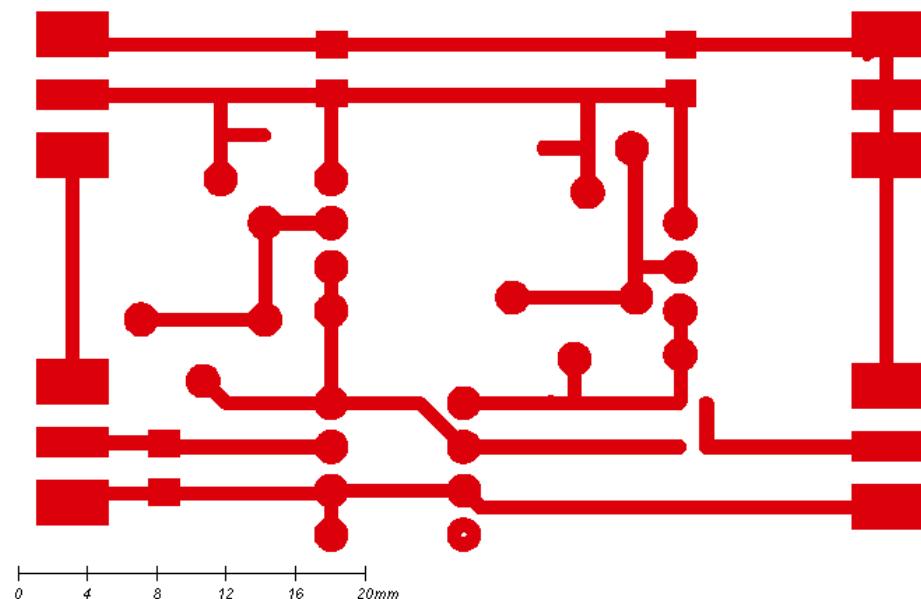

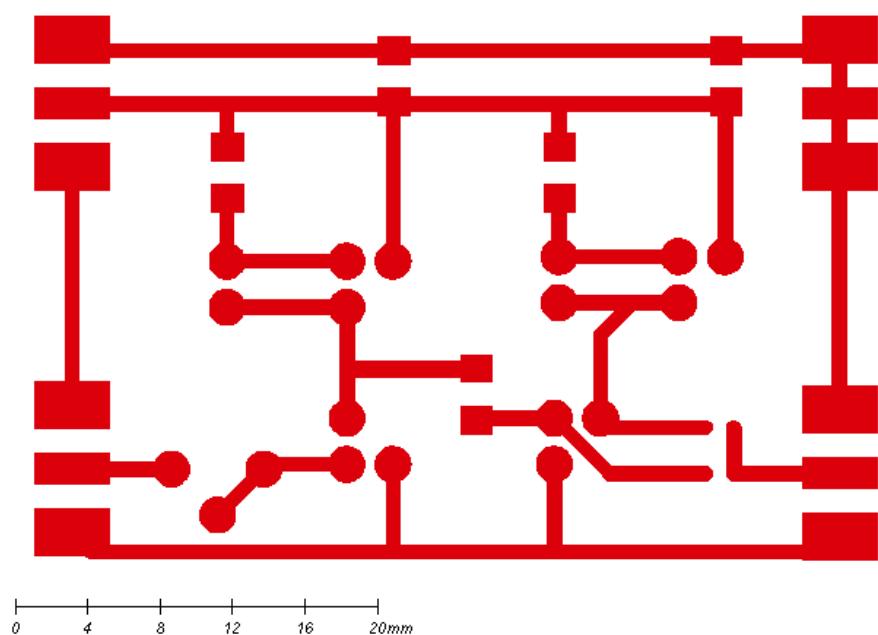

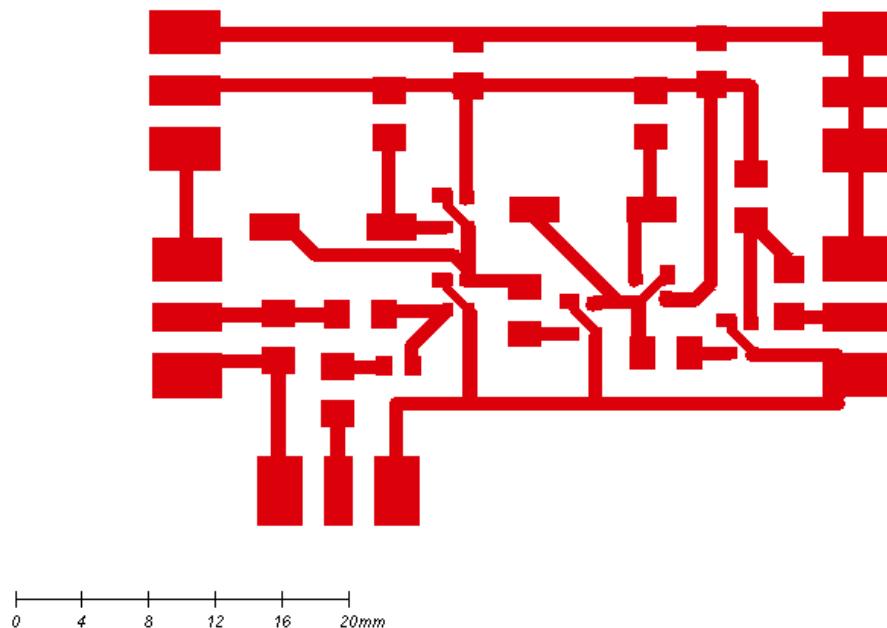

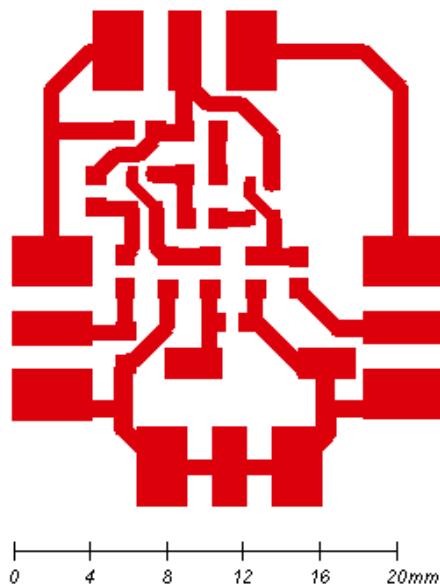

Para ello se han realizado simulaciones utilizando los modelos de *Spice* de los componentes con el entorno de simulación *PSpice* de *Cadence* y posteriormente se ha diseñado una PCB mediante el *software* de diseño electrónico *Eagle* para comprobar experimentalmente los resultados.

Se ha elegido el transistor bipolar **2N222A** de *ST* para la implementación del ecualizador. Debido a las restricciones sobre el rango de variación de los elementos resistivos del ecualizador, se ha optado por dejar estos componentes con un valor fijo calculado previamente y variar los condensadores  $C_1$  y  $C_2$ . Es interesante contrastar que esta restricción es producto de la migración tecnológica ya que para la topología con MOSFET (ANEXO IV), suelen ser las resistencias los valores modificables de la red de compensación.

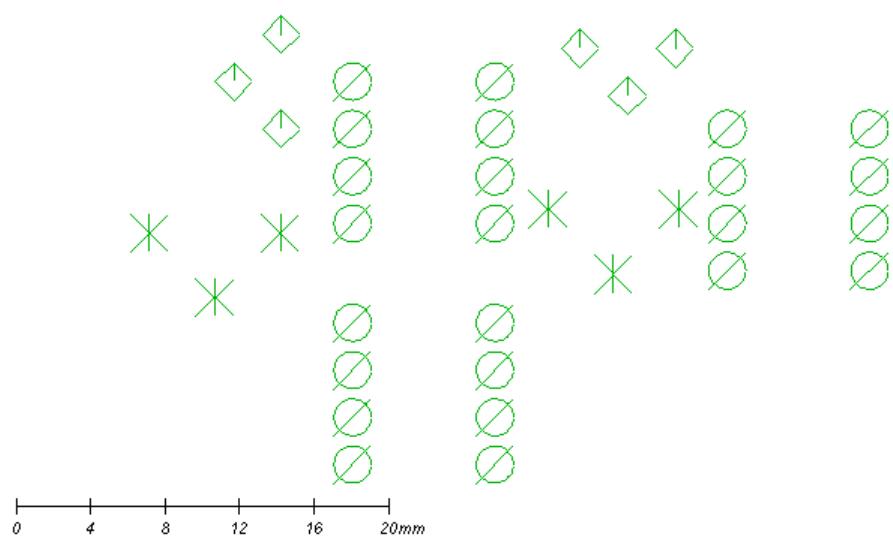

Dado que la ganancia se puede controlar mediante  $R_{IN}$ , se ha colocado un *trimmer* con el que controlar la ganancia del ecualizador para las diferentes medidas experimentales. Se han utilizado conectores SMA y las resistencias y el resto de componentes de la PCB son SMD 1206 estándar, Fig. 27. Los esquemáticos y planos se encuentran en el ANEXO V: planos.

Fig. 27 Prototipo ecualizador bipolar para bajas frecuencias

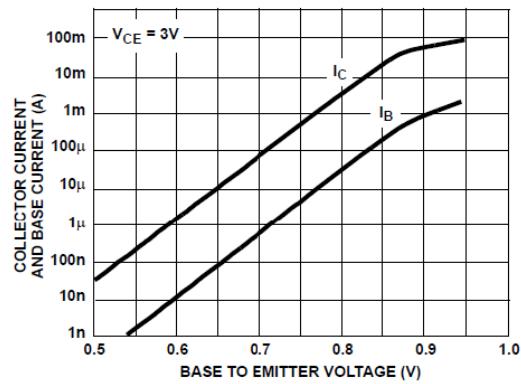

Mediante los *datasheets* y la simulación, se elige la corriente de base con un compromiso entre bajo consumo y una buena respuesta frecuencial de los transistores y se fija mediante  $V_{in}$  y  $R_{in}$ . A partir de este valor de corriente por base, se calculan los valores de los elementos del ecualizador para la correcta polarización del circuito y se obtienen los valores característicos del transistor  $R_B$  y  $\beta$ . Con todos estos valores se procede al cálculo de los condensadores para fijar los ceros y los polos con los que se va a trabajar.

Para medir las respuestas frecuenciales, se ha utilizado un generador de señales capaz de trabajar hasta 30 MHz (33522A, *Agilent*) con el que se genera la señal AC de excitación del circuito más un offset para polarizar los transistores en DC.

Variando la frecuencia de esta señal se tomaron los valores de amplitud en la salida del circuito con un osciloscopio digital (MSO9404A, *Agilent*) para definir la respuesta frecuencial de los ecualizadores. Estos equipos presentan impedancias infinitas de entrada y salida en sus terminales por lo que se han podido interconectar con los ecualizadores directamente.

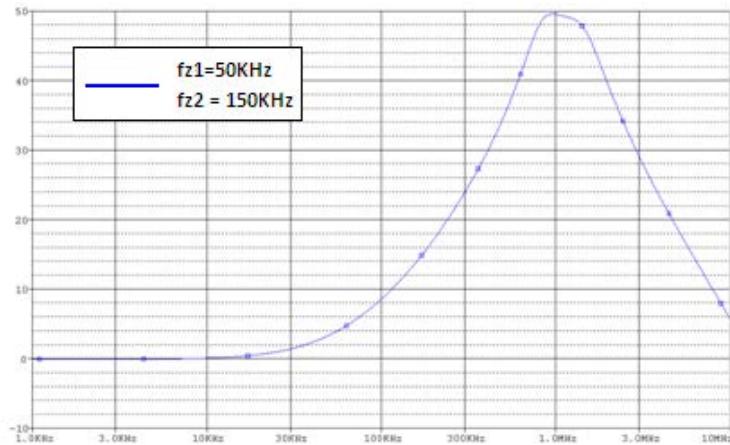

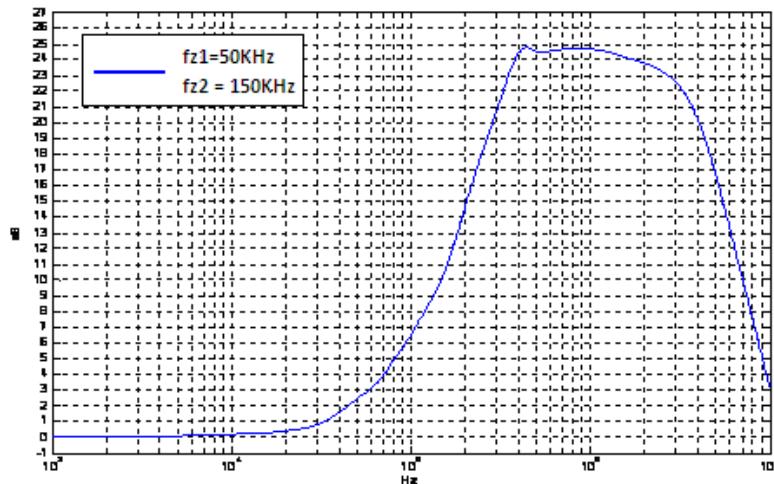

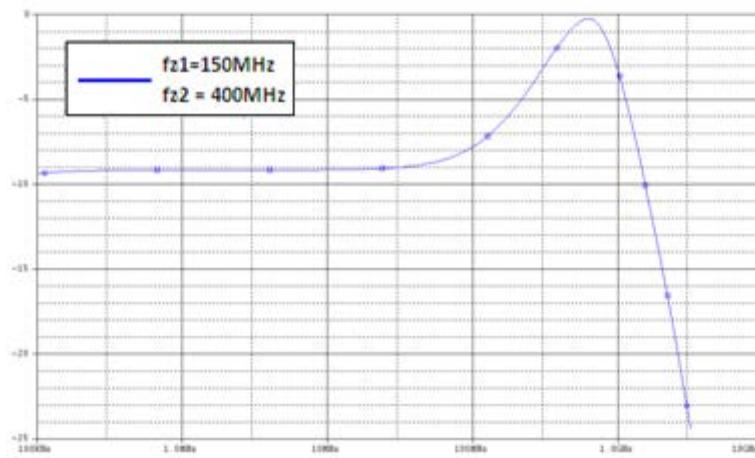

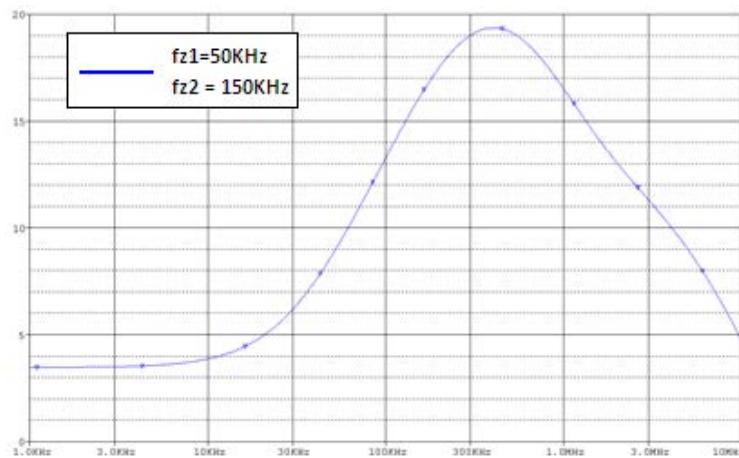

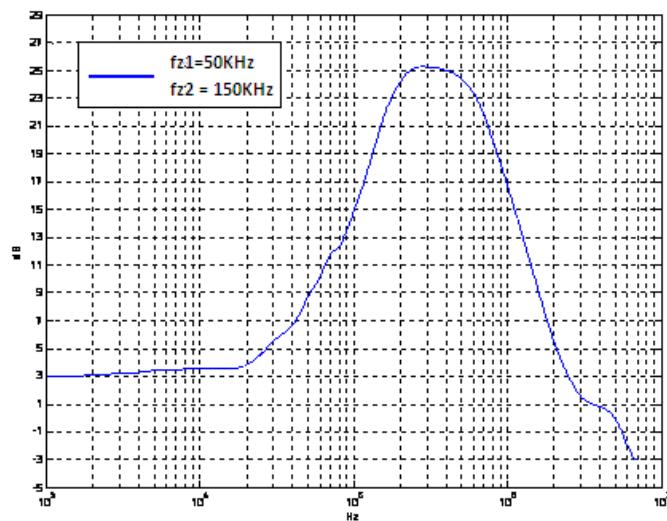

Con los valores de componentes mostrados en la Tabla 4, obtenemos los siguientes resultados mediante simulación (Fig. 28) y experimentales (Fig. 29) del prototipo para las dos siguientes frecuencias de ecualización:  $f_{z1} = \omega_{z1}/2\pi = 50 \text{ KHz}$  y  $f_{z2} = \omega_{z2}/2\pi = 150 \text{ KHz}$ .

## Diseño del ecualizador en tiempo continuo

| PARÁMETRO | VALOR         |

|-----------|---------------|

| $V_{DD}$  | 2 V           |

| $R_1$     | 1800 $\Omega$ |

| $R_2$     | 1000 $\Omega$ |

| $R_p$     | 3900 $\Omega$ |

| $C_1$     | 3 nF          |

| $C_2$     | 12 nF         |

Tabla 4 Valores de los parámetros del prototipo de ecualizador *active shunt peaking* 2N2222

Fig. 28 Resultados simulación ecualizador *active shunt peaking* 2N2222.

Fig. 29 Resultados experimentales ecualizador *active shunt peaking* 2N2222.

El prototipo se comporta de la forma deseada a las frecuencias calculadas para los ceros del ecualizador y coincide con las pruebas realizadas en el simulador. Si comparamos las ganancias de las figuras anteriores, se observa que en los resultados experimentales es menor. Esto es debido a que se satura a valores próximos a  $V_{DD}$ , algo que no se observa en el análisis AC del simulador debido a su aproximación lineal pero si en el análisis transitorio del simulador.

Sin embargo el ancho de banda del ecualizador no llega hasta el polo teórico del sistema ya que el pico del *boosting* cae a frecuencias más bajas. Esto es debido a limitaciones frecuenciales provenientes de efectos parásitos que se presentan en los transistores (en los que se ha usado un modelo de pequeña señal simplificado para los cálculos teóricos) y al *routing* de la PCB. La información extraída de estos resultados es valiosa de cara a hacer el prototipo final ya que parámetros como la capacidad por unidad de superficie de la PCB o el grado de modelado de los componentes activos pueden ser establecidos desde el principio.

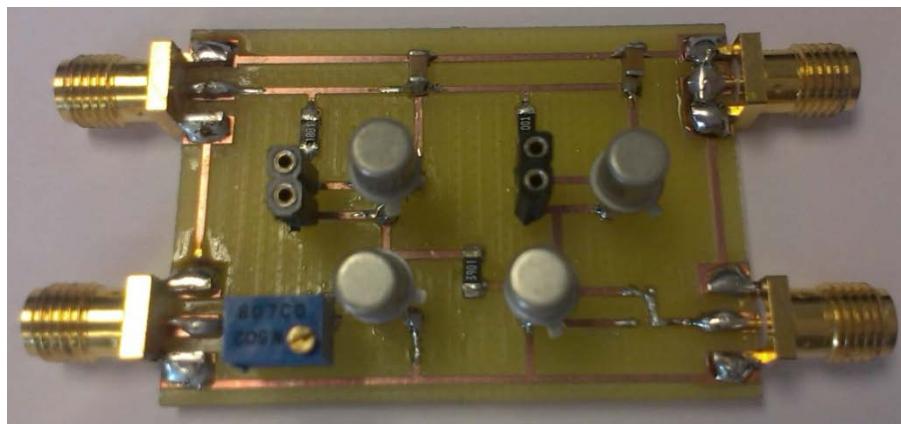

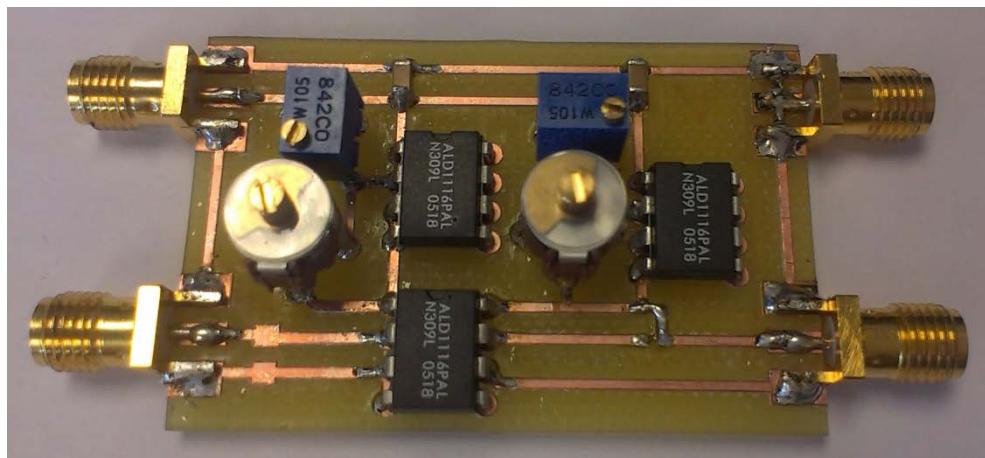

#### 4.3.3. Implementación del ecualizador BJT *active shunt peaking* para alta frecuencia

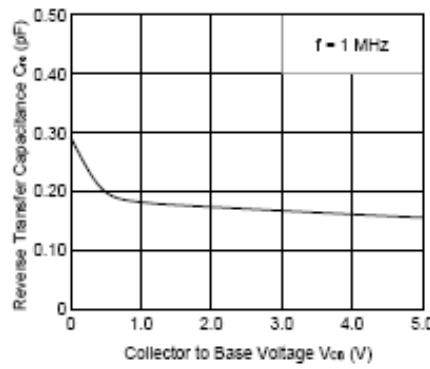

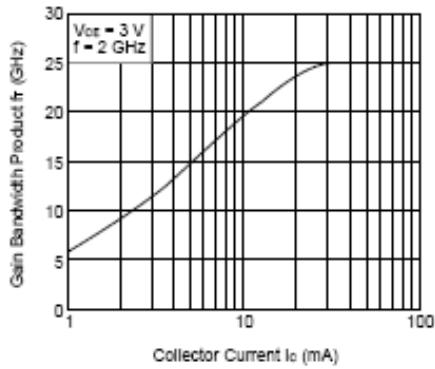

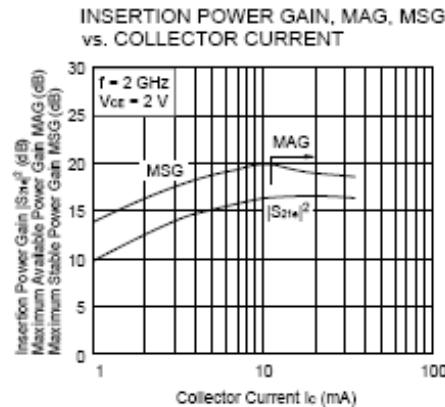

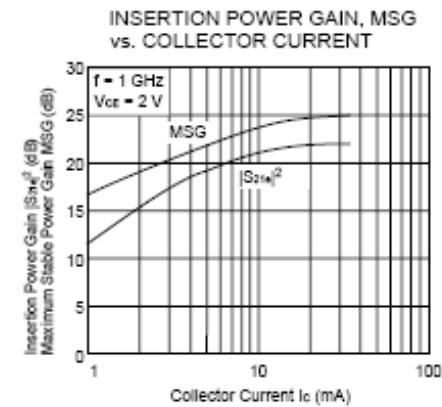

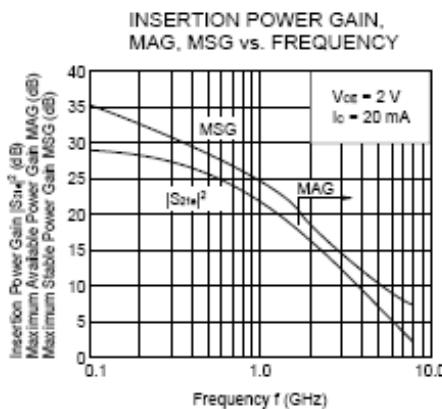

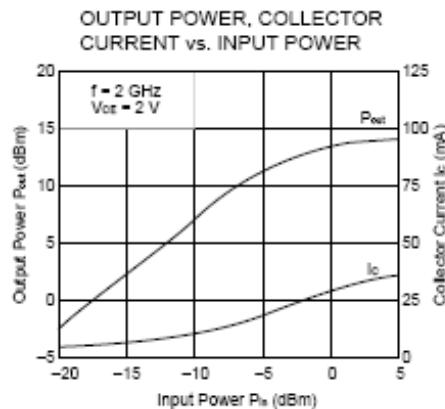

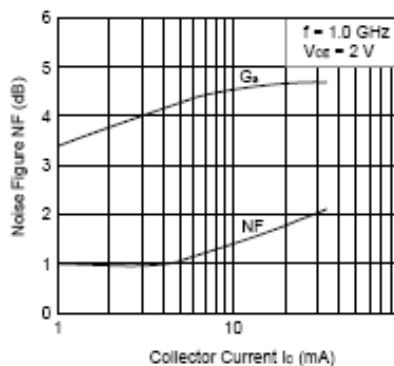

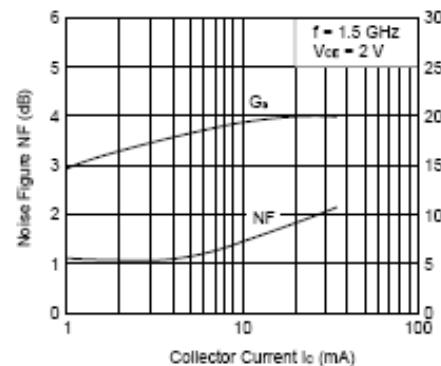

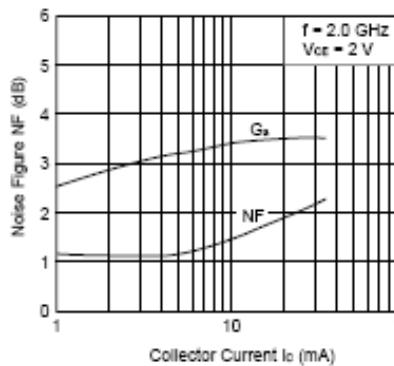

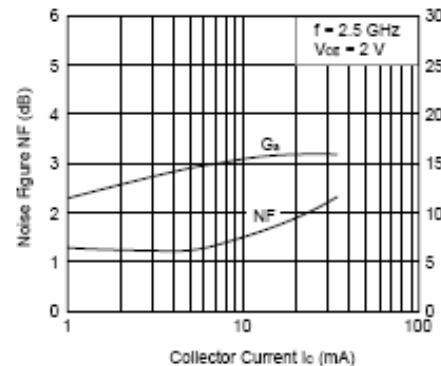

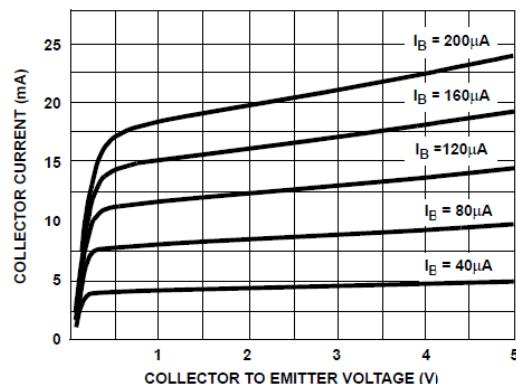

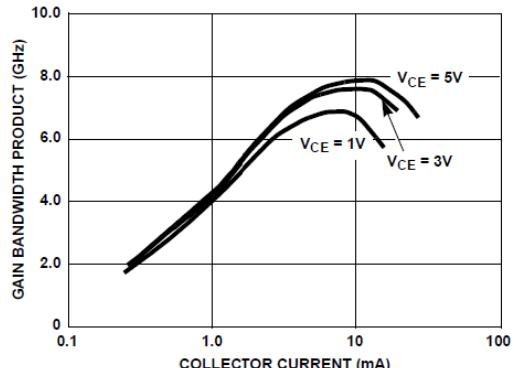

A la hora de abordar la implementación del ecualizador final el primer paso es la elección de un transistor bipolar capaz de trabajar a frecuencias elevadas. Entre la oferta disponible en el mercado de transistores Si-BJT con esta característica se ha elegido el transistor **NE662M04** de *California Eastern Laboratories*.

El valor de la intensidad de base (y del cual dependen los parámetros característicos de los transistores, ver *datasheet* en ANEXO VI: *datasheets*) se ha elegido en función de un compromiso entre el consumo y la frecuencia de transición del transistor. La tensión de alimentación del bloque se ha fijado en un valor compatible con el utilizado para el TIA, el cual recordemos es 1.8 V.

El valor de uno de los ceros está fijado por el conjunto TIA/fotodiodo a 150MHz y el otro debe ser ajustable, debido a la variación de la limitación frecuencial introducida por la fibra óptica. Los valores de todos los componentes teniendo en cuenta estas premisas de diseño se muestran en la Tabla 5.

| PARÁMETRO | VALOR             |

|-----------|-------------------|

| $V_{DD}$  | 1.8 V             |

| $R_1$     | 180 $\Omega$      |

| $R_2$     | 180 $\Omega$      |

| $R_p$     | 330 $\Omega$      |

| $R_b$     | 200 $\Omega$      |

| $V_{in}$  | 0.87 V            |

| $\beta$   | 70                |

| $I_B$     | 100 $\mu\text{A}$ |

| $R_{in}$  | 100 $\Omega$      |

| $C_1$     | 3 nF              |

| $C_2$     | 12 nF             |

Tabla 5 Valores de los parámetros del prototipo de ecualizador *active shunt peaking* BJT para alta frecuencia

Tenidos en cuenta todas estas elecciones, se ha llevado a cabo la simulación eléctrica del ecualizador con los modelos *Spice* proporcionados por el fabricante en los que se incluyen los efectos del encapsulado, por lo que a priori el comportamiento real debería ajustarse a los resultados obtenidos en simulación.

## Diseño del ecualizador en tiempo continuo

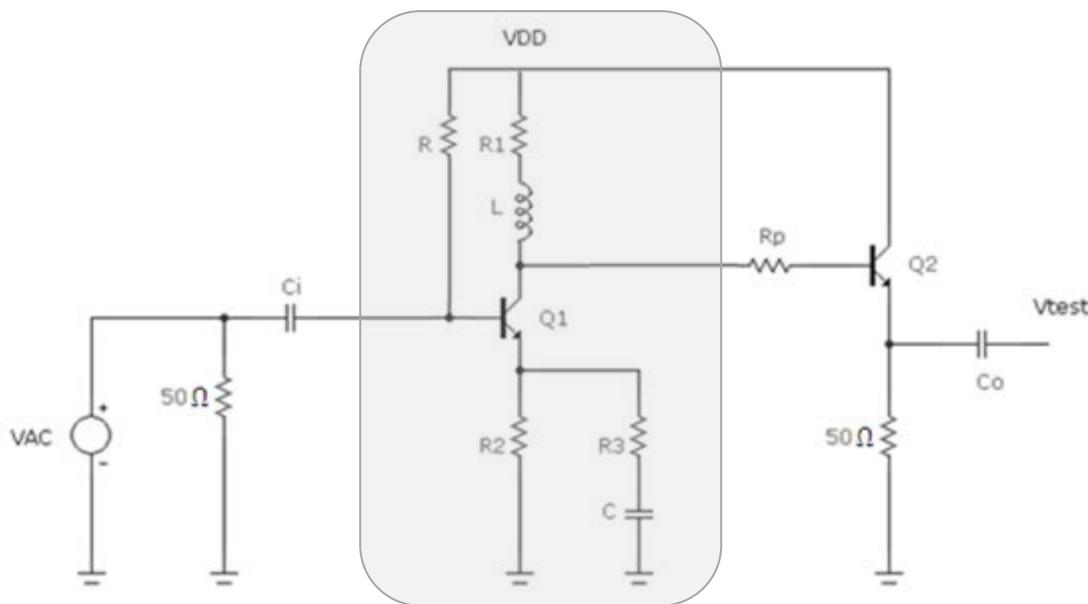

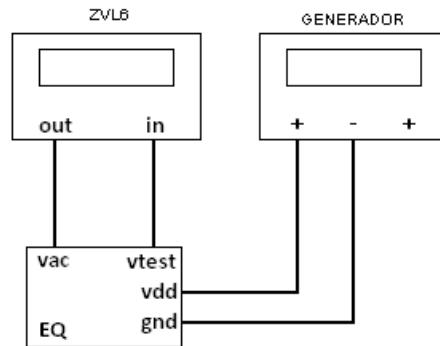

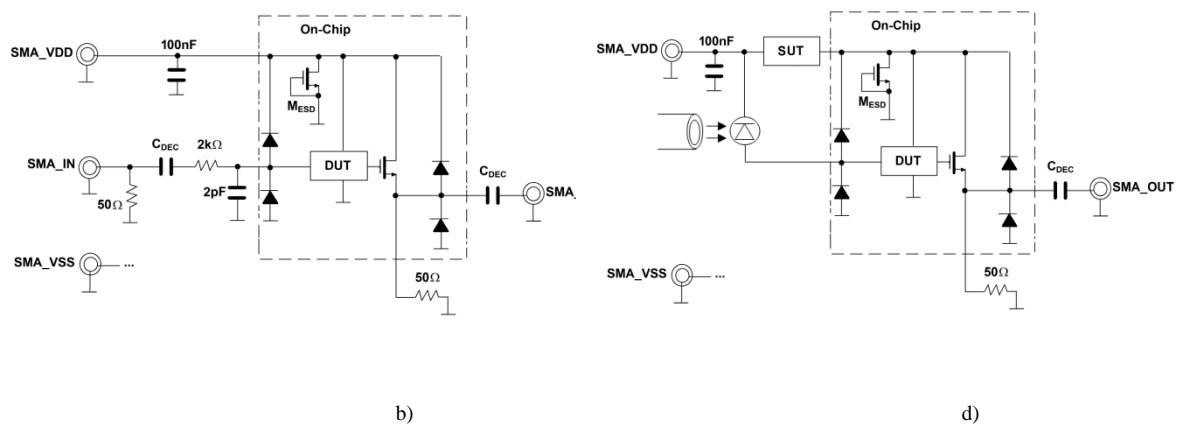

En el caso de alta frecuencia, se deben tomar consideraciones especiales para la medida de la respuesta frecuencial ya que se utilizan equipos específicos que requieren una adaptación de impedancias de  $50\ \Omega$  y un filtrado de la componente DC de las señales. Por lo tanto, antes de la fabricación del ecualizador, se debe tener en cuenta cómo se van a realizar las medidas experimentales.

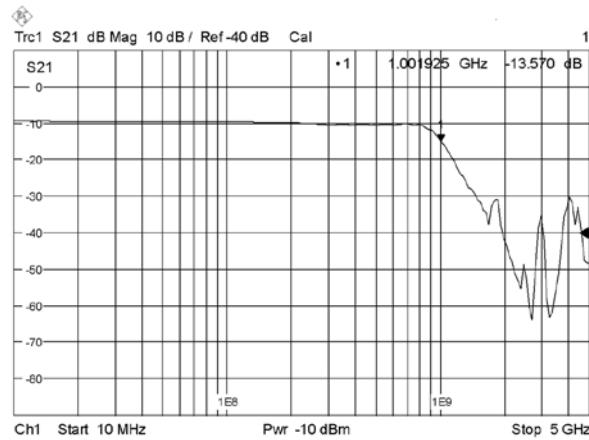

En este trabajo, se va medir la respuesta frecuencial con un analizador de redes de *Rohde & Schwarz vector network analyzer ZVL6*, que posee un rango de frecuencias de 9KHz a 6GHz y un *matching* de entrada y salida de  $50\ \Omega$ .

Para adaptar el ecualizador al equipo de medida, se debe diseñar un circuito de *test*. Para la etapa de entrada hay que tener en cuenta la adaptación de impedancias a  $50\ \Omega$  y la necesidad de proporcionar un nivel en DC para polarizar los transistores del ecualizador.

Para la etapa de salida es necesario incluir un driver de desacoplo para acomodar las impedancias y reducir la influencia del sistema de test sobre los resultados finales.

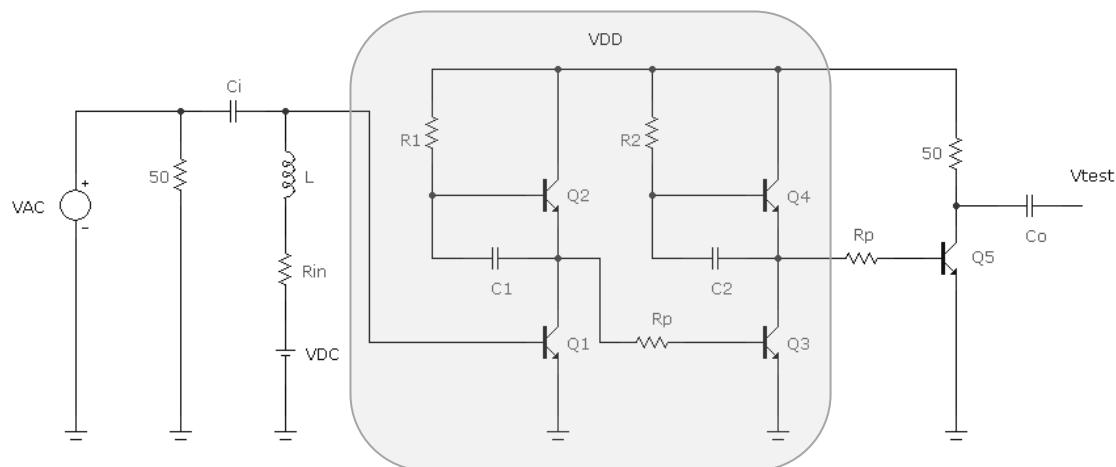

Teniendo esto en cuenta, el circuito final resultante con los circuitos de *test* incluidos del ecualizador se muestra en la Fig. 30.

Fig. 30 Ecualizador *active shunt peaking BJT* (DUT en recuadro gris) con etapas de *test*.

Todos los componentes de la placa, incluidos los transistores, son SMD. Para los condensadores variables se han usado unos *trimmers* SMD con un rango de variabilidad de entre 7 pF y 50 pF que permiten la fijación de los ceros en las frecuencias de trabajo.

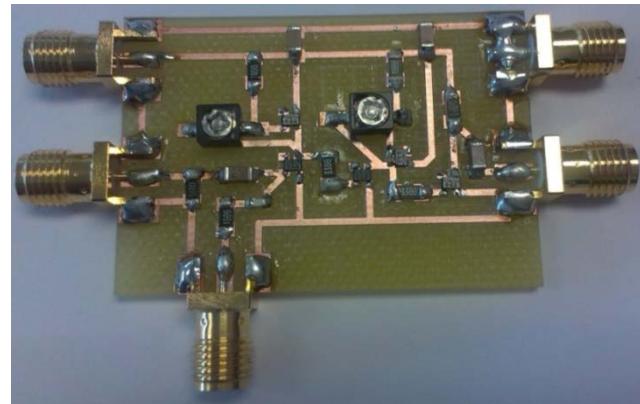

El resto de condiciones de diseño son las mismas que las empleadas en caso de baja frecuencia. El resultado puede verse en la Fig. 31. Los esquemáticos y planos se encuentran en el ANEXO V: planos.

**Fig. 31 Prototipo ecualizador *active shunt peaking BJT* alta frecuencia**

Los resultados de la simulación han mostrado un comportamiento satisfactorio a frecuencias elevadas alcanzando valores de ancho de banda próximos al GHz, BW = 900MHz en el ejemplo de la Fig. 32.

**Fig. 32 Simulación de ecualizador *active shunt peaking BJT* para alta frecuencia.**

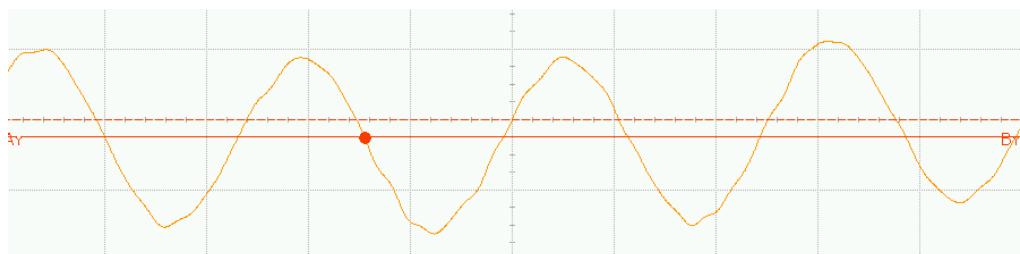

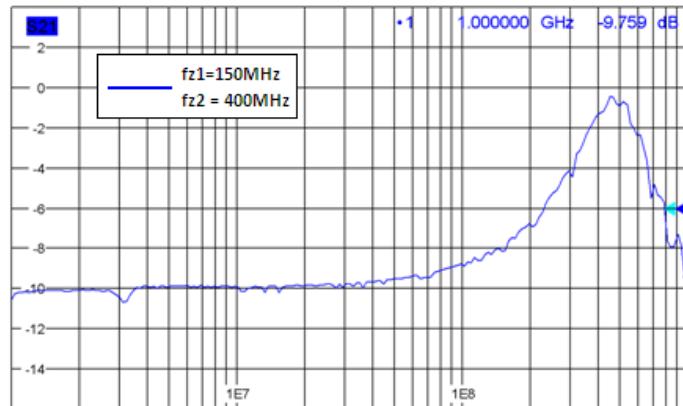

De los resultados experimentales, se puso de manifiesto un problema de estabilidad como se puede ver en el comportamiento oscilante de la Fig. 33. Este comportamiento indeseado tiene su origen en el lazo de realimentación positiva de la estructura ecualizadora, Fig. 24, y está relacionado con las capacidades parásitas entre terminales del transistor. Al ser estas capacidades muy pequeñas, del orden de pF, estos efectos indeseados no aparecieron cuando se llevó a cabo el estudio experimental del prototipo de baja frecuencia.

**Fig. 33 Oscilación de la estructura *active shunt peaking BJT***

Se ha probado la misma estructura con un transistor diferente, HFA3127 de *Intersil* (ANEXO VI: *datasheets*), para desechar la hipótesis de que el comportamiento inestable es debido al comportamiento particular del transistor NE662M04 obteniendo el mismo resultado indeseado del ecualizador.

Para justificar este comportamiento oscilante se realiza un análisis teórico de la estructura teniendo en cuenta las capacidades parásitas asociadas al transistor base emisor  $C_{BE}$  y base colector  $C_{BC}$ . Realizando el análisis para pequeña señal obtenemos la siguiente ecuación característica del sistema con el lazo de realimentación para una rama ecualizadora (Fig. 24 a):

$$\frac{R_B}{1 + R_B C_S} + \frac{R}{1 + R C_{BC} S} + \frac{R_o (1 + C_{BE} R_B S)}{1 + (R_o C_o + R_o C_{BC} \beta) S} \left( 1 + \frac{\beta}{1 + R_B C_S} \right) = 0 \quad (21)$$

Dónde  $R_o$  y  $C_o$  son la resistencia y capacidad que ve la estructura en su salida que en nuestro caso se corresponderán con la resistencia y capacidad de entrada vista desde la base del siguiente transistor de la estructura ecualizadora, Fig. 30.

A la hora de hallar una condición de oscilación a partir de la ecuación (21), nos encontramos con un sistema de cuarto orden en donde todos los parámetros están relacionados entre sí, por lo que no es una tarea trivial el poder identificar la condición de oscilación y controlarla mediante el cambio del valor de los componentes del circuito.

Es importante notar que la topología *active shunt peaking* CMOS integrada original es altamente estable. Pero los resultados experimentales de esta sección demuestran que el comportamiento del bloque tras la migración tecnológica a elementos discretos y bipolares conlleva unos cambios que no hacen viable tal migración.

A la vista de estos resultados, es necesario replantear la estructura ecualizadora por una que presente un comportamiento estable al trabajar en altas frecuencias.

#### **4.4. Ecualizador BJT *pasive shunt peaking***

##### **4.4.1. Diseño del ecualizador *pasive shunt peaking***

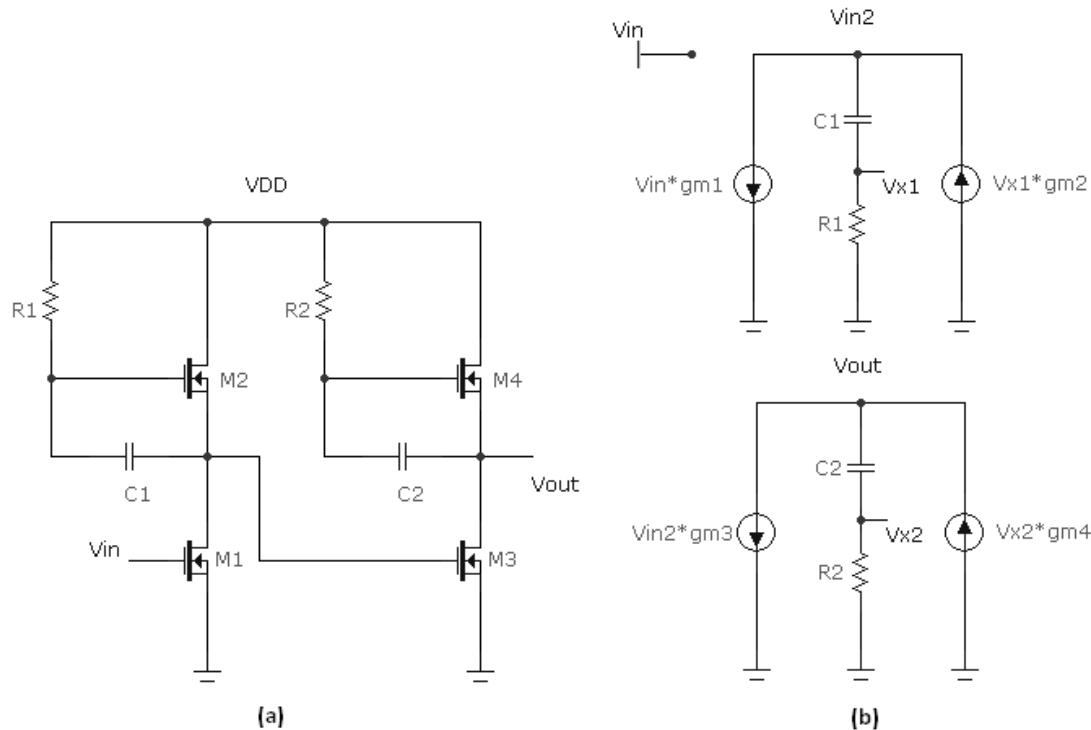

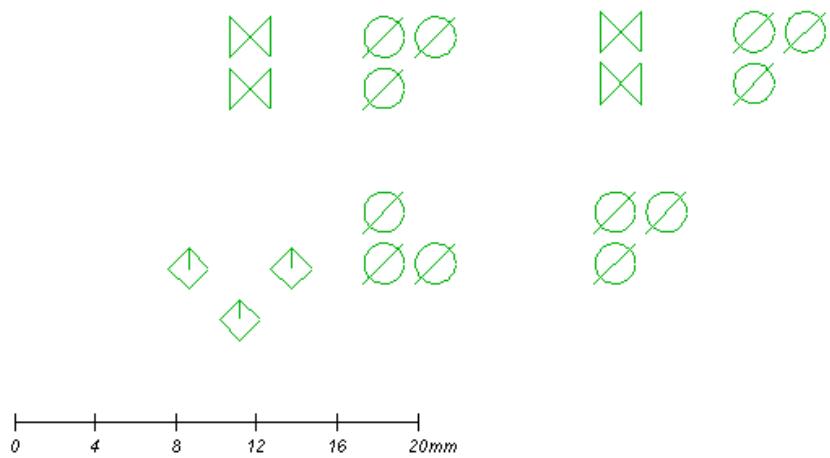

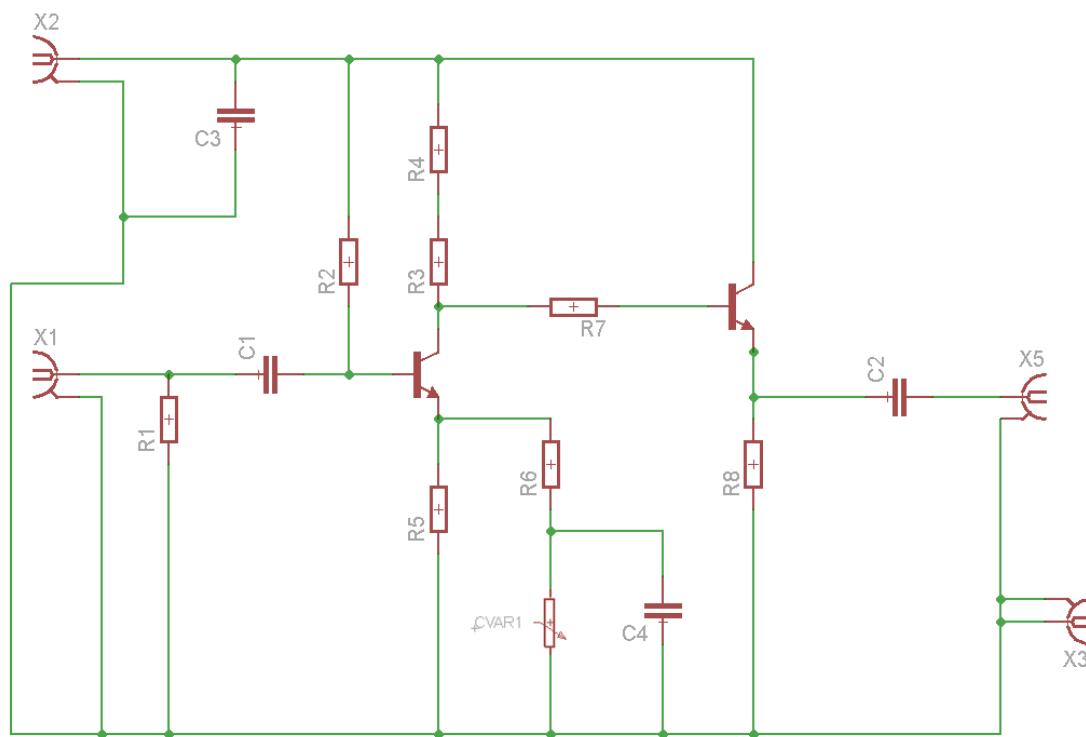

Para el diseño de la nueva estructura se ha eliminado el lazo de realimentación de los transistores para evitar una posible inestabilidad del sistema. La arquitectura usada es el resultado de unir una topología de degeneración de emisor con un filtro pasa baja [RAD05] más una topología *pasive shunt peaking* mediante la inclusión de una bobina, Fig. 34 (a).

El motivo de esta unión de estructuras ecualizadoras es la necesidad de obtener dos ceros para compensar las limitaciones frecuenciales del sistema, ecuación (17), ya que la estructura *pasive shunt peaking* presenta una función de transferencia similar a la estructura *active shunt peaking* con un solo cero.

Se va a seguir la misma metodología de diseño que en los anteriores apartados utilizando los transistores BJT para altas frecuencias directamente en la implementación del ecualizador.

Fig. 34 (a) Arquitectura EQ-CT *pasive shunt peaking* del ecualizador (b) Circuito equivalente para pequeña señal

Se realiza el análisis AC para pequeña señal de la estructura propuesta para obtener su comportamiento en frecuencia, Fig. 34 (b). La función de transferencia resultante es la presentada en la ec. (22):

$$\frac{V_{out}}{V_{in}} = -\frac{\beta R_1}{\beta R_2 + R_b} \frac{\left(1 + \frac{L}{R_1}s\right)(1 + (R_2 + R_3)Cs)}{1 + \frac{\beta R_2 R_3 + R_b R_2 + R_b R_3}{\beta R_2 + R_3} Cs} \quad (22)$$

donde:

$$\omega_{z1} = \frac{R_1}{L}, \quad \omega_{z2} = \frac{1}{(R_2 + R_3)C} \quad (23)$$

$$\omega_p = \frac{\beta R_2 + R_3}{(\beta R_2 R_3 + R_b R_2 + R_b R_3)C} \quad (24)$$

Como se observa en la ecuación anterior, la función de transferencia del ecualizador incluye los dos ceros buscados. El valor de estos ceros depende de la red de elementos pasivos del ecualizador por lo que su posición en el dominio frecuencial se calculará tomando valores de manera adecuada de las resistencias, el condensador y la bobina.

En cuanto al polo del sistema, fijará el ancho de banda del ecualizador por lo que se debe situar en una frecuencia coherente con el *bitrate* y contribuciones de ruido que se pretenden alcanzar. Para ello, teniendo en cuenta el valor del parámetro característico  $\beta$  del transistor, se debe hacer una buena elección de los valores de los componentes que aparecen en la ecuación de  $\omega_p$  sin comprometer el valor de  $\omega_{z2}$ .

Por otro lado, en la ganancia del sistema aparecen los parámetros característicos del transistor  $\beta$  y  $R_b$ , pero se puede fijar mediante la elección de los valores de  $R_1$  y  $R_2$ . Por todo esto, es necesario un compromiso en la elección de los valores de componentes a la hora de calcular los parámetros frecuenciales y la ganancia del ecualizador.

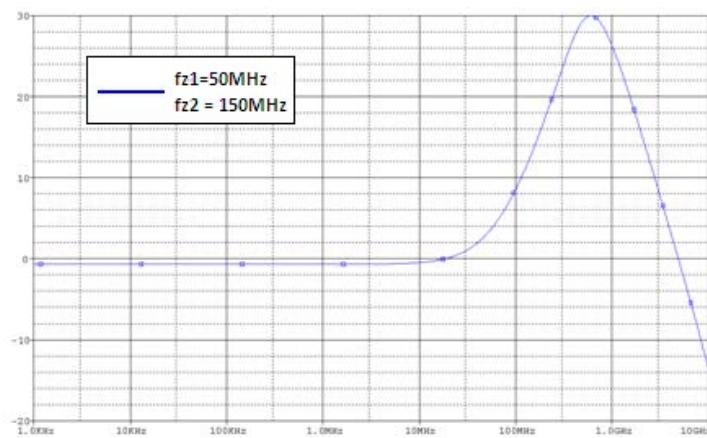

#### 4.4.2. Implementación del ecualizador BJT *pasive shunt peaking*

El transistor utilizado es el mismo que el utilizado en la estructura *active shunt peaking*, el transistor **NE662M04** de *California Eastern Laboratories*.

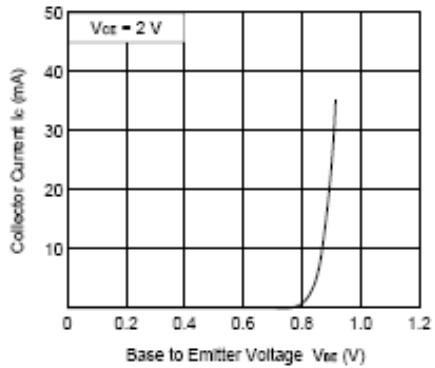

Para fijar el valor de la intensidad de base por los transistores se utiliza una resistencia ( $R$ ) entre  $V_{DD}$  y  $V_{in}$ . Para la elección de  $I_B$ , ya que la estructura lo permite, se polariza el transistor para que presente un consumo muy bajo, obteniendo una intensidad ( $I_C$ ) igual a 1 mA.

Para controlar el cero variable y el polo se ha optado por un condensador variable ya que las resistencias afectan a la ganancia del sistema. La ganancia depende de los elementos resitivos del circuito así como de los parámetros del transistor  $R_B$  y  $\beta$ , ecuación (22).