**Universidad**

Zaragoza

## Proyecto Fin de Carrera

# IMPLEMENTACIÓN DE UNA RED DE CONFORMADO DIGITAL DE HAZ PARA AGRUPACIONES DE ANTENAS DE FASE PROGRESIVA

Autor

Eduardo Perea Fernández

Director y ponente

Ismael Bel Albesa

Pedro Luis Carro Ceballos

Ingeniería de Telecomunicación / EINA

## *Resumen*

Debido a la presente demanda de recursos en la red de comunicaciones móviles surge la necesidad de dotar con mayor capacidad las actuales celdas de la red celular. En este contexto se plantea la evolución de las tradicionales antenas pasivas de estación base en nuevas antenas activas con importantes ventajas sobre las anteriores.

Actualmente la estación base para red móvil se compone de tres dispositivos, el equipo de procesado de datos en banda base, los encargados de convertir estos datos y adaptarlos a radiofrecuencia y las antenas emisoras/receptoras. Las antenas activas para estación base plantean la integración de los dos últimos en uno solo, mejorando así el ahorro energético y aportando flexibilidad para redimensionar la red móvil de manera remota.

Se propone un prototipo de transmisión/recepción de señales en dominio digital con conformado del haz de radiación. El prototipo, una vez se le conecte su correspondiente etapa analógica adaptadora y los elementos radiantes, permitirá al operador transmitir y recibir señales WCDMA sin tener que hacer uso de un equipo de radiofrecuencia que las convierta al dominio digital o analógico. Para ello es importante realizar un correcto procesado digital de la señal y la conversión entre ambos dominios, manejando de modo síncrono los componentes que participan en el proceso. El sistema recibirá señales analógicas desfasadas entre sí progresivamente. La señal será procesada digitalmente y se volverá a transmitir de manera analógica, conformando un haz de radiación con el ángulo de inclinación configurado digitalmente.

El proyecto permitirá desarrollar e implementar la base sobre la que se sustentan las antenas activas y evolucionar hacia una solución viable de cara al mercado, ubicándose dentro de los productos relacionados con antenas de telefonía móvil que tiene la empresa Telnet Redes Inteligentes.

## *Agradecimientos*

A Ismael, mi director de proyecto, por tener inmensa paciencia conmigo y mi *excelente* ortografía y redacción, ayudarme siempre sin reparos, enseñarme todo lo que está en su mano y su magistral diseño de placas ADC/DAC.

A Adrián, amo y señor de las FPGAs, por enseñarme todo lo que sé sobre el entorno Xilinx y actuar siempre como un oráculo de sabiduría. Este trabajo es tan mío como vuestro.

A Pedro, porque a pesar de tener un año con mil y una tareas ha tenido tiempo para mí. A toda la gente de Telnet por su gran trato y por prestarme su ayuda siempre que se lo he pedido. He aprendido muchísimo este año.

Por último y más importante a mis padres, Manuel e Inmaculada, por brindarme la educación que he recibido, sin duda lo que más valoro en el mundo, sin esperar nada a cambio.

Gracias.

# Índice general

|                                                                                  |             |

|----------------------------------------------------------------------------------|-------------|

| <b>Resumen</b>                                                                   | <b>III</b>  |

| <b>Agradecimientos</b>                                                           | <b>v</b>    |

| <b>Índice de figuras</b>                                                         | <b>xI</b>   |

| <b>Índice de cuadros</b>                                                         | <b>xIII</b> |

| <b>Abreviaturas</b>                                                              | <b>xv</b>   |

| <br>                                                                             |             |

| <b>1. Introducción</b>                                                           | <b>1</b>    |

| 1.1. Contexto del proyecto . . . . .                                             | 1           |

| 1.2. Escenario de trabajo . . . . .                                              | 2           |

| 1.3. Objetivo del proyecto . . . . .                                             | 4           |

| 1.4. Tareas a realizar . . . . .                                                 | 5           |

| 1.5. Herramientas utilizadas . . . . .                                           | 5           |

| 1.6. Organización de la memoria . . . . .                                        | 6           |

| 1.7. Planificación . . . . .                                                     | 7           |

| <b>2. Estado del arte</b>                                                        | <b>9</b>    |

| 2.1. Situación actual de las antenas pasivas para estación base . . . . .        | 9           |

| 2.2. Antenas Activas para BTS . . . . .                                          | 14          |

| 2.3. Estudio sobre las redes de conformado digital . . . . .                     | 15          |

| 2.4. Evolución del desarrollo en el ámbito de las BTS . . . . .                  | 15          |

| <b>3. Diseño del prototipo teórico</b>                                           | <b>17</b>   |

| 3.1. Teoría de arrays unidimensionales de antenas . . . . .                      | 17          |

| 3.2. Especificaciones de la unidad de conformado de haz . . . . .                | 19          |

| 3.2.1. Diseño de un array de antenas con elementos desfasados entre sí . . . . . | 21          |

| 3.2.2. Etapa RF previa a la unidad de conformado de haz . . . . .                | 22          |

| 3.3. Diseño de la unidad de conformado de haz . . . . .                          | 23          |

| 3.3.1. Etapa de conversión de la señal en dominio analógico a digital . . . . .  | 23          |

| 3.3.2. Etapa de conformado del haz de radiación en recepción . . . . .           | 26          |

| 3.3.2.1. Teoría de la aproximación a señal de banda estrecha . . . . .           | 27          |

|                                                                                                                        |               |

|------------------------------------------------------------------------------------------------------------------------|---------------|

| 3.3.2.2. Modelo matemático de la etapa de conformado de haz de radiación en recepción . . . . .                        | 28            |

| 3.3.3. Enlace de recepción del conformador de haz de radiación . . . . .                                               | 30            |

| 3.3.3.1. Obtención de tramas IQ a partir de la señal digital . . . . .                                                 | 30            |

| 3.3.3.2. Etapa de diezmado de tramas IQ de la señal digital . . . . .                                                  | 31            |

| 3.3.3.3. Filtrado con raíz de coseno realzado de las tramas IQ . . . . .                                               | 34            |

| 3.3.4. Enlace de transmisión del conformador de haz de radiación . . . . .                                             | 36            |

| 3.3.5. Etapa de conformado del haz de radiación en transmisión . . . . .                                               | 37            |

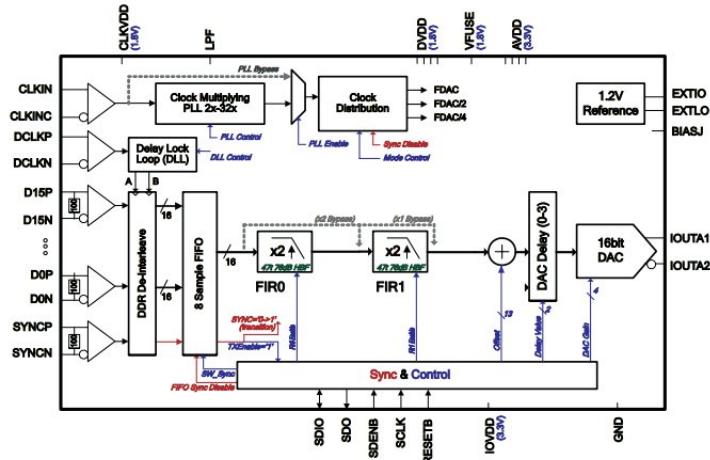

| 3.3.6. Etapa de conversión de la señal en dominio digital a analógico . . . . .                                        | 39            |

| <b>4. Simulación del conformador de haz de radiación</b>                                                               | <b>41</b>     |

| 4.1. Simulación del enlace de recepción con 1 solo elemento radiante . . . . .                                         | 42            |

| 4.1.1. Simulación del enlace de transmisión en conjunto con el de recepción con un solo elemento radiante . . . . .    | 46            |

| 4.2. Simulación del conformado de haz en recepción y transmisión . . . . .                                             | 47            |

| <b>5. Implementación de la red de conformado de haz</b>                                                                | <b>51</b>     |

| 5.1. Implementación de la conversión analógico-digital en el prototipo del enlace de recepción . . . . .               | 52            |

| 5.2. Implementación del enlace de recepción del conformador del haz de radiación para una entrada analógica . . . . .  | 56            |

| 5.3. Implementación del enlace de transmisión del conformador del haz de radiación para una salida analógica . . . . . | 59            |

| 5.4. Implementación de la conversión digital-analógica en el prototipo del enlace de transmisión . . . . .             | 61            |

| 5.5. Implementación del conformado de haz en transmisión y recepción del prototipo                                     | 63            |

| <b>6. Conclusiones y futuras mejoras del proyecto</b>                                                                  | <b>67</b>     |

| 6.1. Conclusiones . . . . .                                                                                            | 67            |

| 6.2. Futuras mejoras . . . . .                                                                                         | 69            |

| <br><b>A. Antenas Activas</b>                                                                                          | <br><b>73</b> |

| A.1. Contexto y situación de las antenas activas para estaciones base . . . . .                                        | 73            |

| A.2. Estructura de las antenas activas . . . . .                                                                       | 74            |

| A.3. Ventajas de las antenas activas . . . . .                                                                         | 76            |

| <br><b>B. El standard WCDMA</b>                                                                                        | <br><b>79</b> |

| B.1. Contexto sobre el que se sitúa el protocolo WCDMA . . . . .                                                       | 79            |

| B.1.1. Características del protocolo WCDMA . . . . .                                                                   | 79            |

| B.1.2. La capa física de WCDMA . . . . .                                                                               | 81            |

| <br><b>C. El protocolo CPRI</b>                                                                                        | <br><b>83</b> |

| C.1. Comparando los protocolos CPRI y OBSAI . . . . .                                                                  | 83            |

| C.2. Análisis del protocolo CPRI . . . . .                                                                             | 85            |

| C.2.1. Determinación del standard wireless a utilizar . . . . .                                                        | 85            |

| C.2.2. Estructura de la trama CPRI . . . . .                                                                           | 86            |

| C.2.3. Formato de los datos de salida CPRI . . . . .                                                                   | 87            |

|                                                              |            |

|--------------------------------------------------------------|------------|

| C.3. Uso del protocolo CPRI con FPGAs . . . . .              | 87         |

| <b>D. Muestreo en banda de paso</b>                          | <b>91</b>  |

| <b>E. Diseño y programación del microprocesador embebido</b> | <b>95</b>  |

| <b>F. Herramientas utilizadas.</b>                           | <b>101</b> |

| F.1. Software . . . . .                                      | 101        |

| F.2. Hardware: . . . . .                                     | 103        |

| <b>Bibliografía</b>                                          | <b>107</b> |

# Índice de figuras

|                                                          |    |

|----------------------------------------------------------|----|

| 1.1. Antena activa . . . . .                             | 1  |

| 1.2. Esquema de una red móvil . . . . .                  | 3  |

| 1.3. Esquema del prototipo . . . . .                     | 4  |

| 1.4. Diagrama de Gantt . . . . .                         | 7  |

| 2.1. Esquema RRU . . . . .                               | 10 |

| 2.2. Parche fractal . . . . .                            | 12 |

| 2.3. Concepto de downlink en RRU . . . . .               | 15 |

| 3.1. Array de elementos unidimensional . . . . .         | 18 |

| 3.2. Escenario de trabajo . . . . .                      | 20 |

| 3.3. Conformador del haz de radiación. . . . .           | 21 |

| 3.4. Etapa RF . . . . .                                  | 22 |

| 3.5. Conversión AD . . . . .                             | 23 |

| 3.6. Cuantificador uniforme . . . . .                    | 25 |

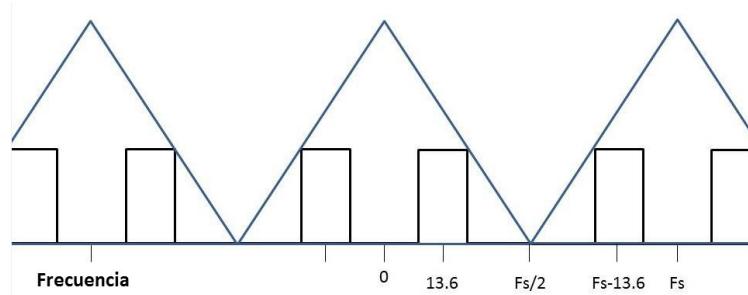

| 3.7. Frecuencia de muestreo . . . . .                    | 26 |

| 3.8. Conformador del haz en recepción . . . . .          | 26 |

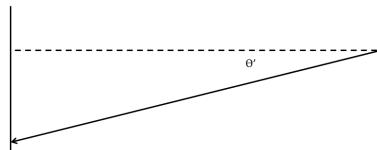

| 3.9. Haz de radiación desfasado incidente . . . . .      | 28 |

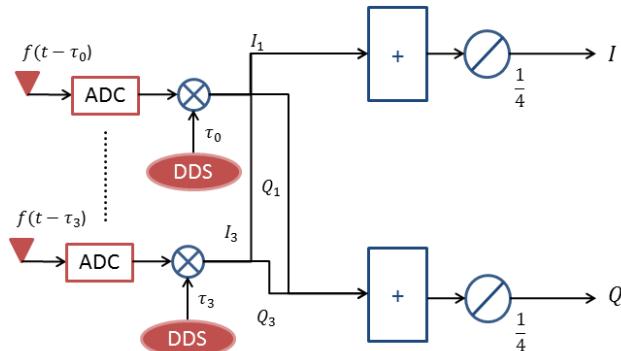

| 3.10. Multiplicación en cuadratura . . . . .             | 31 |

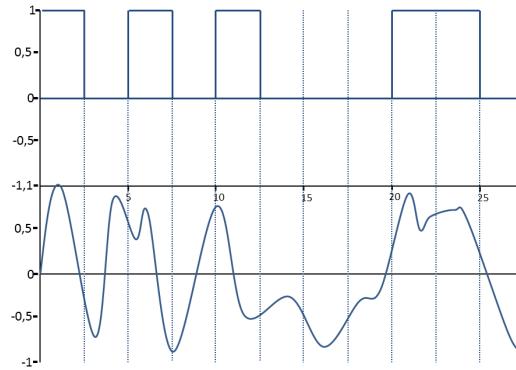

| 3.11. Señal digital teórica y real . . . . .             | 32 |

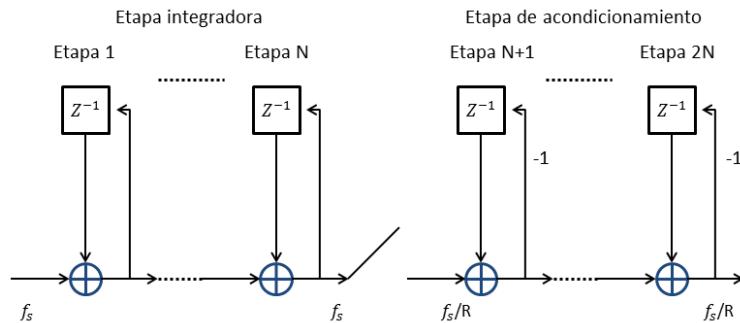

| 3.12. Diezmador CIC . . . . .                            | 32 |

| 3.13. Diezmado FIR lineal . . . . .                      | 33 |

| 3.14. Variación de la señal con ISI . . . . .            | 34 |

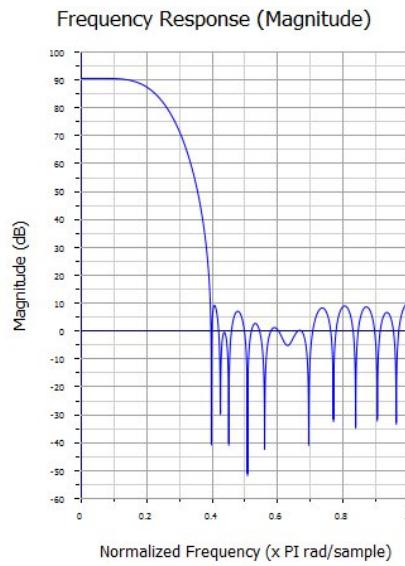

| 3.15. Respuesta frecuecnial filtro rcosre . . . . .      | 35 |

| 3.16. Enlace de transmisión teórico . . . . .            | 36 |

| 3.17. Equivalencia entre ángulos de incidencia . . . . . | 38 |

| 3.18. Conversor DAC tipo . . . . .                       | 40 |

| 4.1. Bloque simulación downlink . . . . .                | 43 |

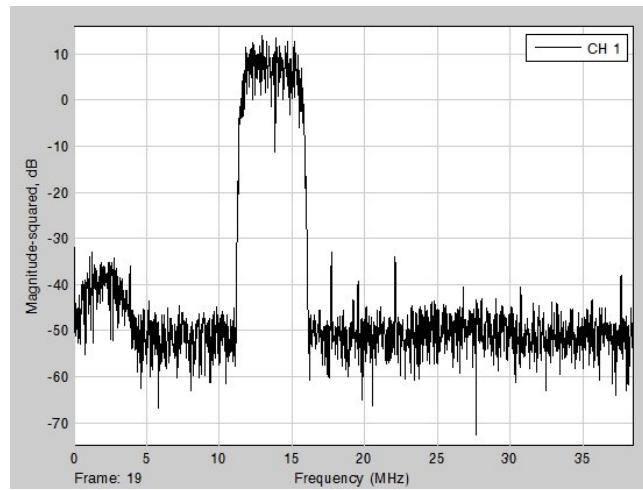

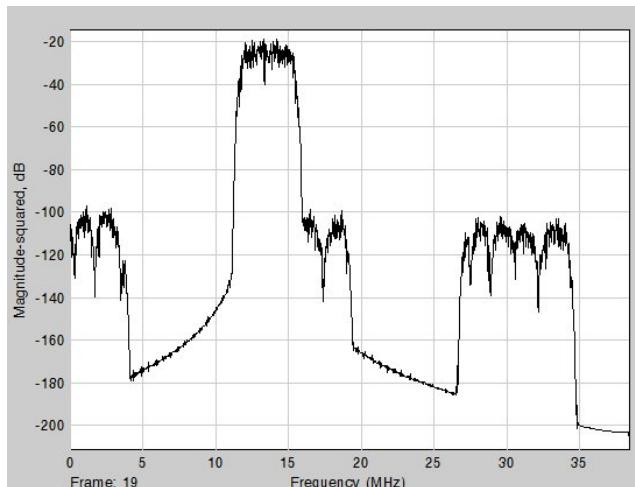

| 4.2. Señal WCDMA de entrada en simulación . . . . .      | 44 |

| 4.3. Salida DDC simulación . . . . .                     | 44 |

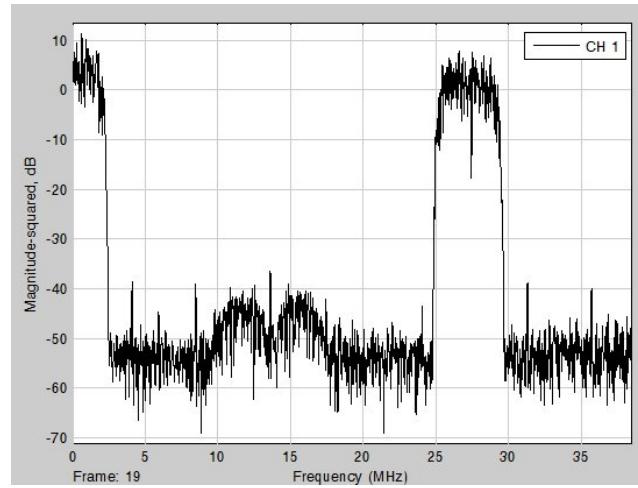

| 4.4. Salida filtro prediezmodo en simulación . . . . .   | 45 |

| 4.5. Salida Rcosre en simulación . . . . .               | 45 |

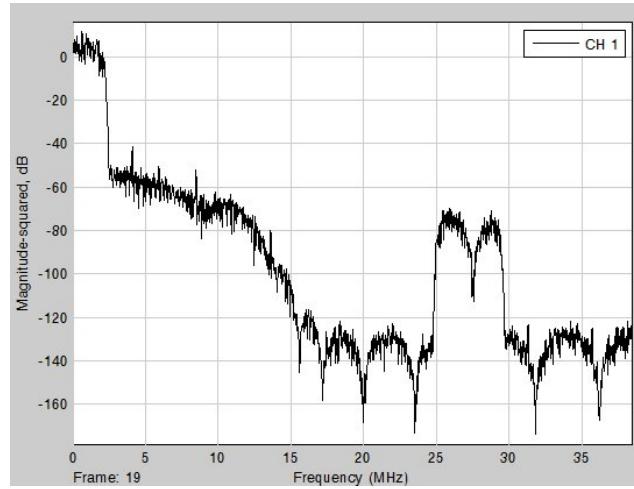

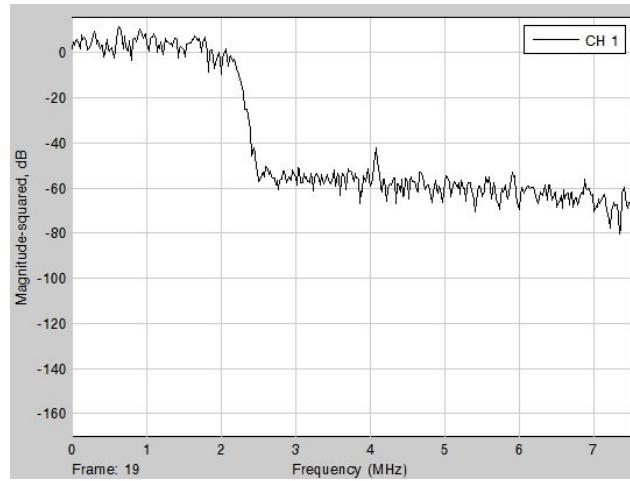

| 4.6. Salida simulación . . . . .                         | 46 |

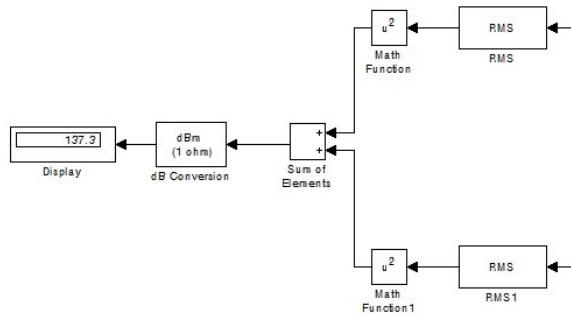

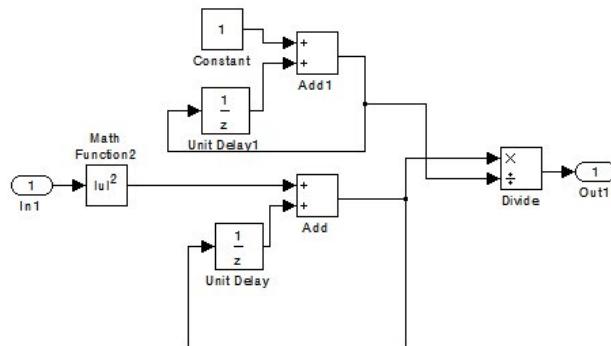

| 4.7. Bloque de medición de potencia . . . . .            | 48 |

| 4.8. Bloque de medición de potencia 2 . . . . .          | 48 |

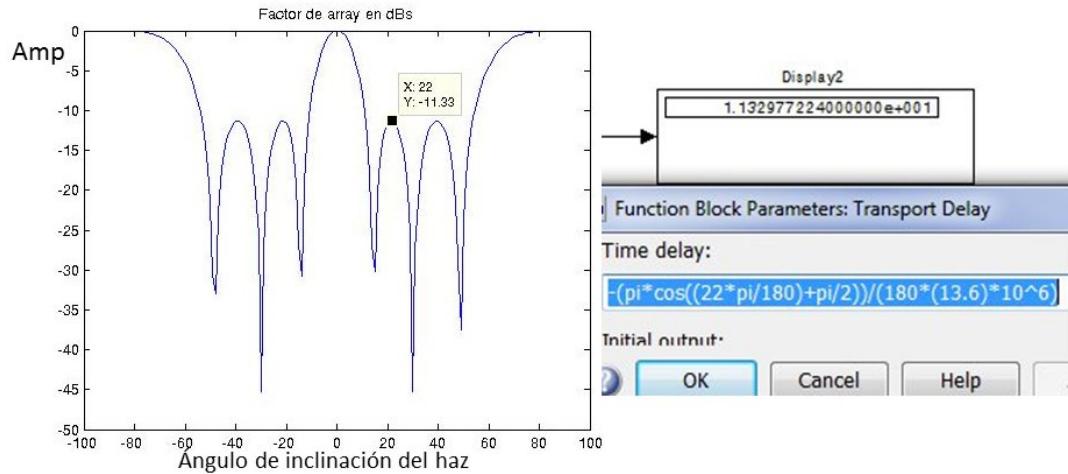

| 4.9. FA Matlab . . . . .                                 | 49 |

| 4.10. Sistema Simulink . . . . .                         | 49 |

|                                                                     |    |

|---------------------------------------------------------------------|----|

| 4.11. Tilts Microwave Office . . . . .                              | 50 |

| 5.1. Placa de evaluación . . . . .                                  | 51 |

| 5.2. ADC Microhemir . . . . .                                       | 52 |

| 5.3. Muestreo no válido ADC . . . . .                               | 53 |

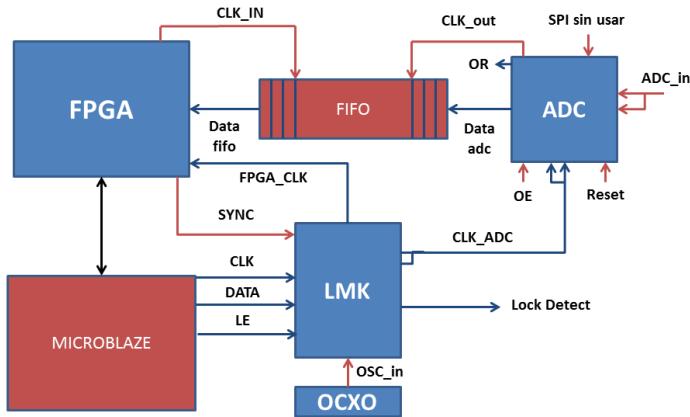

| 5.4. Esquema completo de la conversión ADC . . . . .                | 55 |

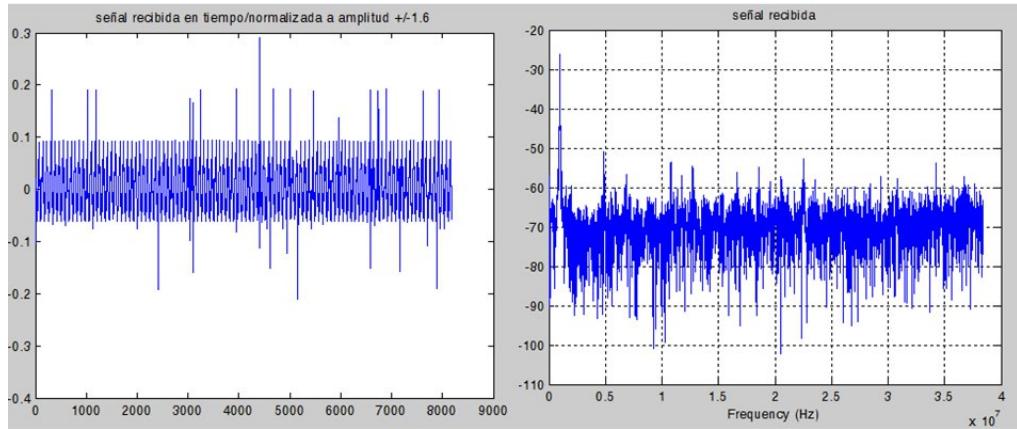

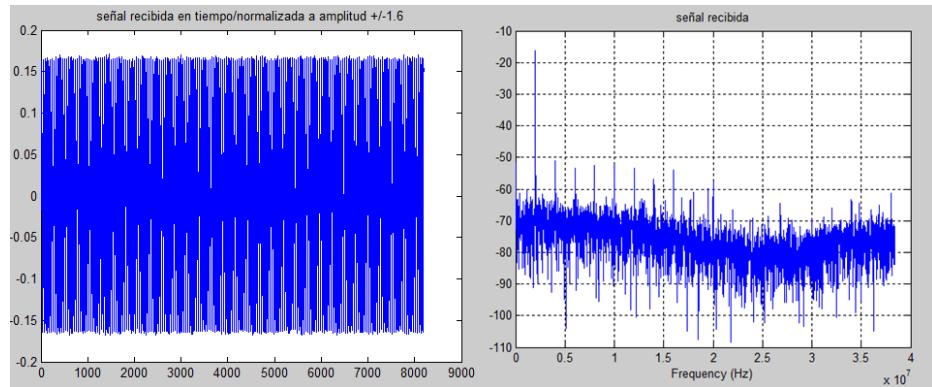

| 5.5. Señal muestreada . . . . .                                     | 55 |

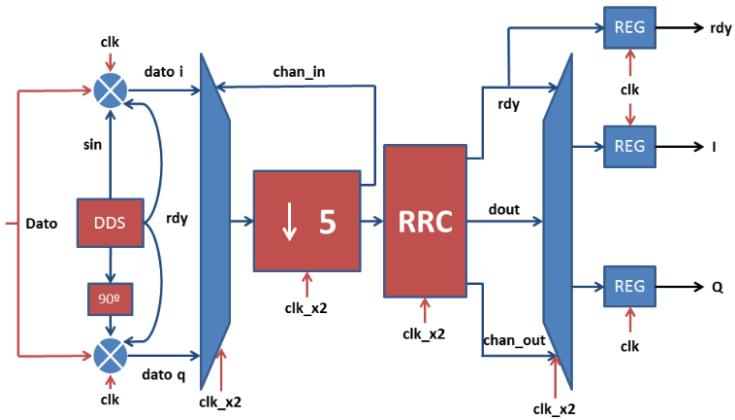

| 5.6. Esquema de la implementación del enlace de recepción . . . . . | 56 |

| 5.7. Filtro diezmador . . . . .                                     | 58 |

| 5.8. Esquema de la implementación del enlace de recepción . . . . . | 59 |

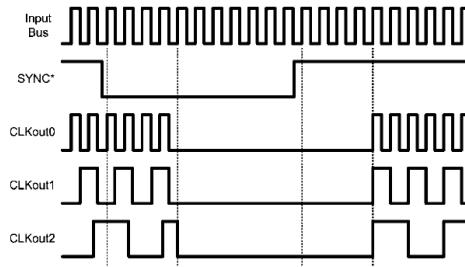

| 5.9. Cronograma . . . . .                                           | 61 |

| 5.10. Conversor DAC . . . . .                                       | 62 |

| 5.11. Hardware del prototipo final . . . . .                        | 64 |

| 5.12. Esquema del conformador de haz en FPGA . . . . .              | 65 |

| 6.1. Tapping de amplitud . . . . .                                  | 70 |

| A.1. Evolución de las BTS . . . . .                                 | 74 |

| A.2. Esquema interior de una antena activa . . . . .                | 75 |

| A.3. Beneficios del tilting en antenas activas. . . . .             | 77 |

| A.4. Autoreparación . . . . .                                       | 78 |

| B.1. Esquema WCDMA . . . . .                                        | 80 |

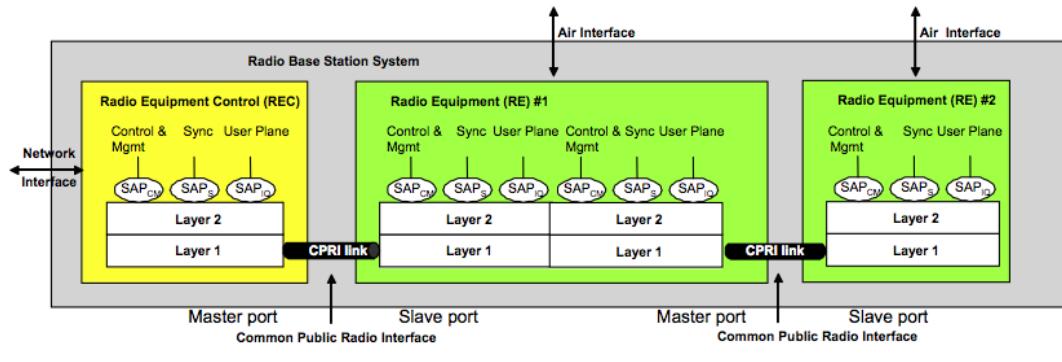

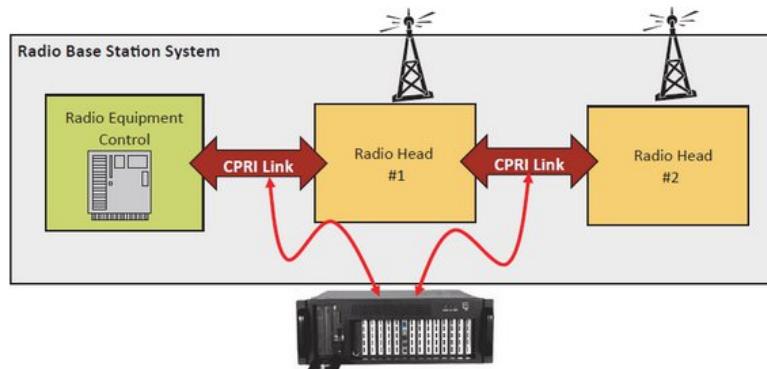

| C.1. Esquema CPRI . . . . .                                         | 85 |

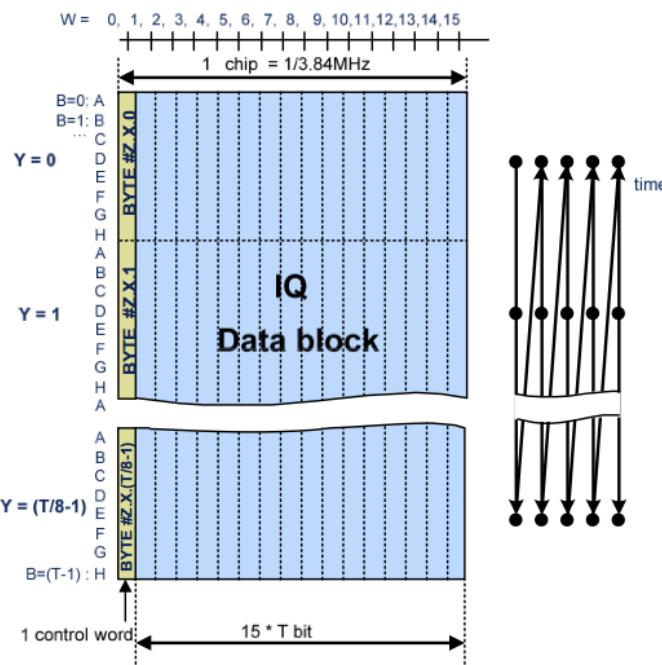

| C.2. Trama CPRI . . . . .                                           | 86 |

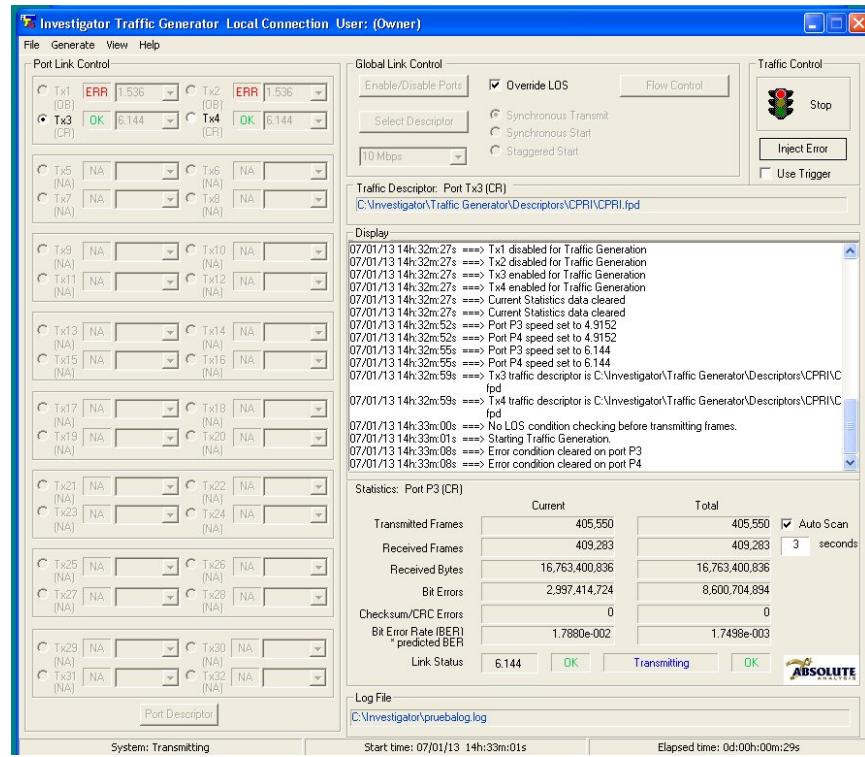

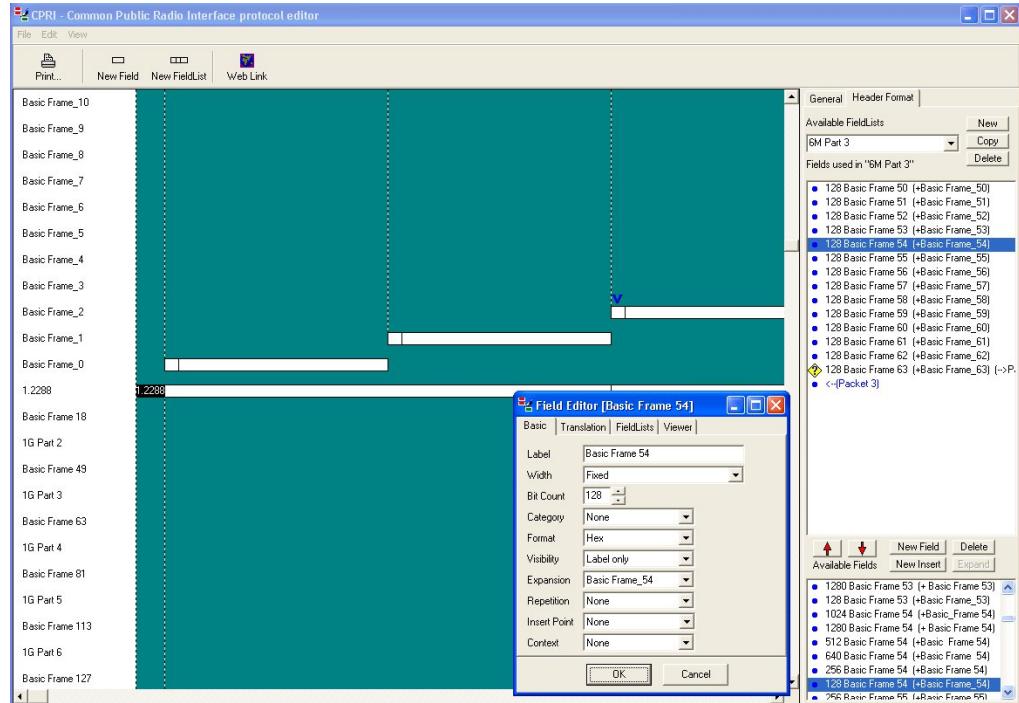

| C.3. Investigator . . . . .                                         | 88 |

| C.4. Generador de tráfico . . . . .                                 | 89 |

| C.5. Editor de protocolos . . . . .                                 | 90 |

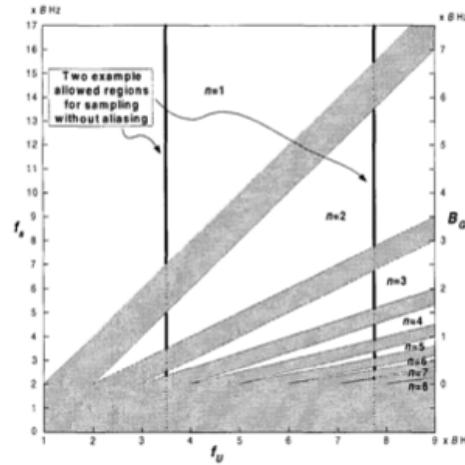

| D.1. Regiones de aliasing . . . . .                                 | 92 |

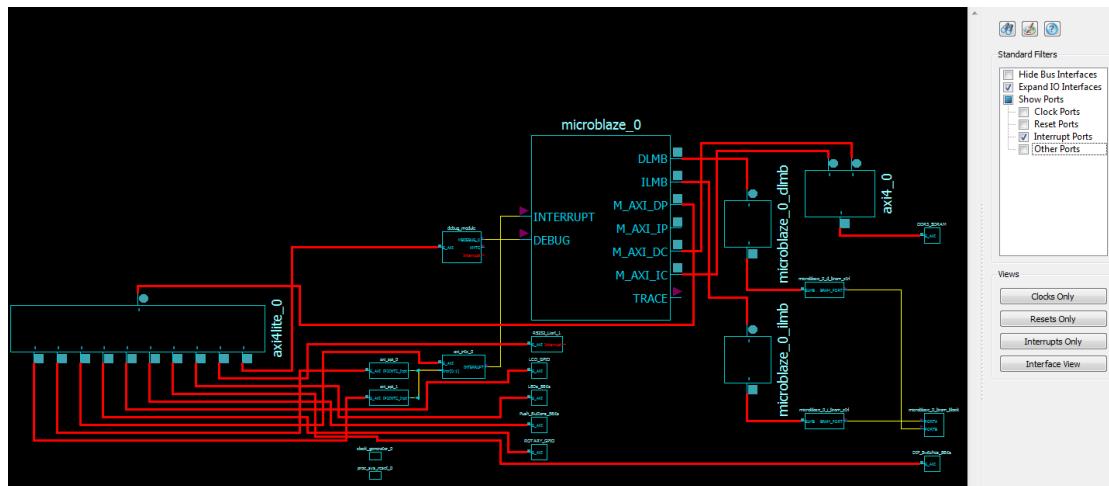

| E.1. Esquema del microprocesador . . . . .                          | 96 |

| E.2. Cronograma SPI LMK03001c . . . . .                             | 98 |

# Índice de cuadros

|                                                                                         |    |

|-----------------------------------------------------------------------------------------|----|

| 1.1. Cuadro de anexos . . . . .                                                         | 7  |

| 3.1. Retardos . . . . .                                                                 | 39 |

| 6.1. Comparativa de los posibles filtros a utilizar en el bucle de procesado digital. . | 69 |

| A.1. Pérdidas de potencia en antenas activas vs antenas pasivas . . . . .               | 77 |

# Abreviaturas

|              |                                           |

|--------------|-------------------------------------------|

| <b>PFC</b>   | Proyecto Fin de Carrera                   |

| <b>BBU</b>   | Base Band Unit                            |

| <b>RRU</b>   | Remote Radio Unit                         |

| <b>MIMO</b>  | Multiple Input Multiple Output            |

| <b>WCDMA</b> | Wide Code Division Multiple Access        |

| <b>TDMA</b>  | Time Division Multiple Access             |

| <b>FDMA</b>  | Frequency Division Multiple Access        |

| <b>MSC</b>   | Mobile Switching Center                   |

| <b>RF</b>    | Radio Frequency                           |

| <b>CPRI</b>  | Common Public Radio Interface             |

| <b>OBSAI</b> | Open Base Station Architecture Initiative |

| <b>ORI</b>   | Open Radio Interface                      |

| <b>FPGA</b>  | Field Programmable Gate Array             |

| <b>BW</b>    | Band Width                                |

| <b>ADC</b>   | Analog Digital Converter                  |

| <b>ISI</b>   | Inter Symbolic Interference               |

| <b>DAC</b>   | Digital Analog Converter                  |

| <b>HSPA</b>  | High Speed Packet Access                  |

| <b>LTE</b>   | Long Term Evolution                       |

| <b>GSM</b>   | Global System for Mobile communications   |

| <b>UE</b>    | User Equipment                            |

| <b>FSTD</b>  | Frequency Switched Transmit Diversity     |

| <b>SON</b>   | Self Organized Network                    |

| <b>CFR</b>   | Crest Factor Reduction                    |

| <b>RET</b>   | Remote Electrical Tilt                    |

|               |                                            |

|---------------|--------------------------------------------|

| <b>UMTS</b>   | Universal Mobile Telecommunications System |

| <b>RNC</b>    | Radio Network Controller                   |

| <b>QoS</b>    | Quality of Service                         |

| <b>ARQ</b>    | Automatic Repeat reQuest                   |

| <b>PSTN</b>   | Public Switched Telephone Network          |

| <b>FDD</b>    | Frequency Division Duplexing               |

| <b>TDD</b>    | Time Division Duplexing                    |

| <b>OSI</b>    | Open System Interconnection                |

| <b>UTRAN</b>  | UMTS Terrestrial Radio Access Control      |

| <b>OSI</b>    | Open System Interconnection                |

| <b>SFP</b>    | Small Form-factor Pluggable transceptor    |

| <b>BER</b>    | Bit Error Rate                             |

| <b>DDR</b>    | Dual Data Rate                             |

| <b>DDC</b>    | Digital Down Conversion                    |

| <b>DUC</b>    | Digital Up Conversion                      |

| <b>SNR</b>    | Signal to Noise Ratio                      |

| <b>CRC</b>    | Cyclic Redundancy Check                    |

| <b>FMC</b>    | FPGA Mezzanine Card                        |

| <b>BTS</b>    | Base Transceiver Station                   |

| <b>FEC</b>    | Forward Error Correction                   |

| <b>RE</b>     | Radio Equipment                            |

| <b>REC</b>    | Radio Equipment Control                    |

| <b>BPSK</b>   | Binary Phase Shift Keying                  |

| <b>QPSK</b>   | Quadrature Phase Shift Keying              |

| <b>OpEx</b>   | Operational Expenditures                   |

| <b>CapEx</b>  | Capital Expenditures                       |

| <b>FIFO</b>   | First In First Out                         |

| <b>SERDES</b> | SERializer/DESerializer                    |

| <b>MSB</b>    | Most Significant Bit                       |

| <b>LSB</b>    | Less Significant Bit                       |

| <b>OFDM</b>   | Orthogonal Frequency Division Multiplexing |

# Capítulo 1

## Introducción

### 1.1. Contexto del proyecto

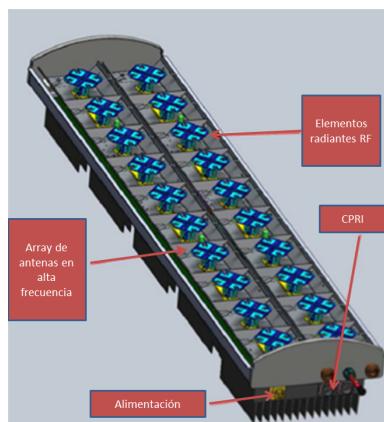

Este PFC ha sido realizado en la empresa **TELNET Redes Inteligentes** [1] como uno de sus proyectos de I+D+i, iniciando el desarrollo de antenas activas (Fig 1.1). Se ubica dentro de la sección de antenas para estación base evaluando una posible solución que ofrecer como producto final al cliente. Ofrecerá al operador una red más versátil y simple de diseñar, pudiéndose realizar de una manera escalada y reubicándose según los requisitos. Para ello modificará las diferentes inclinaciones del haz de radiación variando el área cubierta por la antena y pudiendo distribuir la capacidad entre áreas en función de la demanda.

---

FIGURA 1.1: Concepto de antena activa.

El proyecto pretende sentar las bases para un futuro desarrollo de esta antena diseñando, simulando e implementando un prototipo funcional de las tareas básicas a realizar, posibilitando el que en el futuro se continúe con un prototipo completo sobre los principios que aquí se describen.

El prototipo realizará las funciones de recepción, tratamiento y transmisión de la señal digital, el conformado del haz de radiación y las conversiones entre dominios digital y analógico necesarias. La señal digital viajará en forma de tramas **IQ** (fase y cuadratura) desde la estación base entramadas bajo alguno de los múltiples protocolos destinados a estandarizar las comunicaciones entre la **BBU** (BaseBand Unit) y la **RRU** (Remote Radio Unit).

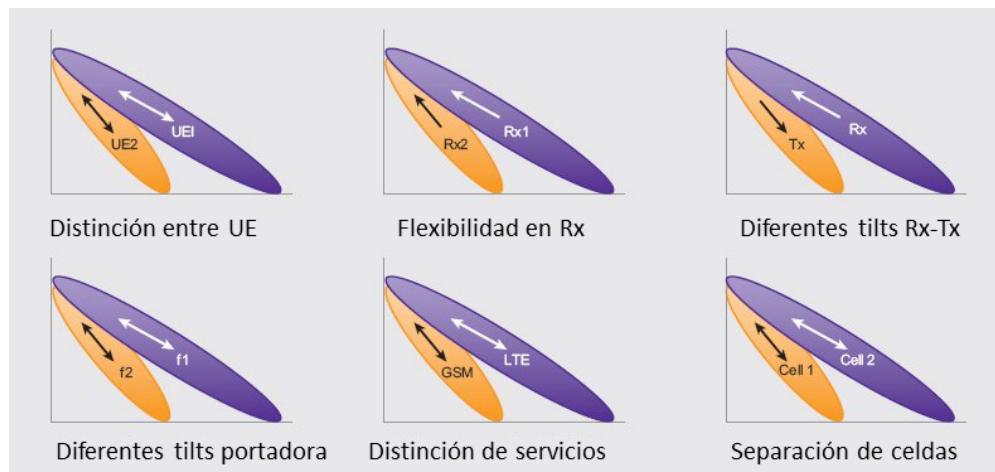

La red de conformado permite controlar la señal aplicada a cada elemento radiante previo paso por una etapa de adaptación en radiofrecuencia. La señal es procesada por cada una de las ramas del sistema, una por cada elemento transmisor/receptor. De este modo se abre un abanico de posibilidades de cara a las nuevas exigencias del mercado. Para más información sobre las antenas activas consultar el anexo [A](#).

El resultado final del proyecto servirá para estudiar la viabilidad del desarrollo de un producto comercial en cuyo caso podría formar la base de una antena de más características, MIMO (Multiple Input Multiple Output), múltiples arrays, auto ajuste etc...

## 1.2. Escenario de trabajo

Para entender el escenario en el que se ubica el proyecto es importante definir la estructura actual en las comunicaciones móviles.

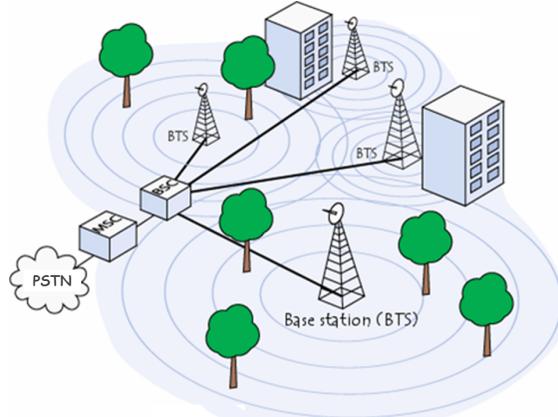

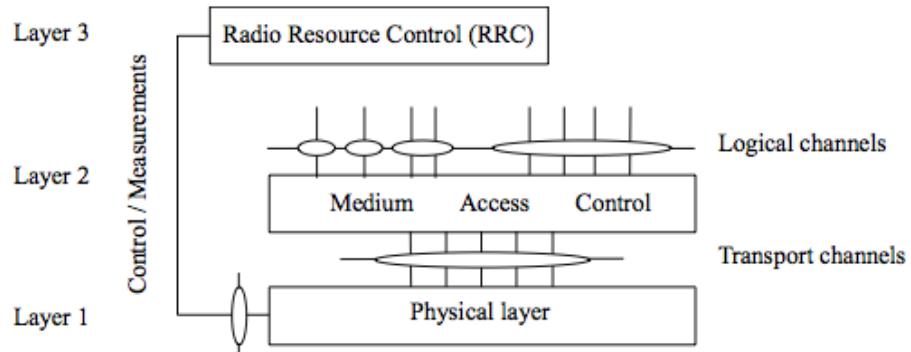

La red de comunicaciones móviles (Fig [1.2](#)) está compuesta de celdas que dan cobertura a diferentes dispositivos móviles que se comunican entre sí [\[2\]](#). En el caso de este proyecto la tecnología de acceso al medio es **WCDMA** (Wideband Code Division Multiple Access) (Véase el anexo [B](#)), protocolo basado en la diferenciación por código. Este standard presenta mayor eficiencia espectral que otros sistemas menos complejos como son TDMA (Time Division Multiple Access) o FDMA (Frequency Division Multiple Access), permitiendo transmitir con mayores tasas binarias y aprovechando el espectro de frecuencia de manera más óptima. El

dispositivo de usuario se conecta a la estación base y ésta al **MSC** (Mobile Switching Center), encargado de conectar el dispositivo de usuario a la **PSTN** (Public Switched Telephone Network).

FIGURA 1.2: Esquema general de una red de comunicaciones móviles.

La BTS (Base Transceiver Station) tiene se compone de una BBU, las RRUs y antenas encargadas de radiar en RF (Radiofrecuencia). Cada BBU puede manejar varias RRU enviando la información digital en banda base por medio de fibra óptica. La RRU recibe esta información entramada mediante protocolos como pueden ser **CPRI** (Common Public Radio Interface)[3] u **OBSAI** (Open Base Station Architecture Initiative)[4](véase el anexo C) y se encarga de desentramarla, realizar el procesado digital y convertirla a señal analógica. Una vez en dominio analógico debe aplicarle un procesado de adaptación en una etapa RF donde la señal se verá amplificada en potencia y desplazada a la frecuencia que opera la red. De este modo, la señal estará lista para ser transmitida por la antena pasiva. En recepción, el proceso actúa de manera inversa, la señal radiada es recibida por la antena pasiva en la frecuencia de la red, se transmite a la RRU donde es acondicionada, tanto en amplitud como en frecuencia, convertida a dominio digital y desplazada a banda base. La señal digital en banda base es transmitida a la BBU donde es gestionada para ser transmitida hacia la red pública.

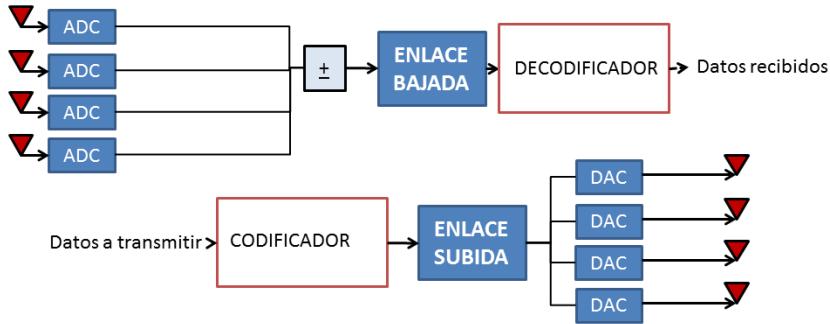

Definido el escenario sobre el que se ubica el proyecto, el sistema que se propone (Fig 1.3), una vez puesto en conjunto con una etapa en radiofrecuencia y los elementos radiantes, realiza las funciones descritas por la RRU y la antena pasiva en un solo dispositivo. Abarca en recepción desde la señal analógica en frecuencia intermedia hasta la obtención de los paquetes de información IQ en banda base. En transmisión se parte de los paquetes IQ ya desentramados de

la señal óptica bajo protocolo CPRI, hasta la construcción de la señal que se desea transmitir en dominio analógico en la misma frecuencia intermedia.

FIGURA 1.3: Esquema conceptual del prototipo conformador del haz de radiación.

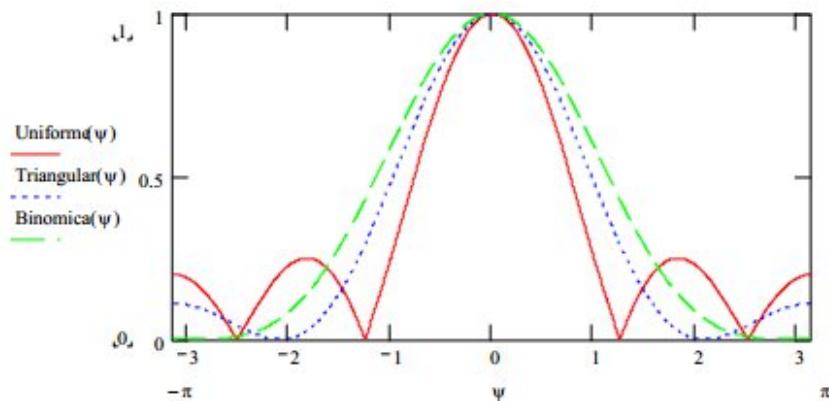

Además, se realizará la recepción de la señal en las entradas del prototipo de forma simultanea, estando desfasadas progresivamente entre sí y la transmisión de la señal por sus múltiples salidas con los desfases progresivos oportunos para lograr el grado de inclinación en el haz de radiación deseado. Otra técnica para variar la forma del haz de radiación consiste en aplicar una graduación (*tapping*) en la amplitud de la señal con la que se alimentan los elementos radiantes de la antena, creando diferentes patrones del diagrama de radiación.

### 1.3. Objetivo del proyecto

El objetivo principal del proyecto es el diseño, simulación e implementación de un sistema de transmisión y recepción digital con conformado del haz de radiación para antenas activas. Éste será capaz de realizar las siguientes tareas:

- Recibir y transmitir simultáneamente una señal WCDMA por varios elementos radiantes.

- Realizar una correcta demodulación de la señal digital para conseguir los datos transmitidos en forma de tramas IQ.

- La aplicación de diferentes algoritmos de procesado de la señal digital que la adapten para su correcta recepción y transmisión.

- Conocido el ángulo de inclinación del haz de radiación deseado, aplicar los desfases pertinentes a cada una de las señales de los elementos radiantes para conseguir el conformado de haz.

- Implementación de todas estas tareas en un sistema de procesamiento digital en tiempo real y de manera síncrona controlado por una **FPGA** (Field Programmable Gate Array).

- Manejo de periféricos externos a la FPGA en la placa de prototipado mediante un microprocesador *embebido*.

#### 1.4. Tareas a realizar

Para la correcta realización de un prototipo que sea funcional y útil se realizarán las siguientes tareas:

I **Estado del arte:** Realizar un estudio de las soluciones presentes en las estaciones base y de todas las funcionalidades y posibilidades que pueden ofrecer dispositivos con las características de las antenas activas respecto de las actuales.

II **Diseño teórico:** Diseñar en primera instancia el sistema completo para estudiar el posterior aprovisionamiento de componentes y modelar teóricamente cada uno de los bloques (filtros, diezmadores etc...) como base para su implementación.

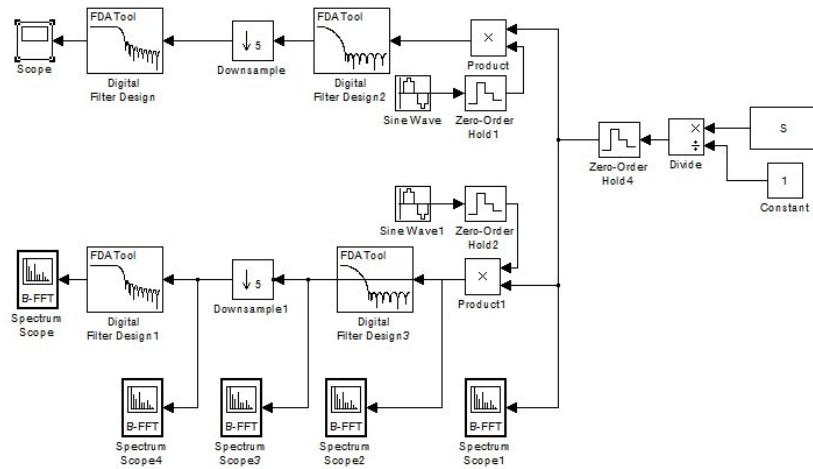

III **Simulación:** Simulación del sistema por bloques para identificar y corregir posibles fallos de diseño además de comprobar el procesado de la señal a lo largo del circuito.

IV **Estudio de la arquitectura:** Familiarizarse con la arquitectura de cada uno de los componentes sobre los que se va a realizar la implementación final.

V **Implementación:** Implementación, puesta en marcha y verificación del funcionamiento del sistema real con señales WCDMA reales analógicas bajo un hardware específico para su test.

#### 1.5. Herramientas utilizadas

Para la realización de este PFC se han usado varias herramientas de software y componentes hardware. Una completa descripción de ellos queda documentada en el anexo F. Aquí se describen las más importantes:

- Para la generación y captura de tramas de CPRI se hizo uso del equipo **Absolute Analysis Investigator** con su correspondiente conjunto de programas [5].

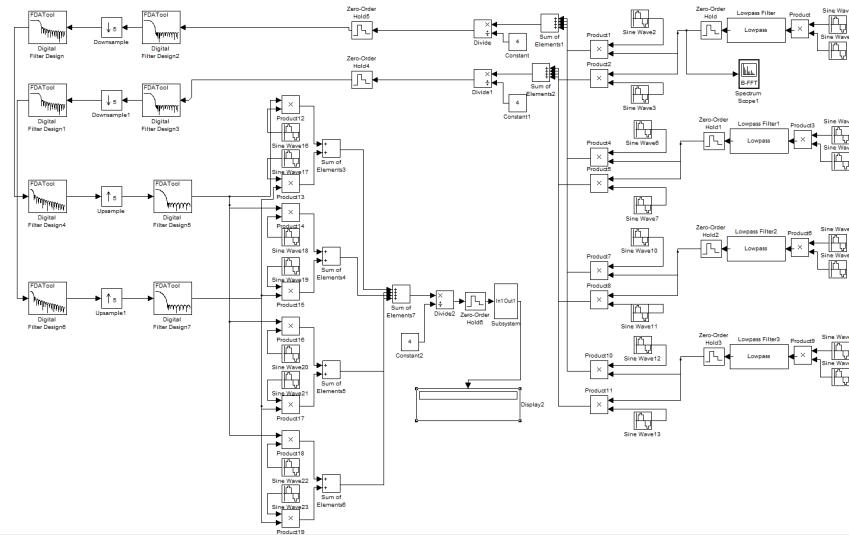

- La simulación del sistema completo se ha realizado con la herramienta **Simulink** de Mathworks [6].

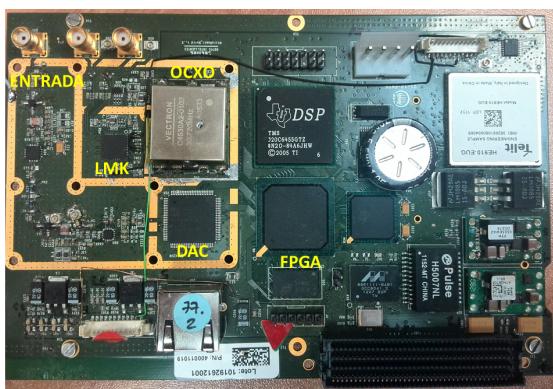

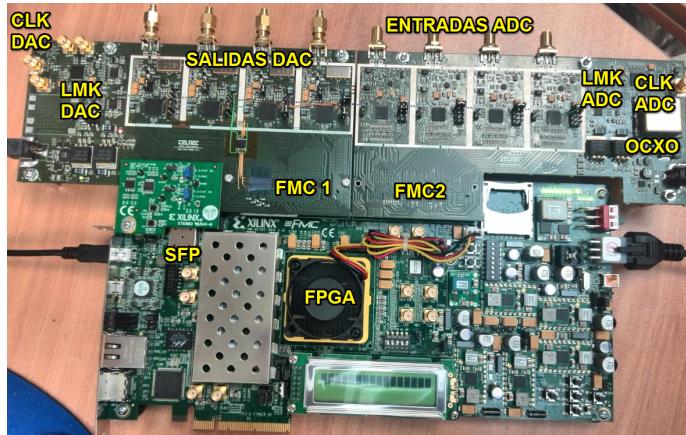

- El trabajo con FPGA y el microprocesador embebido se ha hecho mediante las herramientas de Xilinx **ISE** [7]. Los programas **ISE project** y **Planahead** se utilizaron para programar el código en Verilog, **XPS** en el diseño del microprocesador, **Impact** para la comunicación con las diferentes placas, **Isim** y **ModelSim** en la simulación de los códigos, **Chipscope** para la monitorización de las señales dentro de la FPGA. En el apartado de hardware se usó las placas de desarrollo **Microhemir** de TELNET Redes Inteligentes [8] con la FPGA Spartan 6 de Xilinx y la placa de evaluación **VC707** de Xilinx en conjunto con las FMC (FPGA Mezzanine Card) **DAC/ADC Eval Board** fabricadas por TELNET Redes Inteligentes.

- **Matlab** para realizar comprobaciones de las señales trabajadas en las fase de test y **Matlab Filter Design Tool** en la obtención de coeficientes de filtros dados unos parámetros de diseño [6].

- La creación y edición de código se realizó conjuntamente con los programas **Sublime Text 3** y **Notepad++**.

## 1.6. Organización de la memoria

La memoria se divide en una parte principal que explica los aspectos más importantes del desarrollo del PFC y una segunda parte de anexos orientada a aquel contenido que se considera complementario para la comprensión del proyecto.

En la primera, se realizará un repaso al estado del arte sobre el campo en el que se sitúa el proyecto y de la situación actual. Sus tres etapas principales de diseño, simulación e implementación finalizando con unas conclusiones finales y posibles desarrollos de cara al futuro. La segunda parte de la memoria se compone de los distintos anexos que se han generado a lo largo del proyecto para complementar con más profundidad la comprensión de éste. En el siguiente cuadro (Cuadro 1.1) aparecen listados según su orden de aparición.

| Anexo | Contenido                                          |

|-------|----------------------------------------------------|

| A     | Antenas Activas                                    |

| B     | El standard WCDMA                                  |

| C     | El protocolo CPRI                                  |

| D     | Muestreo en banda de paso                          |

| E     | Diseño y programación del microprocesador embebido |

| F     | Herramientas utilizadas                            |

CUADRO 1.1: Cuadro de anexos

## 1.7. Planificación

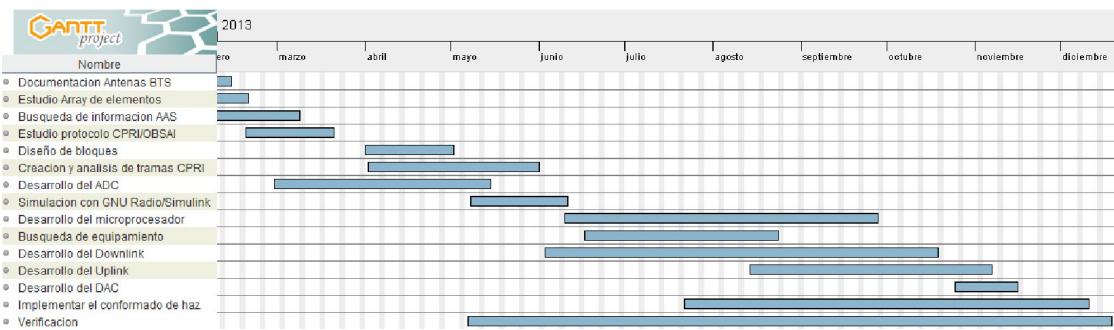

Una correcta planificación de las tareas a realizar resultará de gran utilidad para la fijación de plazos y tener una visión global del proyecto al inicio del mismo. En este caso, dado que el proyecto está enfocado en la investigación y el desarrollo, la planificación es una referencia que puede verse modificada debido a los imprevistos que puedan surgir.

La clasificación de tareas servirá para priorizar unas tareas sobre otras y ordenarlas en el tiempo. Los criterios para la división de tareas se tomaron en función de la documentación, análisis y diseño del sistema, implementación del mismo y verificación de errores. Las tareas en las que se dividió el proyecto se muestran en la siguiente figura (Fig 1.4):

FIGURA 1.4: Diagrama de Gantt.

## Capítulo 2

### Estado del arte

#### 2.1. Situación actual de las antenas pasivas para estación base

Para poder trabajar sobre una antena para estación base es necesario definir su estructura, funciones y evolución, la cual atiende a las peticiones de ancho de banda y capacidad por parte de los usuarios de la red móvil. Satisfacer estas demandas requiere implementar nuevas tecnologías espectralmente más eficientes como HSPA (High Speed Packet Access) o LTE (Long Term Evolution) e introducir nuevas bandas de frecuencia para incrementar el ancho de banda disponible dentro del espectro, con más canales y portadoras. Además, se debe de seguir prestando servicio a las tecnologías ya asentadas de segunda y tercera generación sin empeorar sus prestaciones.

La estructura de las actuales BTS se compone de tres elementos: BBU, RRU y antena pasiva. La BBU gestiona toda la estación base tramitando las llamadas entrantes y salientes de los equipos que operan en el área que controla. Una misma BBU puede dar soporte a varias RRU, recibiendo la señal en banda base de éstas en forma de tramas IQ. Las tramas se transmiten por medio de fibra óptica encapsuladas bajo los protocolos CPRI u OBSAI. Se establece el nexo de unión entre usuario y MSC a la vez que controla el procesado de la señal en banda base, el mantenimiento de todo el sistema y la generación de señal de reloj sobre la que se sincronizan todas las RRU.

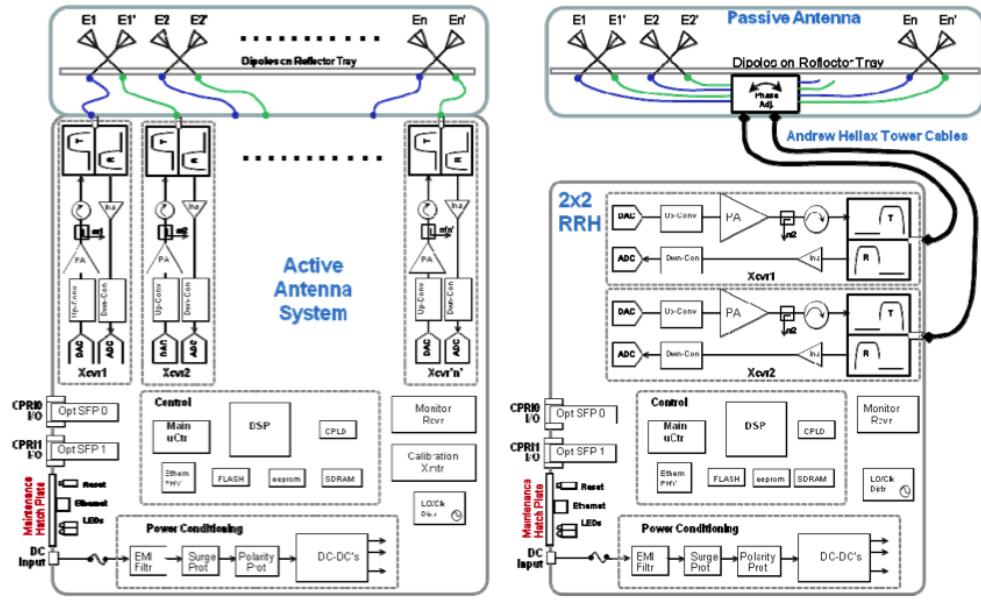

La RRU (Fig 2.1) acondiciona la señal para que la antena pasiva pueda realizar su transmisión. Para ello realiza las funciones principales de procesamiento de la señal digital recibida de la BBU, conversión de la señal digital al dominio analógico, traslación a la frecuencia de portadora

de la red y amplificación. Sus características pueden diferir en base al número de portadoras y bandas de frecuencia que soporta.

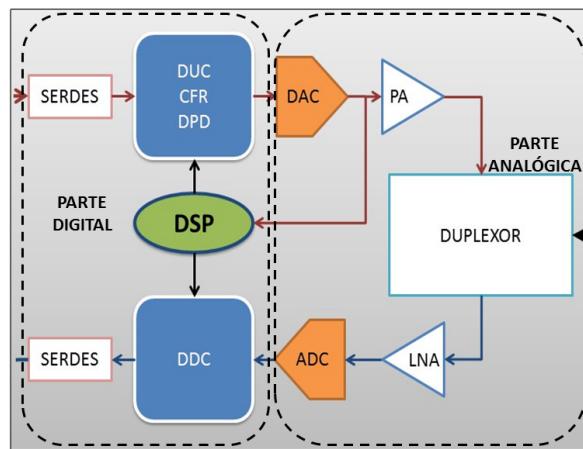

La estructura de la RRU consta de una etapa de procesado digital y de otra en RF. A la entrada de la etapa digital se ubica uno o más puertos SERDES (Serializer/Deserializer) para la recepción/transmisión de la señal con la BBU en modo síncrono. Posteriormente, en transmisión, el bloque de procesado digital se compone de una etapa DUC (Digital Upconversion), un sistema CFR (Crest Factor Reduction) y otro DPD (Digital Predistortion) haciendo uso de un DSP (Digital Signal Processing). En recepción el sistema es menos complejo, realizando la DDC (Digital Downconversion) de la señal en frecuencia intermedia procedente de la etapa RF.

Al inicio del procesado digital una etapa analógica en RF está compuesta por un LNA (Low Noise Amplifier) utilizado para la recepción de los datos. Éstos amplifican la señal a los niveles necesarios para que sea procesada por la etapa digital, introduciendo el menor ruido posible. Por otro lado, al final del procesado digital se utiliza una etapa RF con amplificadores PA (Amplificador de Potencia) para su uso en la transmisión de datos puesto que el objetivo primario es amplificar la potencia de la señal lo máximo posible. La etapa previa a la antena se compone de un duplexor encargado de separar las señales de transmisión y recepción. La señal es transmitida y recibida por el elemento radiante.

FIGURA 2.1: Esquema de bloques típico de una RRU.

En un principio la RRU se situaba en el mismo emplazamiento que la BBU transmitiendo la señal de forma analógica a las antenas pasivas por cable coaxial. Dado que las pérdidas en cable coaxial son mayores que las pérdidas en fibra óptica, la tendencia en la evolución de las

BTS consiste en aproximar la RRU cada vez más a la antena de emisión/recepción. En este sentido, la integración de los dos dispositivos en uno es el paso final.

La antena pasiva se compone de un radomo que actúa como protector de la antena, fabricado en materiales que alteran lo menos posible la señal radiada. Actualmente, acostumbra a usarse radomos de resina con fibras de vidrio que proporcionan altos valores de rigidez con espesores muy pequeños. Internamente, un bastidor metálico de aluminio hace las funciones de plano de masa, aislando los elementos radiantes de los cables.

En la parte trasera de la antena se disponen los cables de alimentación que distribuyen la señal a los elementos radiantes y el desfasador. Este último, se compone de estructuras que distribuyen la señal por medio de líneas de transmisión y crean desfases progresivos en las señales aplicadas a los elementos radiantes para conformar un haz de radiación con diferentes ángulos de inclinación. El mecanismo para realizar el desfase suele estar patentado y difiere en función del fabricante.

En la parte frontal se disponen los elementos radiantes. Éstos acostumbran a ser dipolos o parches fabricados en materiales conductores como el aluminio.

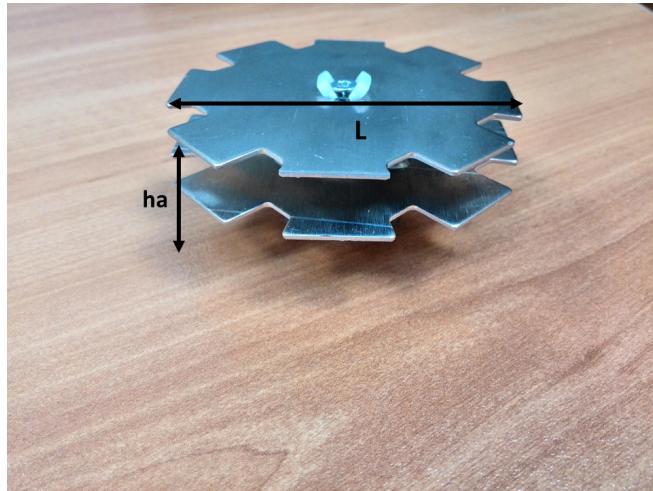

En el caso de TELNET son parches fractales basados en la geometría del copo de nieve de Koch. Los parches son alimentados de manera diferencial, usando una alimentación individual para cada una de las dos polarizaciones. Los puntos de alimentación están dispuestos según la polarización del parche. Se utilizan dos polarizaciones cruzadas (ortogonales) de  $+45^\circ$  y  $-45^\circ$  en los puntos de alimentación. Su frecuencia de resonancia, es decir, la frecuencia a la que pueden transmitir los datos depende de las dimensiones en los parches. En una primera aproximación simplificada se puede definir la frecuencia de resonancia en base a la longitud y la altura sobre el bastidor o plano de masa en la que se posicionan. Dada  $c$  la velocidad de propagación de las ondas en el vacío,  $L$  la longitud del parche,  $h$ , la altura del parche y  $\epsilon_e$  la constante dieléctrica efectiva del material que compone el parche, la frecuencia de resonancia, approximando el parche a uno rectangular, es [9]:

$$f_r = \frac{c}{2(L + h)\sqrt{\epsilon_e}} \quad (2.1)$$

donde

$$\epsilon_e = \frac{\epsilon_r + 1}{2} + \frac{\epsilon_r - 1}{2}(1 + \frac{12h}{w})^{-1/2} \quad (2.2)$$

FIGURA 2.2: Modelo de parche fractal de TELNET.

Por lo tanto, se precisa de un array de elementos diferente para cada banda de frecuencia sobre la que se desea transmitir. De este modo se dan distintas configuraciones de antenas base en función de las frecuencias que soportan. Si la frecuencia de trabajo de la antena es múltiplo de otra, cabe la posibilidad de intercalar los elementos radiantes para radiar en ambas dentro del mismo array. La disposición de los elementos radiantes y las fases con las que se transmite/recibe la señal conforman el haz de radiación con el que la antena transmite información a los equipos móviles. La antena debe cumplir una serie de especificaciones que garanticen su correcto funcionamiento:

- **Impedancia de entrada:** Se puede definir la impedancia de entrada de la antena ( $Z_e$ ) mediante la relación de los fasores de tensión y corriente en el punto de acceso a la misma. La impedancia de entrada de la antena constará de parte real (resistencia) y parte imaginaria (reactancia), sendos parámetros dependientes, en general, de la frecuencia [10].

$$Z = R_a + jX_a \quad (2.3)$$

Idealmente será la compleja conjugada de la salida que se conecte a la antena, normalmente este valor es de  $Z = 50 \Omega$  por lo que la componente imaginaria debe ser nula.

- **Pérdidas de retorno:** Relaciona la amplitud de la onda reflejada con la amplitud de la onda incidente, debe de tener un valor menor de -14 dB o una ROE de 1.5 [11].

$$\Gamma = \frac{Z - Z_o}{Z + Z_o} \quad (2.4)$$

$$ROE = \text{Ratio de onda estacionaria} = \frac{1 + |\Gamma|}{1 - |\Gamma|} \quad (2.5)$$

$$RL = 20\log_{10}(\Gamma) = 20\log_{10}\left(\frac{ROE - 1}{ROE + 1}\right) \quad (2.6)$$

- **Productos de intermodulación:** Los productos de intermodulación son generados por las no linealidades del amplificador de salida del transmisor (por ejemplo, los semiconductores, los klystrons, etc...) y de los dispositivos pasivos tales como combinadores, circuladores... Surgen al transmitir 2 o más portadoras simultáneamente con un sistema no lineal y causan interferencias, pudiendo bloquear uno o más canales de recepción en la antena. Las no-linealidades generan réplicas de las señales transmitidas en otras frecuencias derivadas de la combinación de las primeras. Si estas réplicas están en frecuencias donde se transmite o recibe información se generan interferencias. Para minimizar el efecto de los productos de intermodulación se deben tomar medidas en la estructura de la antena y los materiales utilizados para poder atenuar la amplitud de las señales replicadas de modo que, aunque existan, no degraden el funcionamiento en la antena [12].

- **Aislamiento entre las bandas de frecuencia y polarizaciones:** Es el nivel de aislamiento mínimo entre bandas frecuenciales de trabajo de la antena y las polarizaciones para una misma banda de trabajo. Debe ser menor de 30 dB para que no aparezcan interferencias que afecten al funcionamiento de la antena.

Por otro lado también se deben de tener en cuenta los siguientes parámetros relativos al diagrama de radiación de la antena:

- **Ancho del haz horizontal:** Es la separación angular de las direcciones en las que el diagrama de radiación de potencia toma el valor mitad del máximo en el corte horizontal. Su valor típico se encuentra entre los 60° - 65° [11].

- **Ancho de haz vertical:** Es la separación angular de las direcciones en las que el diagrama de radiación de potencia toma el valor mitad del máximo en el corte vertical. Su forma depende del número de elementos en el array, la distancia entre ellos y las amplitudes con las que son alimentados [11].

- **Supresión de lóbulos secundarios:** Mide el nivel de potencia que hay entre el haz principal y los lóbulos secundarios. El objetivo es minimizar este valor para aprovechar la potencia disponible y radiar la señal dentro del área deseada.

- **Factor de polarización cruzada:** La radiación de una antena en una polarización especificada se denomina polarización de referencia o copolar, mientras que a la radiación en la polarización ortogonal se la conoce como polarización cruzada. El cociente de las potencias contenidas en ambas polarizaciones es el factor de polarización cruzada, una medida de la pureza de polarización [11].

- **Ganancia de la antena:** La ganancia de una antena se define como la relación entre la densidad de potencia radiada en una dirección y la densidad de potencia que radiaría una antena isotrópica, a igualdad de distancias y potencias entregadas a la antena [11].

$$G = \eta D G(dBi) = D(dBi) - L(dB) \quad (2.7)$$

Donde  $G$  es la ganancia,  $\eta$  la eficiencia y  $D$  la directividad de la antena. Expresándola en función de la frecuencia:

$$G = \frac{4\pi}{\lambda^2} Ae \quad (2.8)$$

donde  $G$  es la ganancia,  $\lambda$  la longitud de onda y  $Ae$  el área efectiva de la antena.

## 2.2. Antenas Activas para BTS

La base teórica de las antenas activas en **BTS** consiste en *integrar* la RRU en la antena pasiva de modo que se puedan aprovechar todos los beneficios surgidos de dicha combinación [13][14][15]. Con esta unión se pasa de tener los tres elementos de las actuales instalaciones a tener solamente dos. Con ello las ventajas son diversas.

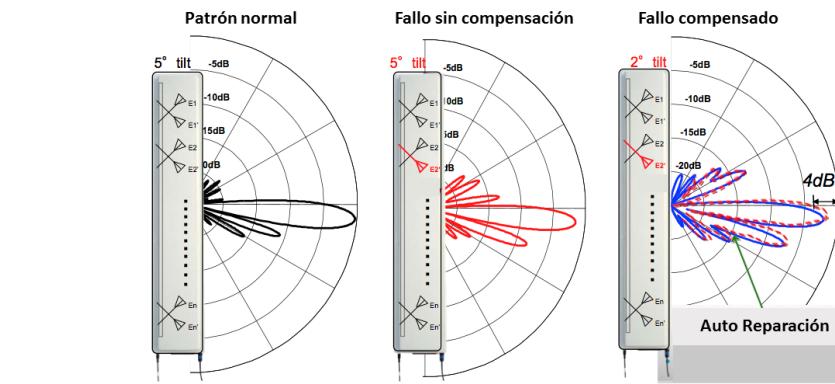

En el plano energético, teniendo un solo dispositivo que ejerce las funciones de la RRU y de la antena pasiva se tienen menos pérdidas derivadas de su consumo, repercutiendo directamente en la relación de señal a ruido. Realizando las funcionalidades de la RRU dentro de la antena, la señal es de dominio digital hasta la etapa RF previa al elemento radiante, aplicando con procesado digital una parte de las operaciones que antes se realizaban bajo dominio analógico.

Además, al controlar la señal de cada elemento radiante de manera digital se obtienen una serie de beneficios como son la posibilidad de incorporar mejoras al sistema sin introducir cambios de hardware o la modificación del haz de radiación. Una completa descripción de las antenas activas queda a disposición en el anexo A.

### 2.3. Estudio sobre las redes de conformado digital

Para la búsqueda de información referente a la red de transmisión y recepción con conformado de haz de radiación, además de buscar proyectos con objetivos similares a los de éste, se estudiaron de las técnicas empleadas por las RRUs actuales, puesto que gran parte de las funciones a realizar por la red de este proyecto son realizadas actualmente por la RRU:

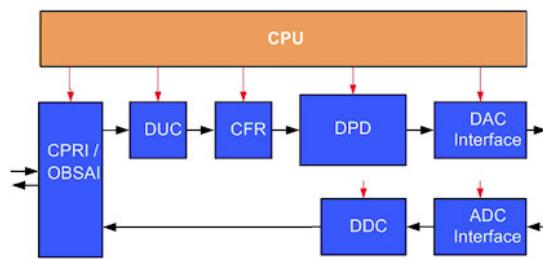

- El artículo de *Xiaofei Dong* para la revista electrónica EE Times “*Designing remote radio heads on high-performance FPGAs*” [16] fue una gran fuente de inspiración que, aún siendo un artículo informativo, informaba de las tendencias más innovadoras para implementar funciones propias de una RRU mediante FPGA (Fig 2.3).

FIGURA 2.3: Concepto de downlink en una RRU con según *Xiaofei Dong* [16].

- Se estudió y comparó diferentes tipos de filtros para su implementación en la cadena de recepción, sus ventajas y desventajas. Para ello se compararon el filtro raíz de senoide realizado, el filtro de raíz Nyqvist de Harry y diferentes tipos de filtros paso bajo [17].

- Respecto a trabajos realizados con anterioridad que asemejen sus objetivos con los del proyecto cabe destacar dos tesis, las presentadas por *Rik Portengen* [18] y *Juan Antonio Torres Rosario* [19] con un enfoque parecido pero sin una aplicación real. La diferencia con estos proyectos es que mientras ellos se basan en la asignación de pesos para realizar el conformado de haz, este proyecto realiza los desfases en la etapa de mezclado con el generador senoidal.

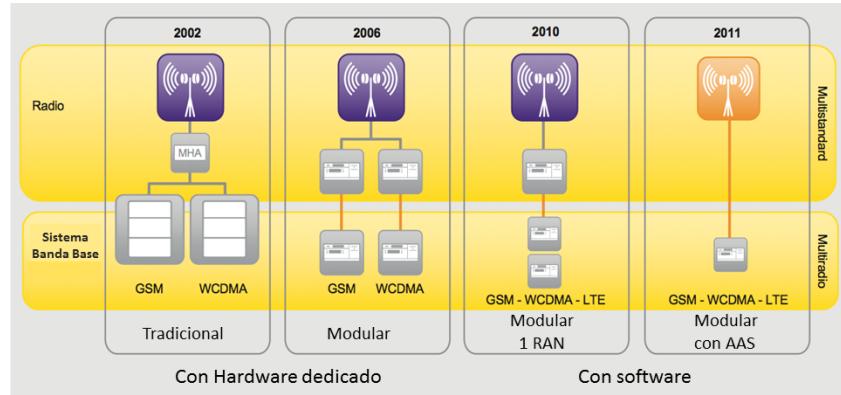

### 2.4. Evolución del desarrollo en el ámbito de las BTS

El desarrollo comercial de las antenas activas para BTS se inicia en el año 2006 con los primeros conceptos y prototipos de Huawei y Nokia Siemens. A día de hoy, la especificación por parte del

**3GPP**, el organismo que se encarga de estandarizar los equipos y redes de telecomunicaciones, sigue en constante revisión y actualización por lo que su implantación en escenarios reales es prácticamente nula. El secretismo en las empresas involucradas es máximo y la información que se puede encontrar es meramente orientativa y comercial, no va más allá de poder conocer las funcionalidades que pueden aportar. Las empresas que actualmente tienen los productos más desarrollados son las siguientes: **Huawei, Nokia-Siemens, Commscope, ZTE, Alcatel Lucent, Ericsson.**

La situación actual presenta un mercado sin modelos comercializados de estas antenas, siendo la mayoría prototipos. Dada la envergadura del producto se han encontrado bastantes asociaciones entre empresas para desarrollar las antenas de manera conjunta como es el caso de Commscope y Ubidyne, dividiendo el trabajo en la parte digital de procesado de la señal y la parte de RF. Los fabricantes apuestan porque que las necesidades de mayor capacidad impulsen la demanda de las antenas para su comercialización [20][21].

Con esta información se concluyó que la mejor manera de empezar a desarrollar la antena activa en forma de PFC era diseñar e implementar la base sobre la que se sustenten todas las características que distinguen las antenas activas de la solución actual, una red de conformado de haz con procesamiento digital de la señal que permita variar el ángulo de inclinación de su haz de radiación.

## Capítulo 3

# Diseño del prototipo teórico

### 3.1. Teoría de arrays unidimensionales de antenas

Basándose en el principio de superposición derivado de la linealidad de las ecuaciones de Maxwell, bajo medios lineales, si se superponen elementos idénticos e igualmente orientados se puede emplear la siguiente función (pag 4.4 [22]) para definir el campo eléctrico radiado por un elemento trasladado respecto al origen de coordenadas y alimentado con un fasor de corriente  $I_i$ :

$$\vec{E}_i(r, \theta, \phi) = \vec{E}_{nor}(r, \theta, \phi) \cdot I_i \cdot e^{jK\hat{r} \cdot \vec{r}_i} \quad (3.1)$$

Con  $\vec{E}_{nor}(r, \theta, \phi)$  = el campo radiado que aparece asociado a la distribución de corriente generada por una elemento isotrópico centrada en el origen.

$$K = \frac{2\pi}{\lambda}$$

$\vec{r}_i$  = el vector posición del campo

Atendiendo a la propiedad de superposición, el campo radiado por el conjunto de elementos que conforma la agrupación tomará la forma:

$$\vec{E}(r, \theta, \phi) = \sum_{i=0}^{N-1} \vec{E}_i(r, \theta, \phi) = \vec{E}_{nor}(r, \theta, \phi) \cdot \sum_{i=0}^{N-1} I_i \cdot e^{jK\hat{r} \cdot \vec{r}_i} \quad (3.2)$$

El campo total radiado se puede expresar como el producto del campo del elemento básico, supuesto situado en el origen y alimentado con un fasor de corriente normalizado a la unidad,

por el factor de array FA:

$$FA(\theta, \phi) = \sum_{i=0}^{N-1} I_i \cdot e^{jK\hat{r} \cdot \vec{r}_i} \quad (3.3)$$

$$\vec{E}(r, \theta, \phi) = \vec{E}_{nor}(r, \theta, \phi) \cdot FA(\theta, \phi) \quad (3.4)$$

El factor de array es función de:

- La posición relativa de los elementos.

- Los coeficientes de alimentación  $I_i$ .

- La frecuencia.

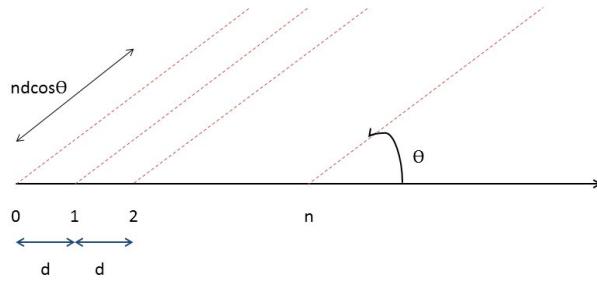

Ahora, considerando una agrupación (Fig 3.1) lineal rectilínea con espaciado  $d$  constante entre los elementos, formada por  $N$  antenas idénticas sobre el eje z, situadas en las posiciones  $z_n = nd$  y alimentadas con fasores de corrientes  $I_n$ , donde  $n = 0, 1, \dots, N - 1$ .

FIGURA 3.1: Agrupación de antenas unidimensional con frente de ondas en un ángulo  $\theta$ .

Si se denota con  $\vec{J}_o(\vec{r})$  a la distribución de corriente que aparece sobre la antena básica centrada en el origen de coordenadas cuando a su entrada se excita con un fasor de corriente unitario, el factor de array se puede denotar como:

$$FA(\theta, \phi) = \sum_{i=0}^{N-1} I_i \cdot e^{jK\hat{r} \cdot \vec{r}_i} \quad (3.5)$$

donde

$$\vec{r}_n = k \cdot d \cdot \hat{z} \quad (3.6)$$

$$\hat{r} \cdot \vec{r}_n = k \cdot d \cdot \cos\theta \quad (3.7)$$

En los sistemas de alimentación típicos, los fasores de corriente  $I_n$  se alimentan con un término de fase progresiva entre antenas consecutivas, escribiéndose:

$$I_n = a_n \cdot e^{j \cdot n \cdot \alpha} \quad (3.8)$$

donde  $a_n$  es la amplitud del elemento y  $\alpha$  la fase del elemento. Por lo que el factor de agrupación es, en estas condiciones:

$$FA(\theta, \phi) = \sum_{n=0}^{N-1} I_n \cdot e^{jnKd \cos\theta} = \sum_{n=0}^{N-1} a_n \cdot e^{jnKd \cos\theta + jn\alpha} = \sum_{n=0}^{N-1} I_n \cdot e^{jn\psi} \quad (3.9)$$

Definiendo, para simplificar esta expresión, la función de ángulo eléctrico  $\psi$  como:

$$\psi = k \cdot d \cdot \cos\theta + \alpha \quad (3.10)$$

Esta función representa la diferencia en la contribución de fase en campo lejano debido a la diferencia de caminos entre dos antenas consecutivas ( $kdcos\theta$ ) y el desfase progresivo en el sistema de alimentación ( $\alpha$ ). Por lo tanto, la expresión del campo eléctrico radiado por la agrupación es:

$$E(r, \theta, \phi) = E_{nor}(r, \theta, \phi) \cdot \sum_{n=0}^{N-1} a_n \cdot e^{jn\psi} \quad (3.11)$$

Es importante denotar que si el array estuviese orientado sobre el eje x o y la expresión sería diferente al depender de  $k_x$  o  $k_y$  en vez de  $k_z$ .

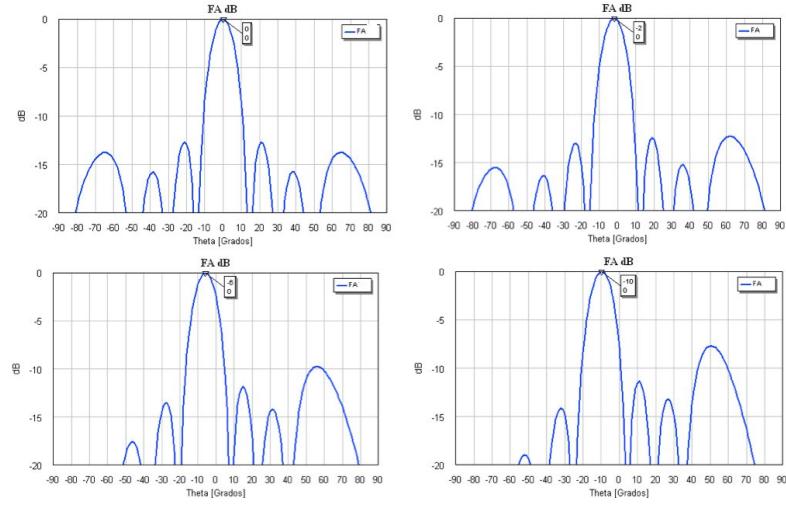

Tomando la ecuación 3.10 se puede ver que, para una  $k$  y  $d$  fijas, variando  $\alpha$  se consigue variar  $\theta$ , es decir, el ángulo de radiación con el que el frente de ondas se radía.

### 3.2. Especificaciones de la unidad de conformado de haz

De cara a conseguir realizar los objetivos propuestos se debe de tener en cuenta las restricciones que plantea el escenario de trabajo:

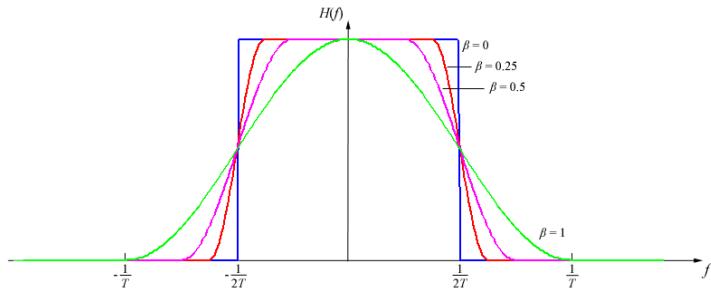

- La señal analógica recibida contiene una portadora WCDMA [23] procedente de una etapa RF anterior, trasladada en a una frecuencia intermedia de 140 MHz, con un ancho de banda de 5 MHz según la especificación WCDMA y una amplitud acondicionada a la entrada del ADC (Analog-Digital Converter) de 0 dBm. La especificación, además,

exige un filtrado en raíz de coseno realizado con un factor de *roll-off*  $\beta = 0,22$  tanto en la rama de recepción como en la de transmisión. El ancho de banda de la portadora es de 5 MHz, pero su frecuencia de chip es de 3.84 MHz por lo que para poder tomar varias muestras se utiliza un factor de sobremuestreo de 4 precisando por ello un ancho de banda de 15.36 MHz.

- La distancia entre los elementos radiantes es de  $d = 0,8\lambda \simeq 130\text{ mm}$  con  $f = 1940\text{ MHz}$  y  $\lambda = \frac{c}{f} = 0,154\text{m}$ .

- La antena se compone de un array de 4 elementos unidimensional.

- Para el desarrollo teórico se supondrá el array de elementos sobre el eje z.

Además, se establecen una serie de requisitos principales que afectan al desarrollo del conformador de manera general:

- **Escalabilidad:** Dada la magnitud del proyecto sobre el que se sustenta este PFC es importante mantener una gran organización y modularidad para poder verificar de una manera sencilla y eficaz cada función cuando se vayan añadiendo nuevas características.

- **Fiabilidad:** Puesto que se pretende realizar un prototipo completamente funcional, es imprescindible que este sea fiable en la prestación de sus servicios, eficaz en la ejecución y eficiente en los tiempos.

FIGURA 3.2: Escenario de trabajo para prototipado del ADC y downlink compuesto de una fuente de alimentación un generador de frecuencias, un osciloscopio y la placa de desarrollo Microhemir.

### 3.2.1. Diseño de un array de antenas con elementos desfasados entre sí

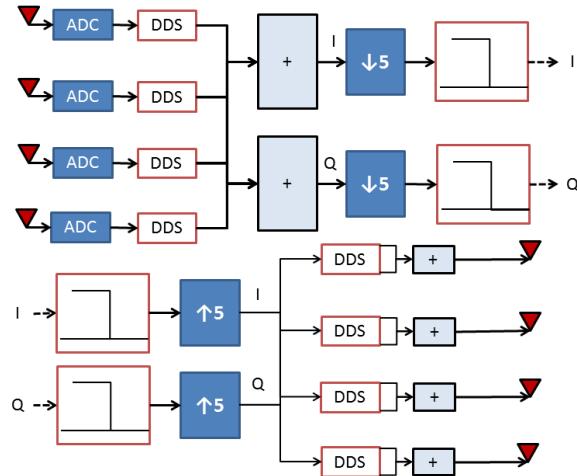

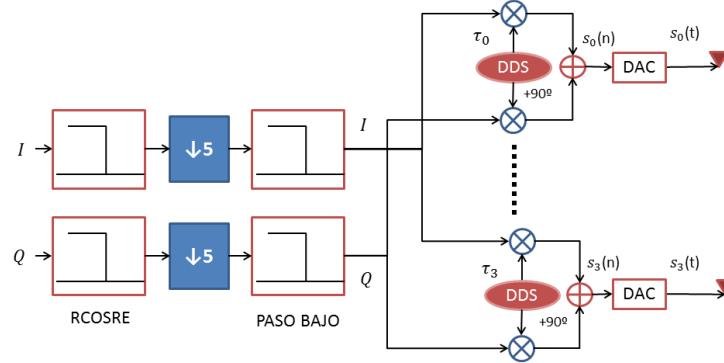

FIGURA 3.3: Esquema del conformador de haz de radiación en recepción y transmisión.

Un array de antenas desfasadas tipo presenta un grupo de elementos radiantes idénticos entre sí, cada uno con su red de alimentación, desfase y amplificación y una red de suma para conseguir la señal del haz en un punto. Para cada elemento se aplica un producto de pesos multiplicando la señal recibida por su correspondiente peso en amplitud y fase dependiendo de la configuración del haz de radiación. La red del conformado de haz puede estar compuesta de lentes de microondas, guías de ondas, líneas de transmisión o circuitos de microondas impresos que apliquen los pesos a las señales.

La aplicación de los desfases a las señales está basada en las matrices multihaz, redes de transmisión/recepción con la capacidad de conformar varios haces diferentes. La matriz multihaz más típica es la matriz de **Butler** [24], está formada por un array de 4 elementos con 4 uniones desfasadas  $90^\circ$  entre sí y dos desfasadores de  $45^\circ$ . Siguiendo la señal por los diferentes caminos se pueden conformar 4 haces que difieren en el ángulo de inclinación.

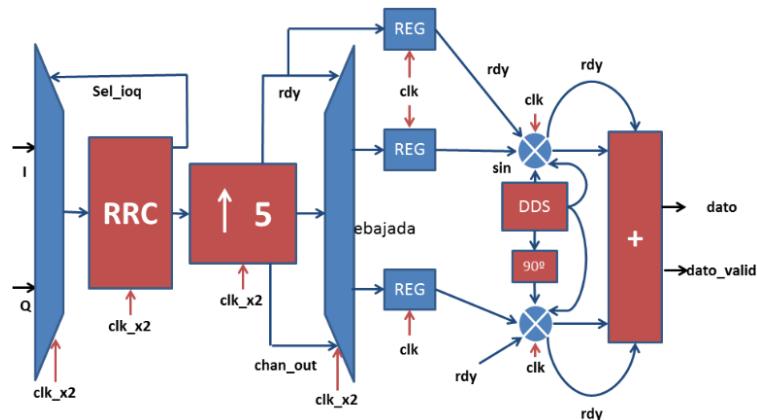

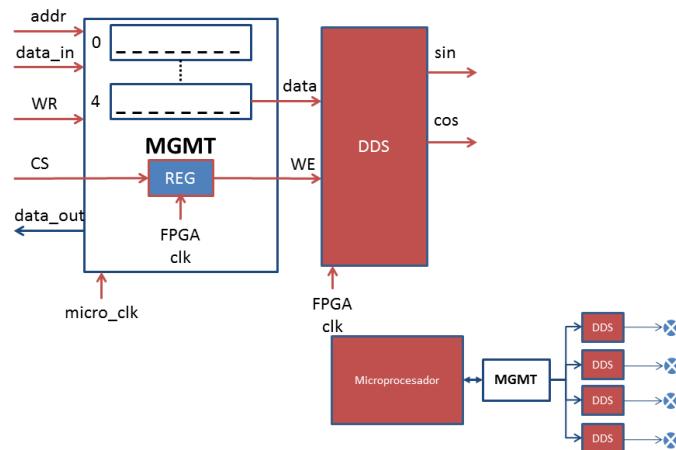

Para realizar el proceso desde un punto de vista digital, la señal se descompone en fase y cuadratura procesándola en banda base de manera independiente y realizando el desfase a la hora de sacar las componentes IQ (Fig 3.3). Para ello se precisan conversores ADC y DAC (Digital-Analog Converter) que conviertan la señal entre los dominios analógico-digital y un procesador digital que realice las operaciones de la señal en dominio digital, además de una etapa RF previa que acondicione la señal recibida por el array para que el conformador de haz digital la pueda procesar.

### 3.2.2. Etapa RF previa a la unidad de conformado de haz

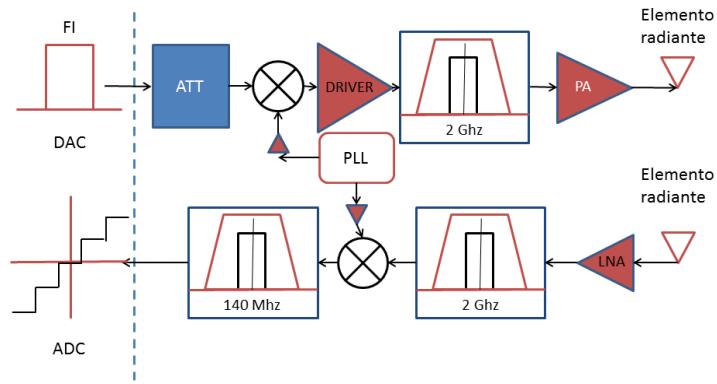

FIGURA 3.4: Esquema de la etapa RF previa al conformador de haz digital en transmisión y recepción.

Para que la señal pueda ser procesada por el conformador de haz digital es necesario que ésta sea acondicionada por una etapa RF previa (Fig 3.4). La etapa es replicada por cada elemento radiante tanto en recepción como en transmisión, en este caso, 4 veces. En recepción, el elemento radiante recibe la señal en una frecuencia de 2 GHz y la señal debe ser amplificada por un LNA debido a que su potencia es muy baja. Tras realizar un filtrado paso banda eliminando las componentes fuera de la banda de interés se vuelve a acondicionar la señal. Ésta se mezcla con la señal de un oscilador local para trasladarla a una frecuencia intermedia de 140 MHz, frecuencia apropiada para la conversión a digital con el ADC. Por último, se realiza un filtrado para eliminar la imagen fruto del mezclado con el oscilador local y se alimenta el ADC.

En transmisión, partiendo de la señal WCDMA, la figura de ruido no es tan crítica por lo que la amplificación se realiza con drivers. Los drivers son acompañados de atenuadores para conformar el control automático de ganancia y la señal es trasladada en frecuencia mediante un mezclador junto con una señal generada con el oscilador local. Tanto este oscilador como el de la etapa en recepción precisan de drivers para amplificar su señal y adecuarla a la amplitud de la señal de datos. Tras la etapa del mezclador se filtran las imágenes surgidas de ésta y se transmite la señal al elemento radiante. Una vez se tenga el prototipo del conformador con los elementos radiantes y la etapa RF será necesario implementar un camino de feedback entre la salida de la etapa RF y la FPGA. De este modo se podrá medir el desfase introducido en la señal debido a la longitud del camino y autocalibrar el sistema. Para ello se ajustan los

desfases asociados a los elementos en función de los caminos que toman sus señales hasta la salida.

### 3.3. Diseño de la unidad de conformado de haz

El diseño se abordará dividiéndolo en dos partes diferenciadas, por un lado la de recepción y por otro la de transmisión, diseñando con ellos sus correspondientes conformadores de haz. Atendiendo a la figura 3.3, ambos son muy similares y de este modo se consigue simplificar todo el proceso de diseño marcando una visión más reducida en primera instancia.

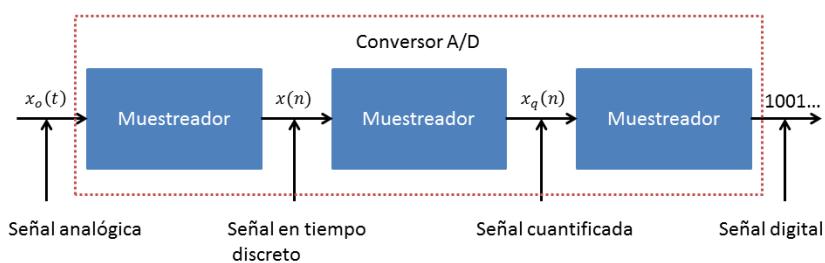

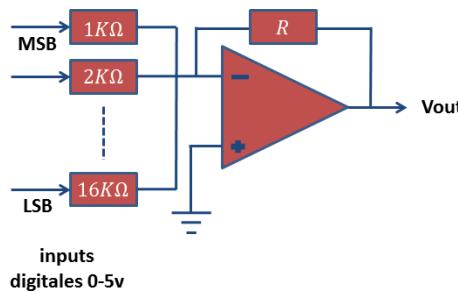

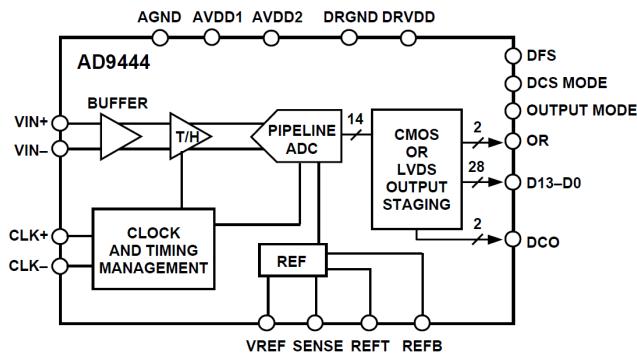

#### 3.3.1. Etapa de conversión de la señal en dominio analógico a digital

Empezando por la parte encargada de la recepción de señal, se parte a la entrada de la señal analógica WCDMA con ancho de banda  $BW = 5 \text{ MHz}$  y portadora en  $140 \text{ MHz}$  proveniente de la etapa RF previa. Esta señal se debe convertir a dominio digital para poder realizar el procesado posterior. El conversor analógico-digital es el paso intermedio entre la señal analógica recibida de la etapa RF y la entrada del conformador digital. Éste transforma una señal analógica al dominio digital mediante las operaciones de muestreo, cuantización y codificación de la señal analógica (Fig 3.5).

FIGURA 3.5: Funciones de un conversor analógico-digital tipo.

Para la conversión se pueden emplear diferentes técnicas [25] como la comparación de voltaje, sigma-delta, doble pendiente, la sucesión de aproximaciones etc... La técnica de *comparación de voltaje* se compone de una serie de comparadores en forma de amplificadores operacionales en paralelo que evalúan la señal de entrada con diferentes umbrales de voltaje. Es un método muy rápido pero tiene poca resolución, es poco eficiente energéticamente y caro. *Sigma-Delta*

basa su funcionamiento en el sobremuestreo de la señal, ésta pasa por un integrador y se compara con el nivel de tierra. Tiene mucha resolución pero debido a que se basa en el sobremuestreo posee una baja frecuencia de muestreo máxima. Los conversores de *doble pendiente* cargan en un condensador la señal de entrada durante un periodo de tiempo para posteriormente descargarlo. Dependiendo del tiempo de descarga los bits codificados serán unos u otros. No generan ruido y tienen gran precisión a costa de ser caros y lentos. Finalmente los conversores por *aproximaciones sucesivas* se basan en la fijación de un valor umbral (Most Significant Bit), su conversión a analógico y comparación con la señal de entrada. Pueden funcionar a altas velocidades y ofrecen un gran compromiso entre resolución y precio.

Cuando se cita la frecuencia de muestreo generalmente se refiere a la frecuencia máxima del conversor, pero es importante tener en cuenta igualmente la frecuencia mínima de operación en caso de que se deba reducir la frecuencia de muestreo, pues los requisitos de tiempos de *hold*<sup>1</sup> incrementan proporcionalmente. En este sentido los conversores de aproximaciones sucesivas presentarán menos problemas que aquellos con arquitectura basada en la comparación de voltaje. Además, los conversores Sigma-Delta no poseen señal de control por lo que presentan un funcionamiento perpetuo, lo cual puede ser un impedimento de cara a utilizar el conversor en aplicaciones síncronas como las presentadas en este proyecto.

Por estos motivos el conversor escogido será un conversor de **aproximaciones sucesivas**. La amplia mayoría de conversores de alta velocidad son de este tipo puesto que sus ventajas superan ampliamente a sus inconvenientes y su precio es muy ajustado.

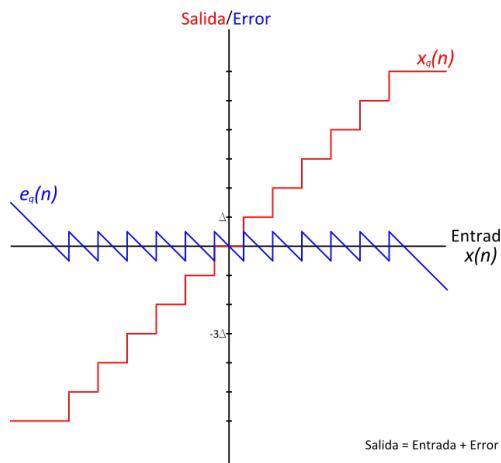

Otro cálculo a tener en cuenta es la **resolución** del conversor en bits. Esta resolución vendrá dada por el nivel de amplitud con el que la señal analógica entra en el conversor e influirá directamente en el error de cuantificación que se pueda encontrar a la salida. El error quedará representado como potencia de ruido y por lo tanto afectará a la **SNR** (Signal to Noise Ratio) de la rama. Para aplicaciones de comunicaciones lo común es trabajar en rangos de los 14-16 bits.

$$e_q(n) = x_q(n) - x(n) \quad (3.12)$$

Donde  $x(n)$  representa a la secuencia de muestras de amplitud continua a la entrada del cuantificador,  $x_q(n)$  a la secuencia de muestras de amplitud discreta a la salida del cuantificador y  $e_q(n)$  representa a la secuencia de muestras de amplitud continua del error de cuantificación (Fig 3.6). Mientras la señal analógica de entrada se encuentre en el rango del cuantificador se

---

<sup>1</sup>El tiempo de hold es el tiempo necesario que la señal de datos debe estar estable una vez ha sido muestreada

cumplirá:

$$-\frac{\Delta}{2} < e_q(n) < \frac{\delta}{2} \quad (3.13)$$

donde  $\Delta$  es el tamaño del escalón de cuantificación que viene dado por:

$$\Delta = \frac{R}{L} \quad (3.14)$$

donde R es el rango del cuantificador y L el número de niveles de cuantificación. El nivel de potencia de entrada debe tratar de maximizar la SNR a fin de realizar una óptima conversión a digital.

FIGURA 3.6: Esquema del nivel de salida de un cuantificador uniforme y su ruido de cuantificación.

El siguiente parámetro a tener en cuenta es la **frecuencia de muestreo**. Dado que la señal que se desea muestrear se encuentra en una frecuencia intermedia de 140 MHz, sería necesario muestrear con una frecuencia  $140 \cdot 2 = 280 \text{ MHz}$  para cumplir con el criterio de Nyquist [26] (Fig 3.7). Ésto es muy complicado de conseguir teniendo en cuenta, además, el factor de sobremuestreo que se utilizará para poder tomar una buena muestra de la señal. Por ello, es conveniente hacer uso de la técnica del *submuestreo* o muestreo en paso banda (véase anexo D). Mediante esta técnica se toman muestras de la imagen de la señal original en una frecuencia más próxima a la banda base, en este caso de 13.6 MHz. Por otra parte se precisa de una frecuencia de muestreo que sea múltiplo de 15,36 MHz para poder realizar el sobremuestreo como se ve en el apartado 3.3.3.2. Una frecuencia múltiplo de 15.36 MHz es 76.8 MHz, frecuencia menor que el límite de 80 MHz que soporta el conversor incorporado en la placa de evaluación *Microhemir*.

$f = 13,6 \text{ MHz}$  = Frecuencia de la portadora.

$B = 5 \text{ MHz}$  = Ancho de banda de la portadora.

Por lo tanto la frecuencia de muestreo según el criterio de Nyqvist es

$$2(f + \frac{B}{2}) = F_s = 32,2 \text{ MHz} \quad (3.15)$$

Teniendo la señal en 13.6 MHz, serán necesarios los cálculos expuestos en el anexo D para corroborar que no hay solapamientos y filtros con buen factor de calidad para aislar la señal de las muestras indeseadas.

FIGURA 3.7: Esquema de frecuencias de muestreo.

### 3.3.2. Etapa de conformado del haz de radiación en recepción

FIGURA 3.8: Bloques del conformador de haz de radiación en recepción.

Una vez ya se dispone de los procedimientos correctos para obtener una señal digital a partir de la analógica se ha de modelar matemáticamente como se recibirán las 4 señales de los elementos radiantes (Fig 3.8). Cada elemento radiante de los 4 que componen el array recibirá una

señal  $f_t$  con un retardo temporal diferente para cada elemento. Este proyecto lleva a cabo la recuperación de la señal original mediante el siguiente proceso.

La señal es recibida en cada elemento y convertida al dominio digital mediante los conversores ADC. Cada elemento dispone de un oscilador local, que genera una señal senoidal a la frecuencia intermedia de 13.6 MHz, frecuencia donde se localiza la imagen de la señal original a 140 MHz. Esta señal senoidal es desfasada con un cierto periodo calculado individualmente para cada elemento el cual está asociado al desfase de la señal de entrada en cada elemento del array, conformando el haz de radiación. Del mezclador salen dispuestas las tramas IQ de cada elemento, éstas se suman y escalan por 4 en cada rama para, calculando una media aritmética de las 4 muestras, poder obtener una muestra lo más parecida posible a la original.

### 3.3.2.1. Teoría de la aproximación a señal de banda estrecha

Para entender el desarrollo matemático del conformador de haz es preciso tener claro el concepto banda estrecha y por qué se puede realizar la aproximación de una señal retardada a esa misma señal sin retardo [19].

Una caracterización de la señal  $f(t, p)$  donde se usa una señal paso banda para transmitir información puede describirse de la siguiente forma:

$$f(t, p_n) = \sqrt{2} \operatorname{Re}\{\tilde{f}(t, p_n) e^{j w_c t}\}, \quad n = 0, \dots, N - 1, \quad (3.16)$$

donde  $t$  es el instante temporal,  $p_n$  la posición del elemento radiante,  $w_c$  es la frecuencia de la portadora (en este caso  $2\pi \cdot 140 \cdot 10^6$  rad/s) y  $\tilde{f}(t, p_n)$  la forma compleja de la señal. Si la señal es una onda plana se puede simplificar a:

$$f(t, p_n) = \sqrt{2} \operatorname{Re}\{\tilde{f}(t - \tau_n) e^{j w_c (t - \tau_n)}\}, \quad n = 0, \dots, N - 1, \quad (3.17)$$

donde  $\tau_n$  está dado por:

$$\tau_n = \frac{\bar{k}^T \cdot \bar{p}_n}{w_c} \quad (3.18)$$

$$\bar{k}^T = \frac{2\pi}{\lambda} \cos \theta \quad (3.19)$$

$$\bar{p}_n = p_z \quad (3.20)$$

para un array unidimensional sobre el eje z.

Dado  $\Delta T_{max}$  el tiempo máximo en recorrer la distancia entre dos elementos por una onda plana:

$$\tau_n \leq \Delta T_{max}, \quad n = 0, \dots, N - 1. \quad (3.21)$$

Por lo tanto, si una señal de ancho de banda  $B_s$  cumple:

$$\Delta T_{max} \cdot B_s \ll 1 \quad (3.22)$$

es definida como de *Banda Estrecha*. Ésto valida la siguiente aproximación:

$$\tilde{f}(t - \tau_n) \simeq \tilde{f}(t), \quad n = 0, \dots, N - 1. \quad (3.23)$$

Como  $\Delta T_{max}$  es equivalente a  $d/c$  con d la distancia entre radiantes y c la velocidad de propagación de la onda en el vacío, la ecuación 3.23 equivale a:

$$B_s \ll \frac{c}{d} \quad (3.24)$$

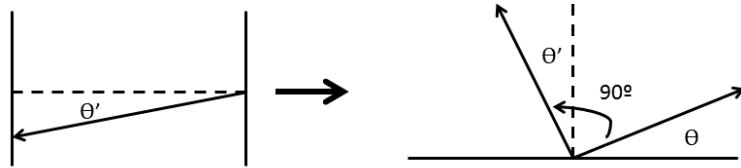

Esta condición no se cumple para  $f_i = 13,6 \text{ MHz}$  pero sí para  $f_i = 140 \text{ MHz}$  por lo que la señal se trasladará a una frecuencia intermedia de 140 MHz y el ADC replicará la señal en 13.6 MHz. Tomando esta expresión en la ecuación 3.17 se puede ver que las líneas con retardos  $\tau_n$  pueden ser sustituidas con las mismas líneas pero con desfases  $e^{-jw_c\tau_n}$ . Usando desfases progresivos se puede dirigir el lóbulo principal del haz de radiación con cualquier ángulo de inclinación sobre el eje  $\theta$ .

### 3.3.2.2. Modelo matemático de la etapa de conformado de haz de radiación en recepción

FIGURA 3.9: Esquema del haz de radiación desfasado que llega en recepción.

La señal, a la entrada de cada elemento:

$$f(t, p_n) = c_n(t) = x(t - \tau_n) \cos(w_{RF}(t - \tau_n)), n = 0, \dots, N - 1 \quad (3.25)$$

utilizando la aproximación de banda estrecha:

$$\approx x(t) \cos(w_{RF}t - \theta'_n) \quad (3.26)$$

Donde  $\theta'_n = w_{RF}\tau_n$  con  $\tau_n$  el retardo temporal al que se ve sometido el elemento n. Al pasar por la etapa RF, la señal es trasladada a la frecuencia intermedia multiplicándola por un oscilador local. Este oscilador modifica la señal de entrada en la parte del coseno con la frecuencia intermedia. Para conseguir el retardo en frecuencia intermedia equivalente al presente en la frecuencia original:

$$w_{FI}\tau_{FI} = w_{RF}\tau_{RF} \quad (3.27)$$

Por lo tanto, tras pasar por el oscilador local de la etapa RF, al inicio del enlace de recepción digital se encuentra la siguiente señal:

$$g_n(n) = x(n) \cos(w_{IF}n - \theta'_n) \quad (3.28)$$

donde

$$\theta'_n = w_{RF}\tau_n \quad (3.29)$$

el desfase a la frecuencia de trabajo de la señal de entrada. El objetivo es procesar la señal original  $x_n$  y para ello se deberá mezclar con un oscilador generando un desfase equivalente al de la señal de entrada.

Para mantener la aproximación de banda estrecha y anular el retardo con el que llega la señal al array se mezcla cada señal de los diferentes elementos con los tonos senoidales generados por sendos osciladores, cada uno desfasado con un valor diferente para cada elemento radiante. De esta forma, a la entrada de los mezcladores:

$$s_n(n) = x_n(n - \tau_{RF}) \cos(w_{FI}n - w_{RF}\tau_{RF}n) \quad (3.30)$$

Multiplicando por el tono desfasado y aplicando la aproximación de banda estrecha:

$$s'_n(n) = x(n) \cos(w_{FIn} n - w_{RF} \tau_{RFn}) \cos(w_{FIn} n - w_{FI} \tau_{FI} n) \quad (3.31)$$

En dominio frecuencial:

$$X(w) e^{-jw_{RF} \tau_{RF}} e^{+jw_{FI} \tau_{FI}} \quad (3.32)$$

Finalmente los cosenos quedan anulados por lo que la señal queda:

$$s'(n) \simeq x(n) \quad (3.33)$$

De este modo se obtiene la señal original en banda base sin desfase para su posterior procesado digital. Multiplicando por señales senoidales desfasadas entre sí 90° se consiguen extraer las tramas IQ de la señal.

### 3.3.3. Enlace de recepción del conformador de haz de radiación

#### 3.3.3.1. Obtención de tramas IQ a partir de la señal digital

Una vez se dispone de la señal captada procedente de los 4 elementos radiantes se procede a obtener las tramas IQ de esta señal mediante una etapa DDC (Digital DownConversion). Este proceso se llevaría a cabo multiplicando la señal digital por una senoide y por esa misma señal desfasada 90°, ambas generadas por un oscilador local a una frecuencia igual a la de la señal de entrada al bloque, en este caso 13.6 MHz (Fig 3.10). Normalmente a ésto le sigue un filtrado de paso bajo con una frecuencia de muestreo igual al ancho de banda de la señal ya en banda base pero, dado que posteriormente se realiza un diezmado de la señal con su filtrado paso bajo asociado, no es necesario redundar en ello. Por lo tanto, en todo el modelo matemático anterior habría que añadir en otra rama la multiplicación por una señal  $\sin(w_{FIn} n - w_{FI} \tau_{FI} n)$ .

Si a la entrada se halla una señal de la forma

$$g[n] = x[n] \cos[w_{IF} n] \quad (3.34)$$

FIGURA 3.10: Esquema de la etapa de mezclado para la obtención de las tramas IQ.

Al multiplicar por las señales senoidales

$$\begin{cases} i[n] = [n]\cos[w_i] = x[n]\cos[w_i]\cos[w_i] \\ q[n] = s[n]\sin[w_i] = x[n]\cos[w_i]\sin[w_i] \end{cases} \quad (3.35)$$

Así, tras la etapa DDC se dispone de 2 señales en banda base IQ.

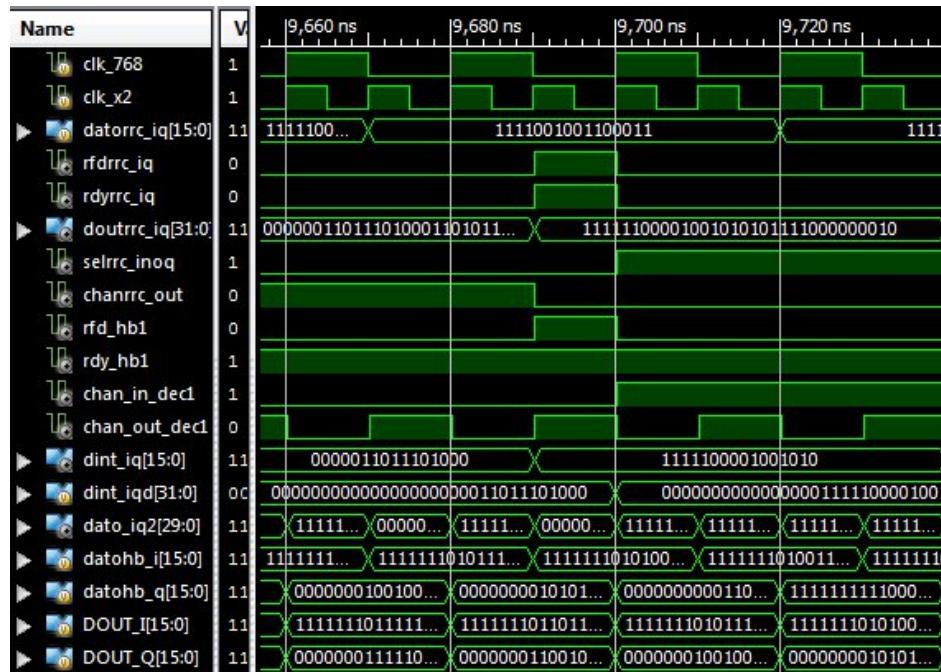

### 3.3.3.2. Etapa de diezmado de tramas IQ de la señal digital

La portadora original recibida se encontraba en 140 MHz y su imagen en 13.6 MHz. Como se ha avanzado anteriormente, es necesario muestrear a 76.8 MHz debido a que las señales digitales no son trenes reales de pulsos binarios teóricos. Al no disponer de un instante perfecto de muestreo es posible que, dependiendo de cuando se tome la muestra se escoja un valor erróneo como se aprecia en la imagen (Fig 3.11). Por ello, es necesario tomar varias muestras de la señal para posteriormente hallar su valor mediante correlación. Para ello se aplicará una etapa de diezmado:

$$Tasa\ de\ chip = T = 3,84\ MHz$$

$$4T = 15,36\ MHz$$

$$Fs = \text{Frecuencia de muestreo} = 76,8\ MHz$$

$$\frac{Fs}{5} = 15,36 = 4T$$

Como se ha expuesto anteriormente, una frecuencia válida para cumplir los requisitos del sobremuestreo es la de 76.8 MHz. Este número de muestras es además requisito del protocolo CPRI, donde en su especificación exige que para el enlace de recepción se tomen como mínimo 1-2 muestras de *chip*<sup>1</sup> para realizar la correcta sincronización en la BTS y de 2-4 en el enlace

<sup>1</sup>El chip es valor muestreado binario

FIGURA 3.11: Señal digital teórica-Señal digital real.

de transmisión.

Matemáticamente se puede realizar de diferentes formas. Aquí se exponen 2, por *filtros en cascada* y usando un filtro *FIR lineal*. Tomando como referencia un filtro integrador en cascada, su estructura se compone de una sección de integración, operando a una frecuencia de muestreo alta combinada con una sección de acondicionamiento y operando a una frecuencia más baja. Estos filtros se pueden usar tanto para interpolar como para diezmar la señal (Fig 3.12).

FIGURA 3.12: Esquema del bloque diezmador mediante filtros en cascada CIC.

La función de transferencia del filtro sería:

$$H(z) = H_I^N(z)H_C^N(z) = \frac{(1 - z^{-RM})^N}{(1 - z^{-1})^N} = \quad (3.36)$$

$$= \left[ \sum_{k=0}^{RM-1} z^{-k} \right]^N \quad (3.37)$$

$$H_C(z) = 1 - z^{-RM}, H_I(z) = \frac{1}{1 - z^{-1}}, z \in \mathbb{C} \quad (3.38)$$

con  $R$  el factor de diezmado o interpolación,  $M$  el número de etapas de retardo en cada etapa de acondicionamiento y  $N$  el número de etapas tanto en la parte de integración como en la de acondicionamiento.

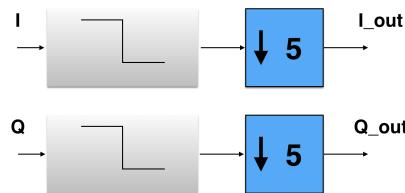

Para realizar el diezmado mediante un filtro FIR lineal (Fig 3.13), si la frecuencia de muestreo final es  $M$  veces menor que la inicial:

$$f_{s2} = \frac{f_{s1}}{M} \quad (3.39)$$

FIGURA 3.13: Etapa de diezmado con filtro FIR lineal.

La disminución de la frecuencia de muestreo se lleva a cabo tomando una de cada  $M$  muestras de la salida y replicándolas posteriormente, desechando las  $M - 1$  intermedias. Para este proyecto  $M = 5$  y la relación entrada-salida será, en dominio temporal:

$$x[n] = x_a[nT] \longrightarrow \downarrow 5 \longrightarrow y[n] = x_a(n5T) \quad (3.40)$$

Este sistema es lineal pero no invariante temporal, es decir, un retardo de  $n$  muestras en la señal de entrada no produce la misma señal de salida retardada  $n$  muestras. Cuando se diezma una señal como se acaba de describir, existe el peligro de que, aunque  $x[n]$  no contenga *aliasing*<sup>2</sup>, dado que  $y[n]$  corresponde a una frecuencia de muestreo menor,  $y[n]$  sí que lo tenga. Para que

---

<sup>2</sup>El aliasing es un fenómeno que se produce en el diezmado cuando a las muestras de la señal se le superponen las muestras de su componente  $2\pi$ -periódica.

al diezmar por  $M$  no exista *aliasing*, el ancho de banda de la señal original deberá ser :

$$B_s < \frac{f_{sy}}{2} = \frac{f_{sx}}{2M} \quad (3.41)$$

Normalmente se cumplirá únicamente que  $B_s < \frac{f_{sx}}{2}$  por lo que será necesario realizar un filtrado paso bajo digital previo de la señal  $x[n]$  antes de ser diezmada. Para determinar la frecuencia de corte discreta necesaria es preciso conocer la frecuencia de muestreo a la que trabajará el filtro  $f_{sx}$ . La frecuencia de corte será por lo tanto  $\frac{f_{sx}}{2M}$ .

Xilinx ofrece un CORE IP para este propósito llamado **FIR Compiler**. Como su propio nombre indica utiliza la segunda forma expuesta tanto para la interpolación como para el diezmado. A este CORE se le pasan los coeficientes del filtro a implementar hallados mediante la herramienta de Matlab **fdatool**. En este caso el factor de diezmado es de **5**. Para definir el filtro prediezmar se precisa de una banda de stop igual a  $\frac{76,8 \text{ MHz}}{5 \cdot 2}$  que por definición es la necesaria para evitar aliasing y una banda de paso de hasta  $3,84 \text{ MHz} \cdot (1 + \beta)$  donde  $\beta$  es el factor de *roll-off* definido en la especificación UMTS (Universal Mobile Telecommunications System) como **0.22**.

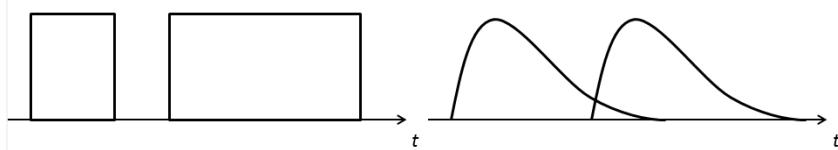

### 3.3.3.3. Filtrado con raíz de coseno realizado de las tramas IQ

Finalmente como última etapa del enlace de recepción se encuentra el filtrado en raíz de coseno realizado. Se utiliza este filtro porque dado un **BER** (Bit Error Rate), es el que menos potencia de transmisión requiere y como se está limitando en banda el espectro, eliminará la **ISI** (Interferencia Intersimbólica) (Fig 3.14). La ISI aparece cuando, al limitar el ancho de banda de los pulsos, éstos se deforman por los bordes.

FIGURA 3.14: Señal digital perfecta y afectada por ISI.

El filtro perfecto para anular este efecto sería el filtro rectangular, pero en la práctica es imposible de realizar por lo que se utiliza el filtro raíz de coseno realizado donde un factor de *roll-off* igual a 0 equivaldría al filtro rectangular. Es, por lo tanto, una implementación de un