# TESIS DE LA UNIVERSIDAD DE ZARAGOZA

2024 272

# Guillermo Díez Señoráns

Nuevas estrategias de diseño FPGA para la implementacion de funciones no-clonables fisicamente en ecosistemas IoT

Director/es

Celma Pueyo, Santiago García Bosque, Miguel

ISSN 2254-7606

Universidad de Zaragoza Servicio de Publicaciones

ISSN 2254-7606

#### **Tesis Doctoral**

# NUEVAS ESTRATEGIAS DE DISEÑO FPGA PARA LA IMPLEMENTACION DE FUNCIONES NO-CLONABLES FISICAMENTE EN ECOSISTEMAS IOT

#### Autor

### Guillermo Díez Señoráns

Director/es

Celma Pueyo, Santiago García Bosque, Miguel

#### UNIVERSIDAD DE ZARAGOZA Escuela de Doctorado

Programa de Doctorado en Física

2024

Nuevas estrategias de diseño FPGA para la implementación de funciones no-clonables físicamente en ecosistemas IoT

Guillermo Díez Señorans

# Nuevas estrategias de diseño FPGA para la implementación de funciones no-clonables físicamente en ecosistemas loT

Tesis presentada a la Universidad de Zaragoza para optar al grado de Doctor en Física por

D. Guillermo Díez Señorans

bajo la dirección de los doctores

Dr. Santiago Celma Pueyo

У

Dr. Miguel García Bosque

Departamento de Ingeniería Electrónica y Comunicaciones Instituto Universitario de Investigación en Ingeniería de Aragón Grupo de Diseño Electrónico

Diciembre de 2023

A mi padre y la memoria de mi madre.

# Agradecimientos

Querría dar las gracias en primer lugar a mis directores, Dr. Santiago Celma Pueyo y Dr. Miguel García Bosque, por su guía a lo largo de estos años, sin los cuales esta tesis doctoral hubiera sido imposible. Igualmente indispensable ha sido el apoyo de los doctores Dr. Carlos Sánchez Azqueta y Dr. Francisco Aznar Tabuenca, así como del resto de miembros del Grupo de Diseño Electrónico de la Universidad de Zaragoza, Óscar, Nicolás, Belén, Concha, Pedro y Pepe . Tampoco puedo dejar de agradecer a mis compañeros de despacho, Abel, Guillermo, Diego, Uxua, Antonio, Jorge(s) y Raúl, el haber hecho siempre más ameno y en ocasiones incluso fácil este doctorado.

De forma especial, agradezco a Laura, a mi padre José Blas y a mi hermana Aurora la paciencia y el cariño con el que me han esperado en el mundo exterior que —creo recordar— hay más allá de los muros de la facultad.

Por último, agradezco también a todas las instituciones que han financiado la investigación recogida en este trabajo: Agencia Estatal de Investigación, Fondo Europeo de Desarrollo Regional a través de los proyectos TEC2017-85867-R, RTC2019-007039-7 y PID2020-114110RA-I00; Gobierno de Aragón a través de la beca para la contratación de personal investigador predoctoral en formación 2018-2022.

# Listado de figuras

| 1.1 | Escítala, un primitivo sistema de criptografía por transposición descu-                                                   |    |

|-----|---------------------------------------------------------------------------------------------------------------------------|----|

|     | bierto en la Grecia clásica                                                                                               | 3  |

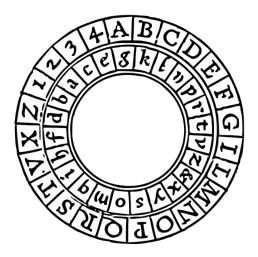

| 1.2 | Disco de Alberti. Primer cifrador polialfabético, en el que la rotación                                                   |    |

| 1 0 | del disco interior permite definir un alfabeto de sustitución diferente                                                   | 4  |

| 1.3 | Grabado anónimo francés de 1815, donde se caricaturiza el <i>cabinet noir</i> .  Procedente del Museo Carnavalet de París | 6  |

| 1 1 |                                                                                                                           |    |

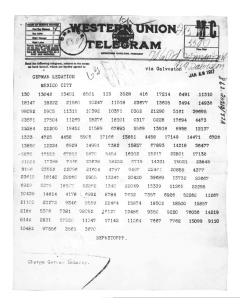

| 1.4 | Telegrama Zimmermann (U.S. National Archives Catalog)                                                                     | 8  |

| 1.5 | (a) Máquina de rotores de Hebern en el <i>National Cryptologic Museum</i>                                                 |    |

|     | de EUA. (b) Reproducción en detalle del sistema de rotores en una                                                         | 0  |

|     | máquina Enigma                                                                                                            | 9  |

| 2.1 | Esquema general de un criptosistema: en negro las posibles vías de                                                        |    |

|     | comunicación de Aurora a Blas, en rojo de Blas a Aurora; ambas sus-                                                       |    |

|     | ceptibles de ser interceptadas o modificadas por un adversario                                                            | 39 |

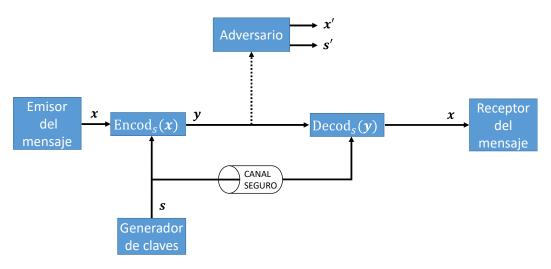

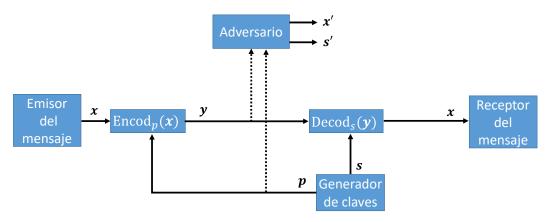

| 2.2 | Representación esquemática de una comunicación secreta cifrada con                                                        |    |

|     | un método de clave secreta. Un adversario es capaz de "romper" el                                                         |    |

|     | criptosistema si logra recuperar la clave secreta $(s'=s)$ y el mensaje                                                   |    |

|     | plano ( $x'=x$ )                                                                                                          | 45 |

| 2.3 | Representación esquemática de una comunicación secreta cifrada con                                                        |    |

|     | un método de clave pública. Este sistema se considera comprometido                                                        |    |

|     | si un adversario logra recuperar la clave secreta $(s^\prime=s)$ y el mensaje                                             |    |

|     | plano ( $x'=x$ )                                                                                                          | 46 |

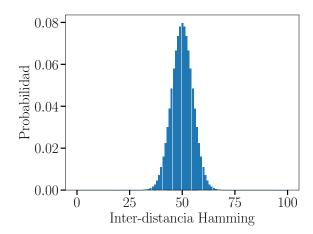

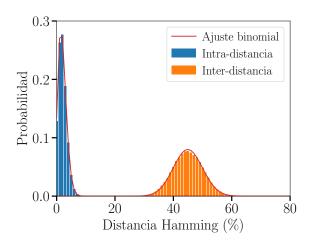

| 2.4 | Distribución de probabilidad de las inter-distancias de Hamming para                                                      |    |

|     | una PUF ideal                                                                                                             | 57 |

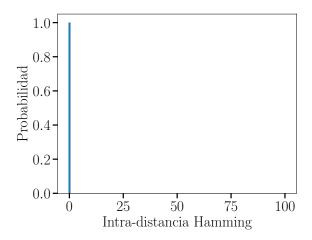

| 2.5 | Distribución de probabilidad de las intra-distancias de Hamming para                                                      |    |

|     | una PUF ideal                                                                                                             | 58 |

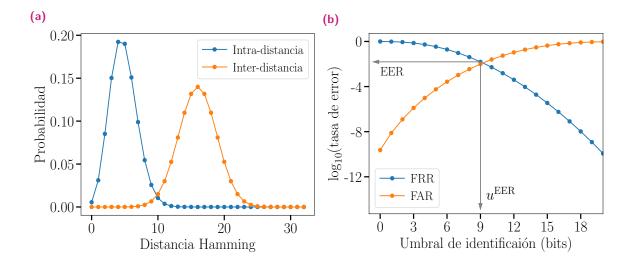

| 2.6 | Ejemplo de análisis de identificabilidad: (a) ajustes binomiales a las                                                    |    |

|     | distribuciones de intra/inter-distancias de Hamming; y (b) ejemplos de                                                    |    |

|     | curvas FAR/FRR. En ambos casos se ha destacado la tasa EER                                                                | 62 |

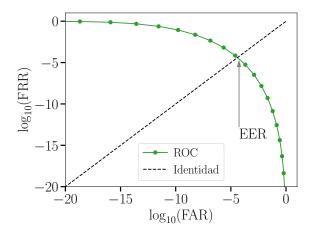

| 2.7 | Ejemplo de curva ROC para una función no-clonable físicamente, donde                                                      |    |

|     | se ha destacado la tasa EER                                                                                               | 63 |

| 2.8               | Histogramas de las intra/inter-distancias de Hamming simuladas con                                 |                         |

|-------------------|----------------------------------------------------------------------------------------------------|-------------------------|

|                   | un modelo PUF cuasi-ideal de parámetros $N_b=100$ , $p^{\rm intra}=0.02$ ,                         |                         |

|                   | $p^{\text{inter}} = 0.45$ , junto con las curvas binomiales esperadas                              | 66                      |

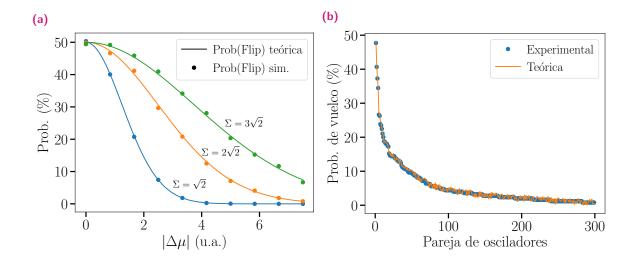

| 2.9               | (a) Simulación y curva de interpolación para las probabilidades del                                |                         |

|                   | vuelco de un bit, para tres valores $\Sigma$ de desviación combinada. (b)                          |                         |

|                   | Probabilidad teórica y experimental de la inversión de un bit para                                 |                         |

|                   | una matriz de osciladores de anillo. Las cantidades $ \Delta\mu $ y $\Sigma$ están                 |                         |

|                   | expresadas en unidades arbitrarias                                                                 | 71                      |

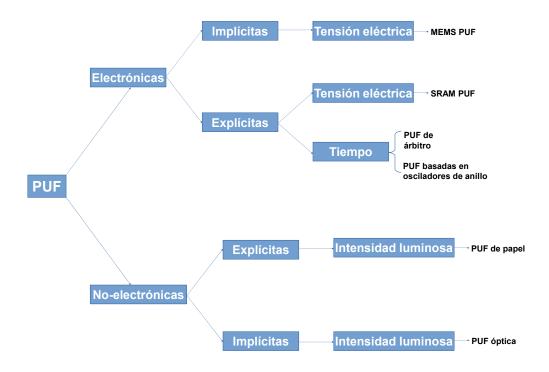

| 2.10              | Taxonomía parcial de las funciones no-clonables físicamente                                        | 77                      |

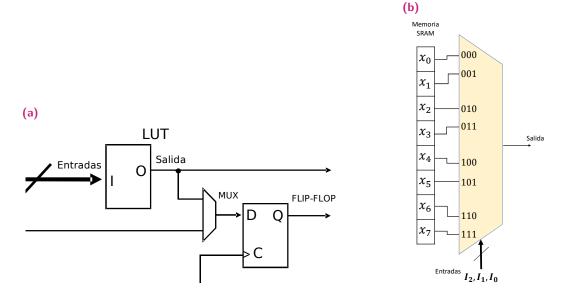

| 2.11              | (a) Esquema de celda lógica (LC) en FPGA. (b) Esquema de tabla de                                  |                         |

|                   | búsqueda (LUT) de tres entradas                                                                    | 86                      |

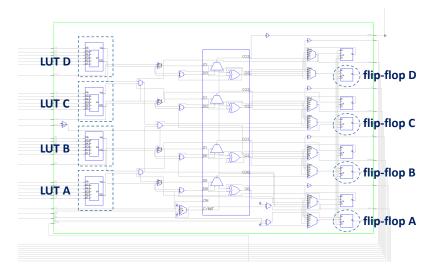

| 2.12              | Detalle de una slice. Se han destacado los recursos que se implementan                             |                         |

|                   | en detalle (LUT y flip-flop)                                                                       | 88                      |

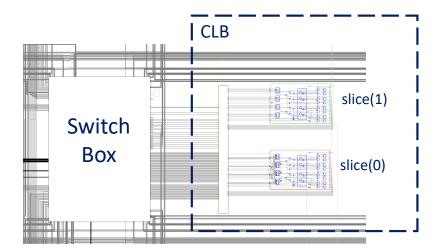

| 2.13              | Representación esquemática de los recursos de un bloque lógico confi-                              |                         |

|                   | gurable (CLB)                                                                                      | 89                      |

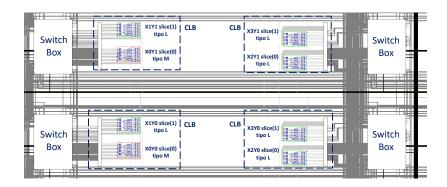

| 2.14              | Representación esquemática de los recursos de una FPGA detallando                                  |                         |

|                   | la disposición de cuatro CLB con sus respectivas cajas de conexiones a                             |                         |

|                   | izquierda y a derecha.                                                                             | 89                      |

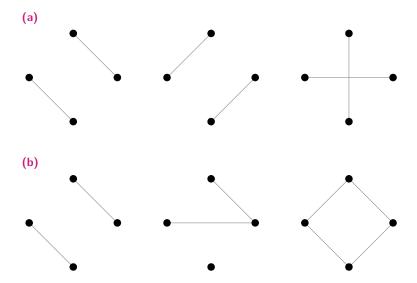

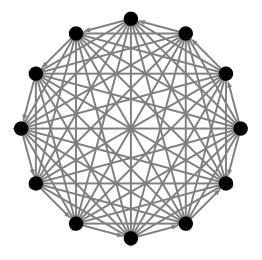

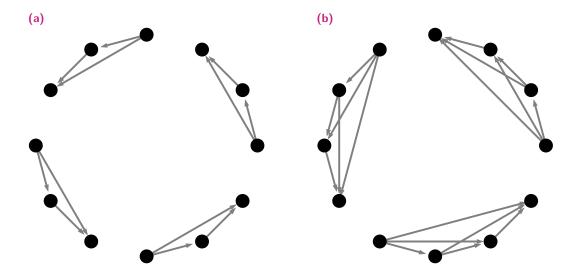

| 3.1               | Ejemplo de grafos pertenecientes a una misma topología de $N=4$                                    |                         |

| 5.1               | vértices: (a) equivalentes y (b) no-equivalentes. Cada punto (vértice)                             |                         |

|                   | representa una celda y cada enlace (arista) una comparación, i.e., un                              |                         |

|                   | bit de salida.                                                                                     | 95                      |

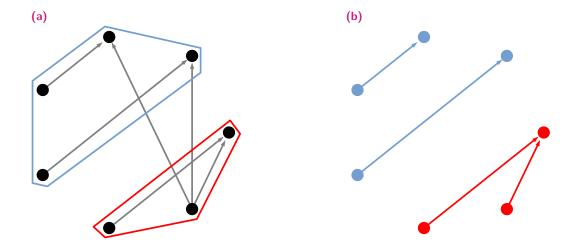

| 3.2               | (a) Topología modular $\mathcal{T}_7$ de $N=7$ vértices, donde se han destacado                    | 75                      |

| 0.2               | dos módulos inconexos $\mathcal{T}_4'$ de $N=4$ vértices (cuadro azul), y $\mathcal{T}_3''$ de     |                         |

|                   | $N=3$ vértices (cuadro rojo). (b) Topologías $\mathcal{T}_4'$ y $\mathcal{T}_3''$ representadas de |                         |

|                   | $-1$ $-3$ vertices (educato 10)0). (b) Topologico $7_A$ y $7_3$ Tepresentudos de                   |                         |

|                   |                                                                                                    | 96                      |

| 3.3               | forma independiente                                                                                | 96                      |

| 3.3               | forma independiente                                                                                |                         |

|                   | forma independiente                                                                                | 97                      |

| 3.4               | forma independiente                                                                                | 97<br>100               |

| 3.4<br>3.5        | forma independiente                                                                                | 97<br>100               |

| 3.4               | forma independiente                                                                                | 97<br>100               |

| 3.4<br>3.5        | forma independiente                                                                                | 97<br>100<br>102        |

| 3.4<br>3.5        | forma independiente                                                                                | 97<br>100<br>102        |

| 3.4<br>3.5<br>3.6 | forma independiente                                                                                | 97<br>100<br>102<br>106 |

| 3.4<br>3.5<br>3.6 | forma independiente                                                                                | 97<br>100<br>102<br>106 |

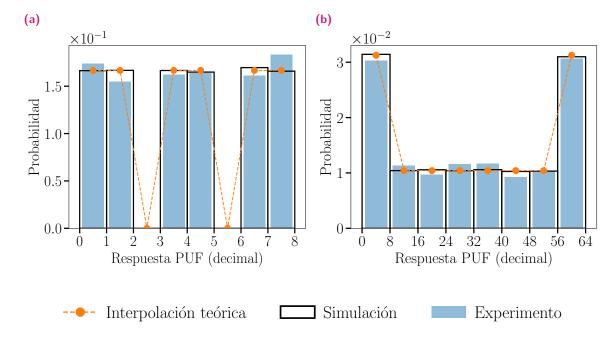

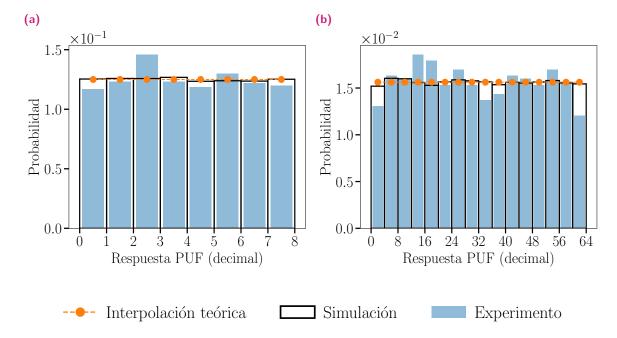

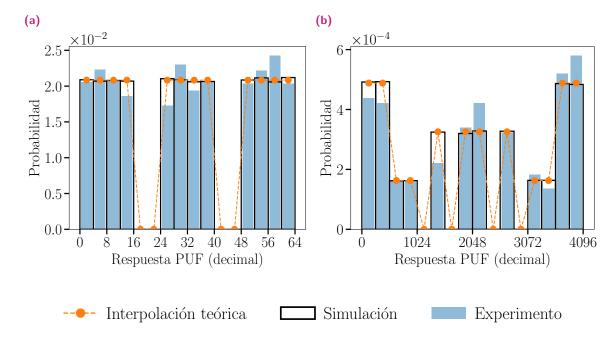

| 3.9  | Histogramas de las respuestas para la topología $\mathcal{N}_{/2}$ con $N=6$ celdas   |

|------|---------------------------------------------------------------------------------------|

|      | (a) y $N=12$ celdas (b), obtenidos mediante simulación y medición                     |

|      | experimental, superpuestos sobre la distribución teórica esperada 112                 |

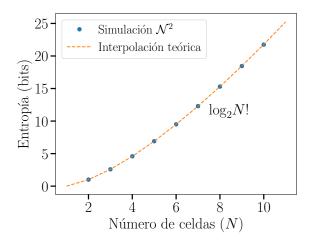

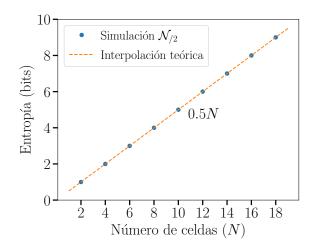

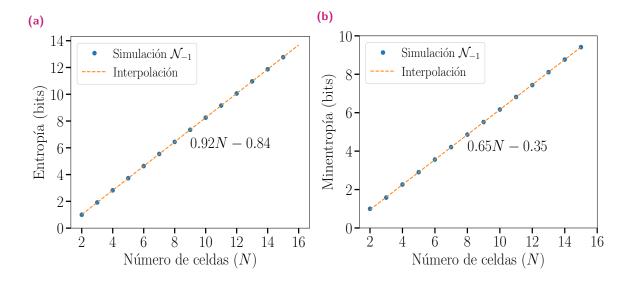

| 3.10 | Entropía entregada por la topología $\mathcal{N}_{/2}$ en función del número $N$ de   |

|      | celdas físicas del sistema, junto con la curva de interpolación teórica 113           |

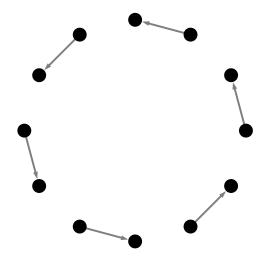

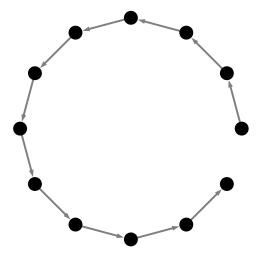

| 3.11 | Grafo típico representante de la topología $\mathcal{N}_{-1}$ con $N=12$              |

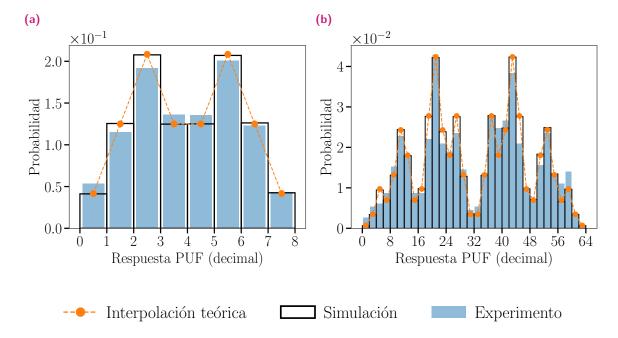

| 3.12 | Histogramas de las respuestas para la topología $\mathcal{N}_{-1}$ con $N=4$ celdas   |

|      | (a) y $N=7$ celdas (b), obtenidos mediante simulación y medición                      |

|      | experimental, superpuestos sobre la distribución teórica esperada 117                 |

| 3.13 | Entropía (a) y minentropía (b) entregada por la topología $\mathcal{N}_{-1}$ en       |

|      | función del número $N$ de celdas físicas del sistema, junto con las curvas            |

|      | de interpolación teórica correspondientes                                             |

| 3.14 | Grafo típico representante de la topología $\mathcal{N}_{/K}^2$ para los casos $K=3$  |

|      | (a) y $K = 4$ (b), con $N = 12$                                                       |

| 3.15 | Histogramas de las respuestas para la topología $\mathcal{N}_{/K}^2$ con $K=3$ celdas |

|      | por módulo, $N=6$ celdas (a) y $K=4$ celdas por módulo, $N=8$                         |

|      | celdas (b), obtenidos mediante simulación y medición experimental,                    |

|      | superpuestos sobre la distribución teórica esperada                                   |

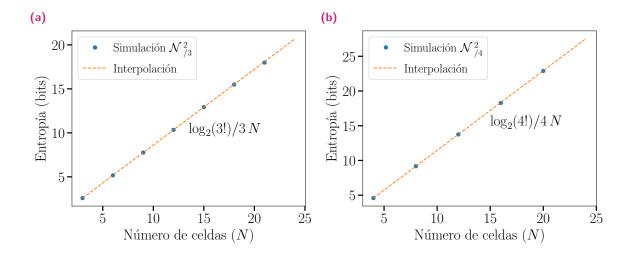

| 3.16 | Entropía entregada por la topología $\mathcal{N}_{/K}^2$ con $K=3$ (a) y $K=4$ (b),   |

|      | en función del número $N$ de celdas físicas del sistema, junto con las                |

|      | curvas de interpolación teórica correspondientes                                      |

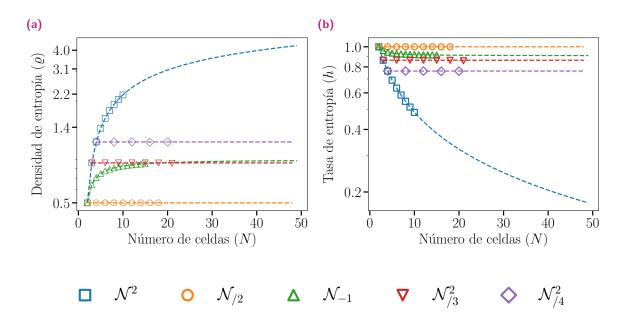

| 3.17 | (a) Densidad de entropía y (b) tasa de entropía para cada topología                   |

|      | estudiada (marcadores), junto con sus curvas de interpolación (líneas                 |

|      | discontinuas)                                                                         |

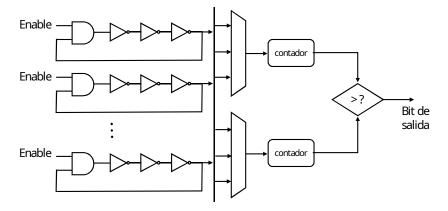

| 4.1  | Esquema de una función no-clonable físicamente basada en osciladores                  |

| 1.1  | de anillo                                                                             |

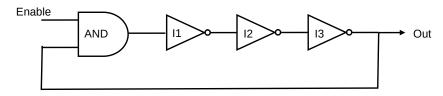

| 4.2  | Esquema de un oscilador de anillo de tres etapas                                      |

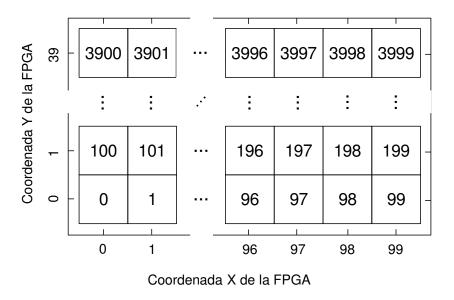

| 4.3  | Definición de los índices de los osciladores y su localización esquemática            |

| 1.0  | en la FPGA                                                                            |

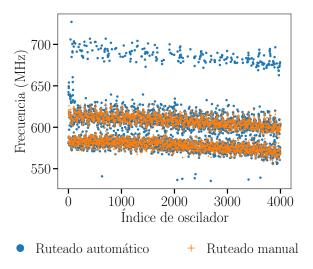

| 4.4  | Frecuencia de los osciladores frente al índice asignado con el ruteado                |

| 1• 1 | automático seleccionado por la herramienta de diseño (azul), y fijado                 |

|      | de manera manual (naranja)                                                            |

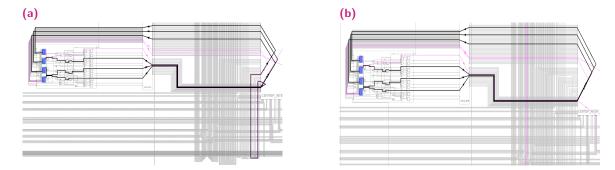

| 4.5  | (a) Oscilador de anillo implementado próximo al borde de la matriz                    |

|      | FPGA. (b) Oscilador implementado en una posición alejada del borde.                   |

|      | Notar la diferencia en el ruteado                                                     |

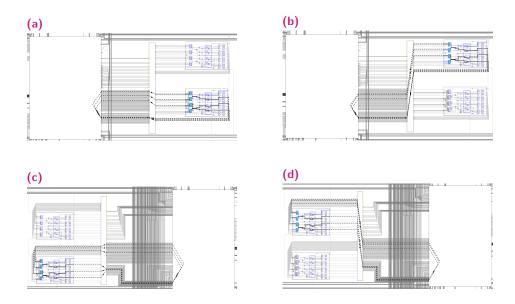

| 4.6  | Posibles configuraciones para el tipo de slice y orientación del CLB: (a)             |

|      | 0, D; (b) 1, D; (c) 0, I; (d) 1, I                                                    |

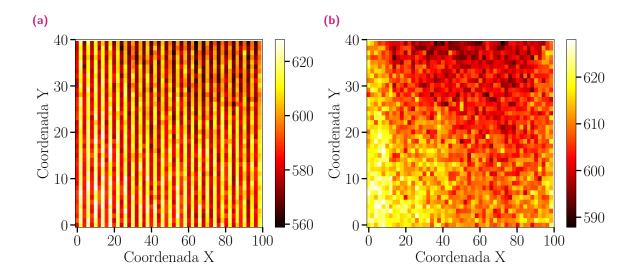

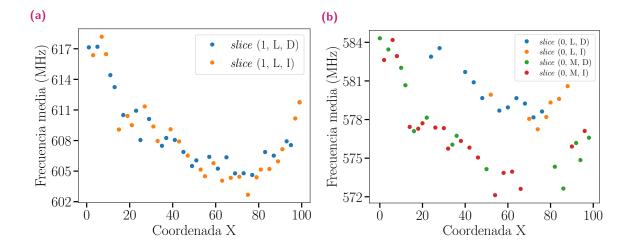

| 4.7  | Frecuencia de los osciladores en función de su posición sobre la FPGA             |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | para: (a) cualquier tipo de CLB ocupado en orden; (b) sólo slice (1)              | 137 |

| 4.8  | Frecuencia promedio de los osciladores en función del tipo de slice               |     |

|      | en la cual se ubican: (a) slice (0), (b) slice (1). Los resultados se han         |     |

|      | destacado también atendiendo al tipo de LUT (L/R) y su orientación                |     |

|      | (I/D)                                                                             | 138 |

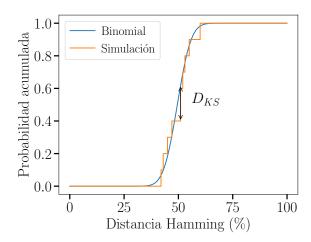

| 4.9  | Distancia de Kolmogorov-Smirnov ( $D_{KS}$ ) entre la distribución binomial       |     |

|      | acumulada de parámetros $n=100,p=0.5,$ y una muestra aleatoria                    |     |

|      | binomial                                                                          | 141 |

| 4.10 | Distribuciones de la distancia de Kolmogorov-Smirnov para: (a) la                 |     |

|      | inter-distancia y (b) la intra-distancia en un experimento PUF simulado           |     |

|      | siguiendo un modelo cuasi-ideal. En las figuras se han superpuesto las            |     |

|      | densidades de probabilidad utilizadas para interpolar los histogramas,            |     |

|      | y se han marcado los umbrales de significancia $\alpha = 5\%$                     | 142 |

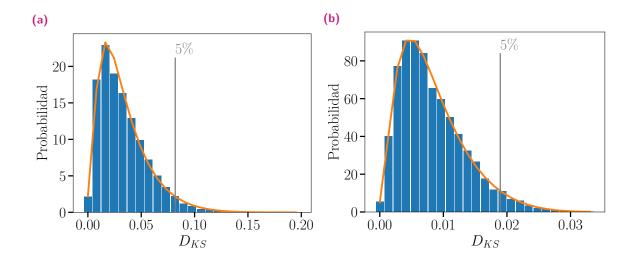

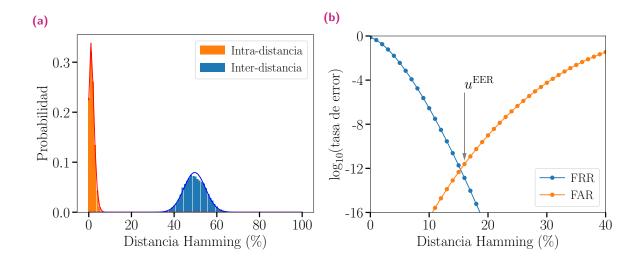

| 4.11 | Métricas de la estrategia de selección <i>Óptima</i> : (a) distribuciones de la   |     |

|      | intra/inter-distancias de Hamming, (b) curvas FAR y FRR, donde se ha              |     |

|      | destacado el umbral de identificación $u^{\mathrm{EER}}$                          | 145 |

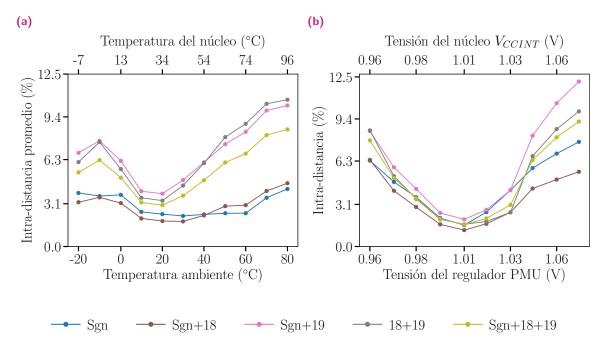

| 4.12 | Evolución de la intra-distancia de Hamming promedio frente a la tempe-            |     |

|      | ratura ambiente y del núcleo, con temperatura ambiente de referencia              |     |

|      | $T_0 \equiv 20$ °C                                                                | 147 |

| 4.13 | Detalle del módulo de control de la alimentación (PMU) utilizado en la            |     |

|      | placa PYNQ-Z2 para alimentar el chip FPGA, destacando la red resistiva            |     |

|      | que acopla la salida SW1 del PMU con la entrada de potencia V <sub>CCINT</sub> al |     |

|      | núcleo FPGA                                                                       | 147 |

| 4.14 | Evolución de la intra-distancia de Hamming promedio con respecto la               |     |

|      | tensión del regulador y del núcleo, con una tensión de referencia del             |     |

|      | núcleo $V_0 = 1.01 \mathrm{V.}$                                                   | 149 |

| 4.15 | Representación binaria de la diferencia entre dos medidas de frecuencia           |     |

|      | utilizando 32 bits                                                                | 150 |

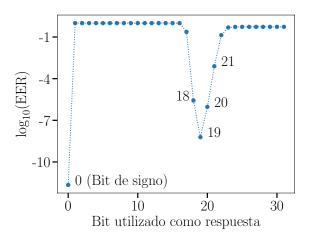

| 4.16 | Tasa de igual error (EER) para las respuestas utilizando cada uno de              |     |

|      | los 32 canales bit estudiados                                                     | 152 |

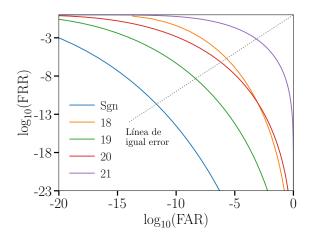

| 4.17 | Curvas ROC para las respuestas generadas por los bits más prometedo-              |     |

|      | res, junto con la identidad (equal error line), que corta cada curva ROC          |     |

|      | en su correspondiente tasa de error EER. Un valor EER menor implica               |     |

|      | una mayor identificabilidad                                                       | 152 |

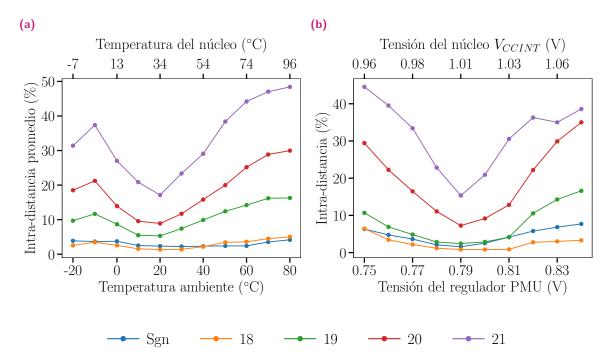

| 4.18 | Análisis "V" para las respuestas generadas por los bits más prometedo-            |     |

|      | res: (a) variaciones de temperatura, (b) variaciones en la tensión de             |     |

|      | alimentación                                                                      | 153 |

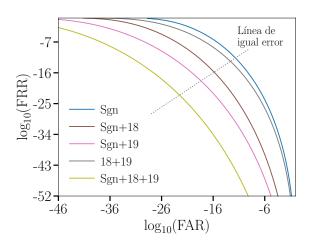

| 4.19 | Curvas ROC para las respuestas generadas por las combinaciones de          |

|------|----------------------------------------------------------------------------|

|      | bits más prometedoras, junto con la identidad (equal error line) 154       |

| 4.20 | Análisis "V" para las respuestas generadas por las combinaciones de        |

|      | bits más prometedoras: (a) variaciones de temperatura, (b) variaciones     |

|      | en la tensión de alimentación                                              |

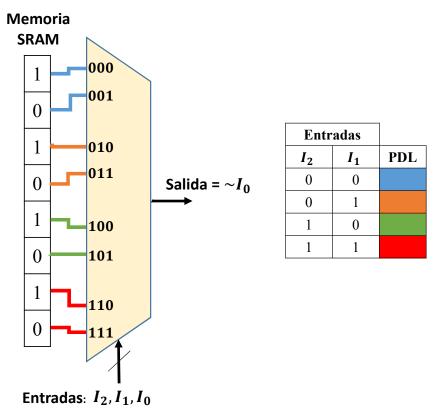

| 4.21 | Representación esquemática de una LUT de tres entradas actuando            |

|      | como inversor de la entrada $I_0$ . Se han destacado en diferentes colores |

|      | cada una de las distintas PDL configurables físicamente mediante los       |

|      | pines $I_2$ e $I_1$                                                        |

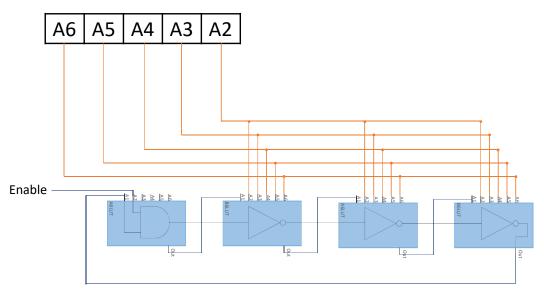

| 4.22 | Esquema conceptual de oscilador de anillo de tres etapas en FPGA,          |

|      | donde se ilustra la disposición de las entradas para la configuración de   |

|      | PDL en cada una de las LUT inversoras del oscilador                        |

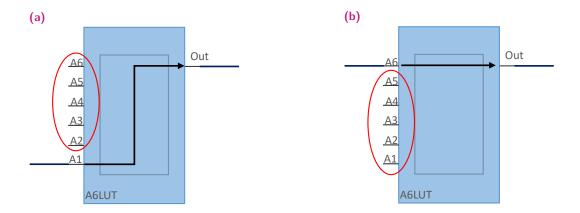

| 4.23 | (a) Inversor implementado en una LUT utilizando el puerto A1 como          |

|      | propagador. (b) Ídem, utilizando el puerto A6 como propagador. En          |

|      | rojo se han destacado los puertos utilizados para configurar las PDL en    |

|      | cada caso                                                                  |

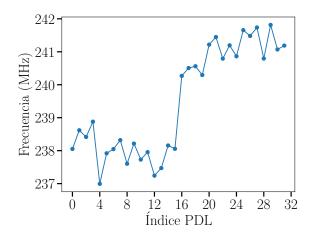

| 4.24 | Curva frecuencia-PDL obtenida al medir la frecuencia característica de     |

|      | un oscilador de anillo para cada posible línea PDL                         |

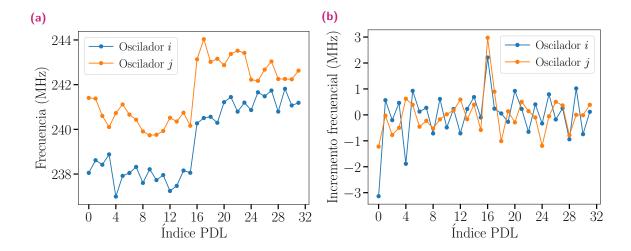

| 4.25 | Medida de dos osciladores de anillo empleando la entrada LUT A1 y          |

|      | configurados mediante PDL: (a) frecuencia de oscilación, (b) derivada      |

|      | de la frecuencia respecto del índice PDL                                   |

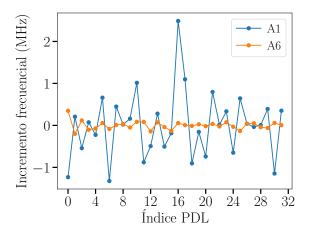

| 4.26 | Incremento frecuencial respecto del índice de selección PDL para un        |

|      | oscilador de anillo. Se muestran conjuntamente dos diseños diferentes      |

|      | para ilustrar la magnitud de las variaciones inducidas en cada caso 159    |

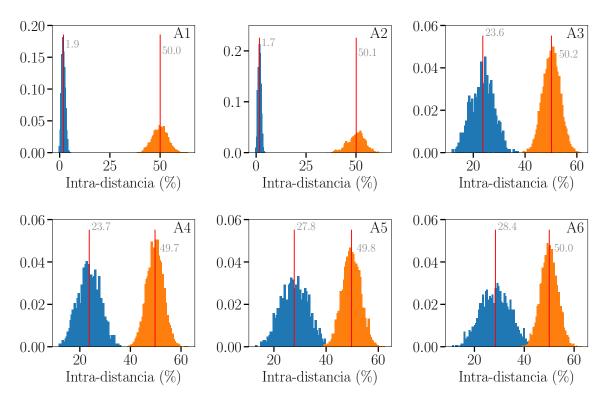

| 4.27 | Distribución de la intra- (azul) e inter- (naranja) distancias de Hamming  |

|      | para cada una de las implementaciones estudiadas A1 - A6 162               |

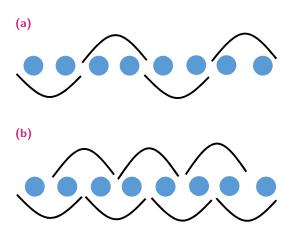

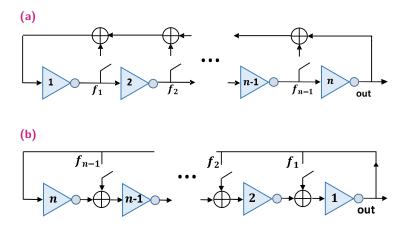

| 5.1  | Esquema de: (a) oscilador de anillo de Fibonacci, (b) oscilador de anillo  |

|      | de Galois                                                                  |

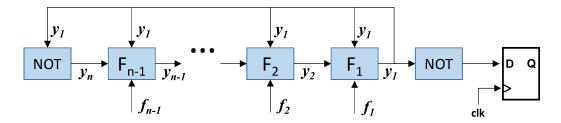

| 5.2  | Esquema de un oscilador de anillo de Galois implementado en FPGA,          |

|      | utilizando $n+1$ LUT y un flip-flop                                        |

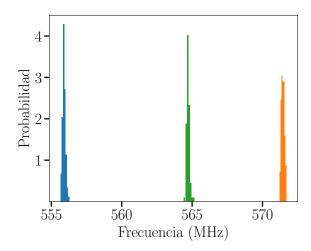

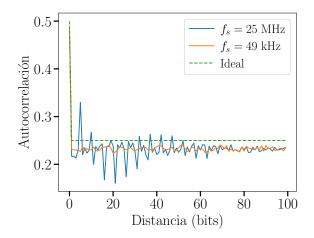

| 5.3  | Curvas de autocorrelación para diferentes frecuencias de un oscilador      |

|      | de anillo de Galois de 7 etapas implementado en FPGA 169                   |

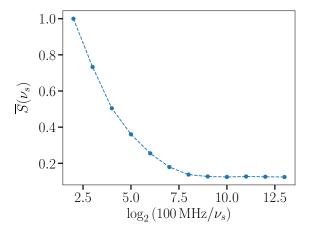

| 5.4  | Área promedio contenida bajo la curva de autocorrelación de 100            |

|      | anillos de Galois implementados en FPGA, frente a la frecuencia de         |

|      | muestreo; un valor inferior representa una longitud de autocorrelación     |

|      | promedio menor                                                             |

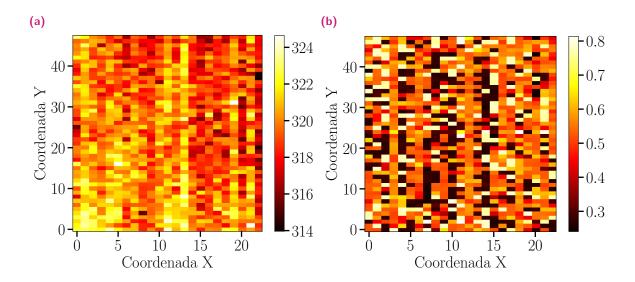

| 5.5 | (a) Mapa de frecuencia característica de una matriz de osciladores de     |

|-----|---------------------------------------------------------------------------|

|     | anillo estándar de 7 etapas; (b) mapa de sesgo de la misma matriz         |

|     | formada por anillos de Galois de 7 etapas, ubicados en las mismas         |

|     | posiciones que sus homólogos estándar                                     |

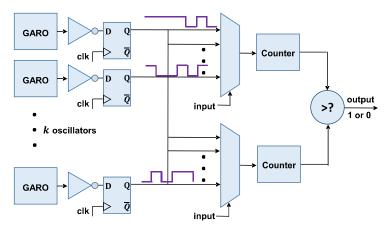

| 5.6 | Esquema de una PUF basada en osciladores de anillo de Galois: GARO-       |

|     | PUF                                                                       |

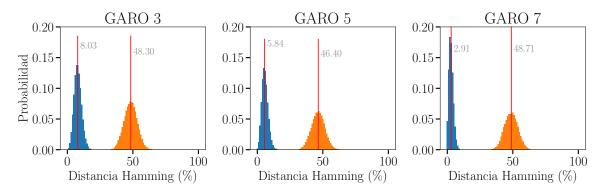

| 5.7 | Distribución de la intra- (azul) e inter- (naranja) distancias de Hamming |

|     | para cada una de las arquitecturas estudiadas: GARO 3, 5 y 7 etapas 176   |

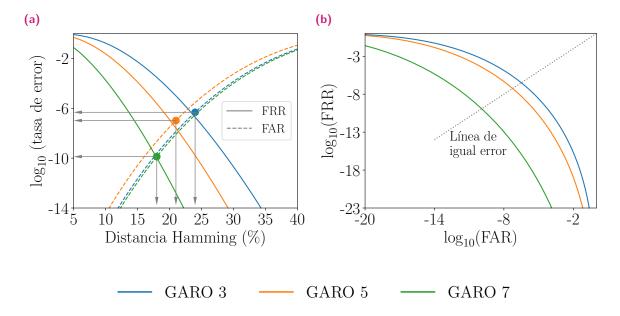

| 5.8 | (a) Curvas FAR y FRR para cada arquitectura GARO, donde se ha desta-      |

|     | cado el punto de intersección y sus correspondientes coordenadas en       |

|     | el eje de umbral de identificación (abscisas) y tasa de error (ordena-    |

|     | das). (b) Curva característica operativa del receptor (ROC) para cada     |

|     | arquitectura                                                              |

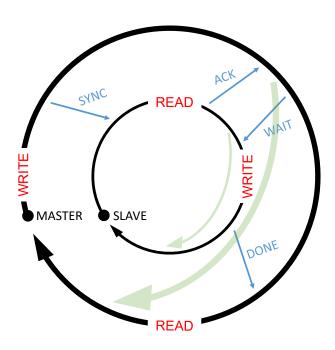

| C.1 | Bucle de comunicación master-slave utilizando un protocolo handshake. 207 |

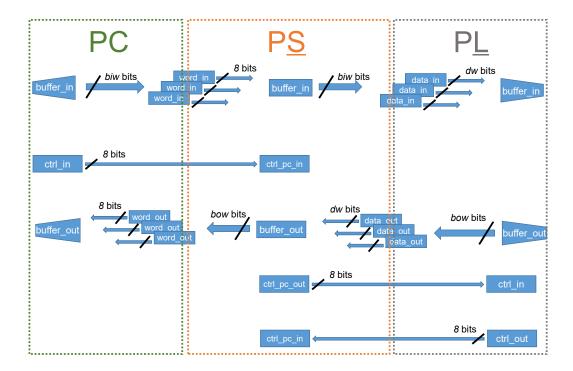

| D.1 | Representación esquemática de la interfaz de comunicación PC – FPGA. 210  |

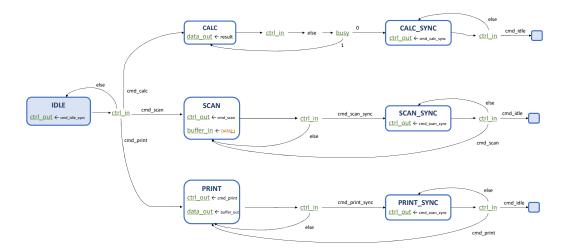

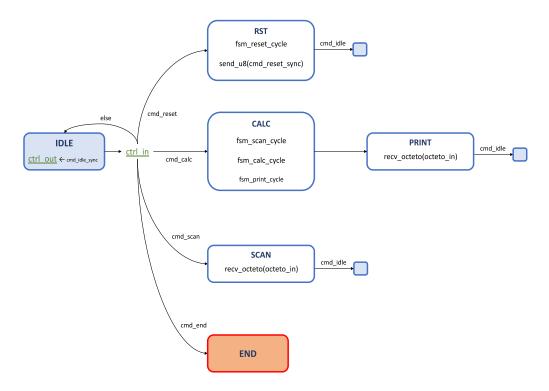

| D.2 | Máquina de estados para implementar interfaz en el lado de la lógica      |

|     | programable (FPGA Artix 7 )                                               |

| D.3 | Máquina de estados para implementar interfaz en el lado del sistema       |

|     | de procesamiento (microprocesador ARM Cortex-A9 ) 212                     |

# Listado de tablas

| 2.1 | Todos los posibles resultados de los sumandos dados en (2.77) 53                                    |

|-----|-----------------------------------------------------------------------------------------------------|

| 2.2 | Acción combinada del código de repetición y un código de sustracción                                |

|     | en la intra-distancia promedio (%) de una PUF de osciladores de anillo.                             |

|     | Los valores de la tabla se han representado como un mapa de color                                   |

|     | para facilitar la comparación de los códigos ECC utilizados 73                                      |

| 2.3 | Entradas LUT para las cuales el número de nodos de conexionado es                                   |

|     | mínimo dentro de un mismo CLB                                                                       |

| 3.1 | Comparativa del coste ( $\mathcal{C}$ ) y mincoste ( $\mathcal{C}^m$ ) para cada topología estudia- |

|     | da en el límite asintótico $N \to \infty$ , en función del parámetro de diseño                      |

|     | $\alpha$                                                                                            |

| 4.1 | Frecuencia promedio en función del tipo de slice (0/1), el tipo de LUT                              |

|     | (L/M) y la orientación del CLB (I/D) de los osciladores implementados. 139                          |

| 4.2 | Inter-distancia de Hamming promedio para cada estrategia estudiada                                  |

|     | de selección de osciladores                                                                         |

| 4.3 | Intra-distancia de Hamming promedio para cada estrategia de selección                               |

|     | de osciladores estudiada                                                                            |

| 4.4 | Umbral de identificación ( $u^{\rm EER}$ ) y tasas de error (EER) para cada estra-                  |

|     | tegia estudiada                                                                                     |

| 4.5 | Intra/inter-distancias de Hamming más significativas para cada uno de                               |

|     | los 32 canales bit estudiados                                                                       |

| 4.6 | Comparativa de la desviación estándar promedio del incremento fre-                                  |

|     | cuencial debida al ruido aleatorio frente a la selección PDL 161                                    |

| 4.7 | Intra/inter-distancia de Hamming promedio                                                           |

| 5.1 | Desviación estándar de diferentes osciladores                                                       |

| 5.2 | Resultado del análisis de unicidad llevado a cabo sobre cada arquitectu-                            |

|     | ra GARO estudiada                                                                                   |

| 5.3 | Intra-distancia de Hamming promedio obtenidas para cada arquitectura                                |

|     | GARO estudiada                                                                                      |

| 5.4 | Resultados del análisis de identificabilidad para cada arquitectura |     |

|-----|---------------------------------------------------------------------|-----|

|     | GARO-PUF estudiada                                                  | 178 |

## Listado de acrónimos

ADC Analog-Digital Converter.

**AES** Advanced Encryption Standard.

ASCII American Standard Code for Infor-

mation Interchange.

ASIC Application Specific Integrated Cir- HD Hamming Distance.

cuit.

**AXI** Advanced Extensible Interface.

**BEL** Basic Element.

biw Buffer-in Width. bow Buffer-out Width.

**CCA** Chosen-ciphertext Attack.

CIA Central Intelligence Agency.

**CLB** Configurable Logic Block.

**CMOS** Complementary Metal-Oxide-

Semiconductor.

**COTS** Commercial Off-the-shelf.

**CPA** Chosen-plaintext Attack.

**CPU** Central Processing Unit.

**CRP** Challenge-Response pair.

**DAC** Digital-Analog Converter.

**DES** Data Encription Standard.

**DPA** Differential Power Analysis.

**DSA** Digital Signature Algorithm.

dw Data Width.

**ECC** Error Correcting Code.

**EDA** Electronics Design Automation.

**EER** Equal Error Rate.

**FAR** False Acceptance Rate.

FIA Fault Injection Attack.

FIFO First-In-First-Out.

FPGA Field Programmable Gate Array.

FRR False Rejection Rate.

**GARO-PUF** Galois Ring Oscillator PUF.

GC&CS Government Code and Cipher

School.

**GPU** Graphic Processing Unit.

hd Helper Data.

HDL Hardware Description Language.

**IoT** Internet of Things.

KCA Known-ciphertext Attack.

KPA Known-plaintext Attack.

LC Logic Cell.

LFSR Linear Feedback Shift Register.

LUT Look-up Tables.

MAC Message Authentication Code.

MEMS Micro-Electro-Mechanical Sys-

tem.

MITM Man-In-The-Middle.

**MOSFET** Metal-Oxide-Semiconductor

Field Effect Transistor.

NBS National Bureau of Standards.

NIST National Institute of Standards and

Technology.

NRE Nonrecurring Engineering Costs.

**NVM** Non-volatile Memory.

**OTP** One-time Password.

PDL Programmable Delay Lines.

PL Programmable Logic.

PMU Power Management Unit.

POK Physically Obfuscated Keys.

**PS** Processing System.

**PUF** Physically Unclonable Function.

**RO-PUF** Ring Oscillator PUF.

ROC Receiver-Operating Characteris- STT-MRAM Spin Torque Transfer Magnetic.

**RoT** Root of Trust.

RRAM Resistive Random Access Me-

**RTN** Random Telegraph Noise.

SCA Side Channel Attack.

**SDK** Software Development Kit.

SoC System-on-Chip.

SRAM Static Random Access Memory.

tic Random Access Memory.

**TEMPEST** Telecommunication Electronic Material Protected from Emanating Spurious Transmissions.

TRNG True Random Number Generator.

**UART** Universal Asynchronous Receiver-Transmitter.

## Listado de símbolos

Prob Probabilidad.

- \* Operador AND lógico.

- R(L) Autocorrelación de una secuencia de bits a longitud L.

- R(0) Sesgo de una secuencia de bits.

- O "O grande" de Landau.

- $Bin_{n,p}$  Distribución binomial de n número de ensayos y sesgo p.

- bit(i, j) Bit extraído mediante la medida compensada de las celdas físicas "i" y "j".

- I Cantidad de información.

- $\theta$  Condición ambiental (abstracta) en la que se evalúa una función físi-

- C Coste de una topología PUF.

- Decod Función de decodificación binaria.

- $\equiv$  Definición.

- *ρ* Densidad de entropía por celda.

- $\rho^{\mathbf{m}}$  Densidad de minentropía por celda.

- dist Distancia métrica.

- $D_{KS}$ Distancia de Kolmogorov-Smirnov.

- Encod Función de codificación binaria. H Entropía.

- $\xi$  Estímulo físico de una función física.

- FA Evento de que se produzca una falautenticación.

- FR Evento de que se produzca un falso rechazo en un proceso de autenticación.

- FAR Tasa de falsa aceptación en función del umbral de identificación.

- $\mathcal{F}$  Función física.

Firma Aplicación de firma digital.

- Flip Evento de que se produzca la inversión de un bit al repetir sucesivamente dos medidas de una misma instancia PUF.

- $\nu$  Frecuencia de oscilación.

- $\nu^{\text{ref}}$  Frecuencia de referencia (reloj).

- $\nu_s$  Frecuencia de muestreo de un oscilador de Galois.

- FRR Tasa de falso rechazo en función del umbral de identificación.

- Enroll Función que extrae el identificador de referencia de una PUF.

- HD Distancia de Hamming.

Hash Función hash.

- $\mathbf{hd}_{ii}^{\mathcal{P}}$  Síndrome de la *i*-ésima instancia PUF, j-ésimo reto.

- $\lambda$  Índice de fabricación de una función física

- ECC Aplicación de corrección de erro-  $\mathrm{HD}^{\mathrm{inter}}_{ii'jk}$  Inter-distancia de Hamming entre las instancias i, i' para el jésimo reto y la k-ésima repetición.

- sa aceptación en un proceso de  $\mathrm{HD}^{\mathrm{intra}}_{ijkk'}$  Intra-distancia de Hamming entre las repeticiones k, k' para la

- i-ésima instancia y el j-ésimo re-

- $\mathrm{HD}^{\mathrm{intra-env}}_{ijkk'll'}$  Intra-distancia entre las respuestas obtenidas en diferentes condiciones ambientales l, l'.

- MAC Función MAC.

- $C^{\mathbf{m}}$  Mincoste de una topología PUF.

- $H^{\mathbf{m}}$  Minentropía.

- $\mu^{\text{inter}}$  Inter-distancia media.

- $u^{intra}$  Intra-distancia media.

- $N_b$  Número de bits de un vector bina-

- $N^{\text{inst}}$  Número de instancias que participan en un experimento PUF.

- $Norm_{\mu,\sigma}$  Densidad de probabilidad normal de media  $\mu$  y desviación

- $N^{\text{rep}}$  Número de repeticiones de cada medida en un experimento PUF.

- $N^{

m retos}$  Número de retos que utilizados en un experimento PUF.

- distancia de dos bits valga "1".

- $p^{intra}$  Probabilidad de que la intradistancia de dos bits valga "1".

- × Producto cartesiano.

- P Función no-clonable físicamente.

- DAC Interfaz decodificadora de una PUF.

- ADC Interfaz codificadora de una PUF.

- $\vec{y}_{ii}^{\mathcal{P}}$  Identificador de referencia de una PUF para la *i*-ésima instancia, *j*ésimo reto.

- $\vec{y}_{ijk}^{\mathcal{P}}$  Respuesta binariade una PUF para la i-ésima instancia, j-ésimo reto, k-ésima repetición.

- $ec{y}_{ijkl}^{\mathcal{P}}$  Respuesta de la PUF  $\mathcal{P}$  para la i-  $\mathcal{T}$  Topología abstracta de una PUF de meésima instancia, j-ésimo reto, k-

- ésima repetición, l-ésima condición ambiental.

- $q^{inst}$  Probabilidad de que el bit nominal de una respuesta PUF valga "1".

- q<sup>rep</sup> Probabilidad de que un bit se invierta al repetir una medida PUF.

- $\delta \tilde{\nu}^{\, \text{min}}$  Resolución de una medición de frecuencia.

- $\psi$  Respuesta física de una función físi-

- ≡ Espacio de estímulos físicos de una función física.

- **Λ** Espacio de índices de fabricación de una función física.

- Dinter Conjunto de inter-distancias medidas en un determinado experimento PUF.

- D<sup>intra</sup> Conjunto de intra-distancias medidas en un determinado experimento PUF.

- $p^{\text{inter}}$  Probabilidad de que la inter-  $D^{\text{intra-env}}$  Conjunto de intra-distancias medidas en un determinado experimento PUF ampliado para contener medidas ambientales.

- $\mathbf{Y}^{\mathcal{P}}$  Conjunto de respuestas medidas durante la evaluación experimental de la PUF  $\mathcal{P}$ .

- $\mathbf{Y}^{\mathcal{P}*}$  Experimento PUF ampliado para incluir medidas en diferentes condiciones ambientales.

- $\Psi$  Espacio de respuestas físicas de una función física.

- h Tasa de entropía por bit.

- $h^{\mathbf{m}}$  Tasa de minentropía por bit.

- dida compensada.

- $u^{ extsf{EER}}$  Distancia umbral de identificación  $\mathcal{N}^2$  Topología completa de una PUF de correspondiente a una "tasa de igual error" para una PUF.

- $u^{ ext{id}}$  Distancia umbral de identificación pa-  $\mathcal{N}_{/K}^2$  Topología modular en grupos de Kra una PUF.

- dera aceptación en un proceso de autenticación.

- dero rechazo en un proceso de autenticación.

Verif Función de verificación.

⊕ Operador XOR lógico.

- medida compensada (todas las comparaciones).

- celdas.

- **VA** Evento de que se produzca una verda-  $\mathcal{N}_{-1}$  Topología de una PUF de medida compensada repitiendo una celda en cada comparación.

- ${

m VR}$  Evento de que se produzca un verda-  ${\cal N}_{/2}~$  Topología one-out-of-2 de una PUF de medida compensada (sin repetición de celdas en cada comparación).

# Índice general

| Li | stado | de fig | uras                                                     |    |    | IX  |

|----|-------|--------|----------------------------------------------------------|----|----|-----|

| Li | stado | de tab | olas                                                     |    |    | ΧV  |

| Li | stado | de acr | rónimos                                                  |    | X  | VII |

| Li | stado | de sín | nbolos                                                   |    | X  | ΧIX |

| Ín | dice  | genera | .1                                                       |    | XX | III |

| 1  | Intr  | oducci | ón                                                       |    |    | 1   |

|    | 1.1   | Breve  | historia de la criptografía                              |    |    | 1   |

|    |       | 1.1.1  | Criptografía clásica                                     |    |    | 1   |

|    |       | 1.1.2  | Criptografía moderna                                     |    |    | 10  |

|    |       | 1.1.3  | Criptografía física y estado de la técnica               |    |    | 12  |

|    | 1.2   | Motiv  | ración y objetivos                                       |    |    | 13  |

|    |       | 1.2.1  | Introducción y antecedentes de las funciones no-clonable | 28 |    |     |

|    |       |        | físicamente                                              |    |    | 14  |

|    |       | 1.2.2  | Internet de las cosas - IoT                              |    |    | 17  |

|    |       | 1.2.3  | Objetivos de la tesis                                    |    |    | 18  |

|    | 1.3   | Estruc | ctura de la tesis                                        |    | •  | 20  |

| 2  | Defi  | nicion | es y conceptos básicos                                   |    | :  | 23  |

|    | 2.1   | Teoría | a de la información                                      |    |    | 23  |

|    |       | 2.1.1  | Contenido de información                                 |    |    | 24  |

|    |       | 2.1.2  | Entropía                                                 |    |    | 30  |

|    | 2.2   | Segur  | idad de la información                                   |    |    | 33  |

|    |       | 2.2.1  | Minentropía                                              |    |    | 34  |

|    |       | 2.2.2  | Criptología                                              |    |    | 38  |

|    | 2.3   | Funcio | ones no-clonables físicamente                            |    |    | 50  |

|    |       | 2.3.1  | Unicidad                                                 | •  |    | 54  |

|    |       | 2.3.2  | Reproducibilidad                                         |    |    | 57  |

|   |      | 2.3.3 No-clonabilidad física e identificabilidad 59                             |  |  |

|---|------|---------------------------------------------------------------------------------|--|--|

|   |      | 2.3.4 Modelo cuasi-ideal de PUF 63                                              |  |  |

|   |      | 2.3.5 Resistencia ambiental y compensación de la medida 66                      |  |  |

|   |      | 2.3.6 Clasificación de PUF                                                      |  |  |

|   |      | 2.3.7 Aplicaciones de PUF                                                       |  |  |

|   |      | 2.3.8 Ataques a un sistema PUF                                                  |  |  |

|   | 2.4  | Implementación física 82                                                        |  |  |

|   |      | 2.4.1 FPGA                                                                      |  |  |

|   | 2.5  | Conclusión                                                                      |  |  |

| 3 | Extr | racción de entropía en PUF de medida compensada 93                              |  |  |

|   | 3.1  | Topologías PUF de medida compensada                                             |  |  |

|   | 3.2  | Modelo de fabricación                                                           |  |  |

|   | 3.3  | Topologías en el diseño de PUF de medida compensada 100                         |  |  |

|   |      | 3.3.1 Todas las comparaciones posibles: topología $\mathcal{N}^2$ 102           |  |  |

|   |      | 3.3.2 Comparaciones sin repetición: topología $\mathcal{N}_{/2}$ 107            |  |  |

|   |      | 3.3.3 Comparaciones con una repetición: topología $\mathcal{N}_{-1}$ 114        |  |  |

|   |      | 3.3.4 Comparaciones en grupos de $K$ celdas: topología $\mathcal{N}_{/K}^2$ 119 |  |  |

|   | 3.4  | Comparación entre topologías                                                    |  |  |

|   | 3.5  | Conclusión                                                                      |  |  |

| 4 | Fun  | ciones no-clonables físicamente basadas en osciladores de anillo 127            |  |  |

|   | 4.1  | Osciladores de anillo                                                           |  |  |

|   | 4.2  | Diseño e implementación de matrices de osciladores en FPGA 130                  |  |  |

|   | 4.3  | Estrategias de selección de osciladores de anillo en FPGA 131                   |  |  |

|   |      | 4.3.1 Montaje experimental                                                      |  |  |

|   |      | 4.3.2 Ruteado de los osciladores                                                |  |  |

|   |      | 4.3.3 Diferencias entre LUT L/M                                                 |  |  |

|   |      | 4.3.4 Estrategias de selección de osciladores                                   |  |  |

|   |      | 4.3.5 Resultados                                                                |  |  |

|   | 4.4  | Medida compensada de orden superior aplicada a RO-PUF 149                       |  |  |

|   | 4.5  | Líneas de retardo programables aplicadas a RO-PUF 155                           |  |  |

|   |      | 4.5.1 Experimentos                                                              |  |  |

|   |      | 4.5.2 Resultados                                                                |  |  |

|   | 4.6  | Conclusión                                                                      |  |  |

| 5 |      | inciones no-clonables físicamente basadas en osciladores de anillo              |  |  |

|   | Fun  | ciones no-clonables físicamente basadas en osciladores de anillo                |  |  |

|   | de G | Galois 165                                                                      |  |  |

|   | de G |                                                                                 |  |  |

|     |       | 5.1.2    | Propiedades de la magnitud sesgo $R(0)$ en una matriz de |       |

|-----|-------|----------|----------------------------------------------------------|-------|

|     |       |          | anillos de Galois                                        | . 170 |

|     | 5.2   | Implen   | nentación de GARO-PUF                                    | . 173 |

|     |       | 5.2.1    | Evaluación experimental                                  | . 175 |

|     | 5.3   |          | ısión                                                    |       |

| 6   | Cone  | clusion  | es y líneas futuras                                      | 181   |

|     | 6.1   | Conclu   | isiones                                                  | . 181 |

|     |       |          | futuras                                                  |       |

| Bil | bliog | rafía    |                                                          | 187   |

| Аp  | éndi  | ces      |                                                          | 201   |

| Α   | Entr  | opía m   | áxima                                                    | 203   |

| В   | Flujo | o de dis | seño en FPGA                                             | 205   |

| С   | Prot  | ocolo h  | nandshake                                                | 207   |

| D   | Inte  | rfaz oro | denador – FPGA                                           | 209   |

| E   | Prog  | gramas   | y scripts                                                | 215   |

| F   | Lista | ı de pu  | blicaciones propias                                      | 217   |

Introducción

En este capítulo introductorio se proporciona una visión general de la criptografía en su estado actual a través de su evolución histórica (sección 1.1), enfatizando el papel activo de la capa física sobre la que se sustenta la tecnología de las telecomunicaciones a la hora de proporcionar seguridad. En la sección 1.2 se discuten las particularidades de los sistemas digitales embebidos de bajo rendimiento con conexión a la red (Internet de las Cosas) desde el punto de vista de la seguridad de la información. Así mismo, se exponen los objetivos generales y específicos de esta tesis doctoral. Finalmente, en la sección 1.3 se describe la organización de esta memoria.

## 1.1. Breve historia de la criptografía

#### 1.1.1. Criptografía clásica

La criptografía es hoy una ciencia formal bien establecida cuyo objeto de estudio es la seguridad de la información. Esta es un *desiderata* de los sistemas de comunicación, en el cual el contenido de un mensaje transmitido a través de un cierto canal se mantiene en secreto para entidades ajenas a la comunicación y, paralelamente, cada una de las instancias participantes en dicho proceso disponen de garantías sobre la identidad de las demás. Sin embargo, el establecimiento de la criptografía como ciencia formal fue precedido de siglos durante los cuales el envío eficaz de mensajes secretos era considerado un arte exclusivo del ámbito militar y, aún antes, en los albores del lenguaje escrito, un simple juego artístico con fines meramente decorativos. En este sentido, la evidencia más antigua de un trabajo sistemático de sustitución de símbolos escritos se encuentra en la tumba del noble egipcio Jnumhotep II, la cual data de aproximadamente el 1900 a.C. Se cree que estas sustituciones no buscaban la transmisión de información secreta, sino que tenían un sentido decorativo y místico-religioso. Se pueden encontrar aplicaciones lúdicas de sistemas primitivos de sustitución similares en otras civilizaciones incipientes;

por ejemplo, la mesopotámica o hebrea. En el caso de esta última, resulta llamativa la aparición del criptograma Sheshach para referirse a la ciudad de Babilonia<sup>1</sup> en el Libro de Jeremías —uno de los 46 que componen el Antiguo Testamento generado mediante un método de sustitución denominado "atbash", y que consiste en reemplazar cada carácter de una palabra por su imagen especular respecto de la mitad del alfabeto hebreo (i.e., primero por último, segundo por penúltimo, etcétera). La primera referencia bibliográfica de que se tiene constancia en la que se hace referencia explícita al secreto como una propiedad de la comunicación escrita es el mito de Belerofonte, narrado en la Ilíada de Homero: mientras el héroe griego era huésped en la corte del rey Preto de Tirinto, la esposa de este, despechada, urde con el monarca un plan para asesinar a Belerofonte sin faltar a la hospitalidad debida. Para ello, envía al héroe a su suegro, el rey Yóbates de Licia, junto con una supuesta carta de recomendación que en realidad esconde un mensaje secreto manifestando la intención homicida de hija y yerno. El rey licio trata de satisfacer la petición encomendando a Belerofonte la suicida misión de dar muerte a la Quimera, un monstruo híbrido de león y serpiente que aterrorizaba la región. No obstante, este regresa victorioso y el propio Yóbates, admirado, le entrega la mano de su hija en matrimonio. A pesar de la naturaleza evidentemente poética de la Ilíada, sí que existen referencias históricas del envío de comunicaciones secretas en la Antigüedad clásica, por ejemplo en la recopilación de los "Nueve Libros de Historia" de Heródoto de Halicarnaso, considerado el padre de la historiografía occidental, quien en el siglo V a.C documentó de forma exhaustiva los conflictos entre persas y griegos en el contexto de las guerras médicas. En su obra, Heródoto describe un método esteganográfico<sup>2</sup> por el cual Demarato, antiguo rey de Esparta exiliado en Persia, habría protagonizado en el 484 a.C. uno de los primeros episodios de espionaje militar de la historia occidental, al tener conocimiento de la inminente marcha del ejército persa a las órdenes del rey Jerjes sobre Grecia; Demarato comunicó los planes persas a Leónidas, rey de la ciudad griega de Esparta, a través de un mensaje oculto en una tablilla de cera -material de escritura habitual en la época-, de la cual había removido la cera, grabado el mensaje sobre el soporte de madera, y depositado de nuevo la cera encima. Esta tablilla aparentemente inocente llegó a las manos de Gorgo, esposa de Leónidas, quien descubrió el mensaje secreto, permitiendo movilizar una fuerza griega que, tras las batallas de Las Termópilas (480 a.C), Salamina (480 a.C) y Platea (479 a.C), terminaron con las aspiraciones expansionistas persas sobre el occidente. Además, se sabe que en este siglo los

$^1$ Sustituyendo las grafías hebreas bet, bet, lamed por shin, shin, kaph:  $\mathbf{bbl} o \ddot{\mathbf{Y}}\ddot{\mathbf{Y}}\mathbf{r}$

<sup>&</sup>lt;sup>2</sup>La esteganografía es un conjunto de técnicas dirigidas a esconder mensajes secretos dentro de objetos cotidianos, de forma que la información contenida en ellos pase desapercibida. Se distingue de la criptografía en que permite ocultar el propio establecimiento del hecho comunicativo, además del contenido de la información.

Fig. 1.1.: Escítala, un primitivo sistema de criptografía por transposición descubierto en la Grecia clásica.

espartanos ya utilizaban un precoz sistema normalizado de criptografía para las comunicaciones secretas militares denominado "escítala" (figura 1.1). Este consistía en un cilindro de madera sobre el cual se enrollaba una cinta de cuero o pergamino y se escribía un mensaje. La cinta se transmitía desenrollada mostrando una sucesión ininteligible de letras, que sólo cobraba sentido al enrollarse de nuevo en un cilindro de diámetro idéntico al original. De acuerdo con la taxonomía moderna de la criptografía, este método se clasificaría como cifrado por transposición (i.e., el texto cifrado se construye a partir del mensaje mediante una permutación de sus letras), cuya clave secreta es el diámetro de la escítala. También en la Edad Antigua, el historiador romano Cayo Suetonio, biógrafo de Julio César, describe un método de cifrado utilizado por este para enviar comunicaciones de índole militar a sus generales, el cual consistía en la sustitución de cada carácter en un mensaje por la letra que se encuentra tres posiciones por delante en el alfabeto con condiciones periódicas (esto es, considerando que la primera letra del alfabeto es precedida de la última). Este sistema de cifrado por sustitución, aunque naif para la criptología moderna, hubiera resultado eficaz en el contexto histórico de la Roma clásica, y ha perdurado hasta nuestros días la nomenclatura de "cifrado de César" para referirse de forma general a los algoritmos criptográficos de sustitución por desplazamiento [1], [2].

La Edad Media supuso un estancamiento para la evolución de la criptografía (o, al menos, para el registro documental de su uso, que es escaso), con la notable excepción del egipcio al-Qalqashandi, quien en el año 1412 completó el *Subh al-a 'sha*, una recopilación enciclopédica de 14 tomos que serviría como manual administrativo para los funcionarios estatales del Sultanato Mameluco de Egipto. Esta obra es una enorme compilación del saber medieval árabe, abarcando materias como historia, política, matemáticas o astronomía, e incluyendo un capítulo "Sobre la ocultación de mensajes secretos dentro de las cartas", donde se hace la primera mención explícita al criptoanálisis como una disciplina relacionada con, pero distinta

Fig. 1.2.: Disco de Alberti. Primer cifrador polialfabético, en el que la rotación del disco interior permite definir un alfabeto de sustitución diferente.

de, la criptografía. Durante el siglo XV, la contribución occidental más significativa a la criptografía es el trabajo del genovés Leon Battista Alberti, quien en torno a 1466 escribe un tratado sobre criptografía titulado De cifris donde recopila el criptoanálisis frecuencial (que probablemente hubiese sido descubierto con anterioridad), basado en deducir el alfabeto de sustitución en un "cifrado de César" mediante el análisis de las frecuencias de aparición de cada símbolo, poniendo estas en relación con las frecuencias de aparición conocidas de cada letra en el lenguaje natural en que está redactado el mensaje sin encriptar. Además, Alberti propuso una nueva técnica criptográfica robusta frente a este criptoanálisis frecuencial valiéndose del "disco de Alberti" (figura 1.2). Este dispositivo permitiría aplicar una cifra de sustitución diferente para cada carácter rotando el disco interior respecto del exterior, destruyendo así el patrón de frecuencias de un lenguaje natural. De este modo, Alberti había descubierto el hoy llamado "cifrado polialfabético". Pese a todo, hubo que esperar hasta finales del siglo XV y la llegada del Renacimiento para que resurgiera el interés por las comunicaciones secretas, en un contexto de globalización incipiente propiciada por el progreso en la tecnología del transporte marítimo, la enorme expansión del comercio y, con ello, el papel renovado de la diplomacia y las relaciones exteriores entre estados. Los siglos XVI y XVII fueron testigos de notables avances científicos e intelectuales de los que también participó la criptografía, y la historiografía de la época ya describe como prácticas habituales el cifrado de comunicaciones entre embajadas, así como el reclutamiento y mantenimiento de personal dedicado tanto a la encriptación de mensajes como a la resolución de criptogramas interceptados a potencias rivales. Desde el siglo XV hasta mediados del XIX, esta encriptación de

mensajes se realizaba por medio de cifras de sustitución homofónicas<sup>3</sup>, junto con un código secreto utilizado para codificar algunas palabras específicas. El cifrado basado en claves secretas no se descubriría hasta los trabajos del italiano Giovan Battista Bellaso en 1553 (erróneamente atribuido al matemático francés Blaise de Vigenère), y aún entonces resultaba de poca utilidad práctica ya que el proceso algorítmico de cifrado había de realizarse a mano mediante tablas o dispositivos como el disco de Alberti, lo que aumentaba enormemente la probabilidad de cometer errores catastróficos que volvieran el mensaje ilegible. En su lugar, los códigos secretos se reproducían en listas llamadas "nomenclátor", donde se relacionaba cada letra con su grupo de sustitución, y un pequeño conjunto de palabras con su correspondiente código; por ejemplo, durante Las Guerras de Religión de Francia del siglo XVII, Juan de Moreo, representante de Felipe II en la Liga Católica, se comunicaba con La Corona Española utilizando un nomenclátor que incluía una lista de 413 términos codificados en grupos de dos o tres letras, e.g., España  $\rightarrow$  LO, Navarra  $\rightarrow$  PUL, o Rey de España → POM. En 1628, el matemático francés Antoine Rossignol obtuvo el favor del Cardenal Richelieu, primer ministro de Francia y valido del rey Luis XIII, al resolver en pocas horas comunicaciones encriptadas de los rebeldes hugonotes durante los asedios a las villas sublevadas de Réalmont y La Rochelle. La información interceptada resultó crítica para la victoria de la facción real, y Rossignol pasó inmediatamente al servicio de la corona francesa. Rossignol perfeccionó los métodos criptológicos de su época, sin embargo su mayor contribución a la historia de la criptografía y la seguridad de la información no fue técnica sino administrativa, ya que fundó el "Gabinete del Secreto de Correos" (Cabinet du Secret des Postes), más conocido como "Gabinete Negro" (Cabinet Noir), precursor de los servicios de inteligencia normalizados propios del estado moderno (figura 1.3). A principios del siglo XVIII, los "Gabinetes Negros" a imagen del francés eran organismos estatales comunes en todos los estados europeos, destacando por su eficiencia y productividad el gabinete secreto de Viena, que se convirtió en una de las principales fuentes de inteligencia para la estrategia geopolítica de Austria hasta mediados del siglo XIX. En este momento, la crisis que arrastraba el absolutismo como modelo de gobierno precipitó el fin de muchas estructuras represivas del estado, entre ellas los gabinetes secretos dedicados a la intervención de correo postal. En la década de 1840, estas oficinas ya habían desaparecido en la mayor parte de Europa, incluyendo Francia, Austria e Inglaterra [2], [3].

<sup>&</sup>lt;sup>3</sup>El cifrado homofónico es la sustitución de letras por grupos de símbolos (*i.e.* transformación suprayectiva de un alfabeto natural en un alfabeto de símbolos), de tal modo que el tamaño del grupo asociado a cada letra es proporcional a la frecuencia de aparición de dicha letra en el lenguaje natural en que se redacta el mensaje plano. De este modo, se evita el criptoanálisis frecuencial de Alberti.

Fig. 1.3.: Grabado anónimo francés de 1815, donde se caricaturiza el *cabinet noir*. Procedente del Museo Carnavalet de París.

En el año 1844, el estadounidense Samuel Morse inventa el primer telégrafo práctico, revolucionando la historia de las telecomunicaciones y, con ello, el envío de información de forma segura. Este nuevo invento se expande con rapidez por América y Europa, y sólo seis años después de su aparición ya es utilizado en la totalidad de América del Norte e Inglaterra. En cuanto al modo radical en que transformó las comunicaciones seguras, esto se debe fundamentalmente a la velocidad con la que el telégrafo permitía corregir un mensaje cifrado defectuoso, lo cual eliminaba el principal escollo para la criptografía basada en cifradores tal y como había sido propuesta por Alberti y Battiste más de dos siglos antes. Esto significó el abandono del nomenclátor en favor de los cifrados polialfabéticos tipo Vigenère, que a mediados del siglo XIX eran considerados indescifrables. Esta ilusión habría de terminar en 1864, cuando el comandante retirado del ejército prusiano Friedrick Kasiski publicó el ensayo Die Geheimschriften und die Dechiffrer-Kunst, donde presenta un método criptoanalítico general contra el cifrado de sustitución periódico polialfabético. Este hecho marcó el inicio de la carrera frenética entre propuestas criptográficas y contrapropuestas criptológicas —o viceversa— que caracteriza la relación entre ambas disciplinas a día de hoy. La obra más representativa del conocimiento criptográfico en este siglo XIX es el tratado La Cryptographie Militaire, escrita por el matemático y criptógrafo Holandés Auguste Kerchoffs para la revista francesa "Le journal des Sciences Militaires" mientras trabajaba como profesor de alemán en

París, y que colocó a Francia a la vanguardia de la técnica criptográfica en puertas del siglo XX.

El 28 de junio de 1914 el archiduque Francisco Fernando de Austria, heredero al trono Austro-Húngaro, es asesinado en las calles de Sarajevo por un nacionalista serbio. Este hecho precipitó que Austria-Hungría declarara la guerra a Serbia el 28 de julio, lo cual hizo caer toda una compleja red de alianzas tejida a lo largo del siglo XIX entre las principales potencias europeas con el fin de contener mutuamente su expansión colonial y su poderío militar: Rusia comienza a movilizarse inmediatamente en apoyo de Serbia y en contra de Austria-Hungría, desairando a Alemania, que declara la guerra a Rusia el 31 de julio, y a Francia y Bélgica el 3 de agosto, a cuyo auxilio acude el Imperio Británico (actual Reino Unido junto con Canadá, Australia y la India Británica), declarando la guerra a Alemania el 4 de agosto, dando así comienzo a la Primera Guerra Mundial. La primera acción hostil británica contra Alemania es el seccionamiento de los cables de telecomunicaciones submarinos del Canal de la Mancha utilizando el buque cablero C.S. Alert, forzando a Alemania a utilizar señales de radio y líneas de telégrafo enemigas para su comunicación exterior, lo cual suponía entregar completamente la confidencialidad de sus comunicaciones a un buen sistema criptográfico. En octubre de 1914, el oficial británico Alfred Ewing funda la sección de criptoanálisis del Almirantazgo Británico (conocida popularmente como "Habitación 40"), con el fin de extraer inteligencia de la interceptación de mensajes cifrados alemanes durante la guerra. El logro más notable de esta institución fue la resolución del "telegrama Zimmermann" (figura 1.4), cuando en enero de 1917 los criptólogos William Montgomery y Nigel de Grey resolvieron un telegrama cifrado remitido por el ministro de asuntos exteriores alemán, Arthur Zimmermann, y dirigido a la embajada alemana en México, el cual había sido interceptado por la inteligencia británica. El contenido del telegrama era una propuesta para que el gobierno mexicano atacara a los Estados Unidos de América (EUA) y retomara las regiones de Texas, Nuevo México y Arizona, arrebatadas a México en 1848, en caso de que EUA entrara en la guerra en contra de Alemania. El contenido sibilino del telegrama causó una gran indignación tanto en el gobierno como en la opinión pública estadounidense, y se considera el casus belli que precipitó la entrada de Estados Unidos en la Primera Guerra Mundial, marcando con ello un punto de inflexión en el devenir de la contienda a favor de la alianza franco-británica [2].

El estallido de la guerra había renovado el interés por las comunicaciones secretas, y la compañía estadounidense *American Telephone and Telegraph (AT&T)* comenzó a colaborar con el ejército de los EUA en un proyecto secreto para estudiar

Fig. 1.4.: Telegrama Zimmermann (U.S. National Archives Catalog).

la seguridad de las comunicaciones telegráficas. En 1917, Gilbert Vernam, uno de los ingenieros trabajando para la *AT&T*, propuso una manera de encriptar la información que circulaba a lo largo de la línea de telégrafo codificada mediante código Baudot<sup>4</sup>. El "cifrado de Vernam" consistía en combinar ("sumar") cada símbolo de entrada con un símbolo marcado sobre una cinta perforada que actuaría como clave secreta. Esta clave debía tener la misma longitud que el mensaje a transmitir, y la combinación debía ser reversible para el receptor del mensaje siempre y cuando dispusiera de la misma clave utilizada para el cifrado. La operación propuesta por Vernam fue la siguiente:

| Entrada | Clave | $Entrada \oplus Clave = Cifrado$ |

|---------|-------|----------------------------------|

|         |       |                                  |

|         |       |                                  |

|         |       |                                  |

|         |       |                                  |

Donde "□" representa un espacio y "■" un punto en código Baudot. De este modo, el bit cifrado se obtiene a partir del bit de entrada y de la clave mediante la

<sup>&</sup>lt;sup>4</sup>Sistema de codificación propuesto por el ingeniero francés Émile Baudot en 1874, el cual utiliza sucesiones de cinco símbolos binarios ("bits") para representar cada una de las letras del alfabeto, los números del cero al nueve, y algunos caracteres de escape (espacios, saltos de línea, etcétera). Es un precursor del Código Estándar Estadounidense para el Intercambio de Información (*American Standard Code for Information Interchange*, ASCII) moderno.

**Fig. 1.5.:** (a) Máquina de rotores de Hebern en el *National Cryptologic Museum* de EUA. (b) Reproducción en detalle del sistema de rotores en una máquina Enigma.

operación lógica XOR ( $\oplus$ ), que resulta trivial de revertir ya que esta operación es involutiva (*i.e.*, coincide con su inversa), Entrada = Cifrado  $\oplus$  Clave. Vernam acababa de descubrir el "cifrado de flujo", en contraposición al clásico "cifrado de bloque", donde se utiliza una clave secreta para encriptar todo un bloque de información. Posteriormente, un comandante del Cuerpo de Señales del Ejército de EUA, Joseph Mauborgne, propuso que los símbolos de las claves utilizadas fueran completamente aleatorios y de un solo uso, evitando toda estructura a lo largo de la cinta perforada. Este cifrador fue llamado "one-time pad", y en 1918 se conjeturaba que era indescifrable<sup>5</sup>; lo cual en efecto se probó una intuición acertada, sin embargo, no hubo una demostración matemática rigurosa hasta los trabajos de Claude Shannon en 1949.

En 1919, una vez terminada la Primera Guerra Mundial, la "Habitación 40" fue integrada con la unidad de inteligencia militar británica para formar la Escuela Gubernamental de Codificación y Cifrado (Government Code and Cipher School, GC&CS). En torno a la misma fecha apareció la máquina de rotores, un dispositivo electromecánico que actuaba como un cifrador de flujo, transformando los caracteres introducidos por un operador a través de un teclado en otros diferentes en función de la posición angular de una serie de rotores internos que cambiaban de posición cada vez que se pulsaba una nueva tecla. Esto produce un cifrado polialfabético en el que la probabilidad de que se utilice un mismo alfabeto más de una vez se puede hacer arbitrariamente pequeña mediante la incorporación de un número sucesivamente mayor de rotores, inutilizando el criptoanálisis polialfabético general

<sup>&</sup>lt;sup>5</sup>En el ámbito de la criptología, "indescifrable", "irrompible" o "imposible de descifrar" significa que no existe un método para encontrar la solución a un criptograma más rápido que probando exhaustivamente todas las claves secretas posibles hasta encontrar aquella que resuelve el texto cifrado.

de tipo Kasiski. Sin embargo, la operación de la máquina era determinista dada una posición inicial de sus rotores, lo cual actuaba como clave secreta y permitía al receptor del mensaje cifrado deshacer inequívocamente la operación de encriptación para recuperar el mensaje original. Este dispositivo fue propuesto simultáneamente por al menos cuatro inventores de forma independiente: Alexander Koch (Holanda), Arvid Damm (Suecia), Edward Hebern (EUA) y Arthur Scherbius (Alemania). De estos, el único que gozó de éxito comercial fue el alemán Scherbius, quien inventó la máquina "Enigma" en 1918, y a mediados de los años veinte ya se había convertido en el estándar criptográfico del ejército alemán, interesado en actualizar su sistema de encriptación después de descubrir que la inteligencia británica había sido capaz de descifrar las comunicaciones alemanas a lo largo de toda la guerra. No obstante, en 1932, el matemático y criptógrafo polaco Marian Rejewski había deducido el funcionamiento de la máquina Enigma mediante documentación proporcionada por la inteligencia militar francesa. Tras la invasión alemana de Polonia en 1939 que da comienzo a la Segunda Guerra Mundial, el personal de la Oficina de Cifrado polaca en la que trabajaba Rejewski fue evacuada a Francia, desde donde colaboró con la GC&CS británica. Esta colaboración dio sus frutos en la máquina criptológica "Bombe", diseñada y fabricada por los británicos Alan Turing y Harold Keen en 1940. Esta máquina simulaba mecánicamente un conjunto de varios dispositivos Enigma, y permitió a la inteligencia británica desencriptar muchas de las claves de cifrado alemanas, que eran cambiadas diariamente, hasta el final de la guerra en 1945. Estimaciones modernas sobre el impacto de este hito sostienen un acortamiento en la duración de la guerra de al menos dos años, con el muy significativo número de vidas que ello hubiera supuesto [2], [4], [5].

# 1.1.2. Criptografía moderna

En el año 1949, el matemático e ingeniero estadounidense Claude E. Shannon publicó el trabajo *A Mathematical Theory of Secrecy Systems* [6], basado en gran medida en su *A Mathematical Theory of Commmuncation* [7] que había visto la luz un año antes y que se considera el trabajo fundacional de la Teoría de la Información. En su teoría de los sistemas secretos, Shannon formaliza con éxito la noción de "criptosistema" utilizando las herramientas elaboradas en su trabajo previo, y es capaz de aplicar estas a la demostración de la invulnerabilidad del cifrado *one-time pad*. El trabajo de Shannon proporcionó un lenguaje formal común para la criptología, dotando a esta de todos los elementos propios de la disciplina científica. Por otra parte, el hito de Shannon fue de una naturaleza tan general en cuanto a los aspectos

fundamentales de la criptografía que se considera el nacimiento de la criptografía moderna. El segundo gran hito en esta nueva etapa es el artículo New Directions in Cryptography [8], publicado por Whitfield Diffie y Martin Hellman en 1976. En este, los investigadores de la Universidad de Stanford proponen un sistema de intercambio de claves secretas entre los participantes de un proceso de comunicación sin la necesidad de establecer un canal seguro entre ellos. La innovación fundamental propuesta por Diffie y Hellman, y que constituye la piedra angular del algoritmo de intercambio de claves de Diffie-Hellman, fueron las trapdoor one-way functions, i.e., funciones fáciles de calcular pero difíciles de invertir (one-way functions), a menos que se disponga de una cierta información (trapdoor), en cuyo caso es sencillo obtener la preimagen de un determinado valor. La inspiración para las trapdoor one-way functions bebe de la noción de "seguridad probable" propuesta por Shannon, quien hizo explícita la equivalencia entre la robustez de un sistema criptográfico y la dificultad para resolver un cierto problema matemático. En el caso del algoritmo propuesto por Diffie y Hellman, esta es la dificultad en general para calcular el logaritmo discreto en un cuerpo finito. Además de su propuesta, que todavía hoy se considera uno de los esquemas de intercambio de claves más prácticos y seguros, Diffie y Hellman son considerados los padres de la criptografía de clave pública como nuevo paradigma de las comunicaciones seguras, y su trabajo estimuló una investigación frenética en este área. Esta ha fructificado en soluciones criptográficas con enorme prevalencia en los sistemas de telecomunicaciones modernos, como el protocolo de intercambio de claves RSA diseñado por Ron Rivest, Adi Shamir y Leonard Adleman en 1977, o el protocolo de firma digital (Digital Signature Algorithm, DSA), propuesto por el Instituto Nacional de Estándares y Tecnología (National Institute of Standards and Technology, NIST) como estándar de firma digital en 1991.

La criptografía se diversificó gradualmente más allá de sus aplicaciones militares con el advenimiento de la computación personal y el comercio computerizado, y muy especialmente con la aparición de Internet y su llegada al gran público. En 1973, la Oficina Nacional de Estándares de los Estados Unidos (*National Bureau of Standards*, NBS) propuso un concurso público para un algoritmo de cifrado comercial estándar. Este fue concedido al grupo de criptosistemas de la tecnológica IBM, encabezado por el criptógrafo de origen alemán Horst Feistel, que presentó un sistema de cifrado desarrollado a principios de los años setenta denominado *Lucifer*. El algoritmo fue rebautizado "Estándar de Encriptación de Datos" (*Data Encription Standard*, DES), y sirvió como cifrador digital de referencia hasta 1997. En este año, la agencia de estándares estadounidense —antigua NBS, ahora NIST—presentó un nuevo concurso para un sustituto de DES. En esta ocasión el ganador

fue el algoritmo de cifrado en bloque *Rijndael*, desarrollado por los criptógrafos belgas Joan Daemen y Vincent Rijmen. En el 2000, este algoritmo fue rebautizado "Estándar de Cifrado Avanzado" (*Advanced Encryption Standard*, AES), siendo el sistema de cifrado simétrico más utilizado en la actualidad [9], [10].

# 1.1.3. Criptografía física y estado de la técnica

En el año 1943, la compañía estadounidense Bell Labs trabajaba en el diseño de un teletipo encriptado (131-B2) para el ejército de los Estados Unidos mediante la técnica one-time pad, entonces conjeturada como fundamentalmente segura. Sin embargo, los ingenieros que trabajaban con el prototipo observaron unos pulsos característicos en los osciloscopios físicamente próximos al dispositivo cada vez que se encriptaba un carácter. Estos se debían a la emanación espuria de radiación electromagnética como consecuencia de la operación eléctrica normal del teletipo. El estudio cuidadoso de los patrones captados por los osciloscopios permitió a los técnicos de los Laboratorios Bell interceptar hasta el 75 % del texto original introducido en el teletipo. Las modificaciones realizadas por la compañía para apantallar estas emanaciones fueron consideradas inaceptables por el ejército al restar movilidad al aparato, y en su lugar se estableció una zona de exclusión segura de 30 metros a la redonda en torno al punto de operación del teletipo, una vez este fuera desplegado en campaña. En 1951, la Agencia Central de Inteligencia estadounidense (Central Intelligence Agency, CIA) informó de que, mediante la amplificación de la señal emanada por el 131-B2, había sido capaz de recuperar texto plano hasta una distancia de 400 metros: se habían descubierto los ataques de canal lateral (Side Channel Attack, SCA), una nueva forma de vulneración criptográfica cuyo objetivo es la información filtrada por el dispositivo físico sobre el cual se implementa una solución criptográfica. Este descubrimiento dio lugar a la certificación TEMPEST (Telecommunication Electronic Material Protected from Emanating Spurious Transmissions, TEMPEST), hoy utilizado por la NSA estadounidense y la OTAN, que califica material de comunicación como adecuadamente blindado frente al filtrado de información. El primer ataque SCA conocido, sin embargo, fue efectuado por el servicio de inteligencia interior británico (MI5) en el año 1965 sobre la embajada egipcia en Londres; este consistió en la disposición de una serie de micrófonos próximos a una máquina de cifrado mecánico utilizada por la embajada. El funcionamiento de esta máquina producía unos sonidos característicos, que los técnicos del MI5 pudieron correlacionar con la clave secreta utilizada en cada instante, lo que permitió a la

agencia británica espiar las comunicaciones secretas de la embajada durante años, a pesar de que la clave era modificada diariamente [11]-[13].

En la actualidad, la mayor parte de los esfuerzos de la comunidad criptológica se centran en la seguridad en la capa física. En este aspecto, mucho del trabajo pionero en ataques SCA sobre implementaciones físicas de sistemas criptográficos de clave pública se debe al investigador estadounidense Paul Kocher, quien en 1996 publicó una serie de ataques exitosos sobre protocolos RSA y firmas electrónicas DSA, y propuso en 1999 el análisis diferencial de potencia (*Differential Power Analysis*, DPA), una forma avanzada para relacionar el sesgo en el consumo de energía exhibido por un procesador al ejecutar un determinado algoritmo criptográfico con el contenido de la clave secreta que está siendo procesada. En el año 2004, Kocher *et al.* preconizaron la adopción de la seguridad *hardware* como una dimensión más a tener en cuenta en el diseño de sistemas embebidos [14].

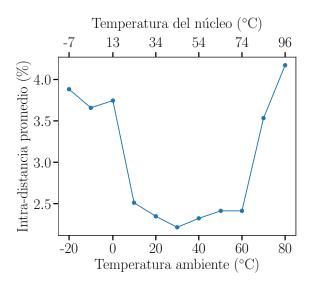

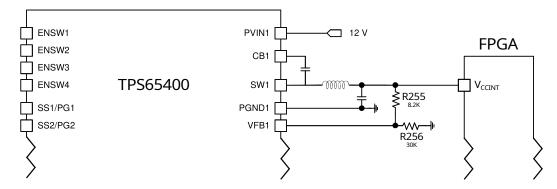

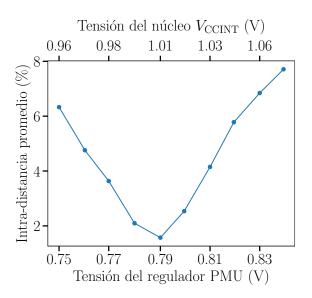

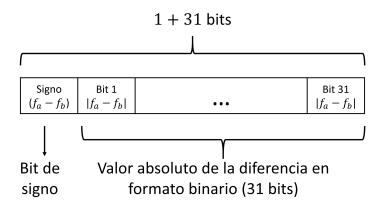

Además de la seguridad en la capa física, otra línea de investigación activa es la protección frente a un hipotético ordenador cuántico, que presumiblemente podría resolver muchos de los problemas matemáticos considerados "irresolubles en la práctica" sobre los cuales se basa la seguridad probable de los protocolos de clave pública. En 2016 el NIST hizo un nuevo llamamiento público para concursar por un algoritmo de criptografía poscuántica que fuera robusto frente a las capacidades teóricas de un ordenador cuántico. Entre agosto y noviembre de 2023, el Instituto mantuvo abierto un período de revisión pública para tres candidatos finalistas a estándares de criptografía poscuántica: un algoritmo de establecimiento seguro de claves denominado *Module-Lattice-Based Key-Encapsulation* [15], y dos algoritmos de firma digital *Module-Lattice-Based Digital Signature* [16] y *Stateless Hash-Based Digital Signature* [17]. Durante este lapso, la comunidad criptográfica ha tenido la oportunidad de proporcionar comentarios técnicos específicos sobre estos finalistas. Como resultado, se espera que el NIST publique una versión estándar definitiva en 2024.