## Trabajo Fin de Máster

Ecualizadores Adaptativos en Tiempo Continuo

para Comunicaciones Multi-Gigabit

Autor

Erick Guerrero Rodríguez

Director

Dr. Santiago Celma Pueyo

Facultad de Ciencias

2014

# ECUALIZADORES ADAPTATIVOS EN TIEMPO CONTINUO PARA COMUNICACIONES MULTI-GIGABIT

Erick Guerrero Rodríguez

Grupo de Diseño Electrónico

Departamento de Ingeniería Electrónica y Comunicaciones

*Facultad de Ciencias*

*Universidad de Zaragoza*

# **ECUALIZADORES ADAPTATIVOS EN TIEMPO CONTINUO PARA COMUNICACIONES MULTI-GIGABIT**

Memoria del Trabajo Fin de Máster

Máster en Física y Tecnologías Físicas

Realizada por

**Erick Guerrero Rodríguez**

Bajo la dirección del profesor

**Dr. Santiago Celma Pueyo**

Dpto. Ingeniería Electrónica y Comunicaciones

Facultad de Ciencias

Universidad de Zaragoza

*Zaragoza, septiembre de 2014*

# Tabla de Contenido

---

|                                                                        |           |

|------------------------------------------------------------------------|-----------|

| <b>1. Introducción</b>                                                 | <b>1</b>  |

| <b>2. Objetivos</b>                                                    | <b>4</b>  |

| <b>3. Ecualizadores adaptativos</b>                                    | <b>5</b>  |

| 3.1. Tipos de ecualizadores . . . . .                                  | 7         |

| 3.1.1. Ecualizadores de tiempo continuo . . . . .                      | 8         |

| <b>4. Diseño e implementación del ecualizador adaptativo propuesto</b> | <b>11</b> |

| 4.1. Técnica de balanceo espectral . . . . .                           | 12        |

| 4.2. Ecualizador de línea . . . . .                                    | 14        |

| 4.2.1. Ecualizador de línea propuesto . . . . .                        | 15        |

| 4.3. Lazo de adaptación . . . . .                                      | 18        |

| 4.3.1. Filtros del lazo de adaptación . . . . .                        | 18        |

| 4.3.2. Comparador de potencia . . . . .                                | 21        |

| <b>5. Resultados</b>                                                   | <b>25</b> |

| 5.1. Resultados de simulación post-layout . . . . .                    | 25        |

| <b>6. Conclusiones</b>                                                 | <b>29</b> |

| <b>Bibliografía</b>                                                    | <b>31</b> |

---

# Capítulo 1

## Introducción

---

La creciente demanda de servicios digitales en el hogar ha generado una necesidad de transmitir datos a elevadas tasas de bit, del orden de los gigabits por segundo, con una alta calidad de servicio (QoS por sus siglas en inglés). Debido a esto, se necesita cada vez más de sistemas de comunicaciones más rápidos, robustos y económicamente accesibles para los usuarios. Estos sistemas deben combinar sinérgicamente redes *wireless* y *wireline*.

A medida que la tecnología de fabricación de circuitos integrados va evolucionando junto con la innovación en las técnicas de diseño de los mismos, se ha logrado desarrollar sistemas digitales de altas prestaciones. Sin embargo, existe una limitación inherente a las propiedades físicas del canal de transmisión que debe ser superada para lograr tasas de transferencia por encima del gigabit por segundo.

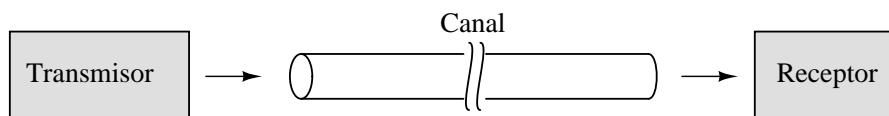

En este trabajo nos vamos a centrar en los sistemas de comunicación serie (*wireline*). Los sistemas de comunicaciones serie se pueden representar, de forma generalizada, con el diagrama de bloques de la Figura 1.1. Contienen un transmisor, el canal y un receptor.

El transmisor es el encargado de procesar la información, ajustarla al protocolo de transmisión deseado y, en su caso, modular los datos con la señal portadora que será transmitida a través del canal. Por su parte, el receptor realiza el proceso

Figura 1.1: Diagrama de bloques general de un sistema de comunicaciones.

Figura 1.2: Interferencia Inter-Símbolo (ISI).

Figura 1.3: Respuesta frecuencial del canal (azul), ecualizador (rojo) y la combinación de ambas (verde).

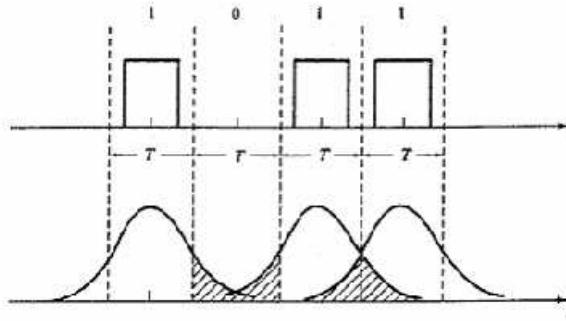

inverso, es decir, demodula la señal y la procesa para recuperar la información originalmente transmitida. Sin embargo, las no-idealidades del canal tales como su limitado ancho de banda generan una atenuación en las componentes de alta frecuencia de la señal, originando un fenómeno conocido como Interferencia Inter-Símbolo (ISI, por sus siglas en inglés), que consiste en un ensanchamiento temporal en los símbolos transmitidos haciendo que se solapen unos con otros. Estas no-idealidades deterioran la calidad de la señal y causan errores en el proceso de recuperación de datos. Éste fenómeno se puede observar en la Figura 1.2.

Para compensar los errores de ISI provocados por el ancho de banda del canal, existen dos opciones básicas: recurrir a sistemas de modulación más complejos o aplicar una ecualización a la señal. De estas dos, la segunda es la mejor opción debido a su bajo nivel de complejidad y, sobre todo, al bajo coste del sistema final.

La ecualización consiste en generar una respuesta frecuencial inversa a la del canal de transmisión. De esta manera, la combinación canal–ecualizador producirá una respuesta plana en el rango frecuencial deseado, lo que equivale a un

ensanchamiento del ancho de banda útil. Este proceso se muestra en la Figura 1.3.

Además, se debe tomar en cuenta que en un sistema práctico de transmisión, las características del canal pueden tener variaciones debido a la temperatura, las propiedades físicas del canal, su longitud, etc. Por lo tanto, es imprescindible que el ecualizador sea capaz de adaptar su respuesta a dichas variaciones, de lo contrario, resultaría en una sobrecompensación o subcompensación de la señal.

---

## Capítulo 2

# Objetivos

---

El objetivo principal de este trabajo consiste en diseñar, simular y depurar un ecualizador adaptativo capaz de compensar las pérdidas en alta frecuencia debidas al limitado ancho de banda del canal de transmisión en comunicaciones serie de alta velocidad. Debido a que la fibra óptica plástica (POF por sus siglas en inglés) es una alternativa emergente en los últimos años para lograr comunicaciones multi-gigabit con costes considerablemente aceptables, el ecualizador propuesto se diseñará enfocado a compensar una fibra óptica plástica *step-index* Mitsubishi GH para un rango de longitudes de 10 m a 50 m, para secuencias de datos binarias con modulación NRZ a 1.25 Gb/s.

La implementación del sistema propuesto se realizará en el entorno de simulación de circuitos integrados CADENCE. Además, se empleará una tecnología de fabricación estándar CMOS de  $0.18 \mu\text{m}$  de longitud de canal de transistor.

Además, otro de los objetivos principales consiste en lograr la operación del sistema limitado a un voltaje de alimentación de solamente 1 V. Esto con el objeto de demostrar la escalabilidad del sistema a tecnologías más modernas que tienen una longitud de canal mínima más corta y, además, voltajes de alimentación muy bajos.

La memoria está organizada de la siguiente manera: en el capítulo 3 se presenta una introducción a los ecualizadores adaptativos y las distintas estructuras con las que se pueden implementar, en el capítulo 4 se describirá de manera detallada los bloques que conforman el ecualizador propuesto, en el capítulo 5 se presentan los principales resultados obtenidos en simulación y, finalmente, en el capítulo 6 se presentan las conclusiones.

---

## Capítulo 3

# Ecualizadores adaptativos

---

Existen varios canales de comunicación eléctrica con distintas características. Algunos ejemplos son el par trenzado, cable coaxial, trazas en placas de circuito impreso (PCB), etc. En todos ellos, la ecualización ha sido muy utilizada para compensar la atenuación producida por el canal.

Para comunicaciones en largas distancias, los canales de fibras ópticas son la mejor opción para transportar grandes volúmenes de información a velocidades de varios gigabits por segundo. En este caso, la ecualización también se ha utilizado en módems y adsl para corregir la dispersión cromática producida por la fibra óptica de vidrio [1].

Por otro lado, la creciente demanda de conexiones de banda ancha para usuarios residenciales representa un nuevo reto para las operadoras de telecomunicaciones: ¿Cómo llevar las señales digitales con altas tasas de transferencia y una alta calidad de servicio a los dispositivos de los consumidores distribuidos dentro del hogar del usuario final? Dentro de todas las posibilidades existentes, la fibra óptica de plástico representa una alternativa muy atractiva desde el punto de vista de costes, velocidades de transmisión y, sobre todo, facilidad de instalación. En la actualidad, la POF *step-index* es usada comercialmente en la industria, sector automovilístico [2], y en redes de área domésticas (HANs, por sus siglas en inglés) a velocidades de hasta 100 Mb/s sobre 50 m [2].

Sin embargo, el principal problema de la POF es su limitado producto de longitud-ancho de banda de aproximadamente 45 MHz x 100 m debido a la dispersión modal [3].

En primer orden de aproximación, el canal de comunicaciones se puede modelar mediante un filtro pasa-bajas de primer orden. Entonces, su respuesta frecuencial aproximada se puede escribir como:

$$H_{ch}(\omega) = A(\omega) \cdot \frac{1}{(1 + j\frac{\omega}{\omega_p})} \quad (3.0.1)$$

donde  $\omega_p$  es la frecuencia asociada al polo que queremos compensar con el ecualizador y en  $A(\omega)$  se incluye la dependencia frecuencial de orden superior. Por lo tanto, para poder extender el ancho de banda del sistema, el polo dominante debe ser desplazado hacia la izquierda para lograr una respuesta frecuencial plana en el rango de frecuencias deseadas como se mostró en la Figura 1.3. Tomando en cuenta lo anterior, la respuesta frecuencial del ecualizador puede ser descrita por la siguiente función de transferencia [4]:

$$H_{eq}(\omega) = H \cdot \frac{(1 + j\frac{\omega}{\omega_z})}{(1 + j\frac{\omega}{\omega_{eq}})} \quad (3.0.2)$$

donde  $\omega_z$  y  $\omega_{eq}$  son las frecuencias asociadas al cero y al polo del ecualizador, respectivamente, y  $H$  la ganancia en DC.

De esta forma, la función de transferencia total que resulta de multiplicar la función de transferencia del canal,  $H_{ch}(\omega)$ , con la del ecualizador,  $H_{eq}(\omega)$ , es la siguiente:

$$H_t(\omega) = A(\omega) \cdot \frac{1}{(1 + j\frac{\omega}{\omega_p})} \cdot H \cdot \frac{(1 + j\frac{\omega}{\omega_z})}{(1 + j\frac{\omega}{\omega_{eq}})} \quad (3.0.3)$$

De acuerdo con la ecuación (3.0.3), si diseñamos el ecualizador de manera que su cero compense al polo del canal ( $\omega_z = \omega_p$ ), tenemos lo siguiente:

$$H_t(\omega) = A(\omega)H \cdot \frac{1}{1 + j\frac{\omega}{\omega_{eq}}} \quad (3.0.4)$$

Como se puede ver, la respuesta frecuencial del sistema ecualizado contiene ahora un polo dominante que corresponde al propio ecualizador, siendo  $\omega_{eq} >> \omega_p$ . Esto significa que con una elección de compromiso de  $\omega_{eq}$ , tendremos la posibilidad de modificar el ancho de banda del sistema evitando las atenuaciones de alta frecuencia y limitar el ruido eléctrico de alta frecuencia. En consecuencia, se reducirá la tasa de error de bits (BER) en la recuperación de la información recibida.

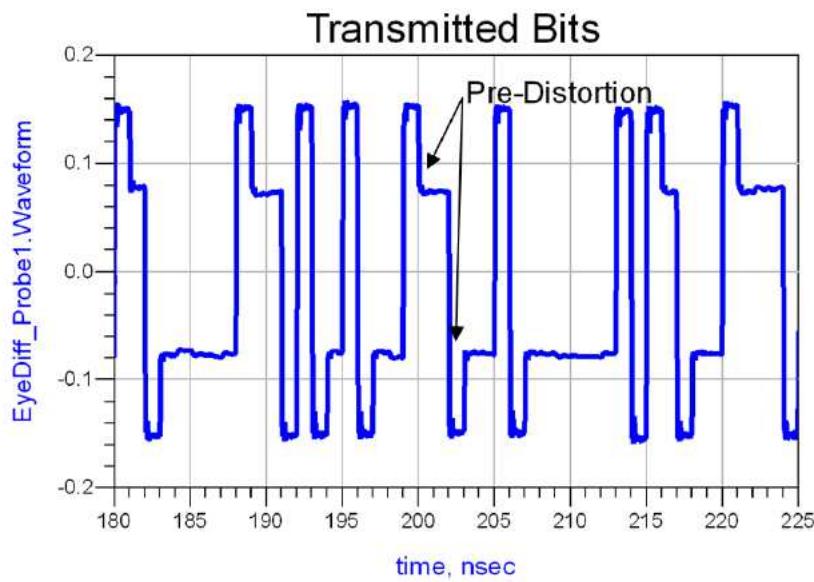

### 3.1. Tipos de ecualizadores

La ecualización se puede aplicar tanto en el transmisor como en el receptor. Una técnica de ecualización consiste en amplificar las componentes de alta frecuencia en la señal que será transmitida para compensar las atenuaciones esperadas que producirá el canal de transmisión. Esta técnica se conoce como “pre-énfasis” y se muestra en la Figura 3.1 [5]. La porción amplificada de la señal es atenuada por el canal, lo que resulta en una secuencia temporal de datos más nítida o diagrama de ojos más abierto que puede ser interpretado más fácilmente por el receptor, reduciendo los errores en la información recuperada.

Sin embargo, al amplificar las componentes de alta frecuencia se puede causar interferencia electromagnética (EMI, por sus siglas en inglés) y un *crosstalk*<sup>1</sup> más severo en transmisiones por canal eléctrico [1]. Sin embargo, este problema no se produce en canales de fibra óptica. No obstante, debido a que la ecualización se realiza en el transmisor, no se puede ajustar a las variaciones que pudiera haber en el canal debido a temperatura, longitud, etc.

En el receptor, hay varios tipos de ecualizadores para transmisiones multi-

<sup>1</sup>El *crosstalk* es un fenómeno por el cual una señal transmitida crea un efecto no deseado en otro circuito o canal

Figura 3.1: Pre-énfasis en el transmisor.

|                                                 | Ventajas                                                                                                                                                            | Desventajas                                                                                                                                                   |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ecualizadores pasivos                           | <ul style="list-style-type: none"> <li>• Fáciles de implementar</li> <li>• Amplio rango de operación</li> </ul>                                                     | <ul style="list-style-type: none"> <li>• Sensible a variaciones de proceso</li> <li>• Bajo nivel de SNR</li> <li>• Estrecho margen de compensación</li> </ul> |

| Ecualizadores digitales FIR de tiempo discreto  | <ul style="list-style-type: none"> <li>• Más robustos</li> </ul>                                                                                                    | <ul style="list-style-type: none"> <li>• Limitación de velocidad</li> <li>• Requieren de ADC</li> </ul>                                                       |

| Ecualizadores analógicos FIR de tiempo discreto | <ul style="list-style-type: none"> <li>• No requieren ADC</li> </ul>                                                                                                | <ul style="list-style-type: none"> <li>• Requieren amplificadores <i>Sample and Hold</i></li> <li>• Atenuan la señal</li> </ul>                               |

| Ecualizadores de tiempo continuo                | <ul style="list-style-type: none"> <li>• No requieren muestreo</li> <li>• Buen compromiso entre potencia y velocidad</li> <li>• Menor complejidad y área</li> </ul> | <ul style="list-style-type: none"> <li>• Degradado margen de fase</li> </ul>                                                                                  |

| Ecualizadores con retroalimentación de decisión | <ul style="list-style-type: none"> <li>• No degradan el margen de ruido</li> </ul>                                                                                  | <ul style="list-style-type: none"> <li>• Alta complejidad</li> <li>• Dificultades de temporizado</li> </ul>                                                   |

Tabla 3.1: Comparación de las distintas arquitecturas de ecualizadores implementadas en el receptor.

gigabit: ecualizadores pasivos, ecualizadores digitales FIR de tiempo discreto, ecualizadores analógicos FIR de tiempo discreto, ecualizadores de tiempo continuo y ecualizadores de retroalimentación de decisión. En la Tabla 3.1 se presentan las ventajas y desventajas de los ecualizadores implementados en el receptor [1].

Como se puede observar en la Tabla 3.1, los ecualizadores de tiempo continuo son una buena alternativa para implementar sistemas de bajo coste y altas prestaciones.

### 3.1.1. Ecualizadores de tiempo continuo

Un ecualizador en tiempo continuo es un circuito lineal e invariante temporal cuya función de transferencia contiene un aumento en la ganancia en las componentes de alta frecuencia que, combinado con la función de transferencia del canal,

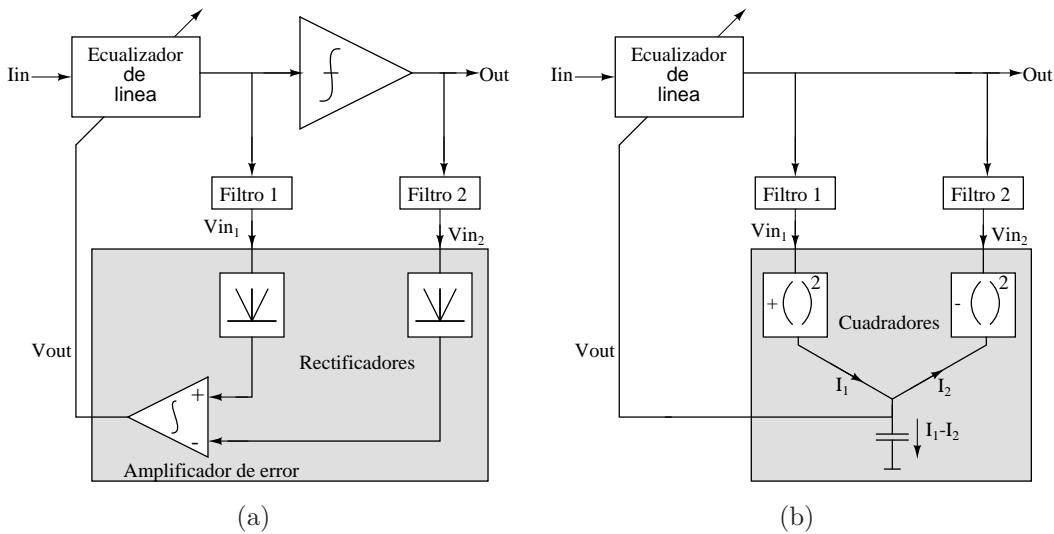

Figura 3.2: Esquema conceptual de ecualizadores adaptativos: (a) con comparador y (b) basado en balanceo espectral.

produce una respuesta plana en el rango de frecuencias deseado.

Para que un ecualizador pueda adaptar su respuesta a los cambios del canal, es necesario que posea un lazo de adaptación. Para ello, se han propuesto en la literatura dos estructuras que pueden ser implementadas: lazo de adaptación con un comparador y lazo de adaptación basado en la técnica de balanceo espectral tal como se muestra en la Figura 3.2. En cualquiera de los dos casos, la operación del lazo tiende a llevar al ecualizador hacia un nivel de compensación óptima para las limitaciones de ancho de banda del canal.

### Ecualizadores de tiempo continuo con comparador

El principio de operación de este tipo de ecualizadores adaptativos se basa en colocar un comparador a la salida del ecualizador de línea, el cual hace que las transiciones entre los bits de la secuencia de datos sean más definidas, lo que se traduce en una amplificación de las componentes de alta frecuencia de la secuencia de datos.

Posteriormente, se puede realizar una comparación de las potencias en altas frecuencias de las señales de entrada y salida del comparador. Esto se realiza mediante el lazo de retroalimentación que consta de un par de filtros, rectificadores y un amplificador de error como se muestra en la Figura 3.2(a), a partir de lo cual se genera la señal de error necesaria para corregir el comportamiento frecuencial

del ecualizador y compensar las pérdidas del canal.

### **Ecualizadores de tiempo continuo basados en el balanceo espectral**

Este tipo de ecualizadores basan su operación en el hecho de que la densidad de potencia espectral (PSD, por sus siglas en inglés) de una secuencia de datos idealmente ecualizada se conoce previamente, admitiendo que se aproxima a una serie aleatoria de bits. Esto permite controlar el lazo de adaptación usando información sobre la relación de potencias entre distintos rangos de frecuencia de la señal obtenida después del ecualizador.

En particular, la mayoría de los esquemas de modulación usados en los sistemas de comunicaciones tienen una PSD con forma de función  $\text{sinc}^2$ ; tal es el caso del no-retorno a cero unipolar (NRZ), modulación de amplitud de pulsos de 4 niveles (4-PAM), o la modulación duo-binaria. En cualquier caso, la extracción de las potencias en distintos rangos de frecuencias se realiza mediante un par de filtros, que pueden ser un pasa-bajas y un pasa-altas [6], un pasa-bajas y un pasa-todo [7], dos pasa-bandas [8], o dos pasa-bajas [9]. Posteriormente, la salida de los filtros se alimenta hacia el comparador de potencia que, en nuestro caso, se implementa en modo corriente, lo que facilita la integración de la señal mediante un condensador a tierra que genera tensión de control que es retroalimentada al ecualizador de línea para ajustar la compensación de la señal (Figura 3.2(b)).

Como se puede observar en la Figura 3.2 y, de acuerdo a la descripción realizada previamente, la estructura de ecualizadores adaptativos en tiempo continuo basados en la técnica de balanceo espectral que se propone en este trabajo tiene una menor complejidad de diseño al igual que un número de bloques analógicos más reducidos. Esto se traduce en menor área consumida por el sistema completo, menor consumo de potencia y, por lo tanto, menor coste final.

Por lo tanto, el ecualizador propuesto que se describe en las secciones posteriores, se ha realizado siguiendo la estructura de la Figura 3.2(b).

---

## Capítulo 4

# Diseño e implementación del ecualizador adaptativo propuesto

---

Como se ha mencionado anteriormente, el ecualizador debe ser robusto a las variaciones que pueda presentar el canal de transmisión. Esto supone que el esquema de adaptación que sea implementado con el ecualizador debe ser capaz de proporcionar una señal de error basada en la respuesta frecuencial ideal que se esperaría tener en un sistema idealmente compensado.

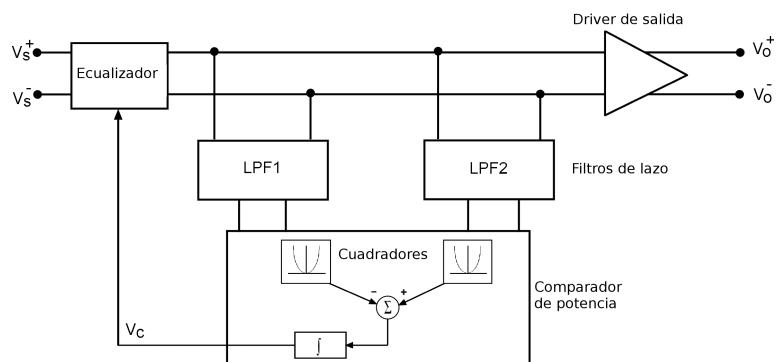

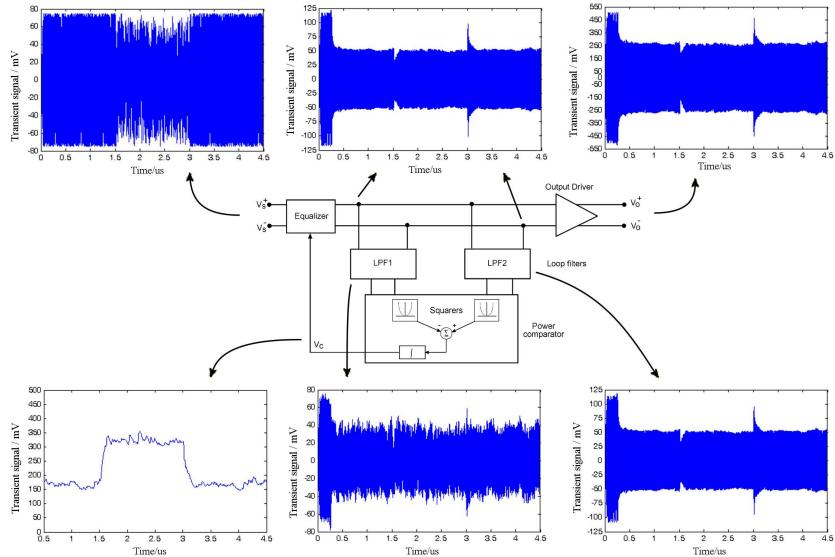

El diagrama de bloques del ecualizador adaptativo en tiempo continuo se muestra en la Figura 4.1. Está formado por un ecualizador de línea, un lazo de adaptación y un driver de salida (que se necesita para realizar las mediciones experimentales en el laboratorio).

La adaptabilidad del sistema se obtiene mediante el lazo de retroalimentación formado por dos filtros y un comparador de potencia, donde se genera la señal de error necesaria para ajustar el comportamiento frecuencial del ecualizador de

Figura 4.1: Diagrama de bloques del ecualizador adaptativo propuesto.

línea. En comparación con otras estructuras reportadas en la literatura, la propuesta reduce significativamente la complejidad del diseño, los bloques analógicos necesarios y, por lo tanto, el consumo de área del sistema [1].

En las secciones siguientes se describirá la teoría de la técnica de balanceo espectral que ha sido base para el diseño del ecualizador propuesto, así como cada uno de los bloques analógicos que lo componen.

## 4.1. Técnica de balanceo espectral

La técnica de balanceo espectral consiste en comparar dos rangos distintos del espectro de la señal recibida. Si consideramos una secuencia de datos binarios aleatoria, su espectro de potencia puede ser representado por una función  $\text{sinc}^2$ <sup>2</sup> como la siguiente [10]:

$$S_X(f) = T_b \left[ \frac{\sin(\pi f T_b)}{\pi f T_b} \right]^2 \quad (4.1.1)$$

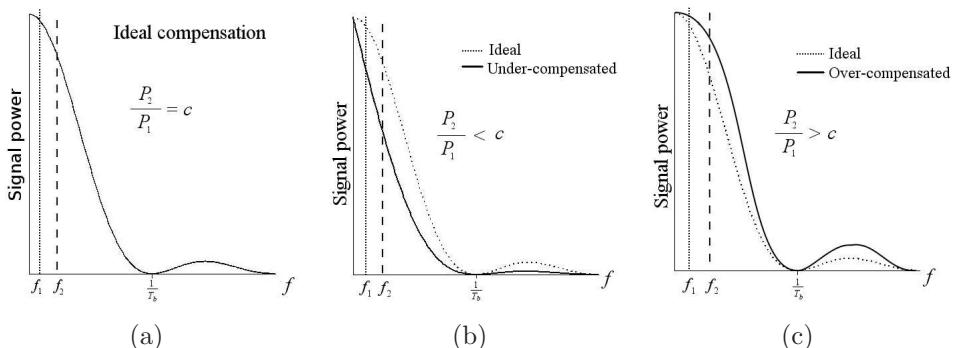

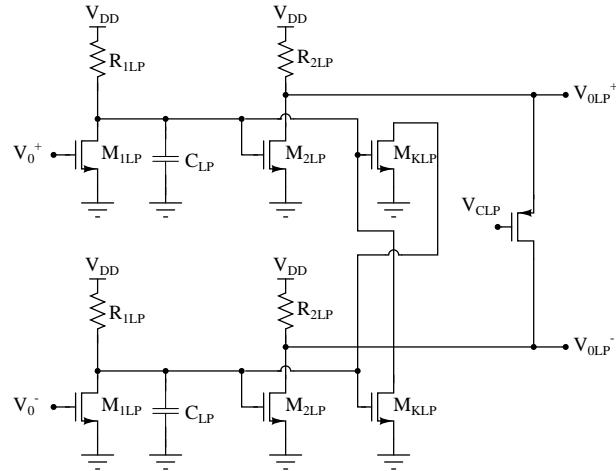

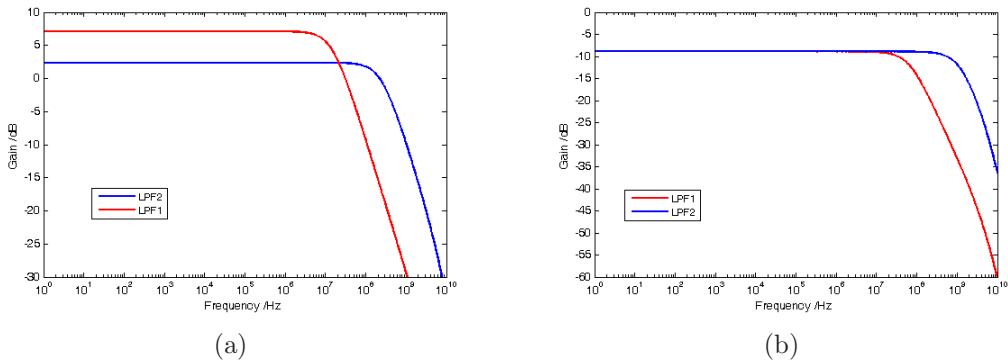

donde  $T_b$  es el periodo de bit de la secuencia de datos. Por lo tanto, el espectro de potencia se puede descomponer en dos rangos diferentes; esto se puede hacer mediante dos filtros pasa-bajas (LPFs) con diferentes frecuencias de corte. Si examinamos el espectro de potencia en la salida del ecualizador, se puede determinar si la secuencia de datos está sobre, sub o idealmente compensada, como se muestra en la Figura 4.2, y ajustar la ganancia de alta frecuencia de acuerdo a ello.

Así pues, para la función  $\text{sinc}^2$  en (4.1.1), se puede determinar que la relación de dos potencias de la señal,  $P_1$  y  $P_2$ , para dos cualesquiera rangos de frecuencia,

Figura 4.2: Densidad de potencia espectral: (a) NRZ ideal, (b) sub-compensado y (c) sobre-compensado; donde  $R_b = 1/T_b$  es la tasa de bit.

$f_1$  y  $f_2$ , es constante y se puede expresar como:

$$\frac{P_2}{P_1} = c \quad (4.1.2)$$

Con fines prácticos, se debe tomar en cuenta para la ecuación (4.1.2) que una relación de potencias pequeña hace la comparación más inexacta mientras que una relación grande causa un consumo de potencia mayor. Esta hipótesis fue comprobada mediante simulaciones en por computador a partir de las cuales se obtuvo que una relación de potencias  $c = 6,8$  era la más adecuada para usarse en la ecuación (4.1.2).

Para poder obtener las potencias  $P_1$  y  $P_2$ , la señal ecualizada pasa a través de dos filtros pasa-bajas (LPF1 y LPF2). De esta manera, los dos filtros proporcionan las distintas secciones del espectro de potencia al comparador de error como se muestra en la Figura 4.1. Unas ganancias de  $A_1 = 2,3$  y  $A_2 = 1,3$  para los filtros LPF1 y LPF2, respectivamente, proporcionan la relación de potencias deseada  $c = 6,8$ .

Para poder determinar teóricamente una aproximación de las frecuencias de corte de los filtros pasa-baja,  $f_1$  y  $f_2$ , la relación de potencias de la ecuación (4.1.2) también puede ser expresada de la siguiente manera:

$$\frac{P_2}{P_1} = \frac{A_2^2 \int_0^{f_2} S_x(f) df}{A_1^2 \int_0^{f_1} S_x(f) df} \approx \frac{A_2^2 f_2 T_b}{A_1^2 f_1 T_b} = \frac{A_2^2 f_2}{A_1^2 f_1} \quad (4.1.3)$$

Debe notarse que ésta aproximación es válida únicamente para frecuencias de corte muy por debajo de la tasa de bit y para filtros ideales *brick-wall*. Por lo tanto, tomando en cuenta (4.1.3), se han obtenido las frecuencias de corte  $f_1 = 23,6$  MHz y  $f_2 = 471$  MHz para un periodo de bit de 800 ps (tasa de bit de 1.25 Gb/s). Sin embargo, estos valores deben ser corregidos para ajustarse a filtros reales de primer orden mediante el factor  $\pi/2$  [11], lo que resulta en las frecuencias de corte  $f_1 = 15$  MHz y  $f_2 = 300$  MHz.

Como es de esperar, ambos filtros implementados realmente tendrán polos adicionales, pero su efecto no será significativo si su posición se encuentra en frecuencias mucho mayores que su frecuencia de corte. Por lo tanto, las variaciones en la señal de control,  $\Delta V_C$ , para el ecualizador se genera mediante la siguiente ecuación:

$$\Delta V_C \propto \Delta P_1 \cdot c - \Delta P_2 \quad (4.1.4)$$

Hasta este punto es importante recalcar que el uso de dos filtros pasa-bajas en el lazo de control hacen que la señal de error sea menos sensible a variaciones de PVT (Proceso, Voltaje y Temperatura). Esto es debido la simetría o *matching* con el que serán implementados en el layout gracias a que ambos tienen exactamente la misma estructura, con los condensadores como única diferencia entre ellos.

## 4.2. Ecualizador de línea

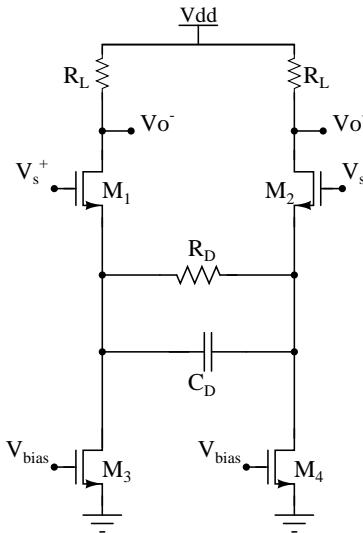

Hasta la fecha, los ecualizadores en tiempo continuo propuestos en la literatura están basados en el par diferencial degenerado que se muestra en la Figura 4.3 [12, 13]. Esta estructura se puede analizar más fácilmente considerando los transistores como ideales, para lo cual tenemos la expresión de la ganancia diferencial como:

$$A_D(s) = \frac{V_O^+ - V_O^-}{V_S^+ - V_S^-} = -\frac{g_m \cdot R_L}{1 + g_m \cdot R_D} \cdot \frac{1 + s \cdot C_D \cdot R_D}{1 + s \cdot \frac{C_D \cdot R_D}{1 + g_m \cdot R_D}} \quad (4.2.1)$$

Como se puede observar, la ganancia en DC y la posición del cero están dadas por la resistencia y el condensador del par diferencial. Esto significa que si sustituimos estos elementos pasivos por una resistencia variable y un varactor im-

Figura 4.3: Par diferencial degenerado.

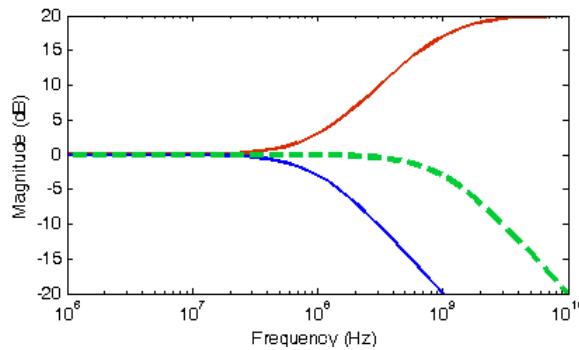

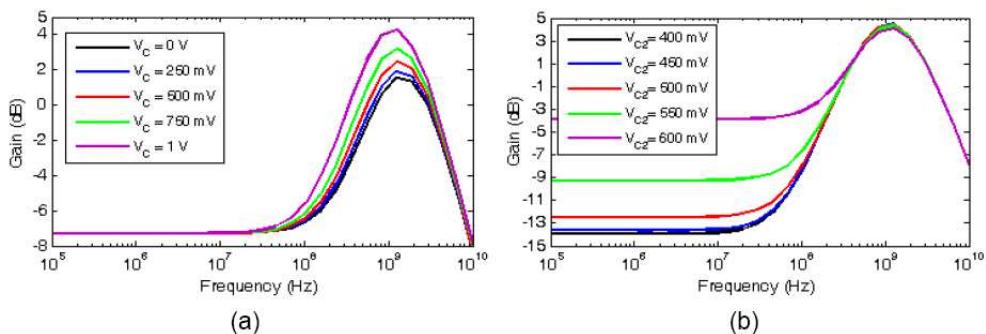

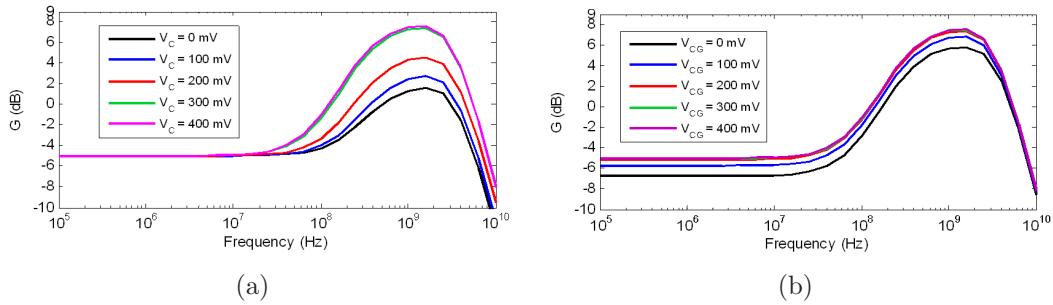

plementados mediante transistores CMOS, tendremos completo control de estos parámetros, como se puede observar en las gráficas de la Figura 4.4, donde se han realizado simulaciones para distintos valores de resistencia y capacidad.

Sin embargo, como se puede ver directamente en las gráficas de la Figura 4.4, la ganancia y la posición del cero están completamente acopladas. Esto significa que cuando se ajusta el nivel de ganancia en DC, la posición del cero cambia y si se ajusta la posición del cero, la ganancia en el pico de alta frecuencia también varía. Esta interdependencia representa una seria desventaja para la sintonización del ecualizador. Además, el bajo voltaje de alimentación limita severamente el rango dinámico del ecualizador, lo que lo pone en gran desventaja para sistemas alimentados con tensiones de 1,2 V o inferiores.

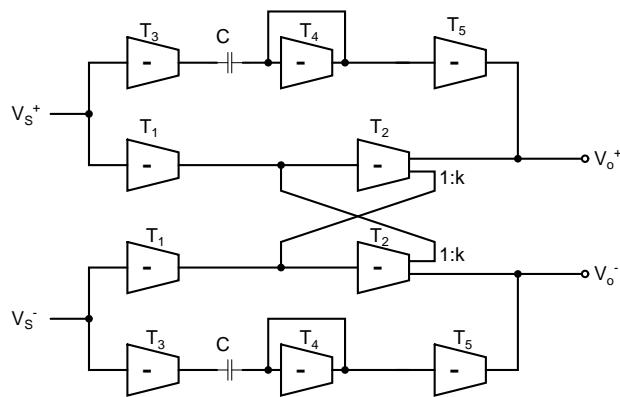

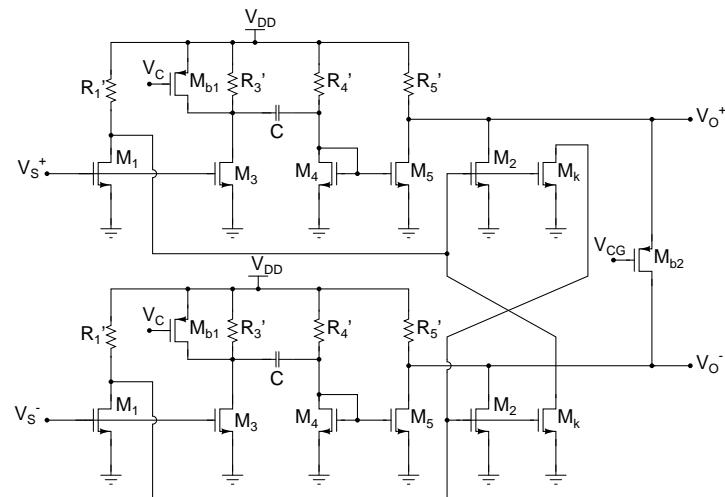

#### 4.2.1. Ecualizador de línea propuesto

En contraste con el ecualizador basado en el par diferencial degenerado, el ecualizador propuesto, que se muestra en la Figura 4.5, es una topología *split-path* completamente balanceada, donde el transductor  $T_2$  tiene dos salidas con transconductancias  $g_{m2}$  y  $kg_{m2}$ , respectivamente; la segunda salida es usada para establecer un lazo de retroalimentación parcial positivo con una configuración cruzada para incrementar la relación entre la ganancia diferencial y la de modo común.

Para frecuencias de operación muy altas y bajo voltaje de alimentación, el transductor más simple que tiene un buen desempeño en estos casos es un transistor operando en una topología de fuente-común, el cual ha sido empleado para implementar el ecualizador de línea propuesto, como se muestra en la Figura

Figura 4.4: Respuesta frecuencial del par diferencial degenerado para distintos valores de control

(a) posición del cero y (b) ganancia en DC.

Figura 4.5: Diagrama de bloques del ecualizador de línea propuesto.

Figura 4.6: Topología a nivel transistor del ecualizador de línea propuesto.

4.6.

Para poder obtener la función de transferencia del ecualizador, consideremos los transistores como transconductores ideales, cuya transconductancia está dada por  $g_{m_i}$ , y  $R_i$  es la resistencia equivalente en sus nodos de drenador, las expresiones aproximadas para la ganancia diferencial y de modo común son [14]

$$A_D(s) = \frac{V_O^+ - V_O^-}{V_S^+ - V_S^-} = -\frac{R_5 \cdot R_1 \cdot g_{m1} \cdot g_{m2}}{R_1 \cdot k \cdot g_{m2} - 1} \cdot \frac{1 + sC \left( \frac{g_{m5} \cdot g_{m3} \cdot R_3}{g_{m1} \cdot g_{m2} \cdot g_{m4}} \cdot \left( k \cdot g_{m2} - \frac{1}{R_1} \right) - R_3 - g_{m4}^{-1} \right)}{1 + sC(R_3 + g_{m4}^{-1})} \quad (4.2.2)$$

$$A_C(s) = \frac{2 \cdot V_O^+}{V_S^+ + V_S^-} = \frac{R_5 \cdot R_1 \cdot g_{m1} \cdot g_{m2}}{R_1 \cdot k \cdot g_{m2} + 1} \cdot \frac{1 + sC \left( \frac{g_{m5} \cdot g_{m3} \cdot R_3}{g_{m1} \cdot g_{m2} \cdot g_{m4}} \cdot \left( k \cdot g_{m2} + \frac{1}{R_1} \right) + R_3 + g_{m4}^{-1} \right)}{1 + sC(R_3 + g_{m4}^{-1})} \quad (4.2.3)$$

Se debe tomar en cuenta que  $k$  es la relación de dimensiones del transistor entre  $M_k$  y  $M_2$ . Como se puede ver claramente de las ecuaciones (4.2.2) y (4.7), las funciones de transferencia que caracterizan al ecualizador son muy complejas. Sin embargo, se puede obtener la razón de rechazo al modo común (CMRR, por sus siglas en inglés) fácilmente si se evalúan las ganancias diferencial y de modo común para  $s = 0$  y se calcula la relación como se muestra a continuación [14]

$$CMRR = \frac{A_D(0)}{A_C(0)} = \frac{1 + R_1 \cdot k \cdot g_{m2}}{1 - R_1 \cdot k \cdot g_{m2}} \quad (4.2.4)$$

donde  $k = 2$  garantiza la estabilidad del ecualizador a la vez que un CMRR similar al del par degenerado se puede obtener bajo las mismas condiciones de operación. El CMRR del ecualizador propuesto es de 9.8 dB mientras que el del par diferencial degenerado es de 9 dB para las mismas condiciones. El circuito puede ajustar la ganancia de alta frecuencia modificando el voltaje de compuerta,  $V_C$ , del transistor  $M_{b1}$ , que se coloca en paralelo con la resistencia  $R_3$ . La ganancia del ecualizador puede ser sintonizada, sin afectar el voltaje de modo común a la salida, usando un resistor flotante de carga, el cual es implementado con un transistor,  $M_{b2}$ , polarizado en la zona de triodo mediante el voltaje de control  $V_{CG}$ . A diferencia del par diferencial degenerado, el control del ecualizador de la ganancia y el cero están completamente desacoplados. En la Figura 4.7(a) y 4.7(b) se muestra la respuesta frecuencial para distintos valores de  $V_C$  y  $V_{CG}$ , respectivamente, donde

Figura 4.7: Respuesta frecuencial del ecualizador propuesto (a) posición del cero vs.  $V_C$  y (b) ganancia en DC vs.  $V_{CG}$ .

se puede ver cómo la modificación de la ganancia no afecta a la posición del cero y viceversa. Se ha logrado obtener un rango para la posición del cero desde 500 MHz hasta 100 MHz para valores de  $V_C$  desde 0 V hasta 400 mV, respectivamente, y un rango en la ganancia en DC desde -6.7 dB hasta -5 dB para valores de  $V_{CG}$  desde 0 V hasta 400 mV también.

## 4.3. Lazo de adaptación

### 4.3.1. Filtros del lazo de adaptación

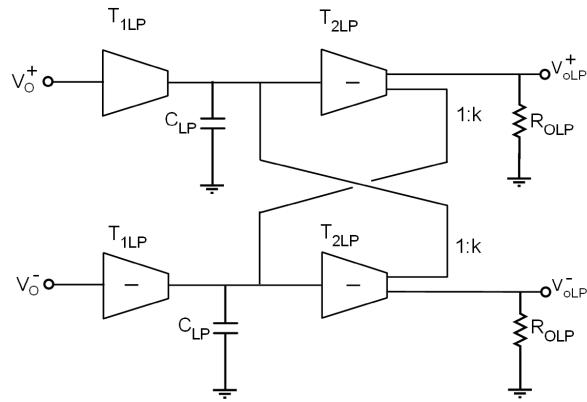

Como se ha descrito anteriormente, para obtener las diferentes partes del espectro de la señal, se necesitan dos filtros pasa-bajas de primer orden. Los diagramas de bloques de los dos filtros se muestra en la Figura 4.8, donde se puede ver que se ha utilizado una estructura similar a la del ecualizador, es decir, retroalimentación parcial positiva (con  $k = 0,5$  en este caso). Gracias a esto, se ha reducido las variaciones en el modo común de la señal, lo cual contribuye a que la comparación de potencias se realice de manera correcta. Una de las ventajas en utilizar dos filtros pasa-bajas es que ambos tendrán la misma estructura como la que se muestra en la Figura 4.8, lo cual ayudará a que el layout pueda ser generado con gran modularidad, haciendo que el *matching* de las distintas etapas sea más fácil.

Siguiendo la misma línea de diseño que con el ecualizador, se han empleado en ambos filtros pasa-bajas transistores en configuración de fuente común y polarizados con una resistencia para mantener la operatividad en bajo voltaje del sistema. El esquemático a nivel transistor de los filtros propuestos se muestra en la Figura 4.9.

Figura 4.8: Diagrama de bloques de los dos filtros pasa-bajas.

Figura 4.9: Topología a nivel transistor de los filtros pasa-bajas propuestos.

Considerando transistores ideales, caracterizados por sus transconductancia  $g_{miLP}$  y con  $R_{iLP}$  como la resistencia equivalente en su nodo de drenador, la expresión aproximada para las ganancias diferencial y de modo común de los filtros pasa-bajas son, respectivamente:

$$\begin{aligned} A_{D_{LPF}}(s) &= \frac{V_{OLP}^+ - V_{OLP}^-}{V_O^+ - V_O^-} \\ &= \frac{R_{1LP} \cdot R_{2LP} \cdot g_{m1LP} \cdot g_{m2LP}}{1 - R_{1LP} \cdot k \cdot g_{m2LP}} \cdot \frac{1}{1 + s \frac{C_i \cdot R_{1LP}}{1 - R_{1LP} \cdot k \cdot g_{m2LP}}} \quad (4.3.1) \end{aligned}$$

$$\begin{aligned}

A_{C_{LPF}}(s) &= \frac{2 \cdot V_{OLP}^+}{V_O^+ + V_O^-} \\

&= \frac{R_{1LP} \cdot R_{2LP} \cdot g_{m1LP} \cdot g_{m2LP}}{1 + R_{1LP} \cdot k \cdot g_{m2LP}} \cdot \frac{1}{1 + s \frac{C_i \cdot R_{1LP}}{1 + R_{1LP} \cdot k \cdot g_{m2LP}}} \quad (4.3.2)

\end{aligned}$$

donde los condensadores de integración son  $C_{1LP} = 6,2$  pF y  $C_{2LP} = 0,26$  pF para los filtros LPF1 y LPF2, respectivamente, mientras que las capacidades parásitas han sido despreciadas. Se puede obtener directamente de (4.3.1) y (4.10) que el CMRR en DC para ambos filtros es

$$CMRR = \frac{A_{DLP}(0)}{A_{CLP}(0)} = \frac{1 + R_{1LP} \cdot k \cdot g_{m2LP}}{1 - R_{1LP} \cdot k \cdot g_{m2LP}} \quad (4.3.3)$$

Es importante notar que, de acuerdo con (4.3.3), si se diseñan correctamente los filtros, se puede obtener un alto CMRR. Mediante simulación se ha comprobado que la ganancia de modo común es de -8.9 dB para los dos filtros. En la Figura 4.10 se muestra, obtenida por simulación, la respuesta frecuencial (diferencial y de modo común) para ambos filtros. Los filtros LPF1 y LPF2 tienen ganancias diferenciales de 7.2 dB y 2.3 dB y frecuencias de corte de 15 MHz y 300 MHz, respectivamente.

Figura 4.10: Respuesta frecuencial de los filtros de lazo: (a) diferencial y (b) de modo común.

### 4.3.2. Comparador de potencia

En la literatura se han reportado comparadores de potencia basados en el uso de dos filtros seguidos por dos rectificadores y un amplificador de error. Estos rectificadores generalmente están basados en pares diferenciales con su voltaje de salida en el nodo de fuente común [15]. Esta configuración no es realmente un comparador de potencia y además sufre de un rango de salida pequeño en altas frecuencias, principalmente debido a las capacidades parásitas del nodo de fuente común. Por lo tanto, estos rectificadores necesitan usar un amplificador de error con una alta ganancia y bajo nivel de offset, lo cual hace que el diseño sea más complicado e incrementa el consumo de potencia en unos pocos mW [15].

Como alternativa al uso de amplificadores de error, se puede utilizar un convertidor de voltaje-corriente (V/I) empleando la técnica conocida como *current-steering*, lo que facilita la integración de la señal de error mediante un condensador a tierra. Por otro lado, ésta técnica empleada para implementar el comparador de error que ha sido reportado en [16, 6, 17], produce un rango de salida para la señal de error muy amplio, lo cual reduce las especificaciones de ganancia para que el amplificador de error ajuste la señal de control,  $V_C$ , al nivel requerido por el ecualizador de línea. Sin embargo, debido a que se necesita un voltaje de saturación<sup>1</sup>,  $V_{Dsat}$ , en cada transistor apilado para que opere en la región de saturación, el nivel máximo de voltaje de entrada se reduce a  $V_{DD} - 3V_{Dsat}$ , lo cual, para aplicaciones de bajo voltaje, limita severamente los límites del rango de entrada.

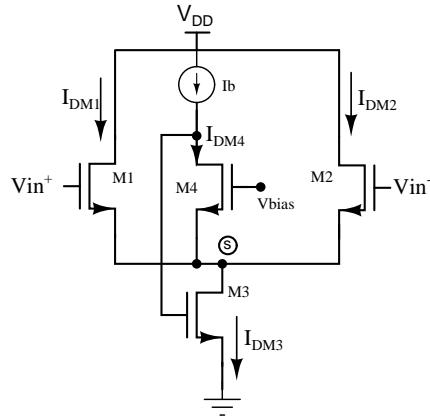

El comparador de potencia propuesto está basado en el par diferencial *flipped-voltage follower* (FVFDP, por sus siglas en inglés) [18], que se muestra en la Figura 4.11, donde los transistores M<sub>1</sub> y M<sub>2</sub> utilizan la característica única del par diferencial acoplado para detectar la potencia de la señal gracias a la respuesta cuadrática de corriente-voltaje de los transistores MOS operando en la región de saturación [19].

Debido a que la corriente de polarización,  $I_b$ , fija una corriente de drenador constante en M<sub>4</sub>,  $I_{DM4}$ , la corriente total de drenador del par diferencial puede obtenerse a través de M<sub>3</sub> como:

---

<sup>1</sup>El voltaje de saturación es el voltaje de drenador a fuente necesario para que el transistor MOS opere en la región de saturación  $V_{Dsat} > V_{GS} - V_{TH}$ .

Figura 4.11: Par diferencial *flipped-voltage follower*.

Figura 4.12: Comparador de potencia propuesto.

$$I_{DM3} = I_{DM1} + I_{DM2} + I_{DM4} = \mu_n C_{OX} \frac{W}{L} \left[ (V_{in,cm} - V_{THn})^2 + V_{in}^2 \right] + I_b \quad (4.3.4)$$

donde  $V_{in,cm} = 750$  mV,  $V_{in} = V_{in}^+ = -V_{in}^-$ ,  $V_{THn}$  es el voltaje umbral del transistor NMOS para la tecnología empleada, y el resto de los parámetros tienen su significado habitual.

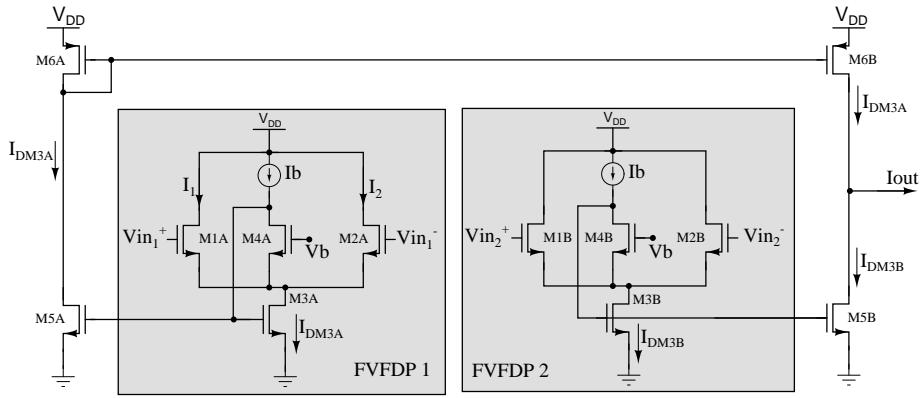

Claramente se puede ver de la ecuación (4.3.4) que la corriente total de cada par diferencial contiene el término  $V_{in}^2$  que es proporcional a la potencia de la señal. Ya que cada FVFDP detecta las potencias  $P_1$  y  $P_2$  de las señales  $V_{in1}$  y  $V_{in2}$ , respectivamente, la comparación entre ellas se puede realizar mediante su diferencia, es decir:

$$I_{out} \sim P_1 - P_2 \quad (4.3.5)$$

donde  $I_{out}$  representa la corriente de error. La ecuación (4.3.5) puede ser directamente implementada como un restador de corriente mediante la etapa de salida formada por M<sub>5</sub>-M<sub>6</sub> como se muestra en la Figura 4.12. De esta manera, la corriente de salida,  $I_{out}$ , se puede expresar como

$$I_{out} = I_{DM3A} - I_{DM3B} = \frac{1}{4}\mu_n C_{OX} \frac{W}{L} \left[ V_{in1}^2 - V_{in2}^2 \right] \quad (4.3.6)$$

donde  $V_{in1} = V_{in1}^+ = -V_{in1}^-$  y  $V_{in2} = V_{in2}^+ = -V_{in2}^-$  corresponden a los voltajes de salida de los filtros LPF1 y LPF2, respectivamente.

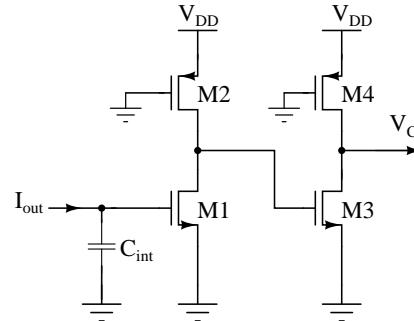

Para generar el voltaje de error,  $V_C$ , la corriente  $I_{out}$  es integrada por un condensador a tierra,  $C_{int} = 7\text{pF}$ , y posteriormente amplificado y desplazado de nivel de DC con un amplificador de fuente común de dos etapas para ser alimentado

Figura 4.13: Esquemático del integrador en modo corriente.

Figura 4.14: Respuesta transitoria del comparador de potencia.

hacia el ecualizador, como se muestra en la Figura 4.13

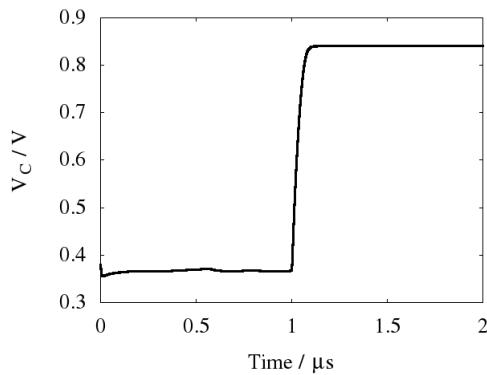

En la Figura 4.14 se muestra la respuesta transitoria del comparador de potencia, donde el voltaje de control,  $V_C$ , se obtiene, de acuerdo a la ecuación (4.1.4), con la diferencia entre dos señales de entrada con distintas potencias,  $P_1 = -16 \text{ dBm}$  y  $P_2 = -6,47 \text{ dBm}$ , respectivamente. De esta manera,  $P_1 = P_2$  en el rango de 0 hasta  $1 \mu\text{s}$ ; por otro lado,  $P_1 > P_2$  desde  $1 \mu\text{s}$  hasta  $2 \mu\text{s}$ .

---

## Capítulo 5

# Resultados

---

El ecualizador adaptativo en tiempo continuo propuesto se ha diseñado en una tecnología estándar CMOS de 0,8 V y 0,18  $\mu\text{m}$ , pero con un voltaje de alimentación simple de sólo 1 V. Cabe recalcar que este nivel de polarización se ha elegido como un banco de pruebas para demostrar la escalabilidad del sistema a tecnologías de canal más corto tales como 45 nm. Como se ha comentado anteriormente, se ha incluido un driver de salida con una resistencia de salida de 50  $\Omega$  para poder realizar las mediciones experimentales. Además, para facilitar el diseño del driver (que no es el objetivo de este trabajo), se ha usado otro voltaje de alimentación de 1,8 V [20].

### 5.1. Resultados de simulación post-layout

Se han realizado simulaciones usando Spectre con modelos de transistor BSIM3v3.2 nivel 53. La tecnología tiene 1 polisilicio y 6 niveles de metal; los condensadores son fabricados con estructuras metal-aislante-metal (MIM, por sus siglas en inglés) las cuales tienen 1 fF/ $\mu\text{m}^2$  y son implementados entre Metal 5 y Metal 6; y los resistores son implementados con capas de polisilicio de alta resistividad (HRP, por sus siglas en inglés), las cuales tienen 1039  $\Omega/\text{sq}$ . Los valores de resistencia usados en el diseño propuesto están en el rango desde 50  $\Omega$  hasta un máximo de 5 k $\Omega$ . Por otro lado, se han usado longitudes de canal mínimos permitidos en la mayoría de los bloques analógicos debido a la alta frecuencia de la señal de entrada. En contraste, se ha usado una longitud de canal de 1  $\mu\text{m}$  en el comparador de potencia para lograr obtener un mejor desempeño en DC.

En la Figura 5.1 se muestra el layout completo. Varias técnicas, tales como

Figura 5.1: Layout del ecualizador adaptativo propuesto. Área activa de  $169 \mu\text{m}^2$

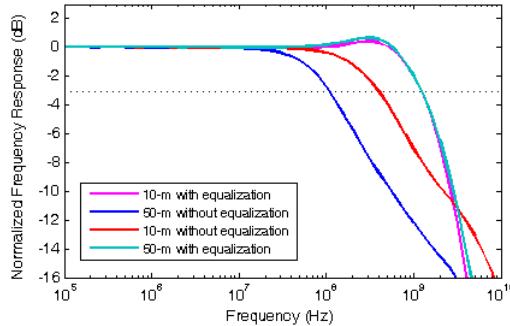

Figura 5.2: Respuesta frecuencial normalizada antes y después de la ecualización

caminos de señal simétricos, elementos *dummy*, anillos de guarda y aislamiento del substrato, para asegurar la correcta operación de los circuitos en condiciones de alta frecuencia y bajo voltaje.

El consumo total del ecualizador completo es de aproximadamente 134 mW, donde 9.4 mW corresponden al ecualizador de línea, 3.9 mW a los filtros del lazo, 1 mW al comparador de potencia y 120 mW al driver de salida.

Debido a que el ecualizador ha sido diseñado para compensar específicamente el limitado ancho de banda de una SI-POF, se han empleado modelos eléctricos con elementos pasivos para modelar la respuesta frecuencial de una SI-POF Mitsubishi

| Parámetro                      | Resultado                                            |

|--------------------------------|------------------------------------------------------|

| Tipo de fibra y longitud       | 10-50 m SI-POF                                       |

| Tecnología                     | CMOS 0,18 $\mu\text{m}$                              |

| Voltaje de alimentación        | 1 V                                                  |

| Tasa de Bit                    | 1,25 Gb/s                                            |

| Mejora del ancho de banda      | Desde 100 MHz (50 m) y 300 MHz (100m) hasta 1,23 GHz |

| Densidad de ruido a la entrada | 9,8 nV/Hz <sup>1/2</sup>                             |

|                                | 9,4 mW (ecualizador de línea)                        |

|                                | 3,9 mW (filtros de lazo)                             |

| Disipación de potencia en DC   | 1 mW (comparador de potencia)                        |

|                                | 119,7 mW (driver)                                    |

| Rango dinámico de entrada      | 63 dB                                                |

| CMRR                           | 9,8 dB                                               |

Tabla 5.1: Resumen de los resultados del ecualizador adaptativo.

GH para distintas longitudes.

Los principales resultados de simulación obtenidos se resumen en la Tabla 5.1. La respuesta frecuencial normalizada antes y después de la ecualización se muestra en la Figura 5.2 para dos longitudes de fibra distintos. Se debe hacer notar que el ancho de banda espectral de la señal recibida se puede mejorar desde 100 MHz y 300 MHz hasta 1.23 GHz para las longitudes de 50 m y 10 m de POF, respectivamente. Este resultado valida la efectividad del sistema propuesto.

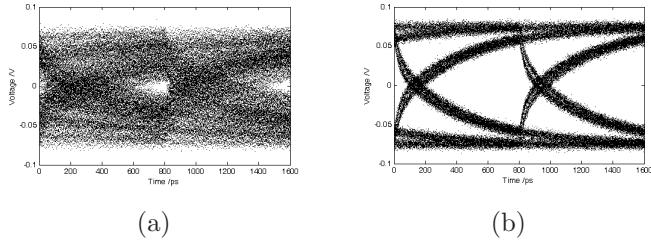

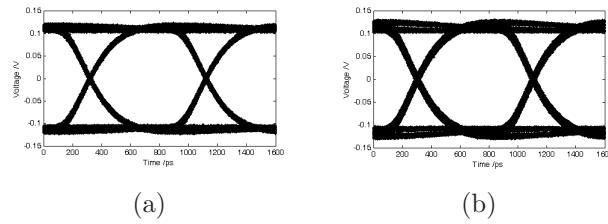

Para poder observar mejor el efecto de la ecualización sobre una señal afectada de ISI, en la Figura 5.3 se muestran los diagramas de ojos de la señal a la salida de la fibra para 10 m y 50 m, donde se puede ver que en el peor caso, el ojo se encuentra casi completamente cerrado, lo que definitivamente ocasionaría errores severos en la recuperación de la información. Por otro lado, en la Figura 5.4 se muestra nuevamente los diagramas de ojos pero ahora a la salida del ecualizador adaptativo. Se puede ver claramente cómo la señal mejora significativamente para las dos longitudes de fibra.

Figura 5.3: Diagramas de ojos antes de la ecualización a 1.25 Gb/s para (a) 50 m y (b) 10 m de POF.

Figura 5.4: Diagrama de ojos a la salida del circuito a 1.25 Gb/s para (a) 50 m y (b) 10 m de POF.

Figura 5.5: Respuesta transitoria en los diferentes bloques que componen el ecualizador adaptativo.

Finalmente, para poder ilustrar de manera gráfica el comportamiento del circuito, en la Figura 5.5 se ha seguido la pista a la señal en cada punto del ecualizador adaptativo. De esta manera se puede observar la operación que efectúa cada uno de los bloques analógicos que componen el sistema en el proceso de ecualización de la señal.

---

## Capítulo 6

# Conclusiones

---

En este trabajo se ha presentado el diseño completo de un ecualizador adaptativo de tiempo continuo basado en la técnica de balanceo espectral. Se ha implementado en una tecnología estándar CMOS de  $0.18\text{ }\mu\text{m}$ . Como meta específica se fijó compensar el ancho de banda de una fibra de plástico Mitsubishi GH para dos distintas longitudes (10 m y 50 m) con señales binarias NRZ a una tasa de bit de 1.25 Gb/s, lo cual se ha logrado satisfactoriamente. Sin embargo, la metodología de diseño que se ha desarrollado es válida para cualquier canal de comunicaciones, ajustando la posición del polo y el cero en el ecualizador, así como las frecuencias de corte de los filtros del lazo de adaptación, de acuerdo a la respuesta frecuencial del canal deseado.

Se ha logrado aumentar el ancho de banda de la POF para 50 m y 10 m desde 100 MHz y 300 MHz, respectivamente, hasta 1.23 GHz. Es importante resaltar que los resultados presentados en el capítulo 5 corresponden a simulaciones post-layout, las cuales incluyen todas las capacidades y resistencias parásitas del trazado físico del circuito integrado. Esto nos proporciona un resultado muy próximo al previsto de post-fabricación.

El bajo consumo de potencia que presenta el sistema, así como la poca área total consumida, hace la propuesta interesante para aplicaciones de enlace multi punto, donde el coste unitario debe ser muy reducido.

Por otro lado, se han abierto varias líneas de investigación que se pueden seguir a partir de este trabajo, las cuales se enumeran a continuación:

- 1.-** Estudiar distintas estructuras del ecualizador para verificar la viabilidad de una adaptabilidad basada en un código digital.

- 2.-** Incorporar al sistema una característica multi-rate, es decir, que funcione de

igual manera a distintas tasas de bit y diferentes modulaciones.

- 3.-** Fabricar físicamente el ecualizador adaptativo propuesto y desarrollar un *set-up* de pruebas para comprobar mediante mediciones experimentales la funcionalidad del sistema.

# Bibliografía

---

- [1] J. Liu and X. Lin. Equalization in high-speed communication systems. *IEEE Circuits and Systems Magazine*, 4(2):4–17, 2004.

- [2] R. Gaudino, J.R. Molina, D. Zeolla, P. Savio, S. Straullu, A. Nespolo, S. Abrate, C. Zerna, J. Sundermeyer, A. Fiederer, N. Verwaal, B. Offenbeck, and N. Weber. Architectures for low-cost Gbit/s POF links for home networking. In *Future Network and Mobile Summit*, pages 1–7, June 2010.

- [3] O. Ziemann, J. Kranser, P.E. Zamzow, and W. Daum. *POF Handbook Optical Short Range Transmission Systems*. Springer, 2008.

- [4] L. Hoon and H. Gunhee. *A low power and small area analog adaptive line equalizer for 100 Mb/s data rate on UTP cable*, volume 87, no. 4, pages 634–639. IEICE transactions on electronics, 2004.

- [5] Michael Peffers. *The Benefits of Using Linear Equalization in Backplane and Cable Applications*. Texas Instruments, June 2013.

- [6] J. Lee. A 20-Gb/s adaptive equalizer in 0.13- $\mu$ m CMOS technology. *IEEE Journal of Solid State Circuits*, 41(9):2058–2066, 2006.

- [7] D. Hong and K.-T. Cheng. A two-tone test method for continuous-time adaptive equalizers. *Springer*, pages 75–87, 2010.

- [8] *3.2 Gbps equalizer and cable driver*. Maxim Integrated Products, 2005.

- [9] C. Gimeno, C. Sánchez-Azqueta, E. Guerrero, C. Aldea, , and S. Celma. A 1-V 1.25-Gbps CMOS analog front-end for short reach optical links. In *IEEE European Solid-State Circuits Conference*, 2013.

- [10] Behzad Razavi. *Design of Integrated Circuits for Optical Communications*. Mc Graw Hill, 2003.

- [11] C. Kuo-Hsing, T. Yu-Chang, W. Yen-Hsuehand, and L. Ying-Fu. A 5-Gb/s Inductorless CMOS Adaptive Equalizer for PCI Express Generation II Applications. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 57(5):324–328, 2010.

- [12] F. Tavernier, C. Hermans, and M. Steyaert. Optimised equaliser for differential CMOS photodiodes. *Electronics Letters*, 42(17):1002–1003, August 2006.

- [13] J. Hao, Z. Yumei, and J. Yishu. A low-power 3.125 Gbps CMOS analog equalizer for serial links. *Journal of Semiconductors*, 3(11), November 2010.

- [14] C. Gimeno, E. Guerrero, S. Celma, and C. Aldea. Reliable CMOS adaptive equalizer for short-haul optical networks. *Microelectronics Reliability, in press*. DOI: 10.1016/j.microrel.2013.07.041, .

- [15] R. Sun, J. Park, F. OMahony, and C. Yue. A low-power, 20-Gb/s continuous-time adaptive passive equalizer. In *Proc. of IEEE International Symposium on Circuits and Systems*, volume 41, no. 9, pages 920–923, May 2005.

- [16] J. Hye-Yoon and K. Lee-Sup. A data-pattern-tolerant adaptive equalizer using the spectrum balancing method. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 57(3):228–232, 2010.

- [17] H. Dongwoo, S. Saberi, C. Kwang-Ting, and CP. Yue. A two-tone test method for continuous-time adaptive equalizers. In *Proc. of Design, Automation & Test in Europe Conference & Exhibition*, pages 1–6, 2007.

- [18] A. López-Martin, J. Ramírez-Angulo, R. Chintham, and R. Carvajal. Class AB CMOS analog squarer circuit. *Electronics Letters*, 43(20), 2007.

- [19] E. Guerrero, C. Gimeno, C. Sánchez-Azqueta, and S. Celma. Power comparator for continuous-time adaptive equalization in ethernet-based instrumentation. *Measurement Science and Technology*, 25(8), 2014.

- [20] C. Gimeno, C. Aldea, S. Celma, and F. Aznar. Low-voltage low-power CMOS receiver front-end for gigabit short-reach optical communications. *International Journal of Circuit Theory and Applications*, DOI: 10.1002/cta.1819,