# Class-D/DE Dual-Mode-Operation Resonant Converter for Improved-Efficiency Domestic Induction Heating System

Héctor Sarnago *Student Member, IEEE*, Óscar Lucía, *Member, IEEE*

Arturo Medianó, *Senior Member, IEEE*, José. M. Burdío, *Member, IEEE*

Department of Electronic Engineering and Communications. University of Zaragoza, Spain

E-Mail: hsarnago@unizar.es, olucia@unizar.es, amediano@unizar.es

*-An earlier version of this paper was presented in the APEC12 conference held in Orlando, FL.-*

**Corresponding author:** Héctor Sarnago

E-mail: hsarnago@unizar.es

Phone: +34-976 762382

Fax: +34-976 762111.

Postal address: María de Luna, 1. 50018 Zaragoza. Spain.

**Keywords:** Resonant power conversion, Inverter, Induction heating.

## Abstract.

Induction heating (IH) technology is nowadays widely present in domestic appliances because of its cleanliness, high efficiency, and faster heating process. All of these advantages are due to its heating process, where the pot is directly heated by the induced currents generated with a varying magnetic field. As a result, the glass where the pot is supported is not directly heated and, consequently, efficiency and heating times are improved.

Induction heating systems are based on dc-link inverters to generate the required alternating current to feed the inductor. Usually, resonant converters are used to achieve higher efficiencies and power densities. In such systems, the maximum output power and efficiency are achieved at the resonant frequency, and the switching frequency is increased to reduce the output power. As a consequence, in these converters the efficiency is also reduced in the low-medium output power range.

This paper proposes the use of the half-bridge inverter in two operating modes to achieve higher efficiency in a wide output power range. The power converter topology can be reconfigured by changing the resonant capacitors through electromechanical relays. As a consequence, the entire efficiency of the cooking process is improved with a cost-effective procedure.

## **I. INTRODUCTION**

The main advantages of domestic induction heating technology are the reduced heating times, cleanliness, higher efficiency, and the more versatile cooking surfaces [1]. Induction heaters directly heat up the vessel by means of a varying magnetic field in the range of 20 kHz to 100 kHz. This magnetic field is generated by an inductor-coil system supplied by a resonant power converter.

A cooking process can usually be divided into two parts. The first one it is known as pre-heating, and it is used to rapidly increase the vessel temperature to the desired level. Higher output power levels for a short time are used in this part. The second one consists of holding the temperature for a long time with low-medium output power levels. As a result, the efficiency of low-middle power levels has a significant impact on the efficiency of the whole cooking process.

The resonant converters used to supply the inductor-pot system can be classified as a function of the number of active devices, which is directly related with the final cost. For low-cost appliances and low output power levels, the one switch topology (1-SW) is the most used [2]. The half-bridge inverter is the most used topology [1], [3-6] for medium-high output power levels due to its high efficiency and low voltage stress across the switching devices. Finally, for higher output power levels, the full-bridge inverter is used [7-9].

Considering the aforementioned alternatives, most of the commercial solutions use the half-bridge ZVS series resonant inverter (class D operation mode) because of its robustness and control simplicity [10-15]. For this topology and operation mode, the maximum output power occurs at the resonant frequency, yielding to the maximum efficiency. However, lower efficiency is achieved at low-medium output power levels due to the higher switching frequency [7], [10], [16]. Usually, pulse density modulation (PDM) is applied to keep high efficiency in the low output power range [10], [17], [18]. However, it increases flicker emissions, which can compromise the appliance electromagnetic compatibility (EMC). For this reason, PDM is usually applied at high switching frequencies, i.e. low output power, increasing switching losses. To overcome this limitation, a dual-mode-operation resonant converter is proposed [19] which further improves efficiency in the low output power range due to the reduced switching losses. Class-D half-bridge converter is used in the high output power range, whereas class-DE half bridge converter [20], [21] is used in the low to medium output power range. The combination of these operation modes achieves high efficiency levels in a wider range of output power levels. In this paper, the proposed converter is analytically studied and additional implementation and experimental results are given to prove the feasibility of the proposed converter.

This paper is organized as follows. Section II describes the proposed dual-mode resonant converter. Section III performs an efficiency analysis, while Section IV introduces the modulation strategies for the proposed hybrid converter. Finally, the experimental results are shown in Section V and the main conclusions of this paper are outlined in Section VI.

## II. DUAL MODE RESONANT CONVERTER

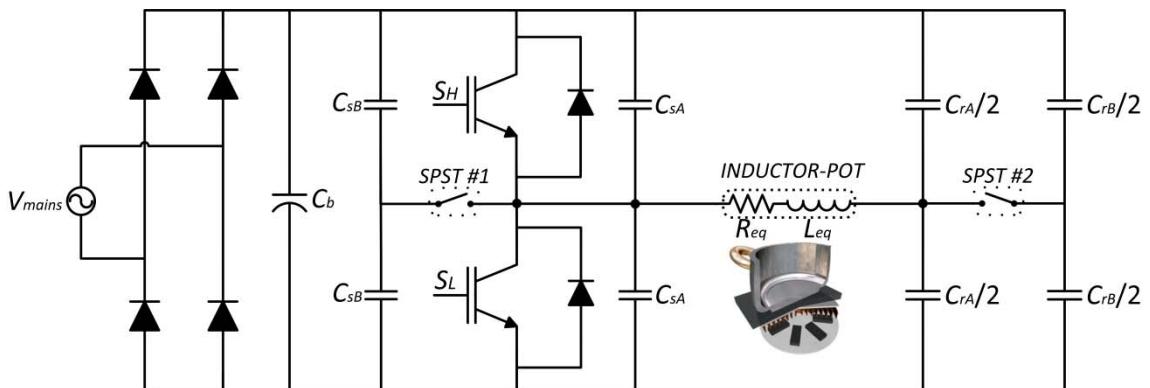

The series resonant half-bridge applied to induction heating operates at switching frequencies higher than the resonant frequency to achieve zero voltage switching (ZVS) conditions [3]. To reduce switch-off switching losses, a lossless snubber network ( $C_s$ ) is added. Typically, class-D operation mode implies that the snubber capacitor  $C_s$  is much lower than the resonant capacitor  $C_r$  [22]. However, if the class E conditions are achieved, i.e. ZVS and zero voltage derivative switching (ZVDS) at the turn-off, the operation mode is known as class DE. This operation mode ensures zero switching losses, but the maximum output power is lower than in class D operation mode. Considering this, a dual-mode resonant converter implementation is proposed in order to improve the efficiency in the whole operating range. Fig. 1 shows the proposed implementation scheme, where electromechanical switches SPST 1 and 2 allow varying the snubber and resonant capacitance in order to change the operation mode. The following subsections details the design procedure for both operation modes, where the superscript D denotes the class-D operation mode and the superscript DE is used for the class-DE operation mode. The operation modes of the half-bridge inverter, including class-D and class-DE operation, are shown in Fig. 2.

Fig. 1. Dual-mode series resonant half-bridge schematic

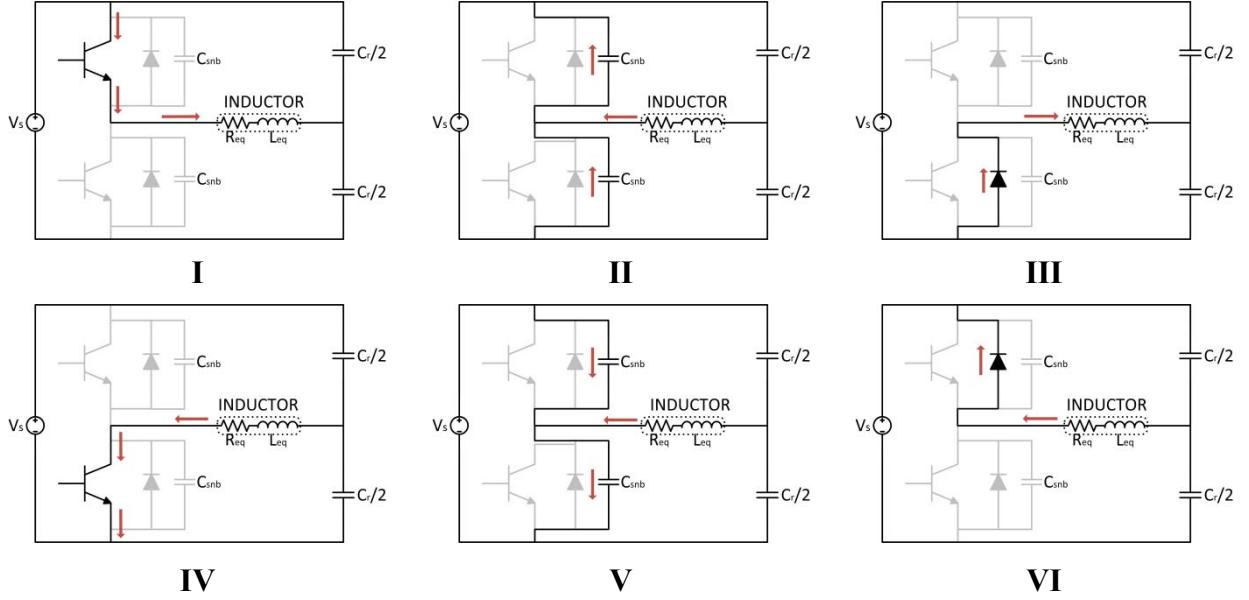

Fig. 2. Main circuit states of the half-bridge series resonant inverter.

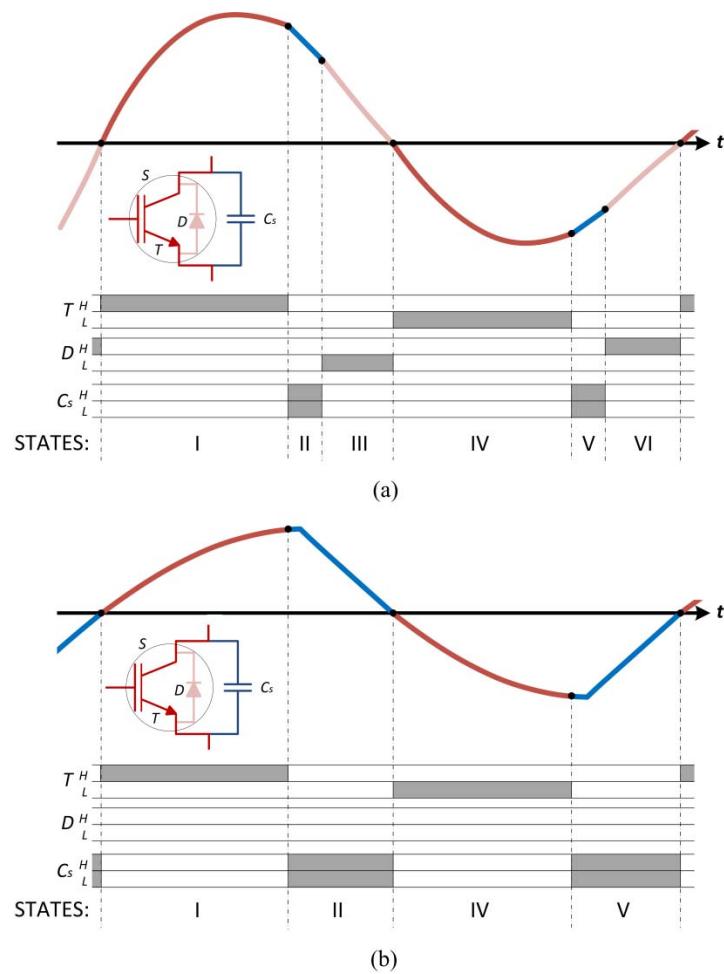

During the first state (I), the load current is positive and it is supplied by the high-side transistor. When high-side transistor is deactivated, the switch-off current is used to charge/discharge the snubber capacitors (state II), i.e. the high-side snubber capacitor is charged to the supply voltage whereas the low-side snubber capacitor is discharged. In state III, the load current is also positive, and thus, it is supplied by the low-side diode. When the load current becomes negative (state IV), it is supplied by the low-side transistor. As soon as the low-side transistor is deactivated (state V), the load current charges the low-side snubber capacitor to the supply voltage whereas the high-side snubber capacitor is discharged. When both snubber capacitors are charged/discharged, the negative load current flows through the high-side diode (state VI). Finally, when the load current reaches zero, the load current is supplied by upper transistor (state I). Class-D operation mode uses configurations I to VI, whereas in class-DE operation mode the configurations II and V, i.e. snubber capacitors charge/discharge, are extended avoiding the use of configurations III and VI, diode conduction.

#### A. Class-D operation mode

The output power in the class-D inverter can be determined using Fourier-transform as expressed in the following expression [3].

$$\begin{aligned}

P_o^D &= \sum_{h=1}^{\infty} R_{eq} I_{o, rms}^2 = \sum_{h=1}^{\infty} R_{eq} \frac{V_{0, rms}^2}{R_{eq}^2 + (h2\pi f_{sw} L_{eq} - \frac{1}{h2\pi f_{sw} C_r^D})} = \\

&= \sum_{h=1}^{\infty} \frac{2R_{eq} V_{mains}^2 / (h\pi)^2}{R_{eq}^2 + (h2\pi f_{sw} L_{eq} - \frac{1}{h2\pi f_{sw} C_r^D})},

\end{aligned} \tag{1}$$

where  $R_{eq}$  and  $L_{eq}$  are the inductor-pot system electrical equivalent,  $f_{sw}$  is the switching frequency, and  $h$  is the harmonic number. The maximum output power ( $P_{o,max}^D$ ) occurs at resonant frequency. As a consequence, the first harmonic approximation can be assumed and the load resistance at this frequency must satisfy [3]

$$R_{eq} \leq \frac{2V_{mains}^2}{\pi^2 P_{o,max}^D}. \tag{2}$$

Besides, the resonant capacitor can be determined as

$$C_r^D = \frac{1}{L_{eq} (2\pi f_{sw})^2}. \tag{3}$$

The snubber capacitance  $C_s^D = C_{SA}$  is used to decrease turn-off switching losses. This capacitance must be charged/discharged during dead time between transistor activation with the output current. As a consequence, a small value of capacitance must be used to ensure the charge/discharge to achieve ZVS in a wide range of operating conditions [3].

### B. Class DE operation mode

The resonant inverter under class-DE operation mode must be designed to supply the required low-medium output power for the same inductor, i.e. same  $R_{eq}$ ,  $L_{eq}$ . Resonant and snubber capacitors are therefore modified, being  $C_r^{DE} = C_{rA} + C_{rB}$  and  $C_s^{DE} = C_{sA} + C_{sB}$ . The load resistance is determined by the maximum output power required in the class-D operation mode. As a consequence, the maximum output power when operating in class-DE operation mode is strongly dependent of the duty cycle  $D$ .

$$P_{o,\max}^{DE} = \frac{V_{mains}^2}{2\pi^2 R_{eq}} (1 - \cos(2\pi D)). \quad (4)$$

Besides, the snubber capacitance can now be calculated as follows

$$C_{snb}^{DE} = \frac{1 + \cos(2\pi D)}{(2\pi)^2 R_{eq} f_{sw}}. \quad (5)$$

The resonant frequency in the class DE operation mode,  $f_r^{DE}$ , determined by the inductor and the resonant capacitors, can now be calculated as

$$f_r^{DE} = \frac{f_{sw}}{2} \left( \sqrt{\left( \frac{\tan(\alpha)}{Q_{eq}} \right)^2 + 4} - \frac{\tan(\alpha)}{Q_{eq}} \right), \quad (6)$$

where  $Q_{eq} = 2\pi f_{sw} L_{eq} / R_{eq}$  is the inductor power quality factor at the switching frequency, and  $\alpha$  is the phase lag between current and voltage, calculated as

$$\tan(\alpha) = \frac{\pi(1 - 2D) + \sin(2\pi D) \cos(2\pi D)}{\sin^2(2\pi D)}. \quad (7)$$

Consequently, the resonant capacitor for the class-DE operation mode is given by

$$C_r^{DE} = \frac{1}{(2\pi f_r^{DE})^2 L_{eq}}. \quad (8)$$

As the Class DE operation mode is used to achieve the lower output power levels, both resonant and snubber capacitor use higher values than in the Class D operation mode. Therefore, the electromechanical relays SPST 1 and 2 are used to increase this capacitance for the Class DE operation mode.

### III. EFFICIENCY ANALYSIS

Power losses in the converter can be divided into two terms: conduction and switching losses. Both of them are caused by the non-idealities in the switching devices: non-zero switching times and non-zero on resistance. As a result, switching waveforms in the converter have a direct impact in the entire converter losses.

As small snubber capacitors are used in the Class D operation mode, the output current can be considered constant during the charge intervals. As a result, the voltage across the device during the switching becomes linear:

$$v_{CE}^D(t) = \frac{I_{C,off}}{2C_{snb}^D} t, \quad (0 \leq t \leq T_{snb}^D), \quad (9)$$

where  $I_{C,off}$  denotes the switch-off current in the switching devices. Moreover, the required time to charge/discharge the snubber capacitance can be calculated as

$$T_{snb}^D = V_s \frac{2C_{snb}^D}{I_{C,off}}. \quad (10)$$

In the case of the class-DE operation mode, the load current is modeled as a linear function that starts in  $I_{C,off}$  and ends at zero

$$i_o(t) = I_{C,off} \left( 1 - \frac{t}{T_{snb}^{DE}} \right), \quad (0 \leq t \leq T_{snb}^{DE}), \quad (11)$$

as a result, the switch voltage is

$$v_{CE}^{DE}(t) = \frac{1}{2C_{snb}^{DE}} \int i_o(t) dt = \frac{I_{C,off}}{2C_{snb}^{DE}} \left( t - \frac{t^2}{2T_{snb}^{DE}} \right), \quad (0 \leq t \leq T_{snb}^{DE}). \quad (12)$$

Where the class-E switching conditions, i.e. ZVS and ZVDS are achieved in the proposed voltage equation (12). The time required to charge/discharge the snubber capacitors  $T_{snb}^{DE}$  can be directly obtained from (12), yielding

$$T_{snb}^{DE} = V_S \frac{4C_{snb}^{DE}}{I_{C,off}}. \quad (13)$$

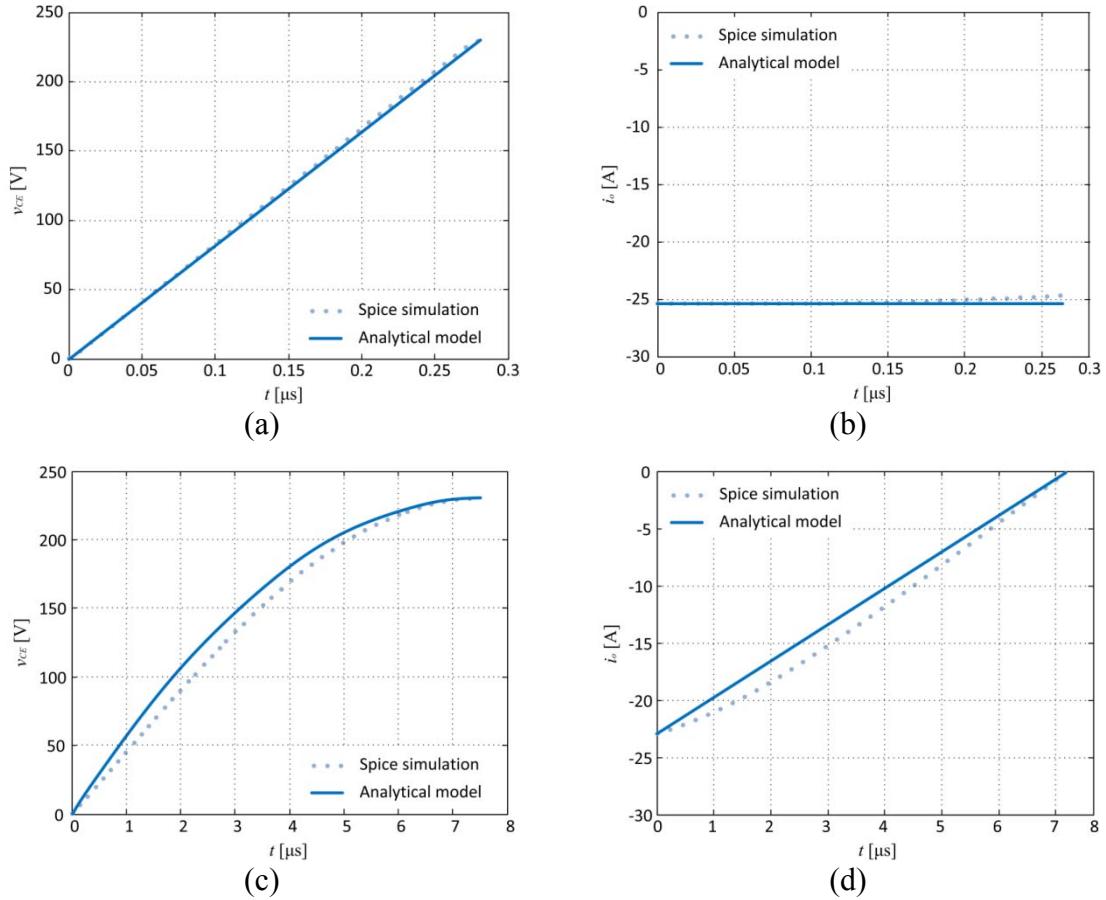

The proposed analytical model for the switching intervals have been validated with simulation results using SPICE simulation tool. The main simulation results are shown in Fig. 3, showing a good agreement with the proposed model.

Fig. 3. Simulation and proposed analytical results. Voltage (a) and current (b) results for class-D operation mode using 15-nF snubber capacitor at 32 kHz. Voltage (c) and current (d) for class-DE operation mode using 464-nF snubber capacitor at 20 kHz..

Main differences between the SPICE and the analytical model are due to the linear current assumption. These errors have a reduced impact in the output power and conduction losses computation and provide a useful method to predict the required dead-time to ensure the correct snubber charge/discharge with reduced computation effort.

#### ***A. Conduction losses***

Conduction losses can be calculated using the average and rms values of current through the devices. Since a bidirectional switch is used, there are two components in each switch to compute conduction losses, the IGBT ( $P_{ON,IGBT}$ ) and the antiparallel diode ( $P_{ON,DIODE}$ ). The total conduction losses,  $P_{ON}$ , therefore results

$$P_{ON} = 2(P_{ON,IGBT} + P_{ON,DIODE}), \quad (14)$$

Where each conduction term is

$$P_{ON} = r_{ON} I_{rms}^2 + v_{ON} I_{avg}, \quad (15)$$

were the on-resistance and collector-to-emitter saturation voltage are  $r_{ON}$  and  $v_{ON}$ , respectively. The block composed of the switching device, the antiparallel diode, and the snubber capacitance must provide the entire load current (Fig. 4). As a result, positive current values are supplied by the main transistor, whereas negative current values are supplied by the snubber capacitor and the antiparallel diode. Consequently, higher snubber capacitance implies lower antiparallel diode conduction and, as a result, lower diode conduction losses. Moreover, in the case of class-DE operation mode, the entire negative current is provided by the snubber capacitance, and antiparallel diode does not conduct.

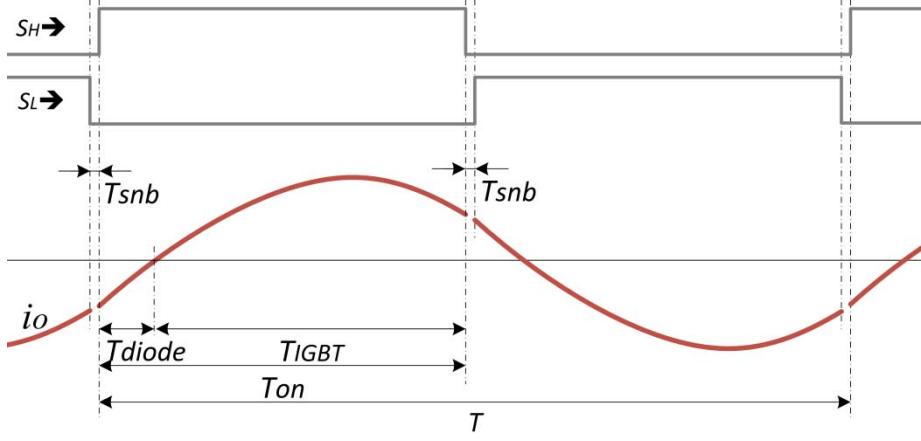

In order to compute the average and rms value of current, it is required to obtain the conduction time in each device. Total conduction time in each switching device is (Fig. 5)

$$T_{on} = T(1 - 2T_{snb}), \quad (16)$$

Fig. 4. Waveforms of the hybrid converter: output current and device activation. Class D operation mode (a) and class DE (b)

Fig. 5. Main current waveform and timing in the class-D operation mode.

In the case of class-D operation mode, the snubber current can be considered constant and as a result, switch-on and switch-off currents have the same opposite value, yielding that load current is [23]

$$i_o^D(t) = e^{-\xi t} \left( M_1^D \sin(\omega_n^D t) + M_2^D \cos(\omega_n^D t) \right), \quad (17)$$

where

$$\xi = R/2L_{eq}, \quad \omega_o^D = 1/\sqrt{L_{eq}C_r^D}, \quad \omega_n^D = \sqrt{(\omega_o^D)^2 - (\xi)^2}. \quad (18)$$

By applying boundary conditions, load current results

$$\begin{cases} i_o^D(t=0) = -I_{C,off} \Rightarrow M_2^D = -I_{C,off} \\ i_o^D(t=T_{on}) = I_{C,off} \Rightarrow M_1^D = I_{C,off} \left( \frac{e^{\xi T_{on}}}{\sin(\omega_n^D T_{on})} + \frac{1}{\tan(\omega_n^D T_{on})} \right), \end{cases} \quad (19)$$

As a result, the diode on time is

$$\begin{aligned} i_o^D(t = T_{diode}) = 0 \Rightarrow T_{diode} &= \frac{1}{\omega_n^D} a \tan\left(\frac{-M_2^D}{M_1^D}\right) \\ \Leftrightarrow T_{diode} &= \frac{1}{\omega_n^D} a \tan\left(\left(\frac{e^{\xi T_{on}}}{\sin(\omega_n^D T_{on})} + \frac{1}{\tan(\omega_n^D T_{on})}\right)^{-1}\right). \end{aligned} \quad (20)$$

The transistor on time is  $T_{IGBT} = T_{on} - T_{diode}$ . Consequently, average currents result

$$I_{avg,diode}^D = \frac{I_{C,off}}{T(\omega_o^D)^2} \left[ \omega_n^D \left( \frac{e^{-\xi T_{diode}}}{\sin(\omega_n^D T_{diode})} - \frac{1}{\tan(\omega_n^D T_{diode})} \right) + \xi \right], \quad (21)$$

$$I_{avg,IGBT}^D = \frac{I_{C,off}}{T(\omega_o^D)^2} \left[ \omega_n^D \left( \frac{e^{\xi T_{IGBT}}}{\sin(\omega_n^D T_{IGBT})} - \frac{1}{\tan(\omega_n^D T_{IGBT})} \right) - \xi \right]. \quad (22)$$

and the rms currents are

$$I_{rms,diode}^D = \sqrt{\frac{I_{C,off}^2}{4\xi T(\omega_o^D)^2 \sin(\omega_n^D T_{diode})} \left[ \frac{(\omega_o^D)^2 - (\omega_o^D)^2 e^{-2\xi T_{diode}}}{\sin(\omega_n^D T_{diode})} + \xi \left( \frac{\xi}{\tan(2\omega_n^D T_{diode})} - \omega_n^D \right) \right]}, \quad (23)$$

$$I_{rms,IGBT}^D = \sqrt{\frac{I_{C,off}^2}{4\xi T(\omega_o^D)^2 \sin(\omega_n^D T_{IGBT})} \left[ \frac{(\omega_o^D)^2 - (\omega_o^D)^2 e^{2\xi T_{IGBT}}}{\sin(\omega_n^D T_{IGBT})} + \xi \left( \frac{\xi}{\tan(2\omega_n^D T_{IGBT})} - \omega_n^D \right) \right]}. \quad (24)$$

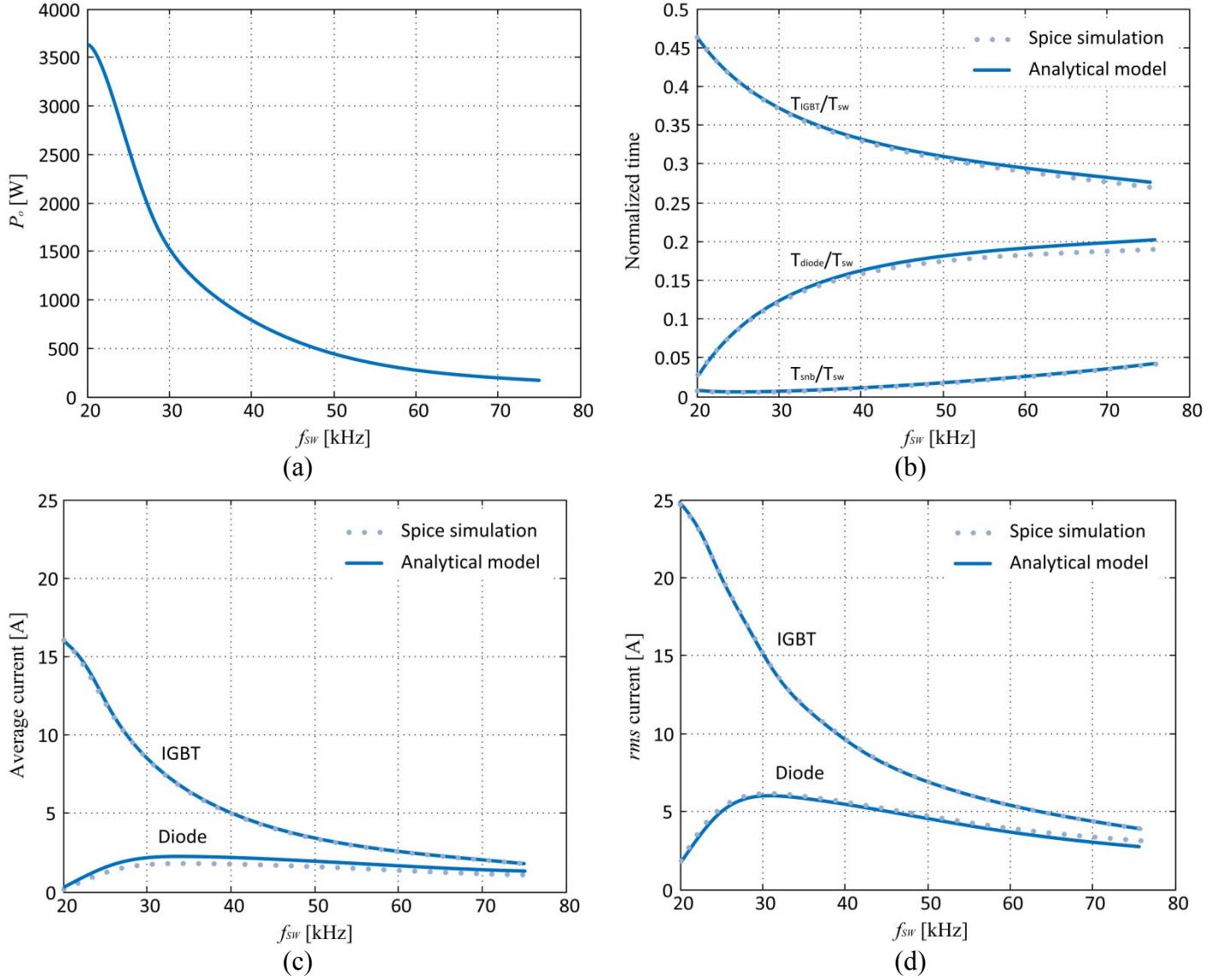

The proposed analytical model has been verified and compared using Spice simulator.

The results are shown in Fig. 6 for the complete output power range in the class-D operation mode, obtaining a good agreement between analytical and simulation results.

Fig. 6. Simulation versus Spice results: (a) output power; (b) normalized IGBT, diode and snubber times; (c) average currents in the IGBT and diode; (d) rms current in the IGBT and diode. Results for  $R_{eq}=2.89 \Omega$ ,  $L_{eq}=29.6 \mu\text{H}$ , resonant and snubber capacitor  $2.04 \mu\text{F}$  and  $15 \text{nF}$ , respectively.

In the case of the class-DE operation mode, the diode does not conduct and, therefore,

$T_{diode} = 0$ ,  $T_{IGBT} = T_{on}$ . By applying the same procedure, the average and rms values of current results

$$I_{avg,IGBT}^{DE} = \frac{I_{C,off}}{T(\omega_o^{DE})^2} \left[ \omega_n^{DE} \left( \frac{e^{\xi T_{on}}}{\sin(\omega_n^{DE} T_{on})} - \frac{1}{\tan(\omega_n^{DE} T_{on})} \right) - \xi \right], \quad (25)$$

$$I_{rms, IGBT}^{DE} = \sqrt{\frac{I_{C,off}^2}{4\xi T (\omega_o^{DE})^2 \sin(\omega_n^{DE} T_{on})} \left[ \frac{(\omega_o^{DE})^2 - (\omega_o^{DE})^2 e^{2\xi T_{on}}}{\sin(\omega_n^{DE} T_{on})} + \xi \left( \frac{\xi}{\tan(2\omega_n^{DE} T_{on})} - \omega_n^{DE} \right) \right]}, \quad (26)$$

where  $\omega_o^{DE} = 1/\sqrt{L_{eq} C_r^{DE}}$ ,  $\omega_n^{DE} = \sqrt{(\omega_o^{DE})^2 - (\xi)^2}$ .

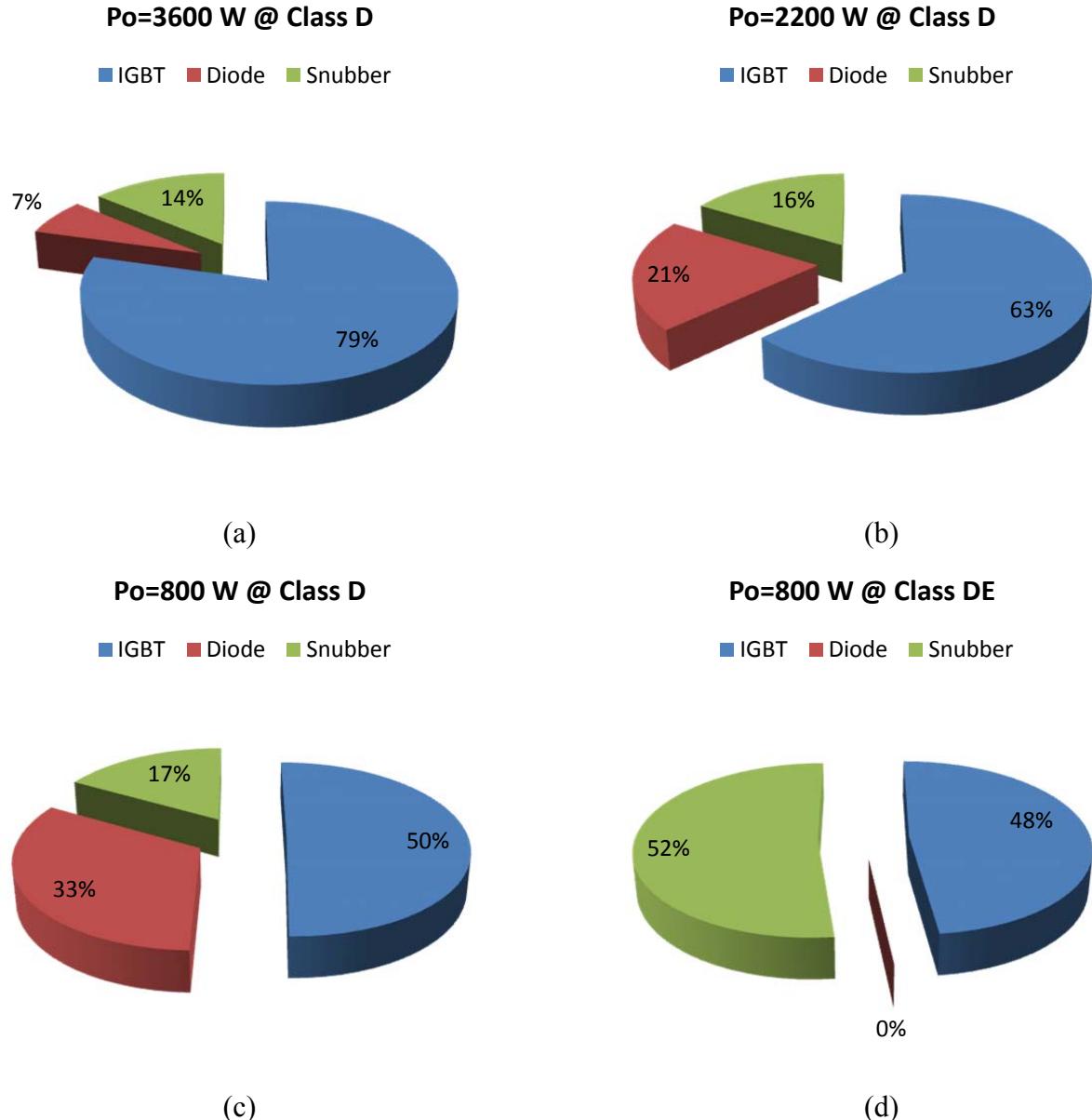

Consequently, the current distribution in the class-DE operation mode is partly derived to the snubber capacitor, reducing conduction losses (Fig. 7).

Fig. 7. Rms current distribution for class-D operation mode: (a) maximum output power, 3.6 kW, (b) nominal power (2.2 kW); minimum power (800 W) (c). Current distribution for class-DE at 800 W (d).

### B. Switching losses

As the devices voltage waveforms in the switching transitions have been obtained (9), (12), switching losses can be directly calculated by means of using a piecewise switch-off current model [24], where the switch-off current is defined for IGBT devices by means of the tail factor  $\beta$ , and *fall* and *tail* intervals,  $t_f$ ,  $t_t$ , respectively

$$i_{C,off}(t) = \begin{cases} I_{C,off} \left( 1 - \frac{\beta}{t_f} t \right), & (0 \leq t < t_f) \\ I_{C,off} (1 - \beta) \left( 1 - \frac{t - t_f}{t_t} \right), & (t_f \leq t \leq t_f + t_t) \end{cases} \quad (27)$$

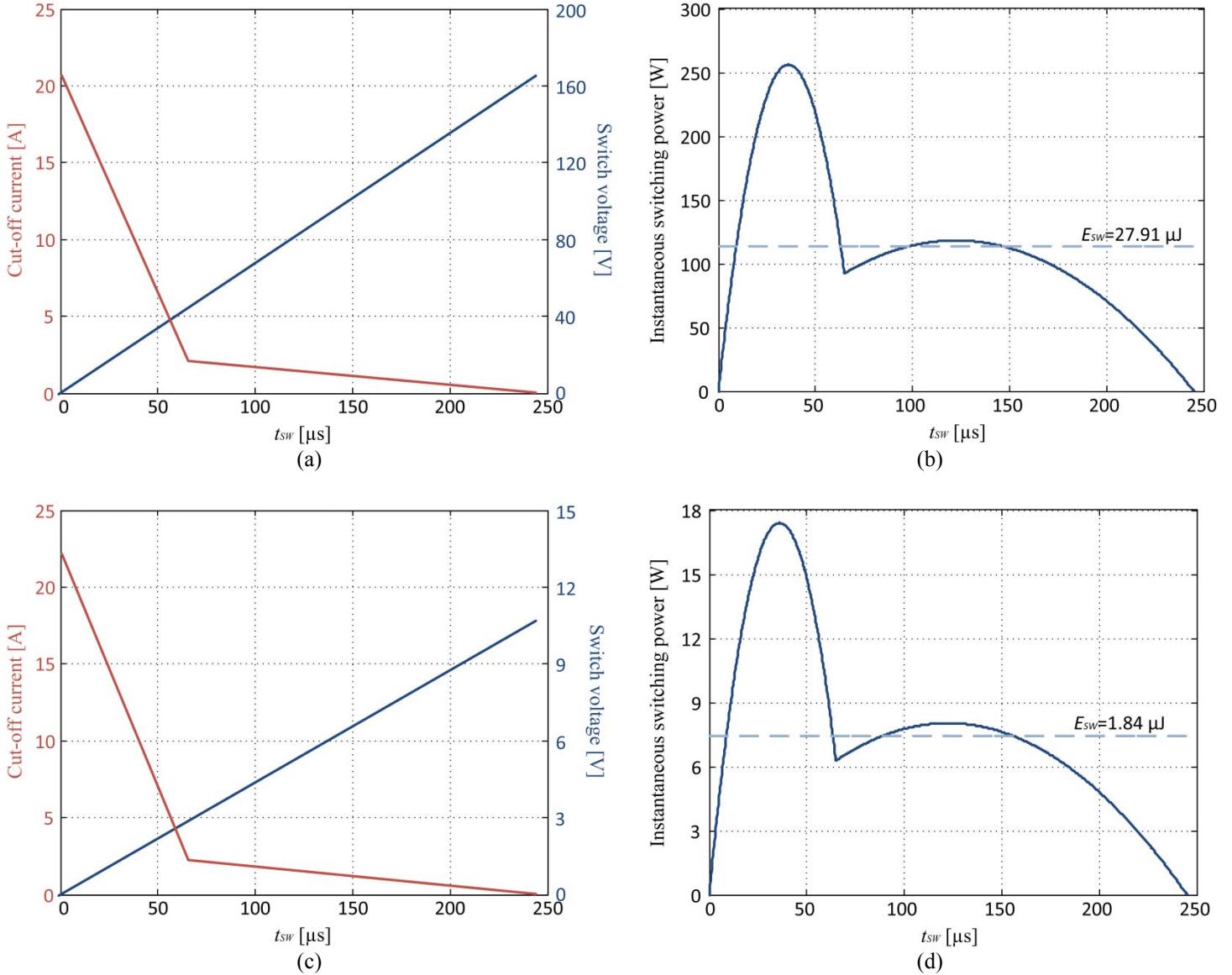

Thus, the instantaneous switching losses can be obtained. Fig. 8 shows results for both operation modes delivering 800-W output power

$$p_{SW}^D(t) = \begin{cases} \frac{I_{C,off}^2}{2C_{snb}^D} \left( 1 - \frac{\beta}{t_f} t \right), & (0 \leq t \leq t_f) \\ \frac{I_{C,off}^2 (1 - \beta)}{2C_{snb}^D} \left( 1 - \frac{t - t_f}{t_t} \right), & (t_f < t \leq t_f + t_t) \end{cases}, \quad (28)$$

$$p_{SW}^{DE}(t) = \begin{cases} \frac{I_{C,off}^2}{2C_{snb}^{DE}} \left( 1 - \frac{\beta}{t_f} t \right) \left( t - \frac{t^2}{2T_{snb}^{DE}} \right), & (0 \leq t \leq t_f) \\ \frac{I_{C,off}^2 (1 - \beta)}{2C_{snb}^{DE}} \left( 1 - \frac{t - t_f}{t_t} \right) \left( t - \frac{t^2}{2T_{snb}^{DE}} \right), & (t_f < t \leq t_f + t_t) \end{cases}. \quad (29)$$

Therefore, the switching losses energy in each operation mode results

$$E_{SW}^D = \frac{I_{C,off}^2}{2C_{snb}^D} \left[ t_f \left( 1 - \frac{\beta}{2} \right) + \frac{t_t}{2} (1 - \beta) \right] \quad (30)$$

$$E_{SW}^{DE} = \frac{I_{C,off}^2}{48C_{snb}^{DE} T_{snb}^{DE}} \left[ \begin{aligned} & 4t_f^2 \left( T_{snb}^{DE} (3 - 2\beta) - t_f \left( 1 - \frac{3}{4} \beta \right) \right) + \\ & t_t (1 - \beta) \left( 6t_f^2 + t_t^2 + 4t_f t_t - 4T_{snb}^{DE} (3t_f + t_t) \right) \end{aligned} \right] \quad (31)$$

Fig. 8. Switching losses simulation for Class D (a, b) using 15 nF snubber capacitor and a cut-off current of 20.63 A at 800 W output power, yielding 328-ns snubber time. Results for Class DE (c, d) using 265 nF capacitor, a cut-off current of 22.7 A at 500 w output power, yielding 10.72-μs snubber time. Simulation results for  $\beta=0.9$ ,  $t_f=65$  ns,  $t_i=180$  ns.

Finally, switching losses result

$$P_{SW} = 2f_{SW}E_{SW}. \quad (32)$$

## IV. MODULATION STRATEGIES AND DIGITAL IMPLEMENTATION

### A. Modulation strategies

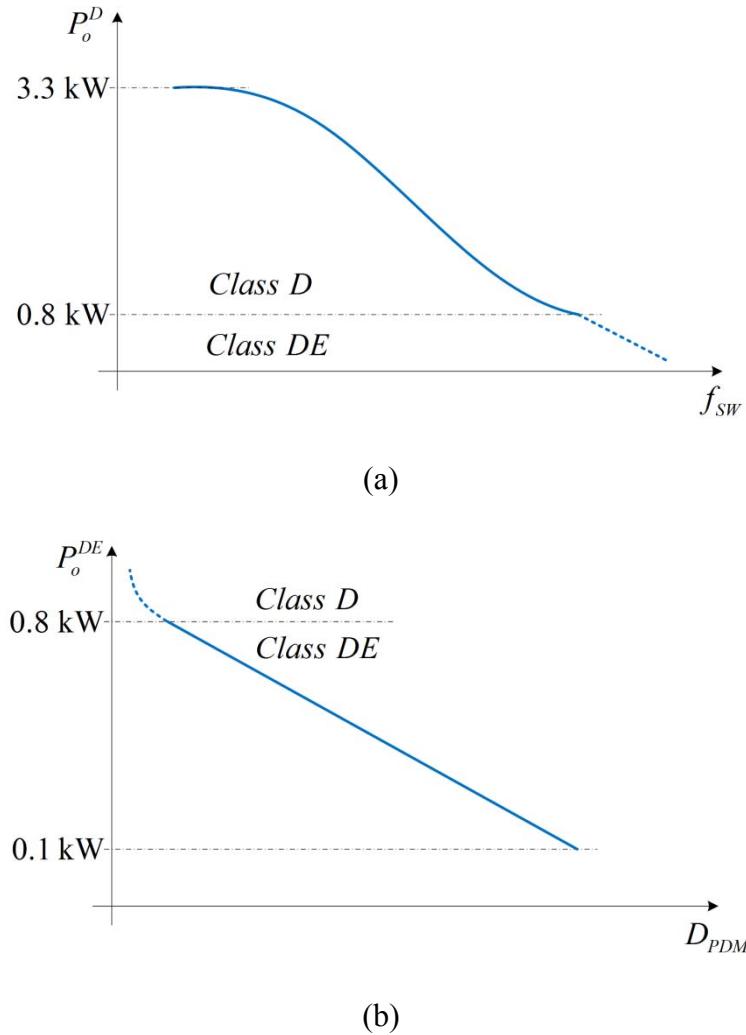

According to the selected operation mode, the hybrid converter uses two modulation strategies. On the one hand, the class-D operation mode supplies the high output power range and, therefore, the square wave modulation (SW) is used [10]. Consequently, the maximum output power is achieved at the resonant frequency, and lower power levels can be obtained by increasing the switching frequency. As a result, the ZVS switching-on condition is achieved in the entire power range for this operation mode. The output power variation as a function of the switching frequency is described in (1).

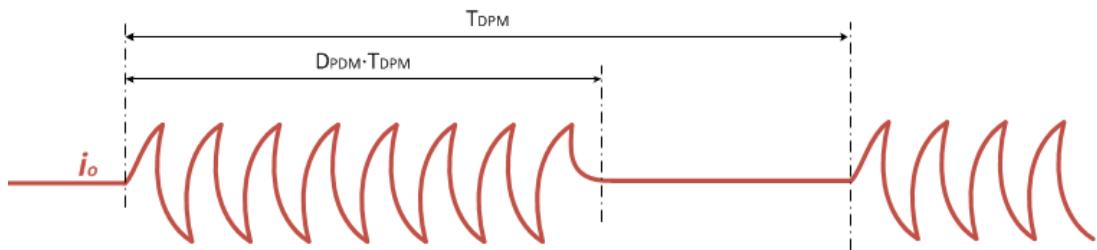

On the other hand, when lower output powers are required, the system changes resonant and snubber capacitors to operate in the class-DE operation mode. For a given load, that is, for a given inductor-pot system, the class-DE optimal switching conditions are only achieved for a single operation point, i.e. a switching frequency, a duty cycle, and a phase lag. Thus, lower power levels are achieved using a pulse density modulation [7], [17], PDM, in the output power. By denoting  $T_{DPM}$  as the total pulse density period, the on-time duty cycle for the PDM is defined as  $D_{PDM}$  (Fig. 9). Consequently, the output power varies linearly with the PDM duty cycle

$$P_o^{DE} = D_{PDM} P_{o,\max}^{DE}, \quad 0 \leq D_{PDM} \leq 1, \quad (33)$$

Fig. 9. Pulse density modulation (PDM): output current and control parameters.

The total PDM time,  $T_{PDM}$ , is chosen according to flicker requirements to ensure that EMC requirements are fulfilled [10]. Fig. 10 shows both the modulation scheme and the output power variation for both of them. The maximum output power, 3.3 kW, is achieved close to resonance in the class-D operation mode and the output power threshold to switch to the class-DE operation mode is 800 W. The switching frequency for the class-DE operation mode is reduced to 20 kHz, reducing therefore the switching losses.

Fig. 10. Output power variation for class-D (a) and class-DE (b) operation modes. Power curve as a function of switching frequency in the class-D operation mode (a). Power curve as a function of the PDM duty cycle for the class-DE operation mode (b).

### B. Digital control implementation

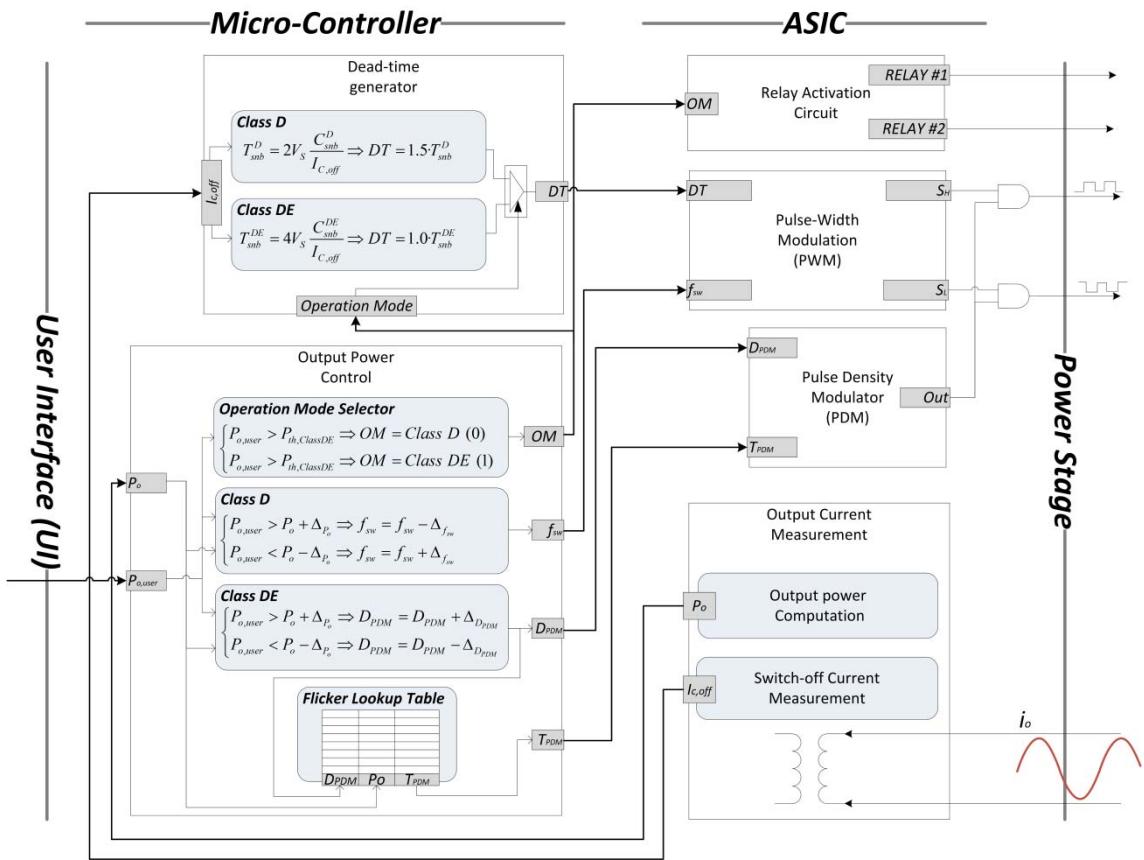

The proposed system is digitally controlled by a microcontroller and an application-specific integrated circuit (ASIC) [25]. The control algorithm as well as the modulation parameters are computed in the microcontroller, while some high computation tasks, such as the digital modulator, the current measurement circuits, and output power computations are included in the ASIC. Main logic level schematic diagram is shown in Fig. 11.

Fig. 11. Logic implementation in the proposed hybrid converter.

The output power set-point is defined by the user through a user interface (UI), which is controlled by the microcontroller. The operation mode depends on the power level, i.e. power levels higher than 800 W are supplied using the class-D operation mode, whereas

the class-DE operation mode is used for lower power levels. For the class-D operation mode, the control algorithm increases or reduces a fixed switching frequency quantity,  $\Delta_{f_{sw}}$ , if the measured output power differs from the set-point output power. On the other hand, for the Class DE operation mode,  $D_{PDM}$  is increased or reduced based on the output power set-point and the measured output power. However, in order to fulfill the EMC requirements, the flicker time,  $T_{PDM}$ , must be in consideration. A lookup table is integrated in the memory of the microcontroller to compute the required flicker time to accomplish the standards proposed by the International Electrotechnical Commission (IEC), considered by the IEEE workgroup p1453 [26]. In addition, the required dead-time to ensure the correct snubber calculation is also performed by the microcontroller, using equations (10), (13), for the Class D and Class DE operation mode, respectively.

On the one hand, the ASIC generates the gating signals, as well as measures output current to perform the required calculations. Depending on the operation mode, the ASIC activates or deactivates the snubber and resonant capacitor relays to change the operation mode. A pulse width modulator (PWM) is also implemented, and the transistor activation signals are generated as a function of the switching frequency and the duty cycle. Besides, a Pulse Density Modulator (PDM) is also included to control the output power in the Class DE operation mode. Finally, the load current is also measured to obtain the output power measurement and the switch-off current, used to compute the correct dead-time in the microcontroller.

## V. EXPERIMENTAL RESULTS

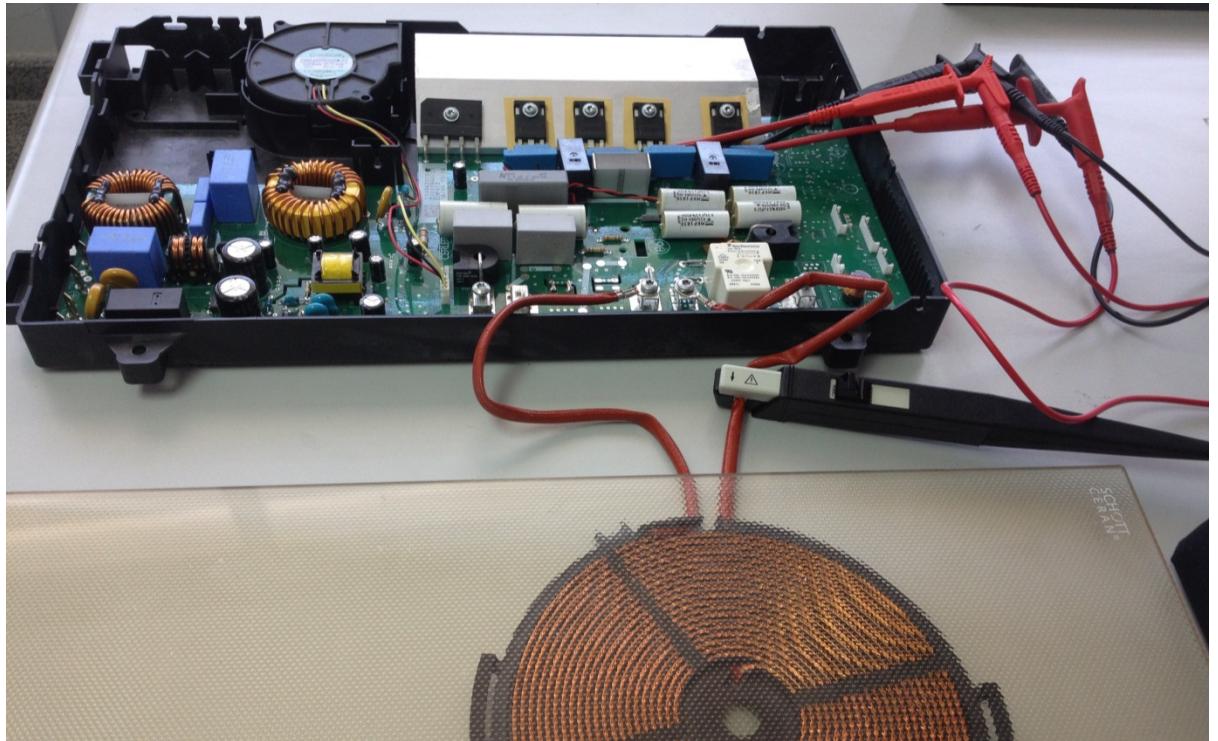

A prototype based on a commercial electronic board has been built to verify the proposed converter. Power levels from 0.8 kW up to 3 kW are supplied using the class-D operation mode, whereas class-DE operation mode is used for power levels lower than 800 W.

The inductor must be designed to ensure the maximum power level up to 3 kW for 230-V power supply voltage. Using (2), the inductor resistance must be lower than  $3.26 \Omega$ . The lower switching frequency was set to 20 kHz to avoid acoustic noise. The equivalent inductor-pot system resistance and inductance are  $2.89 \Omega$  and  $29.6 \mu\text{H}$ , respectively. The measurements have been performed by means of a precision LCR meter from Agilent (E4980A). Consequently, the maximum available output power is

$$P_o \leq \frac{2V_{mains}^2}{\pi^2 R_{eq}} = \frac{2 \cdot 230^2}{\pi^2 \cdot 2.86} = 3.7 \text{ kW} \quad (34)$$

Using (3), the resonant capacitor for the Class D operation mode results 2139 nF. On the other hand, the snubber capacitance was set to 15 nF in order to reduce switching losses and to allow a wider output power range.

For the Class DE operation mode, the duty cycle results 24.09% at 20 kHz switching frequency. Consequently, the snubber capacitor (5) is 463.29 nF. The resonant frequency (6) is 10.79 kHz to achieve the desired output power level, and the phase lag between current and voltage is  $\alpha=59.39^\circ$ . Finally, the resonant capacitor (8) results 7350 nF. A small value DC-Link capacitor,  $C_b$ , is used to ensure an input power factor close to one. Table I summarizes the selected values according to the proposed design method and using standard values.

TABLE I

PROTOTYPE PARAMETERS

| COMPONENTS |                                    | Class D          | Class DE     |

|------------|------------------------------------|------------------|--------------|

| $f_{SW}$   | Switching frequency                | 20 kHz to 40 kHz | 20 kHz       |

| $D$        | Duty cycle                         | 50 %             | 24%          |

| $C_r$      | Resonant capacitor                 | 2.14 $\mu$ F     | 7.35 $\mu$ F |

| $C_{snb}$  | Snubber Capacitor                  | 15 nF            | 464 nF       |

| $C_b$      | DC-Link capacitor                  | 2x3.3 $\mu$ F    |              |

| $R_{eq}$   | Inductor-pot equivalent resistance | 2.89 $\Omega$    |              |

| $L_{eq}$   | Inductor-pot equivalent inductance | 29.6 $\mu$ H     |              |

The proposed prototype implementation board is shown in Fig. 12

Fig. 12. Experimental setup for the proposed hybrid converter.

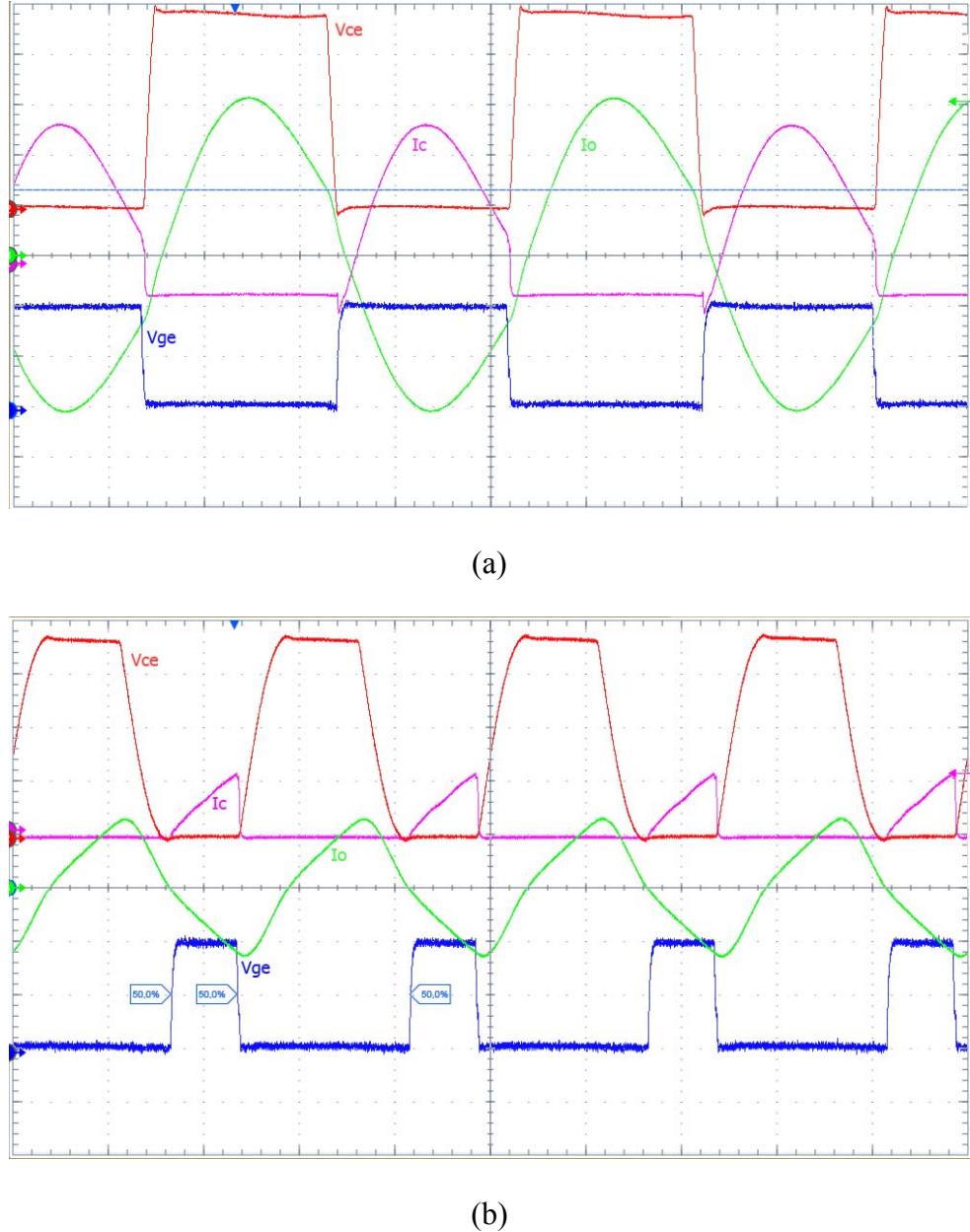

Fig. 13 shows the main waveforms for the class-D operation mode (a) and the class-DE operation mode (b). The converter shows a correct performance and the stray elements added by the electromechanical switches do not affect the converter operation. Therefore, the experimental results are in good agreement with the theoretical ones.

Fig. 13. Power converter main waveforms: collector-emitter voltage ( $V_{ce}$ ), 100 V/div; collector current ( $I_c$ ), 10 A/div; output current ( $I_o$ ), 10 A/div; gate to-emitter voltage ( $V_{ge}$ ), 10 V/div. Time: 1.25  $\mu$ s/div. Class-D (a) and Class-DE (b) operation modes.

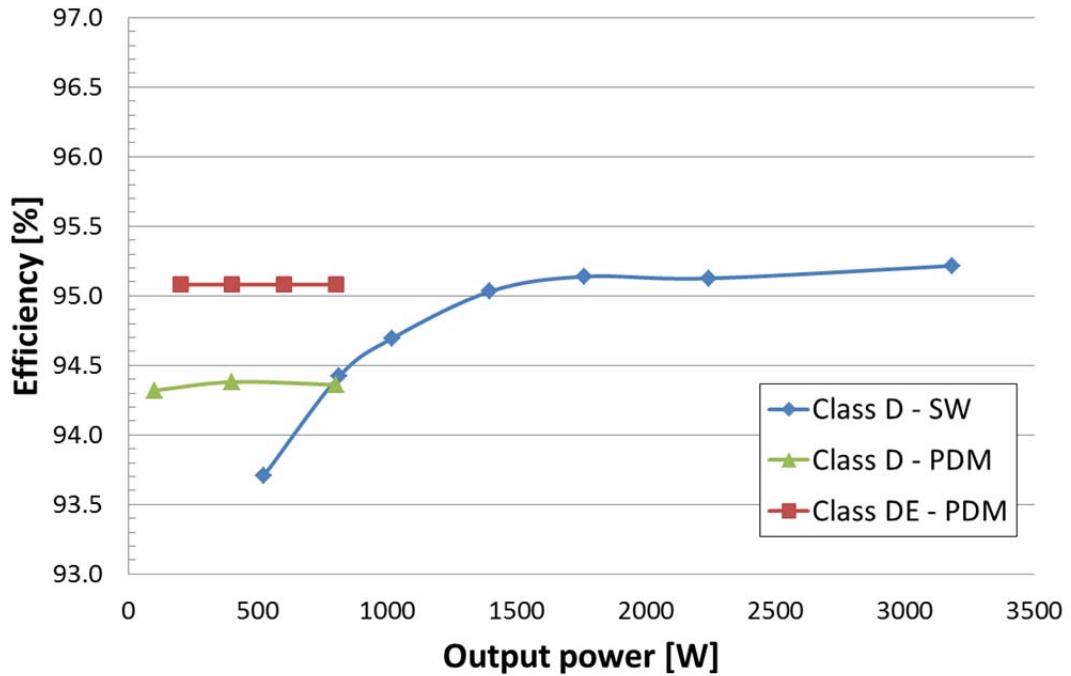

Efficiency in both operation modes have been measured using the power analyzer YOKOGAWA PZ-400 as the ratio between the input power and the power delivered to the load (Fig. 14). These results show that the class-D operation mode efficiency decreases as the switching frequency is increased when the square-wave control (SW) is applied i.e. lower output power range. The class-D operation mode operating with pulse density modulation (PDM) [7], [18] is usually applied when switching frequency increases to reduce switching losses (frequency limit, FL [10]), yielding a power losses reduction in the lower output range. However, the class-DE operation mode proposed in this paper obtains a significantly higher efficiency due to the switching and conduction losses reduction. The combination of both operation modes ensures high efficiency in the complete output power operation range.

Fig. 14. Measured efficiency comparison for the proposed converter operating in class-D SW and class-DE PDM operation, and the current class D PDM operation.

## VI. CONCLUSIONS

In this paper, a novel reconfigurable series resonant inverter topology is proposed in order to improve the efficiency in the whole operating range. It is based on a dual-mode resonant converter where the class-D and class-DE operation modes are combined to optimize the efficiency. The analytical results have been verified by means of an experimental prototype. As a result, the presented dual-mode topology is proposed as a cost-effective implementation to improve the overall converter efficiency.

## VII. REFERENCES

- [1] O. Lucía, J. M. Burdío, L. A. Barragán, J. Acero, and I. Millán, "Series-resonant multiinverter for multiple induction heaters," *IEEE Transactions on Power Electronics*, vol. 24, no. 11, pp. 2860-2868, November 2010.

- [2] H. W. Koertzen, J. A. Ferreira, and J. D. van Wyk, "A comparative study of single switch induction heating converters using novel component effectivity concepts," in *IEEE Power Electronics Specialists Conference*, 1992, pp. 298-305.

- [3] O. Lucía, J. M. Burdío, I. Millán, J. Acero, and L. A. Barragán, "Efficiency oriented design of ZVS half-bridge series resonant inverter with variable frequency duty cycle control," *IEEE Transactions on Power Electronics*, vol. 25, no. 7, pp. 1671-1674, July 2010.

- [4] R. L. Steigerwald, "A comparison of half-bridge resonant converter topologies," *IEEE Transactions on Power Electronics*, vol. 3, no. 2, pp. 174-182, April 1988.

- [5] N. A. Ahmed, "High-frequency soft-switching ac conversion circuit with dual-mode PWM/PDM control strategy for high-power IH applications," *IEEE Transactions on Industrial Electronics*, vol. 58, no. 4, pp. 1440-1448, April 2011.

- [6] H. Fujita, N. Uchida, and K. Ozaki, "A new zone-control induction heating system using multiple inverter units applicable under mutual magnetic coupling conditions," *IEEE Transactions on Power Electronics*, vol. 26, no. 7, pp. 2009-2017, July 2010.

- [7] V. Esteve, et al., "Improving the efficiency of IGBT series-resonant inverters using pulse density modulation," *IEEE Transactions on Industrial Electronics*, vol. 58, no. 3, pp. 979-987, March 2011.

- [8] Y. Kawaguchi, E. Hiraki, T. Tanaka, and M. Nakaoka, "Full bridge phase-shifted soft switching high-frequency inverter with boost PFC function for induction heating system," in *European Conference on Power Electronics and Applications*, 2007, pp. 1-8.

- [9] Y. Kawaguchi, E. Hiraki, T. Tanaka, M. Nakaoka, A. Fujita, and H. Omori, "Feasible evaluation of a full-bridge inverter for induction heating cooking appliances with discontinuous current mode PFC control," in *IEEE Power Electronics Specialists Conference*, 2008.

- [10] O. Lucía, J. M. Burdío, I. Millán, J. Acero, and D. Puyal, "Load-adaptive control algorithm of half-bridge series resonant inverter for domestic induction heating," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 8, pp. 3106-3116, August 2009.

- [11] F. Wang, S. Wei, D. Boroyevich, S. Ragon, V. Stefanovic, and M. Arpilliere, "Voltage source inverter," *IEEE Industry Applications Magazine*, vol. 15, no. 2, pp. 24-33, March/April 2009.

- [12] B. Saha, K. Soon Kurl, N. A. Ahmed, H. Omori, and M. Nakaoka, "Commercial frequency AC to high frequency AC converter with boost-active clamp bridge single stage ZVS-PWM inverter," *IEEE Transactions on Power Electronics*, vol. 23, no. 1, pp. 412-419, January 2008.

- [13] H. Pham, H. Fujita, K. Ozaki, and N. Uchida, "Phase angle control of high-frequency resonant currents in a multiple inverter system for zone-control induction heating," *to be published in IEEE Transactions on Power Electronics*, vol. x, no. x, pp. 1-10, 2011.

- [14] Czarkowski and M. K. Kazimierczuk, "ZVS class D series resonant inverter discrete-time state-space simulation and experimental results," *IEEE Transactions on Circuits and Systems*, vol. 45, no. pp. 1141-1147, November 1998.

- [15] H. Sarnago, A. Mediano, and O. Lucía, "High efficiency ac-ac power electronic converter applied to domestic induction heating," *IEEE Transactions on Power Electronics*, vol. 27, no. 8, pp. 3676-3684, August 2012.

- [16] J. Yungtaek and M. M. Jovanovic, "Light-load efficiency optimization method," *IEEE Transactions on Power Electronics*, vol. 25, no. 1, pp. 67-74, January 2010.

- [17] A. Sandali, A. Cheriti, and P. Sicard, "Comparison of the various PDM control modes," in *IEEE International Conference on Industrial Technology*, 2004, pp. 574-579 Vol. 2.

- [18] H. Fujita and H. Akagi, "Pulse-density-modulated power control of a 4 kW, 450 kHz voltage-source inverter for induction melting applications," *IEEE Transactions on Industry Applications*, vol. 32, no. 2, pp. 279-286, March/April 1996.

- [19] H. Sarnago, O. Lucía, A. Mediano, and J. M. Burdío, "Dual-mode-operation half-bridge resonant converter for improved-efficiency induction heating system," in *IEEE Applied Power Electronics Conference and Exposition*, 2012, pp. 2184-2188.

- [20] I. D. de Vries, J. H. van Nierop, and J. R. Greene, "Solid state class DE RF power source," in *IEEE International Symposium on Industrial Electronics*, 1998, pp. 524-529.

- [21] H. Sekiya, N. Sagawa, and M. K. Kazimierczuk, "Analysis of class DE amplifier with nonlinear shunt capacitances at any grading coefficient for high Q and 25% duty ratio," *IEEE Transactions on Power Electronics*, vol. 25, no. 4, pp. 924-932, April 2010.

- [22] O. Lucía, C. Carretero, D. Palacios, D. Valeau, and J. M. Burdío, "Configurable snubber network for efficiency optimization of resonant converters applied to multi-load induction heating," *Electronics Letters*, vol. 47, no. 17, pp. 989-991, August 2011.

- [23] L. R. Nerone, "Analytical solutions of the Class D inverter," in *IEEE International Symposium on Circuits and Systems*, 2008, pp. 1268-1271.

- [24] R. W. Erickson and D. Macsimovic, *Fundamentals of Power Electronics*. Boulder, Colorado: Springer Science+Business Media, 2001.

- [25] O. Lucía, L. A. Barragán, J. M. Burdío, O. Jiménez, D. Navarro, and I. Urriza, "A versatile power electronics test-bench architecture applied to domestic induction heating," *IEEE Transactions on Industrial Electronics*, vol. 58, no. 3, pp. 998-1007, March 2011.

[26] "Limitation of voltage fluctuations and flicker in low-voltage supply systems for equipment with rated current 16 A," IEC ed: IEC Standard 1000-3-3, 1994.