## Trabajo Fin de Máster

Diseño, Implementación y Control digital con FPGA

de un convertidor elevador “Boost”

Máster en Ingeniería Electrónica

Autor:

Ignacio Machín Mindán

Directores:

José Ignacio Artigas Maestre

Luis Ángel Barragán Pérez

# DISEÑO, IMPLEMENTACIÓN Y CONTROL DIGITAL CON FPGA DE UN CONVERTIDOR ELEVADOR “BOOST”

## RESUMEN

El presente Trabajo Fin de Master consiste en el diseño, modelado, fabricación y validación de un prototipo de un convertidor DC/DC elevador tipo “Boost”. El objetivo de este Trabajo es que este prototipo pueda ser utilizado como material didáctico para prácticas de Grado o de Máster y sobre el cual los alumnos puedan probar multitud de controles digitales, desarrollados por ellos mismos.

El primer paso ha sido el diseñar, modelar y fabricar el convertidor de baja potencia, optimizando su diseño de tal forma que la PCB sea de un tamaño reducido. Como se comentaba anteriormente, el objetivo de este Trabajo es que la plataforma Hardware desarrollada pueda ser utilizada como material didáctico, por lo que existen una serie de anillas de test estratégicamente colocadas para permitir tener acceso a las señales y medidas más importantes.

Posteriormente, siguiendo diversos métodos de cálculo, se han diseñado 5 reguladores con la misma topología de 2 ceros y 2 polos. De entre estos 5 reguladores se ha seleccionado el regulador que mejor comportamiento tiene frente a una serie de funciones de mérito. Estas funciones de mérito son  $GM$ ,  $PO$ ,  $|S|_{inf}$ ,  $|Z_{cl}|_{inf}$ ,  $f_B$ ,  $|G_c * S|_{inf}$  y  $K_i$ .

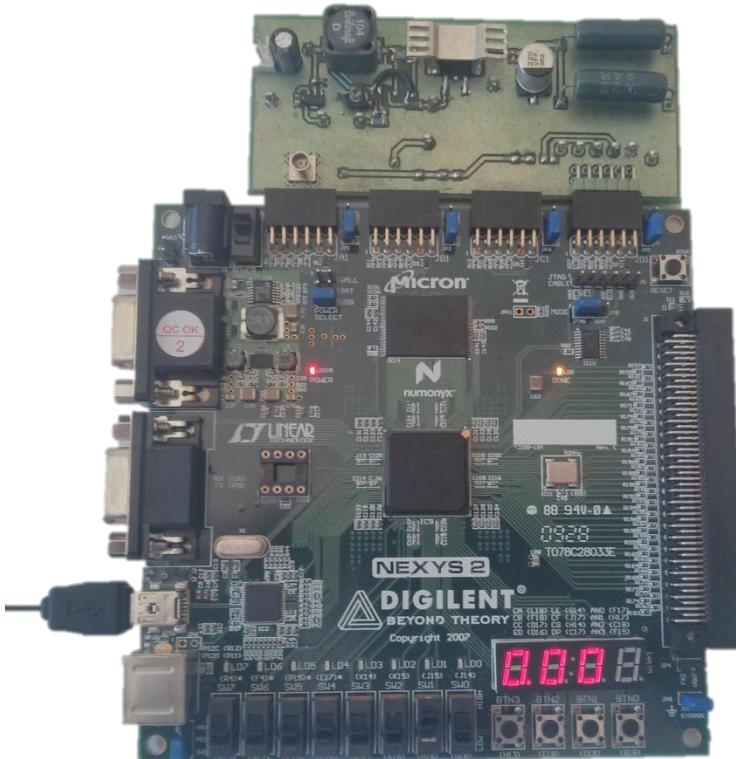

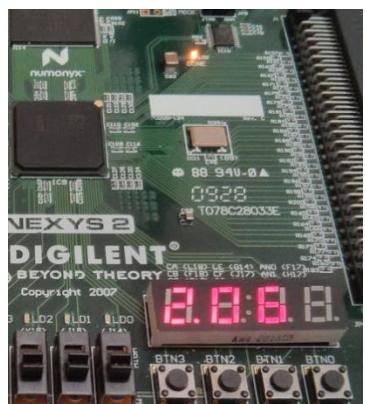

A continuación, utilizando la placa de desarrollo Nexys2 de Diligent, se ha implementado el control digital en la FPGA. Para ello se ha diseñado un código en VHDL en la herramienta Xilinx ISE, el cual se ha verificado con la herramienta software ModelSIM. El diseño digital consta de la implementación del controlador seleccionado anteriormente, la implementación del protocolo de comunicaciones con el conversor analógico digital, la generación de la señal PWM de disparo del transistor de potencia y la gestión de las entradas/salidas de la placa de desarrollo Nexys2.

Por último, para validar el correcto diseño del convertidor y del regulador implementado en la FPGA, se han tomado medidas experimentales, a partir de las cuales, se ha observado que los resultados obtenidos en simulación (Matlab y ModelSIM) son similares a los obtenidos experimentalmente.

**INDICE:**

|          |                                                                                    |           |

|----------|------------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introducción.....</b>                                                           | <b>1</b>  |

| 1.1      | Antecedentes.....                                                                  | 1         |

| 1.2      | Objetivos y alcance .....                                                          | 2         |

| 1.3      | Descripción del sistema y especificaciones de diseño .....                         | 3         |

| 1.4      | Organización de la Memoria Técnica .....                                           | 6         |

| <b>2</b> | <b>Diseño y modelado del convertidor Boost .....</b>                               | <b>7</b>  |

| 2.1      | Análisis teórico del modelo de pequeña señal en modo de conducción continua.....   | 7         |

| 2.2      | Selección de los componentes del convertidor .....                                 | 9         |

| <b>3</b> | <b>Diseño de la Plataforma Hardware desarrollada .....</b>                         | <b>16</b> |

| 3.1      | Selección del resto de componentes .....                                           | 18        |

| <b>4</b> | <b>Diseño del control digital .....</b>                                            | <b>22</b> |

| 4.1      | Cálculo del Regulador .....                                                        | 24        |

| 4.2      | Selección del Regulador .....                                                      | 27        |

| 4.3      | Verificación mediante simulación.....                                              | 30        |

| <b>5</b> | <b>Implementación del control digital.....</b>                                     | <b>36</b> |

| 5.1      | Implementación del regulador en números reales y validación en simulación.....     | 38        |

| 5.2      | Implementación del regulador en coma fija y validación en simulación .....         | 40        |

| <b>6</b> | <b>Resultados experimentales .....</b>                                             | <b>46</b> |

| 6.1      | Configuración de la FPGA.....                                                      | 46        |

| 6.2      | Medidas experimentales.....                                                        | 48        |

| <b>7</b> | <b>Conclusiones y líneas de trabajo futuras.....</b>                               | <b>55</b> |

| <b>8</b> | <b>Referencias bibliográficas .....</b>                                            | <b>57</b> |

| <b>9</b> | <b>ANEXOS.....</b>                                                                 | <b>59</b> |

|          | ANEXO A.- Análisis del modelo de pequeña señal en modo de conducción continua..... | 60        |

|          | ANEXO B.- Planos de la plataforma Hardware .....                                   | 66        |

|          | ANEXO C.- Listado de Componentes: .....                                            | 69        |

|          | ANEXO D.- Cálculo de los reguladores:.....                                         | 71        |

|          | ANEXO E.- Funciones de mérito: .....                                               | 75        |

|          | ANEXO F.- Cálculo de las funciones de mérito: .....                                | 79        |

|                                                |     |

|------------------------------------------------|-----|

| ANEXO G.- Código en VHDL.....                  | 87  |

| ANEXO H.- Código en VHDL no sintetizable ..... | 101 |

### Índice de figuras:

|                                                                                                                                                                   |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

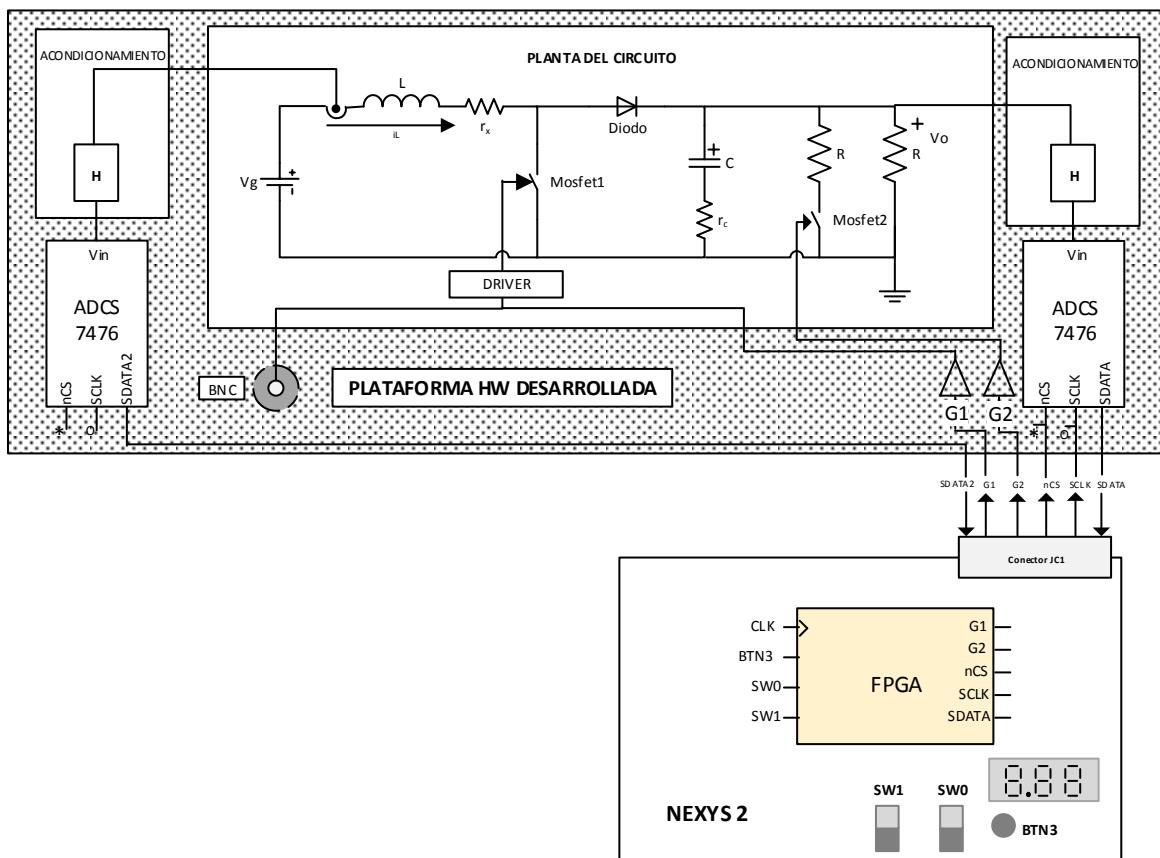

| Fig. 1 Esquema general del sistema completo .....                                                                                                                 | 3  |

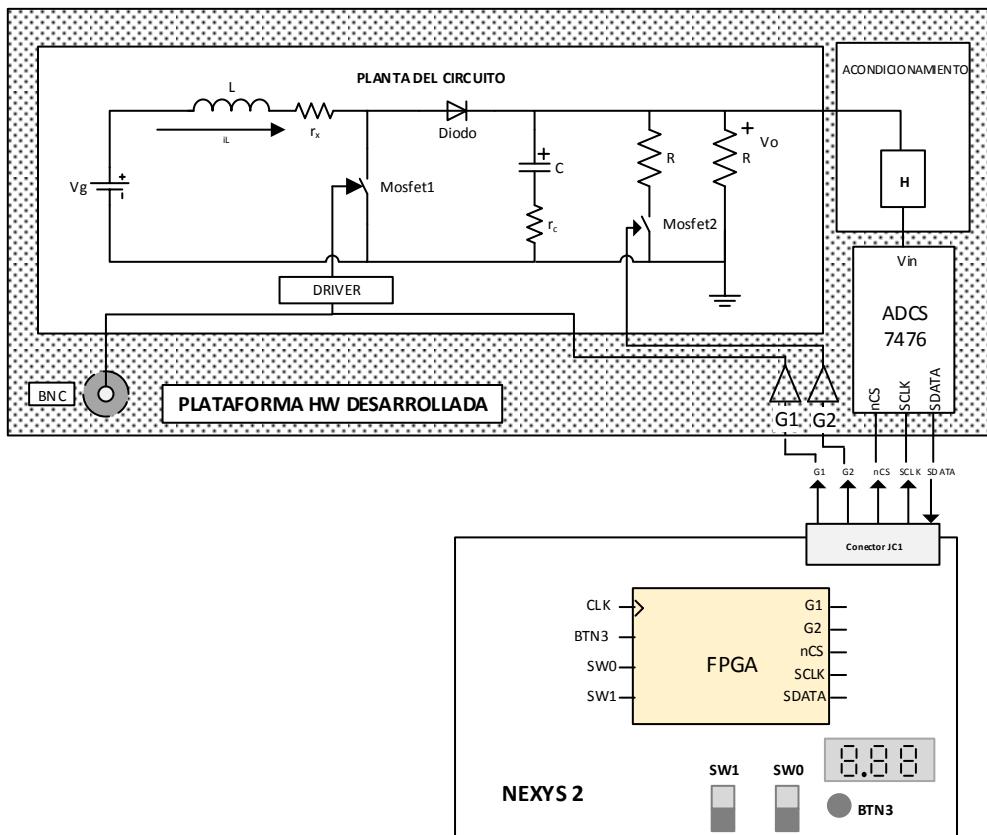

| Fig. 2 Esquema del sistema utilizado para realizar el control por tensión en la carga .....                                                                       | 4  |

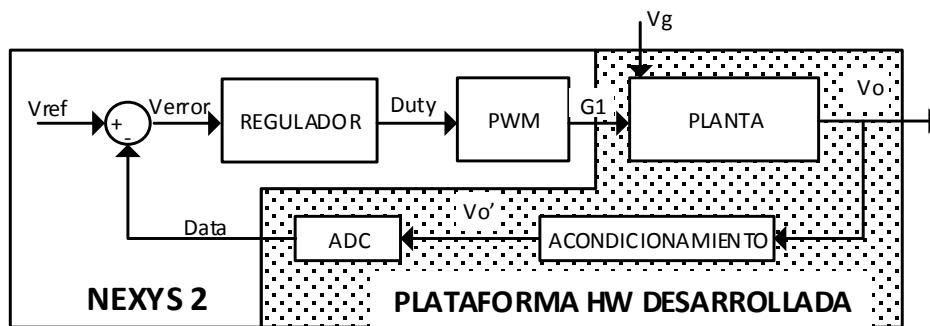

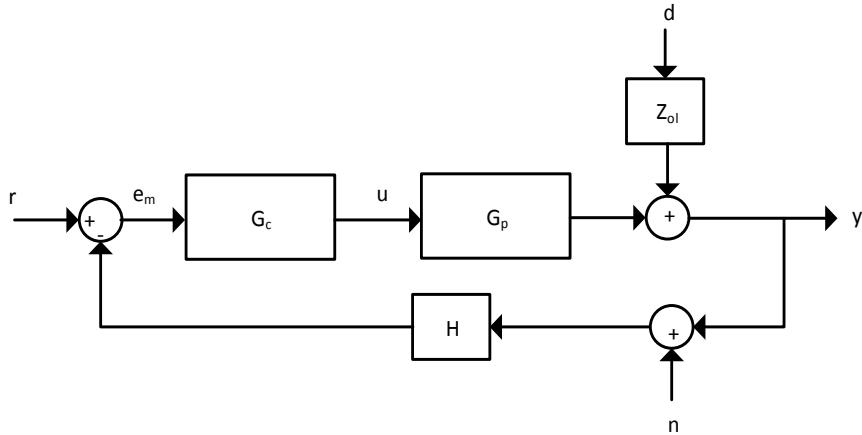

| Fig. 3 Diagrama de bloques del sistema.....                                                                                                                       | 5  |

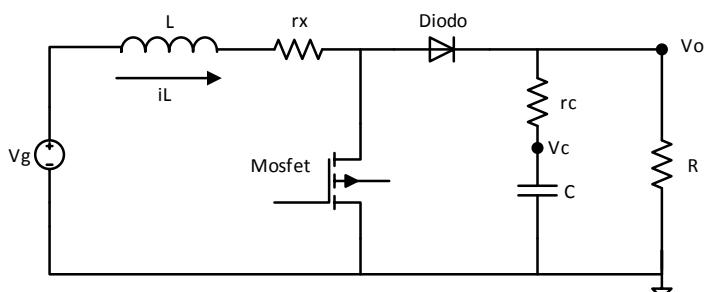

| Fig. 4 Circuito electrónico del convertidor Boost.....                                                                                                            | 7  |

| Fig. 5 Circuito equivalente del convertidor en función del estado del Mosfet.....                                                                                 | 8  |

| Fig. 6 Diagrama de bode de la planta $G_p$ .....                                                                                                                  | 11 |

| Fig. 7 Circuito equivalente de la etapa de acondicionamiento .....                                                                                                | 12 |

| Fig. 8 Diagrama de bode de la planta con el bloque de acondicionamiento $G_p * H$ .....                                                                           | 13 |

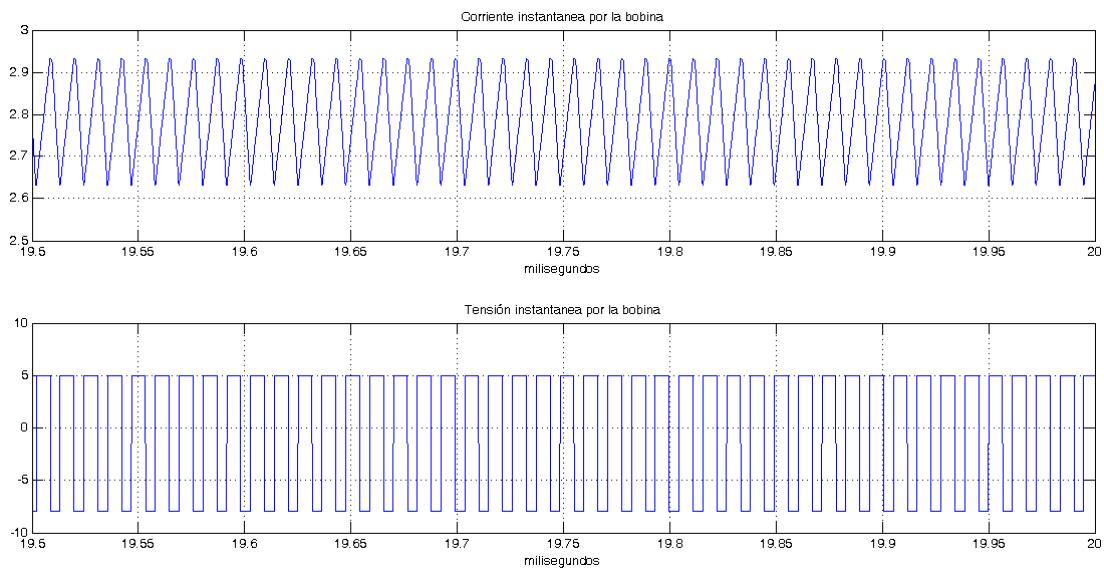

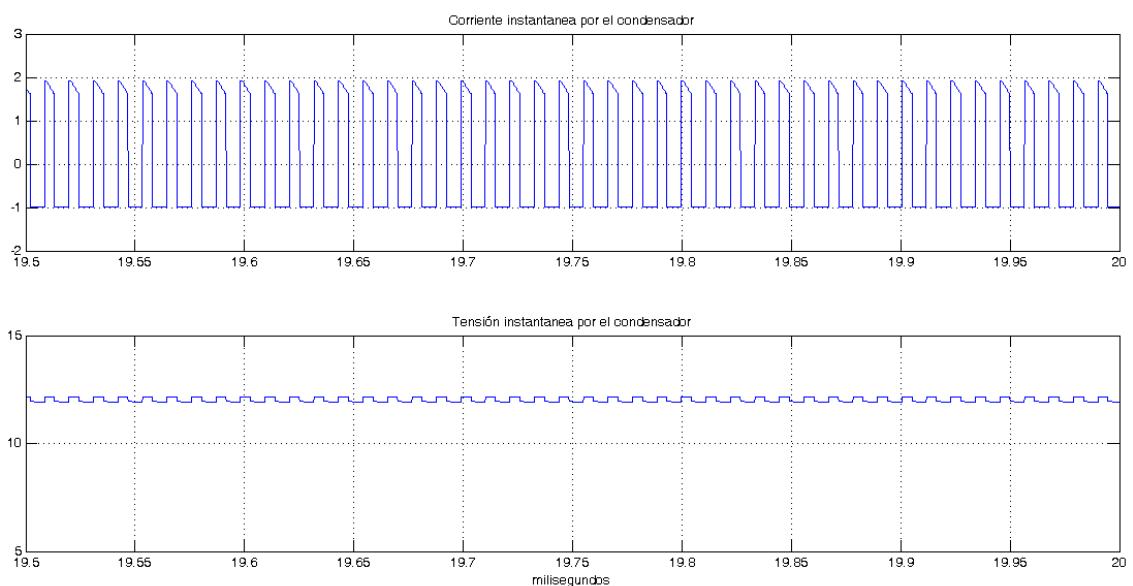

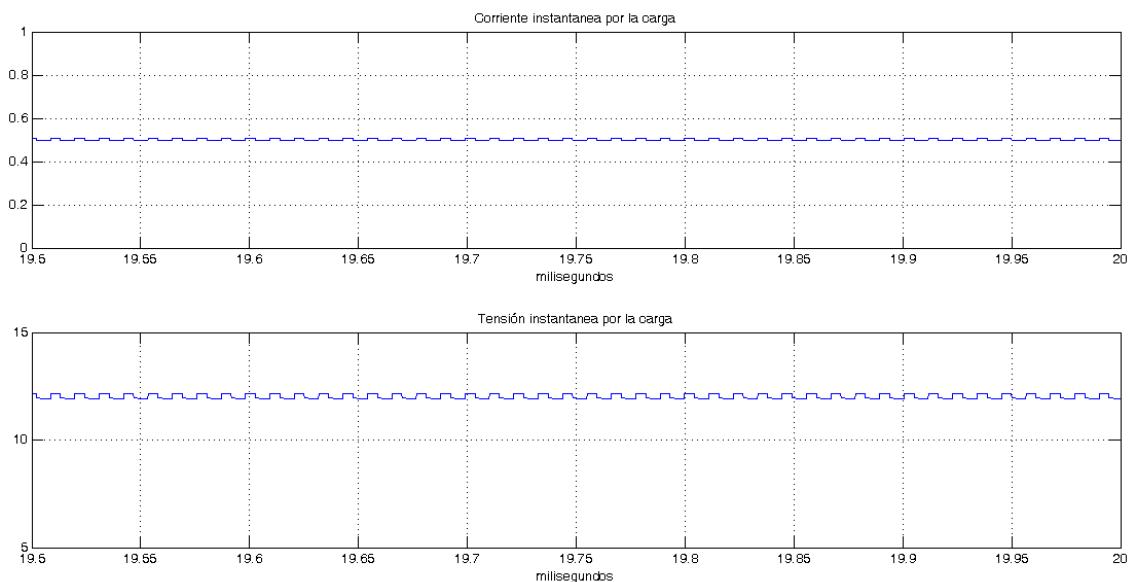

| Fig. 9 Gráficas de corriente (A) y tensión (V) en régimen permanente por la bobina en el caso más desfavorable .....                                              | 13 |

| Fig. 10 Gráficas de corriente (A) y tensión (V) en régimen permanente por el condensador en el caso más desfavorable .....                                        | 14 |

| Fig. 11 Gráficas de corriente (A) y tensión (V) en régimen permanente por la carga .....                                                                          | 15 |

| Fig. 12 Fotografía de la plataforma Hardware desarrollada conectada a la tarjeta NEXYS 2 .....                                                                    | 16 |

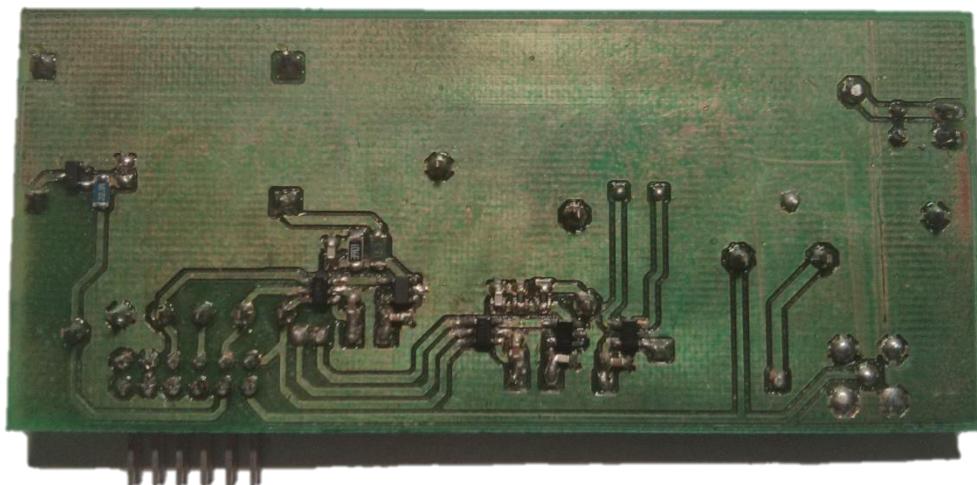

| Fig. 13 Fotografía de la cara BOTTOM de la plataforma HW desarrollada .....                                                                                       | 17 |

| Fig. 14 Fotografía de la cara TOP de la plataforma HW desarrollada .....                                                                                          | 18 |

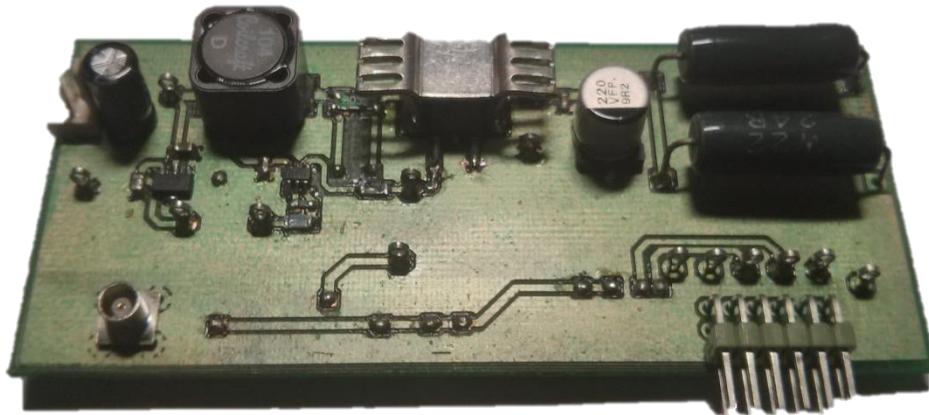

| Fig. 15 Gráficas de corriente (A) y tensión (V) en régimen permanente por el transistor Mosfet en el caso más desfavorable .....                                  | 19 |

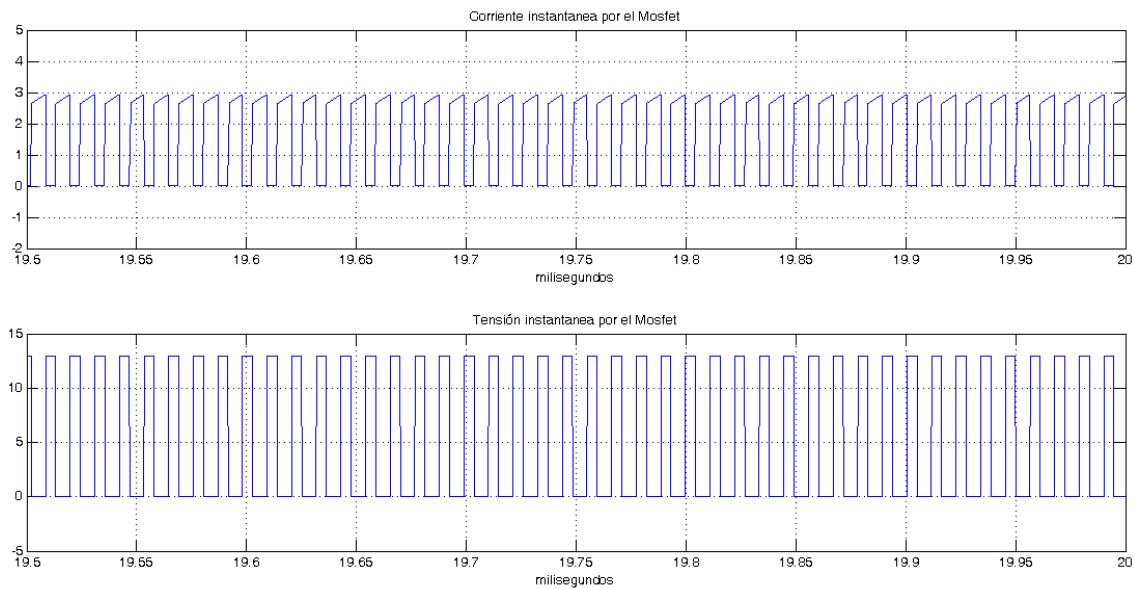

| Fig. 16 Gráficas de corriente (A) y tensión (V) en régimen permanente por el diodo en el caso más desfavorable .....                                              | 20 |

| Fig. 17 Circuito equivalente de la etapa de acondicionamiento .....                                                                                               | 21 |

| Fig. 18 Pasos seguidos para la realización y comprobación del regulador digital implementado...                                                                   | 22 |

| Fig. 19 Diagrama de bloques del sistema.....                                                                                                                      | 24 |

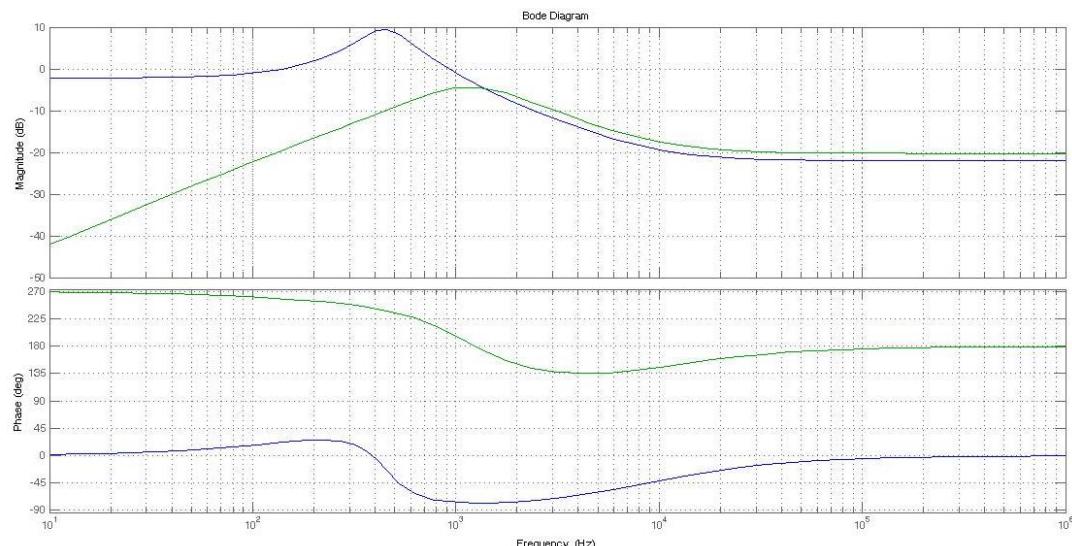

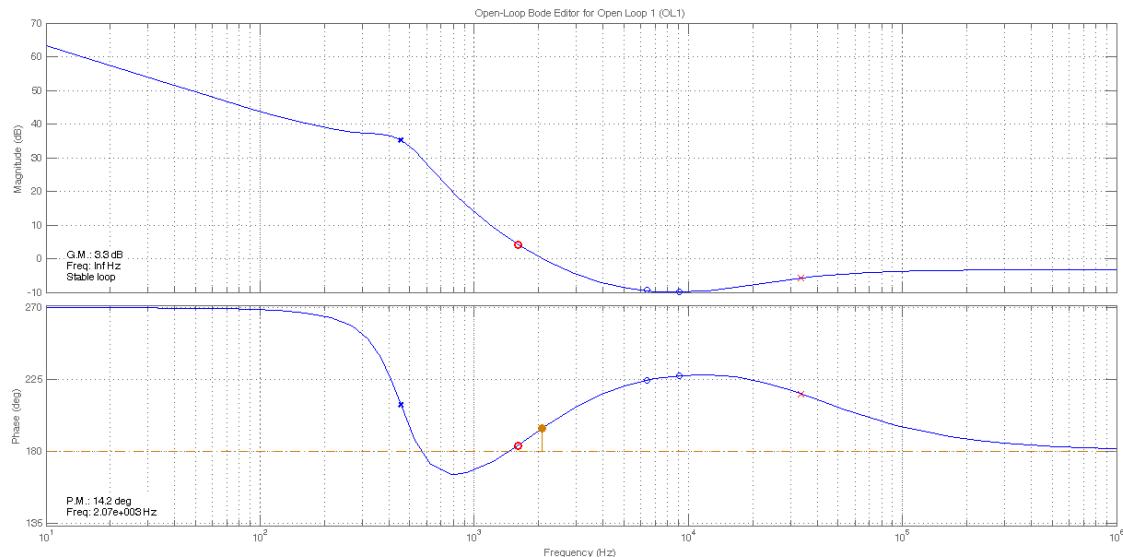

| Fig. 20 Diagrama de bode del sistema en bucle abierto .....                                                                                                       | 28 |

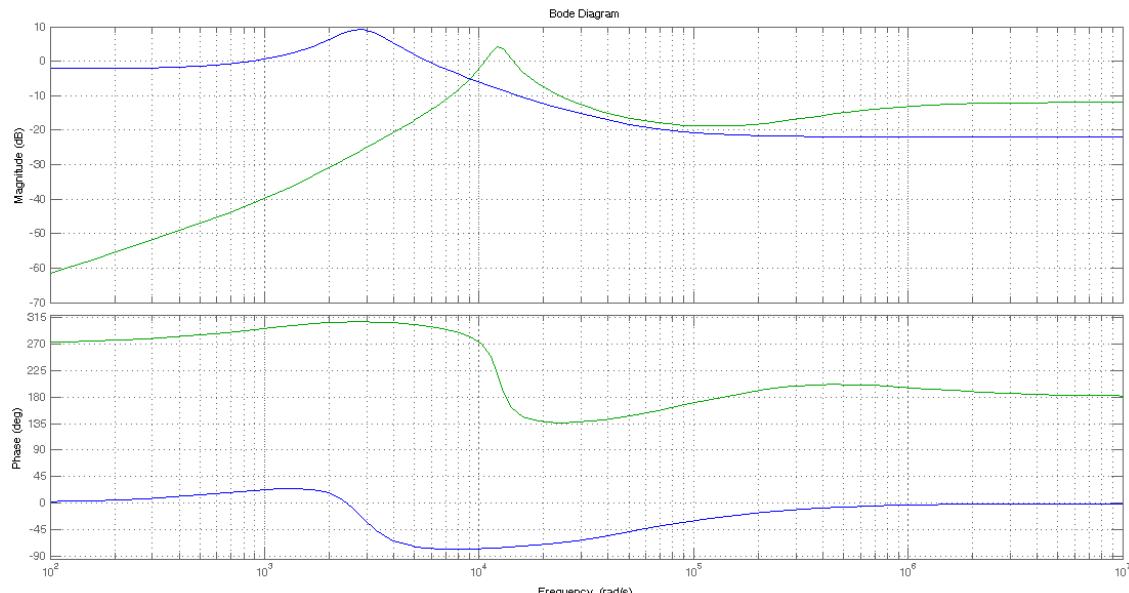

| Fig. 21 Diagrama de bode de la impedancia de salida en bucle abierto (azul) y en bucle cerrado (verde) .....                                                      | 29 |

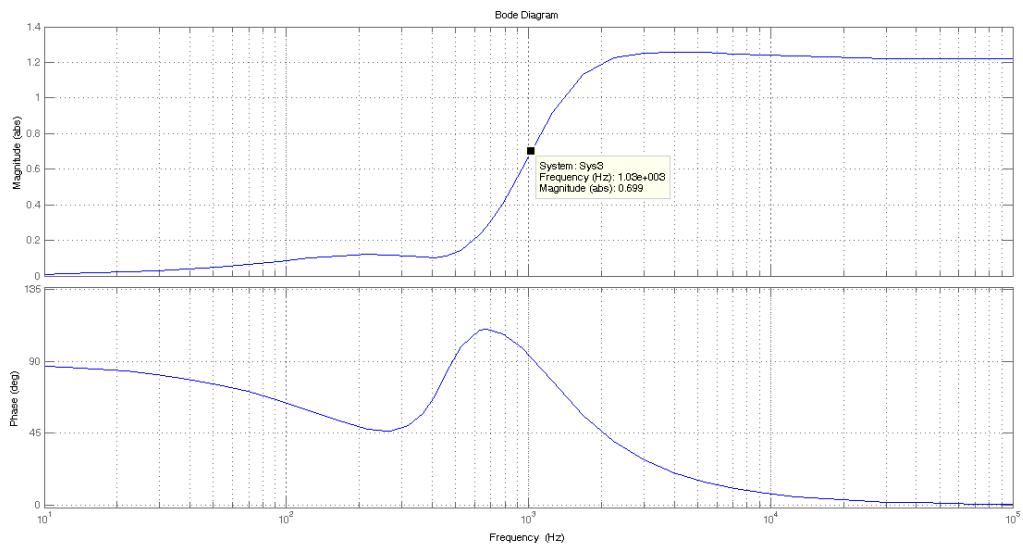

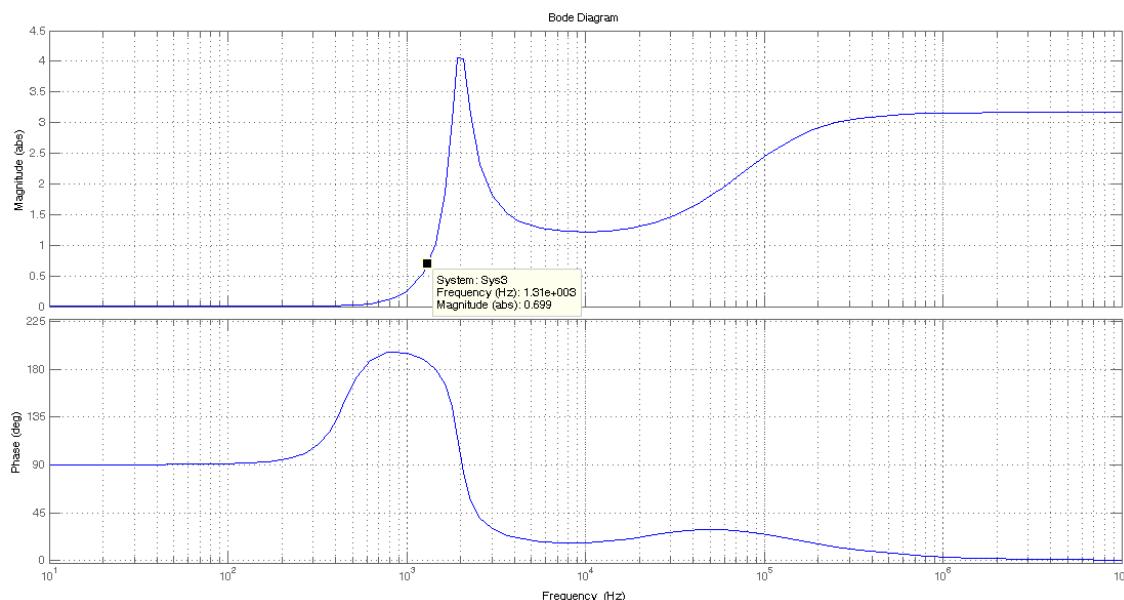

| Fig. 22 Diagrama de Bode de la función de sensibilidad S .....                                                                                                    | 30 |

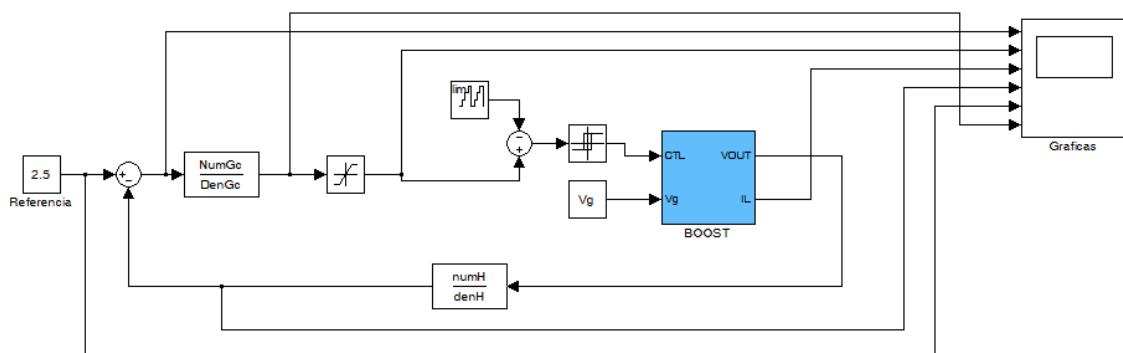

| Fig. 23 Modelo del sistema en modo continuo .....                                                                                                                 | 30 |

| Fig. 24 Circuito equivalente del convertidor Boost obtenido a partir de sus ecuaciones de estado                                                                  | 31 |

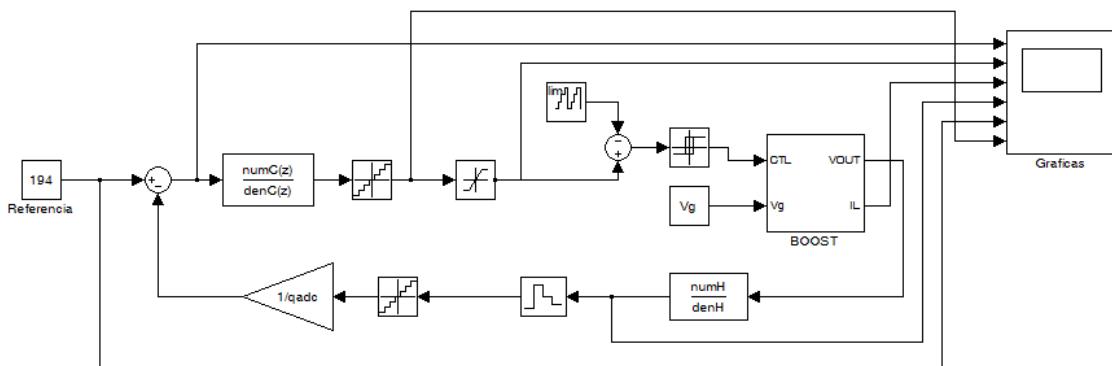

| Fig. 25 Modelo del sistema en modo discreto .....                                                                                                                 | 32 |

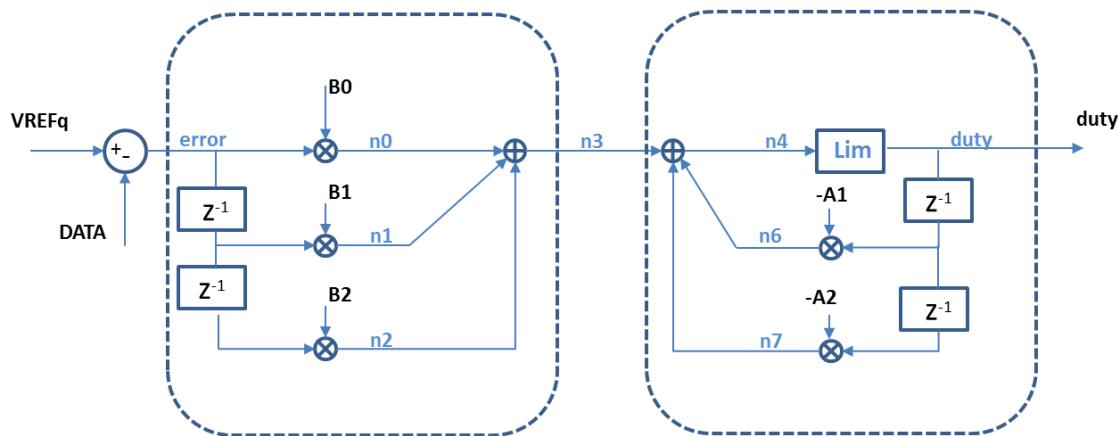

| Fig. 26 Implementación del controlador, a la izquierda método tradicional [6], a la derecha solución implementada en este proyecto.....                           | 33 |

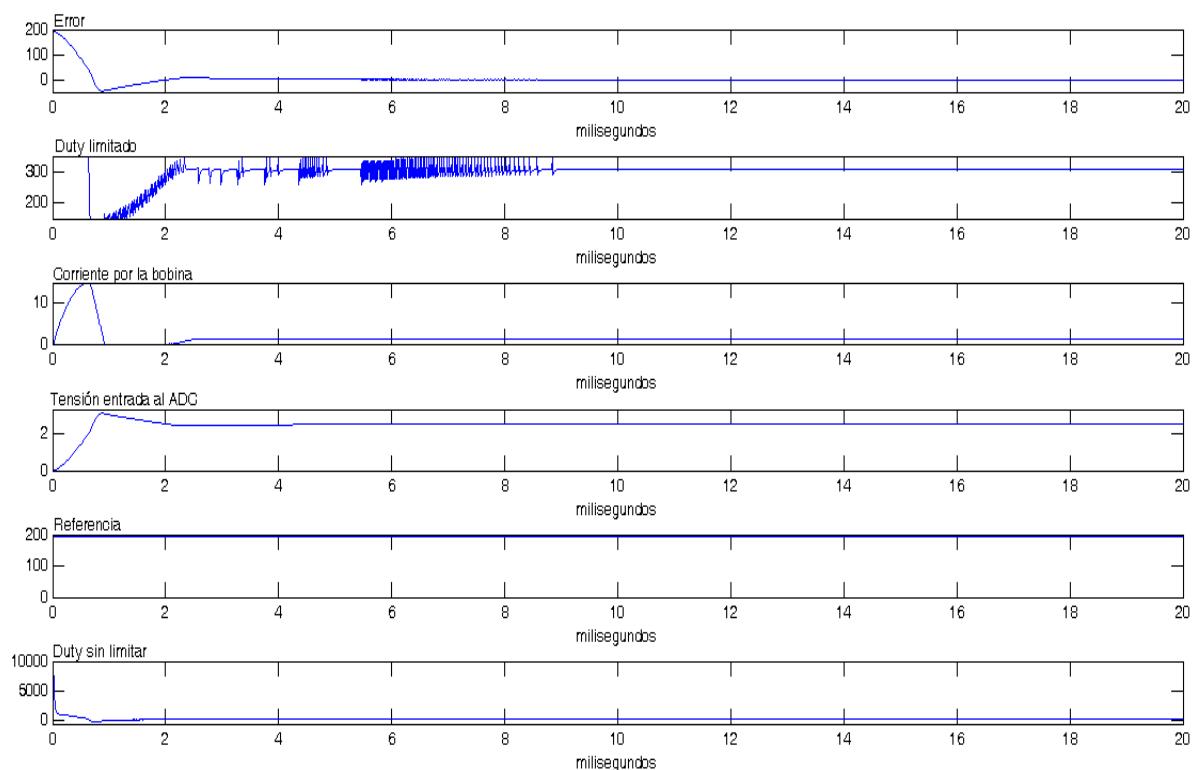

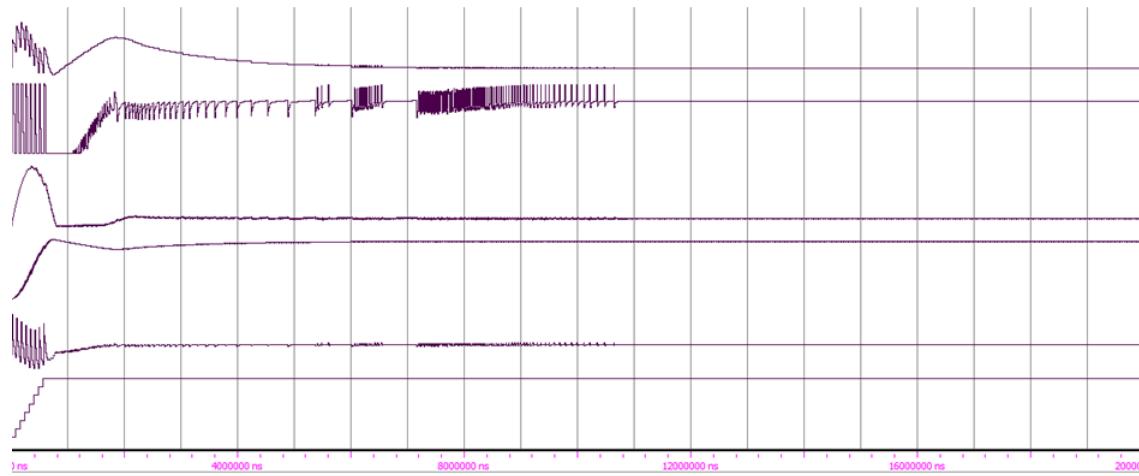

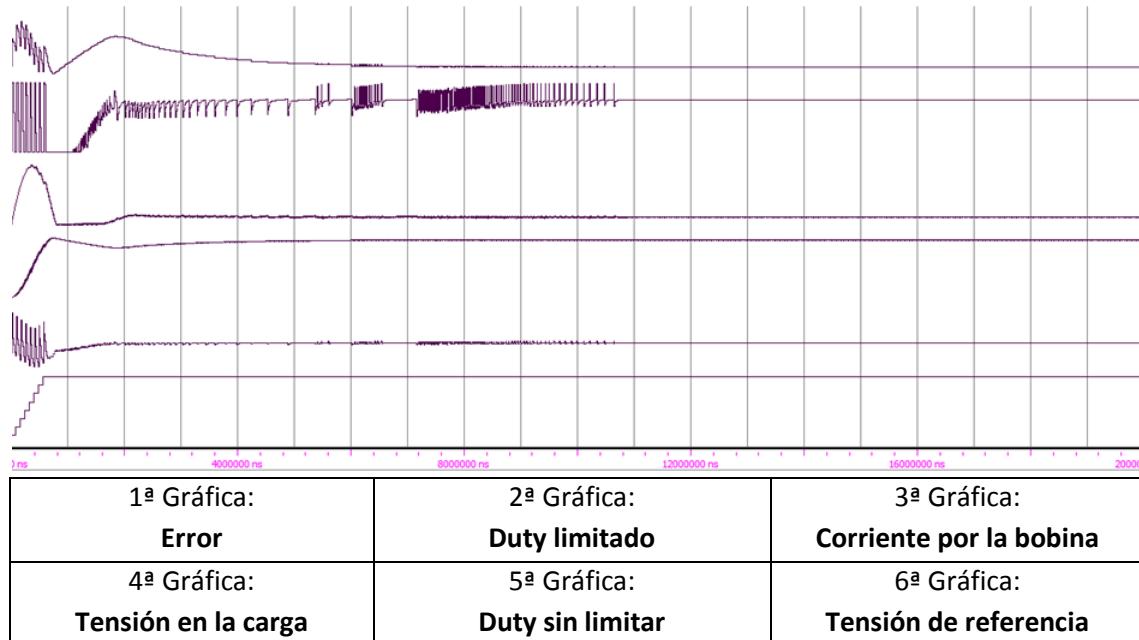

| Fig. 27 Simulación sistema en modo discreto durante 20 milisegundos .....                                                                                         | 34 |

| Fig. 28 Simulación sistema en modo discreto con Soft Start .....                                                                                                  | 35 |

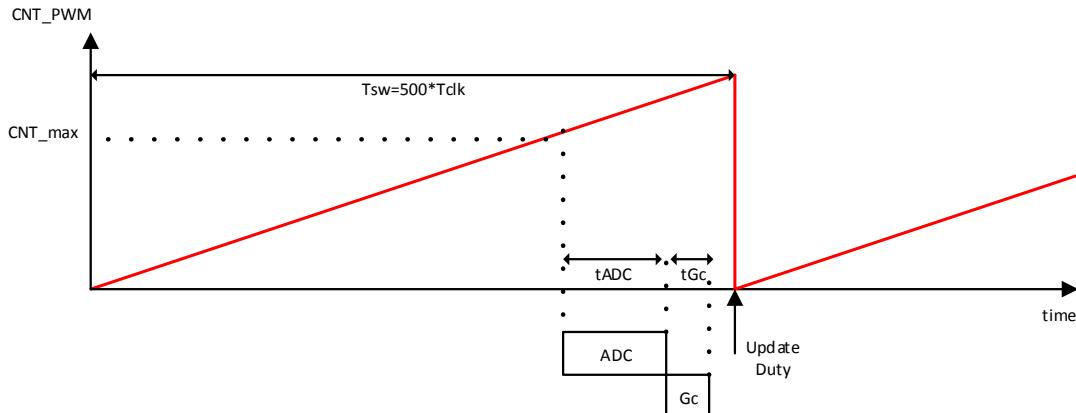

| Fig. 29 Esquema general del sistema completo .....                                                                                                                | 36 |

| Fig. 30 Representación de un periodo de conmutación, mostrando los tiempos destinados al protocolo de comunicaciones con el ADC y al cálculo del nuevo duty ..... | 37 |

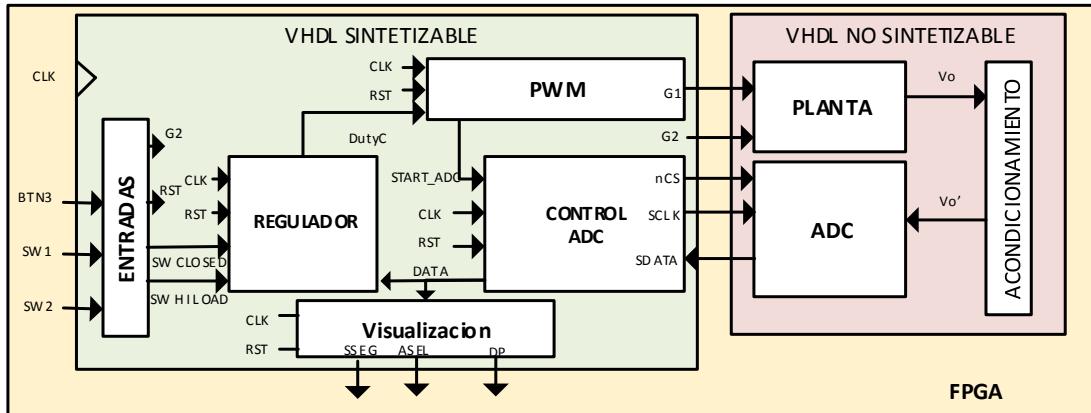

| Fig. 31 Esquema de bloques del diseño VHDL completo para realizar la validación por simulación con la herramienta Modelsim. ....                                  | 38 |

|                                                                                                                                                                                                                        |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 32 Resultados de la simulación con el regulador implementado con números reales en 20ms .....                                                                                                                     | 40 |

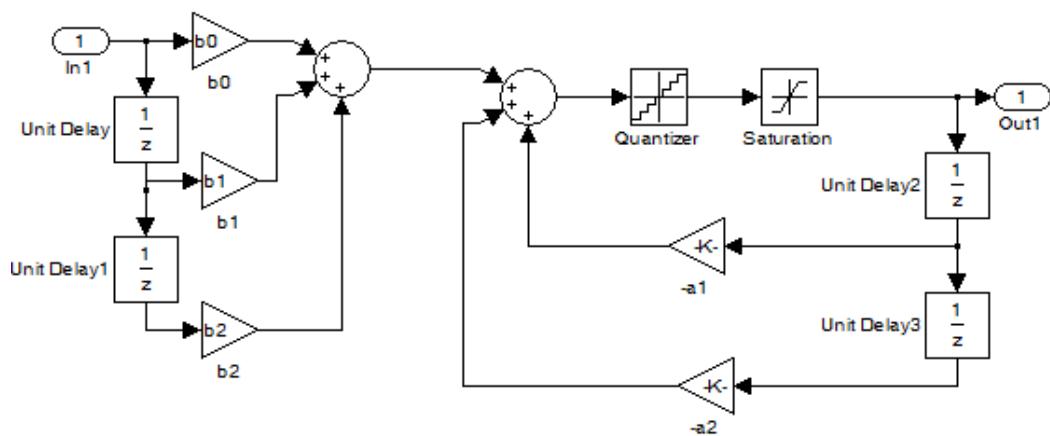

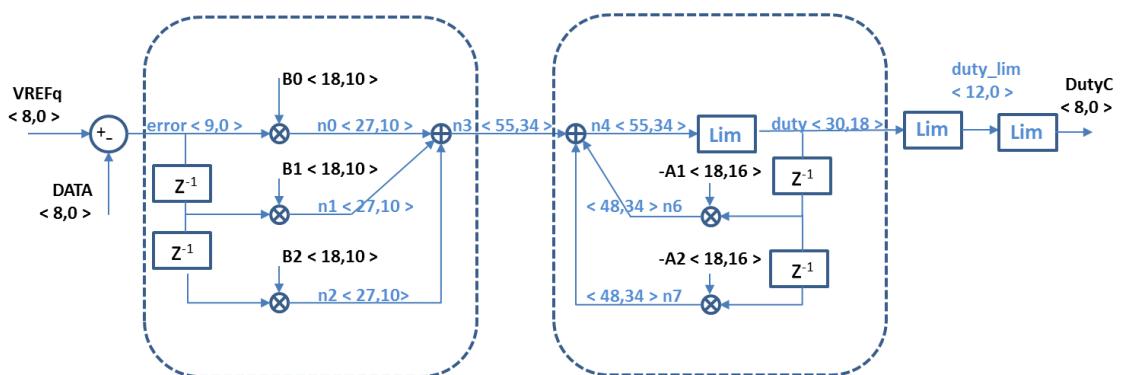

| Fig. 33 Estructura del regulador implementado .....                                                                                                                                                                    | 41 |

| Fig. 34 Modelo del sistema en modo discreto con controlador con resolución finita.....                                                                                                                                 | 42 |

| Fig. 35 Diseño en Simulink para obtener el tamaño de los registros que almacenan las variables de estado.....                                                                                                          | 43 |

| Fig. 36 Estructura del regulador y tamaño de los coeficientes y variables de estado para la implementación del regulador .....                                                                                         | 43 |

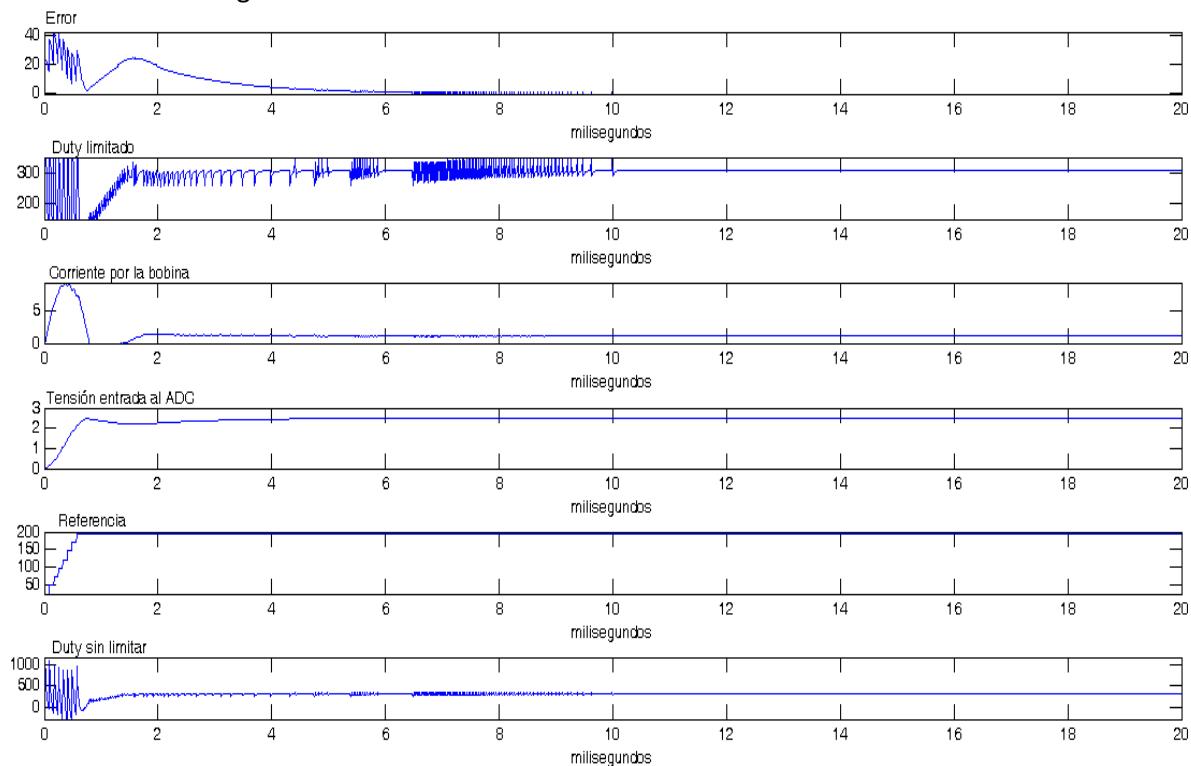

| Fig. 37 Resultados de la simulación, con el regulador implementado en coma fija, en 20ms .....                                                                                                                         | 45 |

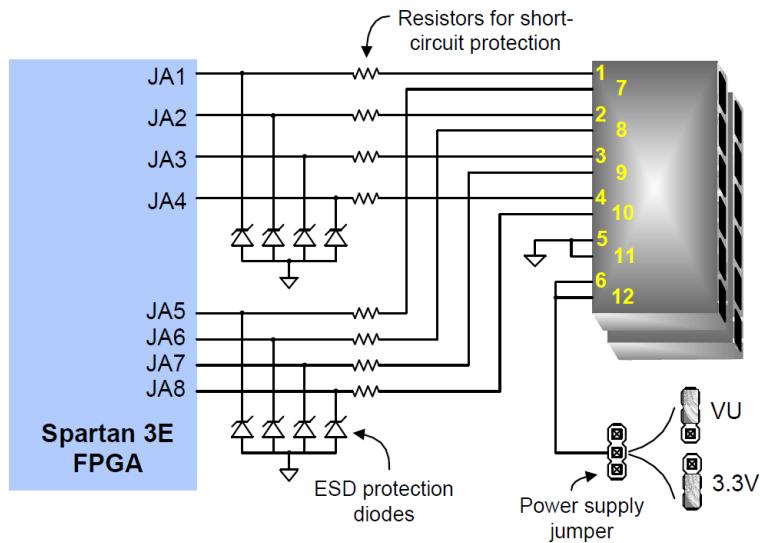

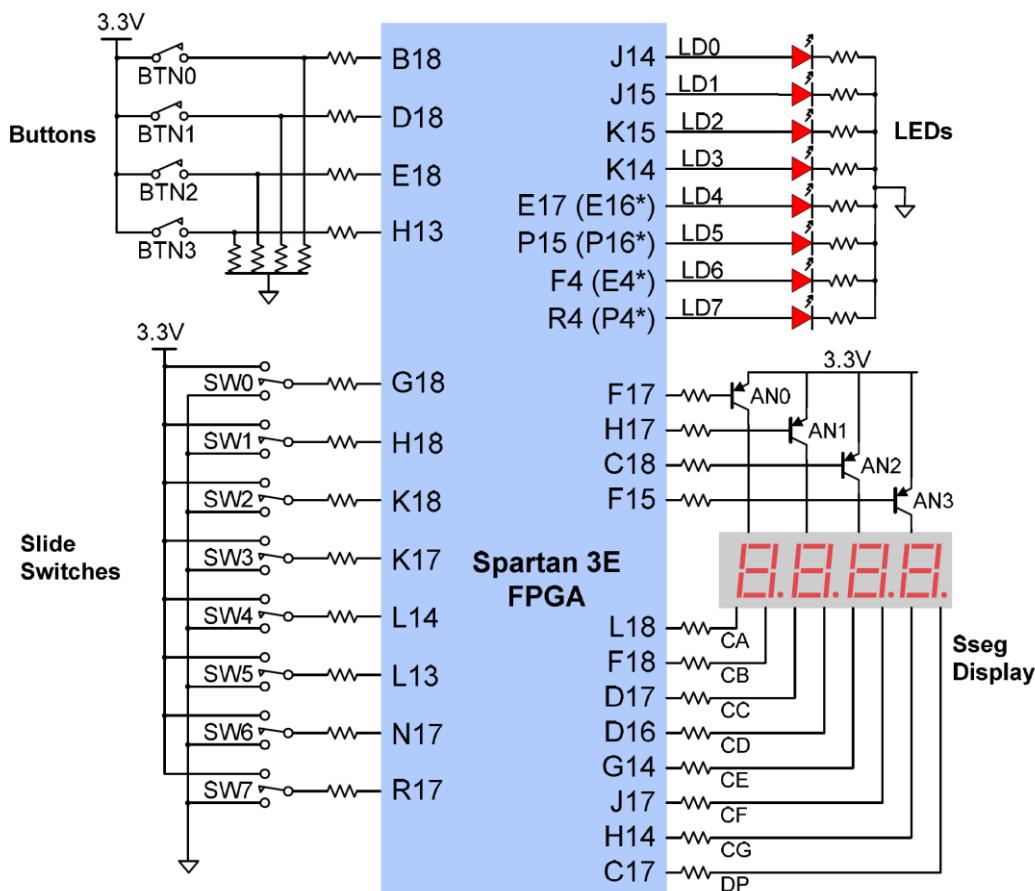

| Fig. 38 Asignación de pines del conector PMOD (imagen obtenida del manual de la placa Nexys2) .....                                                                                                                    | 47 |

| Fig. 39 Asignación de pines y circuitos de entradas/salidas de la FPGA (imagen obtenida del manual de la placa Nexys2).....                                                                                            | 47 |

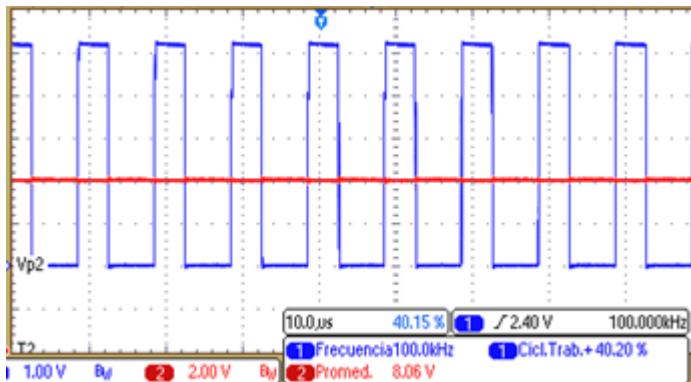

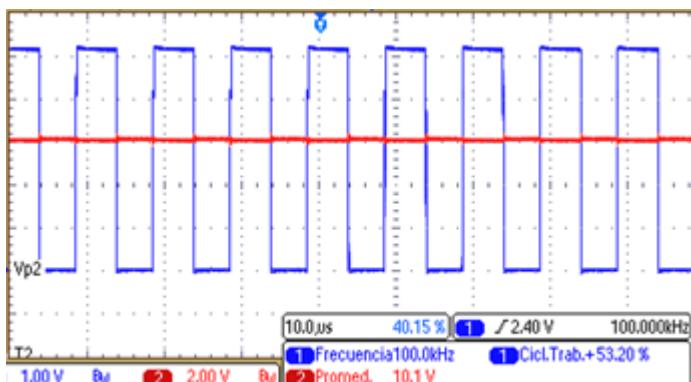

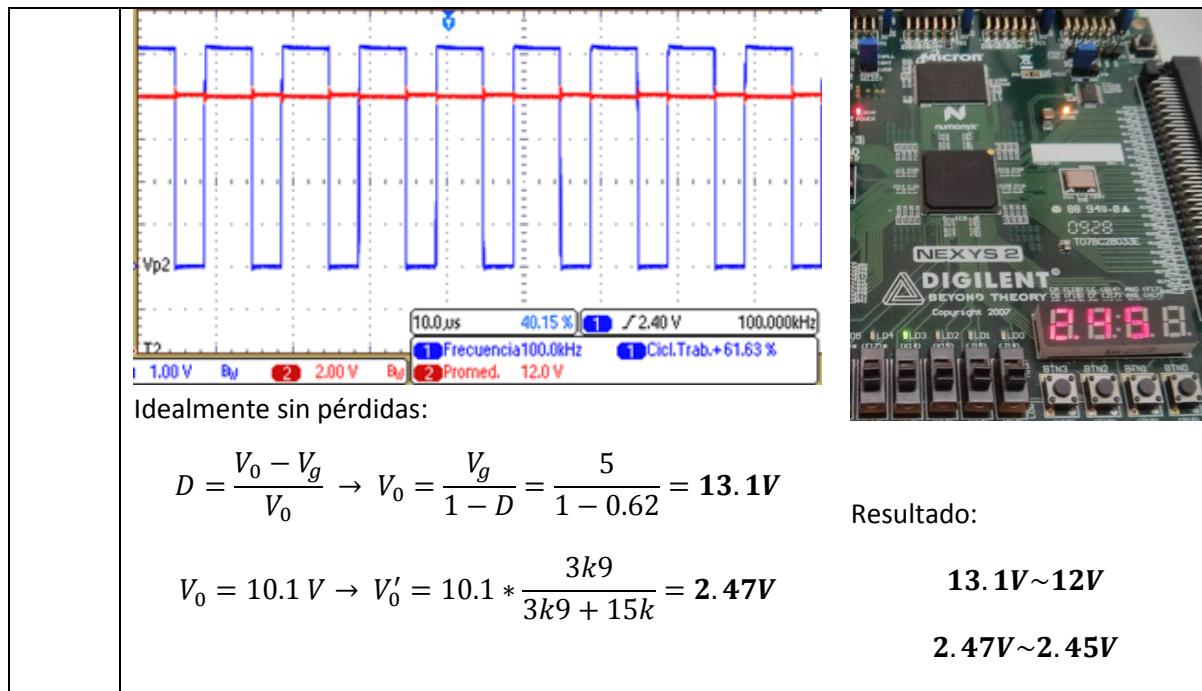

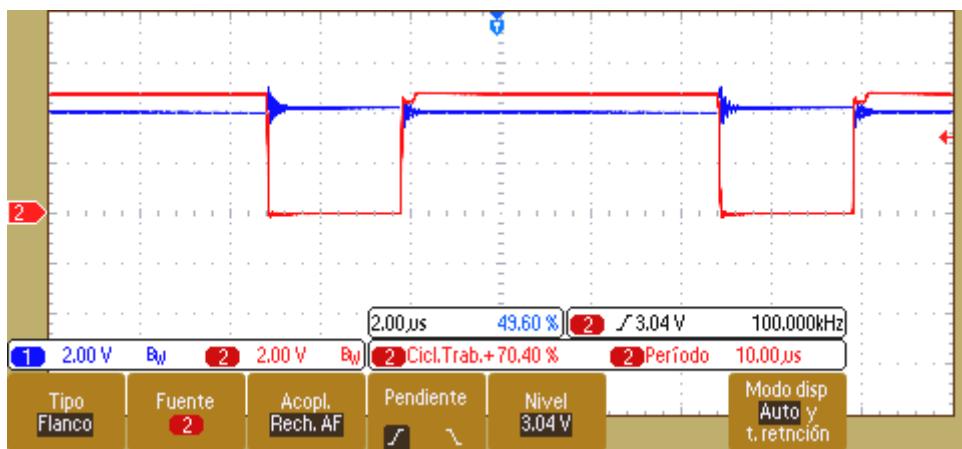

| Fig. 40 Esquema general del sistema para el proceso de verificación de la PCB utilizando un generador de señales .....                                                                                                 | 49 |

| Fig. 41 Puntos de test de la PCB en los que se realizan las medidas.....                                                                                                                                               | 49 |

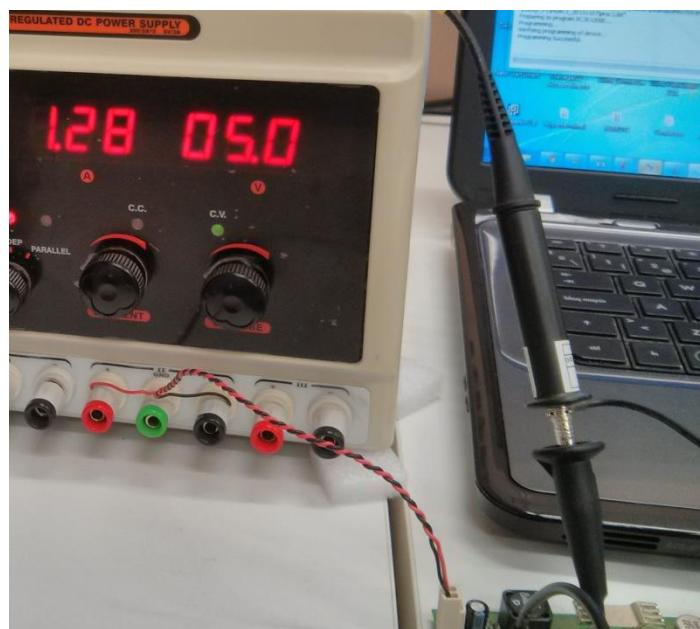

| Fig. 42 Medida de tensión y de corriente en la fuente de alimentación .....                                                                                                                                            | 52 |

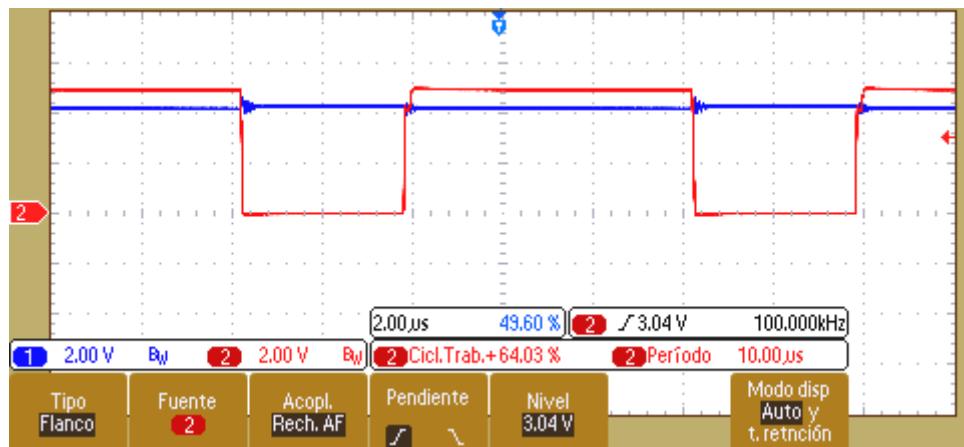

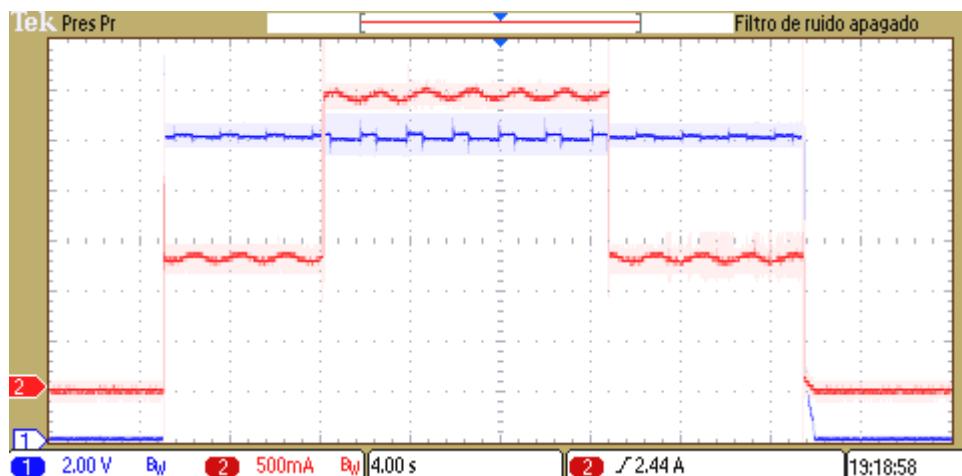

| Fig. 43 Control en Bucle cerrado con carga de $24\Omega$ .....                                                                                                                                                         | 52 |

| Fig. 44 Control en bucle cerrado con carga de $12\Omega$ .....                                                                                                                                                         | 53 |

| Fig. 45 Transitorio de la tensión en la carga y la corriente en la bobina al encender la fuente, modificar la carga de $24\Omega$ a $12\Omega$ , modificar la carga de $12\Omega$ a $24\Omega$ y apagar la fuente..... | 53 |

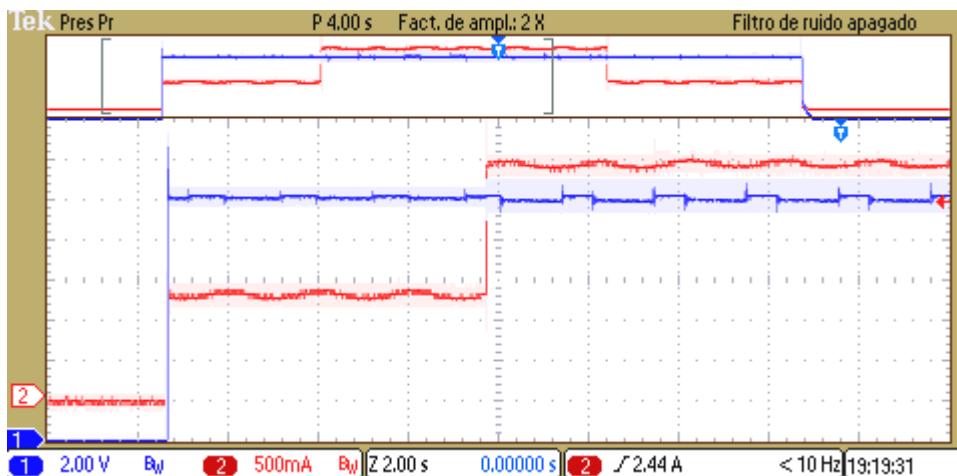

| Fig. 46 Detalle de la tensión en la carga y la corriente en la bobina al encender la fuente de alimentación y modificar la carga de $24\Omega$ a $12\Omega$ .....                                                      | 54 |

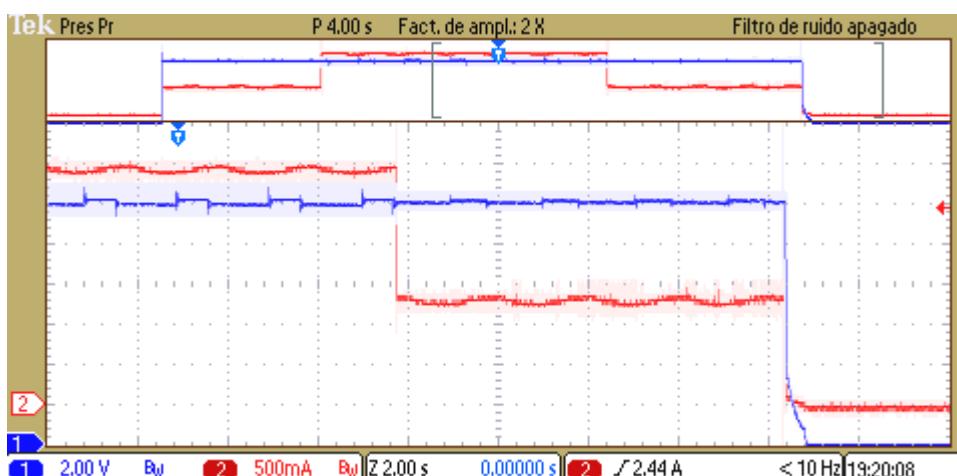

| Fig. 47 Detalle de la tensión en la carga y la corriente en la bobina al modificar la carga de $12\Omega$ a $24\Omega$ y apagar la fuente de alimentación. ....                                                        | 54 |

| Fig. 48 Plano esquemático de los componentes y conexiones de la plataforma Hardware.....                                                                                                                               | 66 |

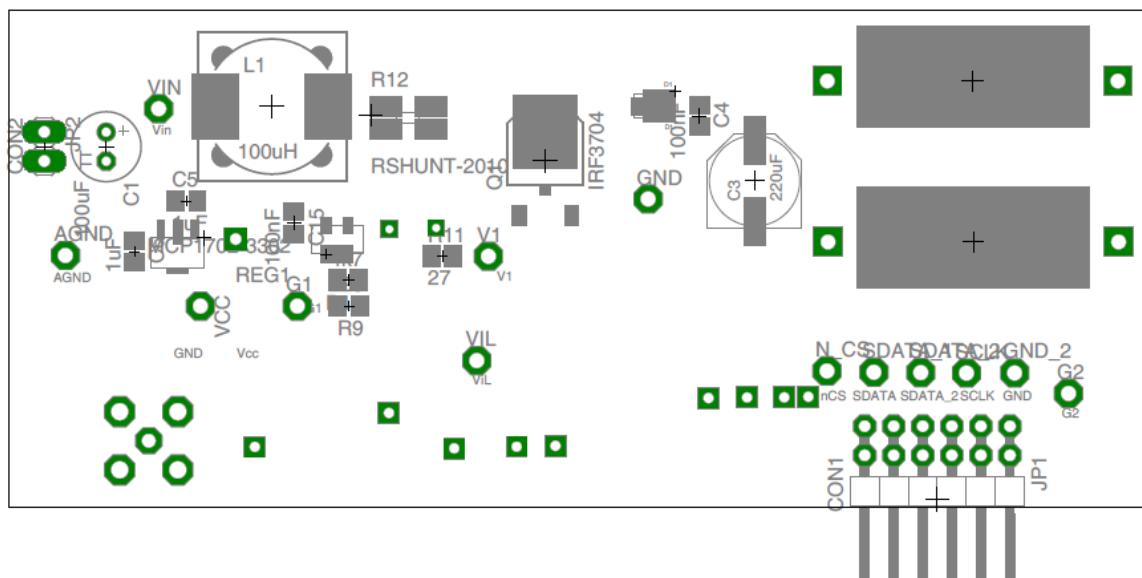

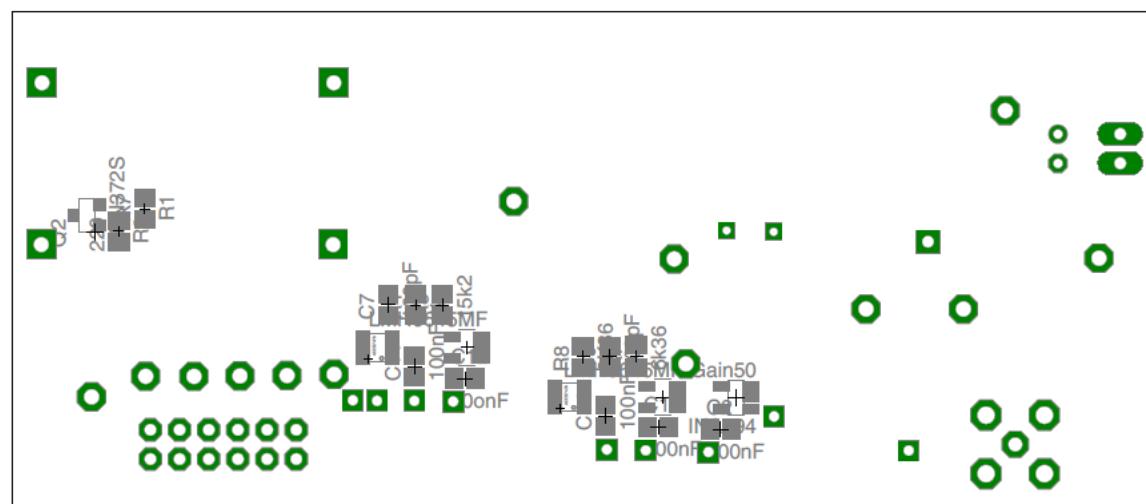

| Fig. 49 Vista de la cara TOP de la plataforma Hardware .....                                                                                                                                                           | 67 |

| Fig. 50 Vista de situación de los componentes en la cara TOP de la plataforma Hardware .....                                                                                                                           | 67 |

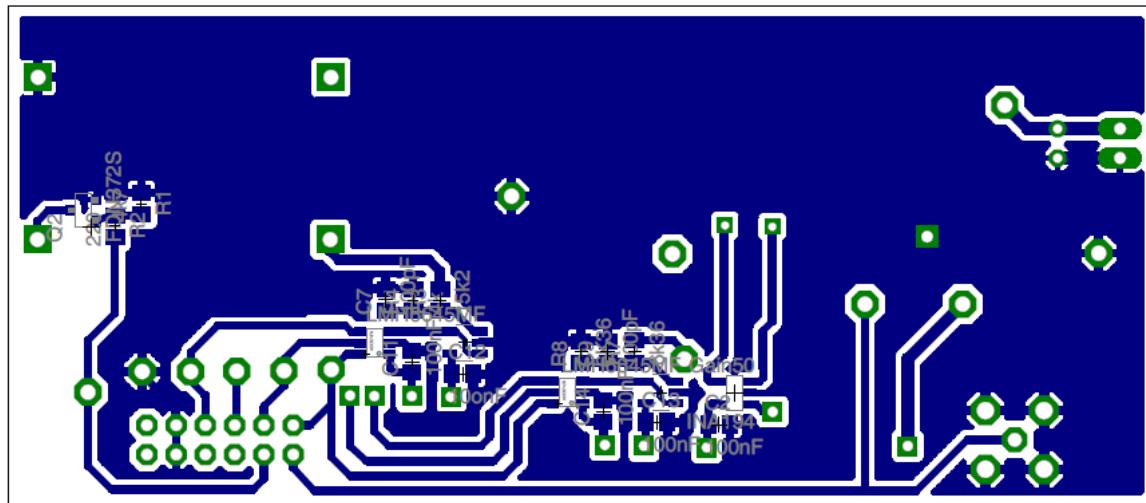

| Fig. 51 Vista de la cara BOTTOM de la plataforma Hardware .....                                                                                                                                                        | 68 |

| Fig. 52 Vista de situación de los componentes en la cara BOTTOM de la plataforma Hardware....                                                                                                                          | 68 |

| Fig. 53 Diagrama de bode de la planta con el acondicionamiento para el cálculo de los parámetros $K_u$ y $w_u$ .....                                                                                                   | 71 |

| Fig. 54 Diagrama de bloques del sistema completo.....                                                                                                                                                                  | 75 |

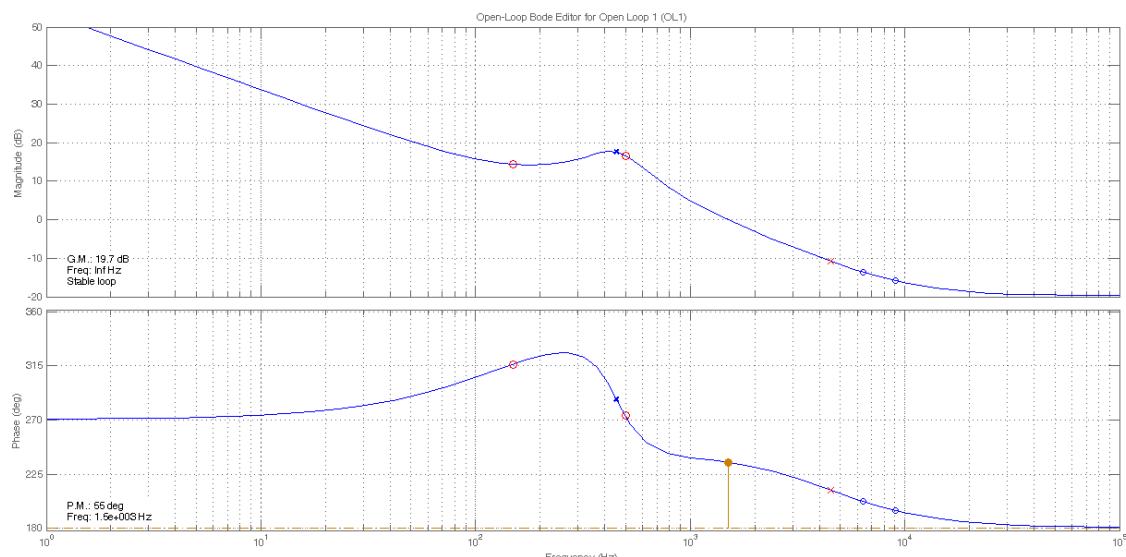

| Fig. 55 Diagrama de bode del sistema en bucle abierto, $fc=2.07\text{kHz}$ , $PM=14.2^\circ$ , $GM=3.3\text{ dB}$ .....                                                                                                | 79 |

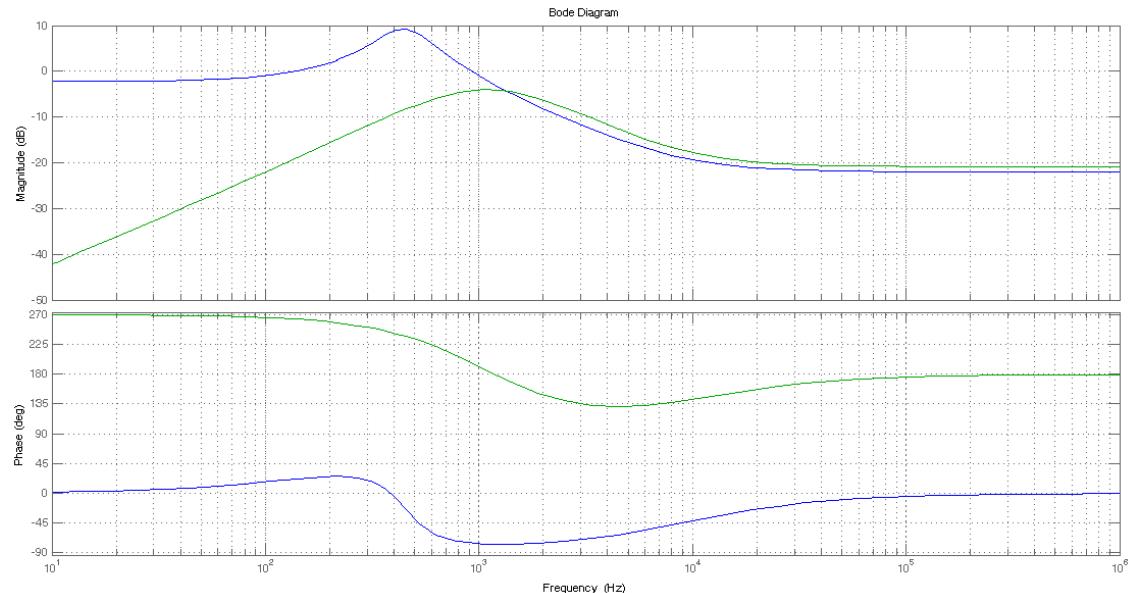

| Fig. 56 Diagrama de bode de la impedancia de salida en bucle abierto (azul) y en bucle cerrado (verde) .....                                                                                                           | 80 |

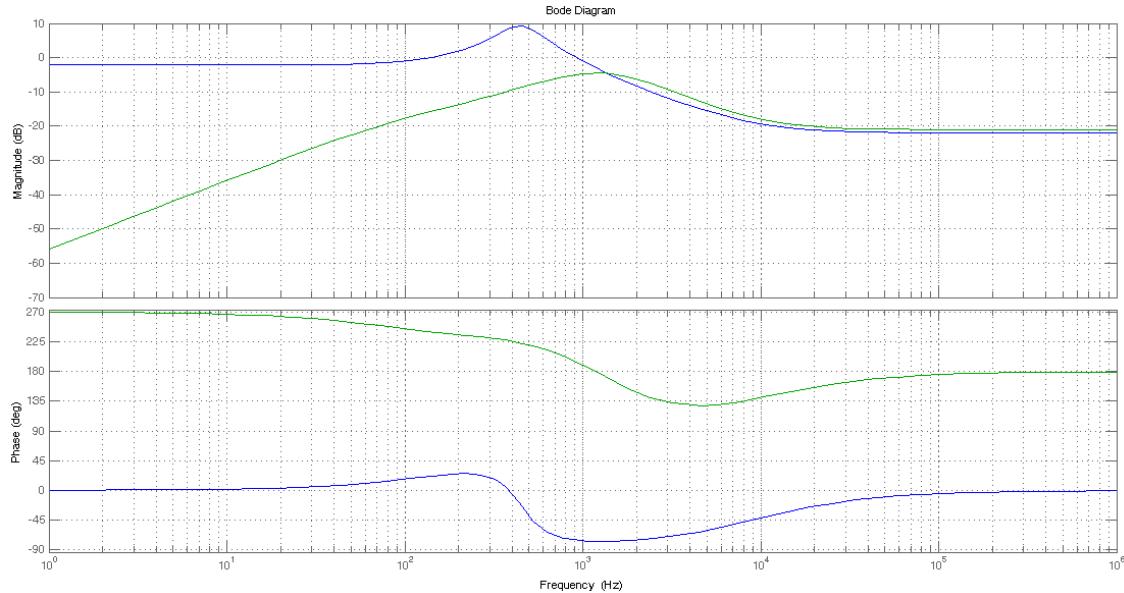

| Fig. 57 Diagrama de Bode de la función de sensibilidad $S$ .....                                                                                                                                                       | 80 |

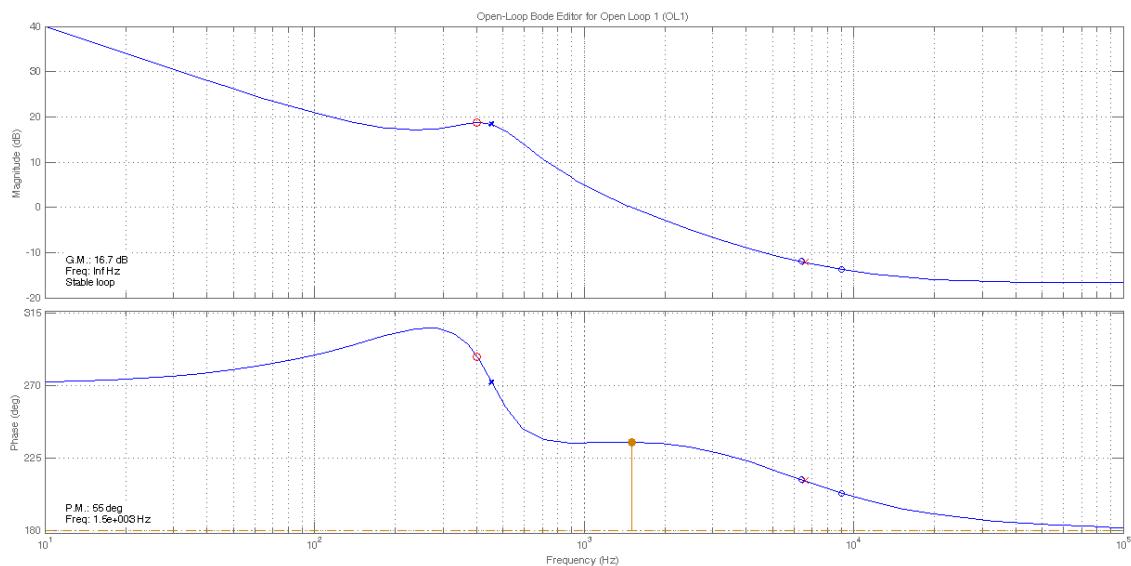

| Fig. 58 Diagrama de bode del sistema en bucle abierto, $fc=1.5\text{kHz}$ , $PM=55^\circ$ , $GM=16.7\text{ dB}$ .....                                                                                                  | 81 |

| Fig. 59 Diagrama de bode de la impedancia de salida en bucle abierto (azul) y en bucle cerrado (verde) .....                                                                                                           | 82 |

| Fig. 60 Diagrama de Bode de la función de sensibilidad $S$ .....                                                                                                                                                       | 82 |

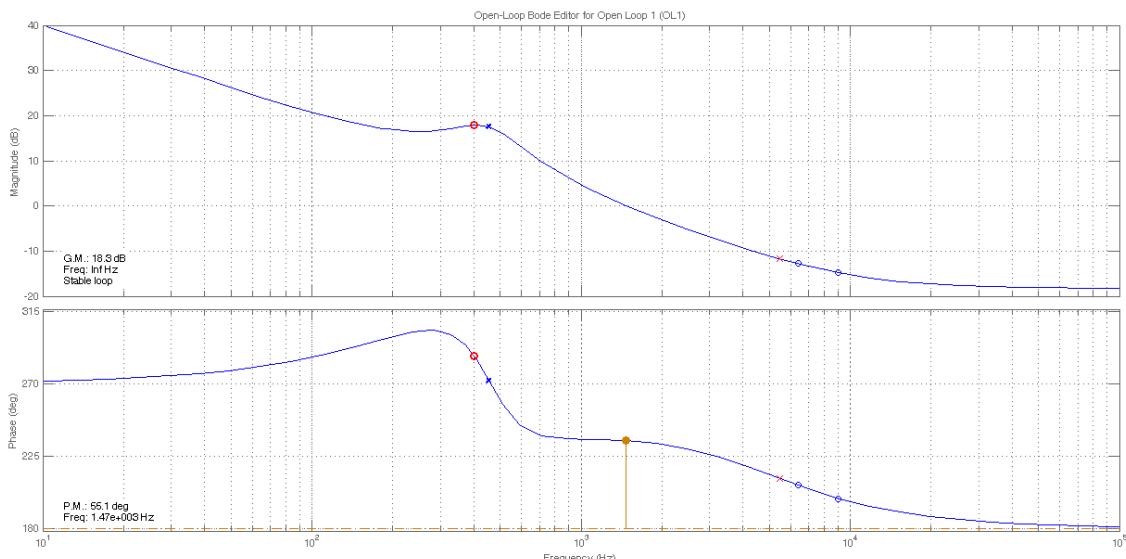

| Fig. 61 Diagrama de bode del sistema en bucle abierto, $fc=1.47\text{kHz}$ , $PM=55.1^\circ$ , $GM=18.3\text{ dB}$ .....                                                                                               | 83 |

| Fig. 62 Diagrama de bode de la impedancia de salida en bucle abierto (azul) y en bucle cerrado (verde) .....                                                                                                           | 84 |

| Fig. 63 Diagrama de Bode de la función de sensibilidad $S$ .....                                                                                                                                                       | 84 |

|                                                                                                                       |    |

|-----------------------------------------------------------------------------------------------------------------------|----|

| Fig. 64 Diagrama de bode del sistema en bucle abierto, $fc=1.5\text{kHz}$ , $PM=55^\circ$ , $GM=19.7\text{ dB}$ ..... | 85 |

| Fig. 65 Diagrama de bode de la impedancia de salida en bucle abierto (azul) y en bucle cerrado (verde) .....          | 86 |

| Fig. 66 Diagrama de Bode de la función de sensibilidad $S$ .....                                                      | 86 |

#### **INDICE DE TABLAS:**

|                                                                                                                                         |     |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tabla 1 Especificaciones iniciales de diseño para el cálculo del regulador.....                                                         | 23  |

| Tabla 2 Reguladores calculados durante el desarrollo del trabajo .....                                                                  | 26  |

| Tabla 3 Funciones de mérito evaluadas .....                                                                                             | 27  |

| Tabla 4 Tabla de resultados en las que se muestran los resultados obtenidos para las distintas funciones de mérito .....                | 27  |

| Tabla 5 Script en Matlab para la obtención de los valores de las funciones de mérito.....                                               | 29  |

| Tabla 6 Script en Matlab para transformar el regulador de continuo a digital.....                                                       | 32  |

| Tabla 7 Parámetros del ADC y de la PWM implementada utilizados para la simulación en Matlab                                             | 33  |

| Tabla 8 Coeficientes del regulador teniendo en cuenta la resolución de la PWM y la cuantización del ADC .....                           | 34  |

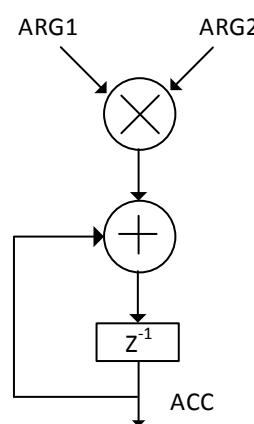

| Tabla 9 Estructura y operación de la unidad MAC implementada.....                                                                       | 38  |

| Tabla 10 Código en VHDL no sintetizable de la implementación en reales del regulador.....                                               | 40  |

| Tabla 11 Representación de los coeficientes en coma fija complemento a 2 y codificación en VHDL .....                                   | 42  |

| Tabla 12 Código en VHDL sintetizable de la implementación en coma fija del regulador.....                                               | 45  |

| Tabla 13 Asignación de pines en la placa Nexys2.....                                                                                    | 48  |

| Tabla 14 Resultados obtenidos experimentalmente con el generador de señales .....                                                       | 51  |

| Tabla 15 Listado de componentes de la plataforma Hardware desarrollada .....                                                            | 70  |

| Tabla 16 Función de transferencia del regulador y parámetros para su cálculo .....                                                      | 71  |

| Tabla 17 Script en Matlab para la obtención de los valores de las funciones de mérito.....                                              | 80  |

| Tabla 18 Script en Matlab para la obtención de los valores de las funciones de mérito.....                                              | 82  |

| Tabla 19 Script en Matlab para la obtención de los valores de las funciones de mérito.....                                              | 84  |

| Tabla 20 Script en Matlab para la obtención de los valores de las funciones de mérito.....                                              | 86  |

| Tabla 21 Código del protocolo de comunicaciones con el conversor ADC en VHDL sintetizable....                                           | 88  |

| Tabla 22 Código del bloque de gestión de los visualizadores de 7 segmentos en VHDL sintetizable. ....                                   | 89  |

| Tabla 23 Código del bloque encargado del filtrado de los rebotes de los interruptores y el pulsador en VHDL sintetizable. ....          | 91  |

| Tabla 24 Código del bloque encargado de la generación de la señal PWM en VHDL sintetizable. .                                           | 91  |

| Tabla 25 Código completo del control digital implementado en la FPGA en VHDL sintetizable. ..                                           | 100 |

| Tabla 26 Código en VHDL no sintetizable de la planta del convertidor y la etapa de acondicionamiento implementado en el Test bench..... | 102 |

| Tabla 27 Código en VHDL no sintetizable modelando el comportamiento del conversor ADC implementado en el Test bench.....                | 103 |

# 1 Introducción

En este primer apartado de la Memoria Técnica se da una visión general del alcance de este Trabajo Fin de Máster, en el que, conforme se vaya avanzando en el documento, se irá profundizando en más detalle.

En primer lugar se ubica este Trabajo en el contexto actual de los convertidores DC-DC, mostrando las características, retos y el porqué de la utilización del convertidor *Boost* en lugar de un *Buck*, así como el por qué se ha seleccionado un control digital en lugar de un control analógico.

En segundo lugar, se detallan los objetivos parciales o hitos a alcanzar, los cuales delimitan el alcance del Trabajo. La consecución de estos hitos implica, en mayor o menor medida, el éxito del Trabajo Fin de Máster.

Posteriormente, en el tercer apartado, se describe el funcionamiento del sistema completo, mostrando el diagrama de bloques equivalente y enumerando las especificaciones iniciales de diseño que debe cumplir el sistema.

Por último, con el fin de facilitar la lectura del documento, se presenta la organización de la Memoria Técnica, incluyendo un breve resumen del contenido de cada uno de los apartados de los que consta el presente documento.

## 1.1 Antecedentes

En el mundo actual es muy habitual el uso de etapas de Electrónica de Potencia para la mejora de la eficiencia en la transferencia de energía tanto en corriente alterna como en corriente continua.

Los convertidores DC/DC son etapas de Electrónica de Potencia que adaptan una tensión continua en la entrada en una tensión continua distinta en la salida. Estos convertidores son utilizados como fuentes de alimentación para una gran variedad de aplicaciones. Básicamente hay dos tipos de convertidores DC/DC estándar, el *Buck* o *reductor*, el cual disminuye la tensión y el *Boost* o *elevador*, el cual aumenta la tensión, para una fuente de tensión continua de entrada.

En este caso el convertidor analizado es el convertidor *Boost*. Este tipo de convertidor está experimentando un crecimiento en aplicaciones para energías renovables y transferencia de energía en continua, más concretamente en dispositivos de corriente continua con niveles de tensión bajos (paneles fotovoltaicos, baterías...) y que es necesario aumentar la tensión para el transporte y transferencia de energía [1],[2].

Por tanto, los profesores de la asignatura “Control digital de etapas electrónicas de potencia” del Máster de Ingeniería Electrónica de Zaragoza, decidieron proponer el diseño y fabricación de una placa con convertidor *Boost* para que los estudiantes pudieran probar diferentes controles digitales en el laboratorio, al estilo de la placa tipo *Buck* que se utilizaba actualmente.

La dificultad añadida del *Boost* frente al *Buck*, es que su función de transferencia tiene un cero en el semiplano derecho, lo que lo hace más difícil de controlar [3],[4]. Otra dificultad añadida es que el ciclo de trabajo no es lineal como en el caso del *Buck*:

- Ciclo de trabajo del convertidor *Buck*  $\rightarrow D = \frac{V_o}{V_i}$

- Ciclo de trabajo del convertidor *Boost*  $\rightarrow D = \frac{V_o - V_i}{V_o}$

Entre las ventajas de realizar un control digital en lugar de un control analógico, se pueden señalar las siguientes:

- Posibilidad de realizar tareas más complejas.

- Facilidad de integración en un sistema mayor.

- Posibilidad de reprogramación.

- Disminución de la sensibilidad a cambios (derivas térmicas y envejecimiento).

- Menor tiempo de diseño.

- Mayor fiabilidad.

- Reproducibilidad.

## 1.2 Objetivos y alcance

El objetivo del Trabajo Fin de Master, es el diseño, fabricación y validación de una plataforma Hardware de desarrollo, más concretamente un convertidor elevador *Boost*. Esta plataforma Hardware es de baja potencia, y está orientada a la enseñanza como material didáctico para prácticas de Grado o de Máster, y así, poder estudiar el comportamiento de este tipo de convertidores. El objetivo es que mediante este prototipo del convertidor se puedan desarrollar y probar multitud de controles digitales diseñados por los alumnos.

Para completar el trabajo y realizar la validación del convertidor, se ha implementado el control digital en una FPGA y se ha validado su funcionamiento mediante simulación y tomando medidas experimentales.

Para alcanzar el objetivo final hay que cumplir una serie de objetivos parciales o hitos, cada uno de ellos asociado a cada una de las fases de desarrollo del presente Trabajo:

- El **primer objetivo parcial** es el diseño eléctrico y físico del convertidor *Boost* de pequeña potencia y tamaño reducido. Incluyendo la selección de componentes adecuados y el diseño de la placa de circuito impreso.

- El **segundo objetivo parcial** es el estudio, selección y validación del regulador que cumpla con las especificaciones iniciales de diseño y que mejor comportamiento tenga frente a una serie de funciones de mérito.

- El **tercer objetivo parcial** consiste en la implementación en VHDL sintetizable del control digital en la FPGA y validación mediante simulación.

- El **cuarto objetivo parcial** consiste en la validación total del sistema mediante medidas y resultados experimentales, mediante las cuales se puedan extraer las conclusiones y líneas de trabajo futuras.

El cumplimiento satisfactorio de los cuatro objetivos parciales o hitos enumerados anteriormente, implica la consecución del Trabajo.

### 1.3 Descripción del sistema y especificaciones de diseño

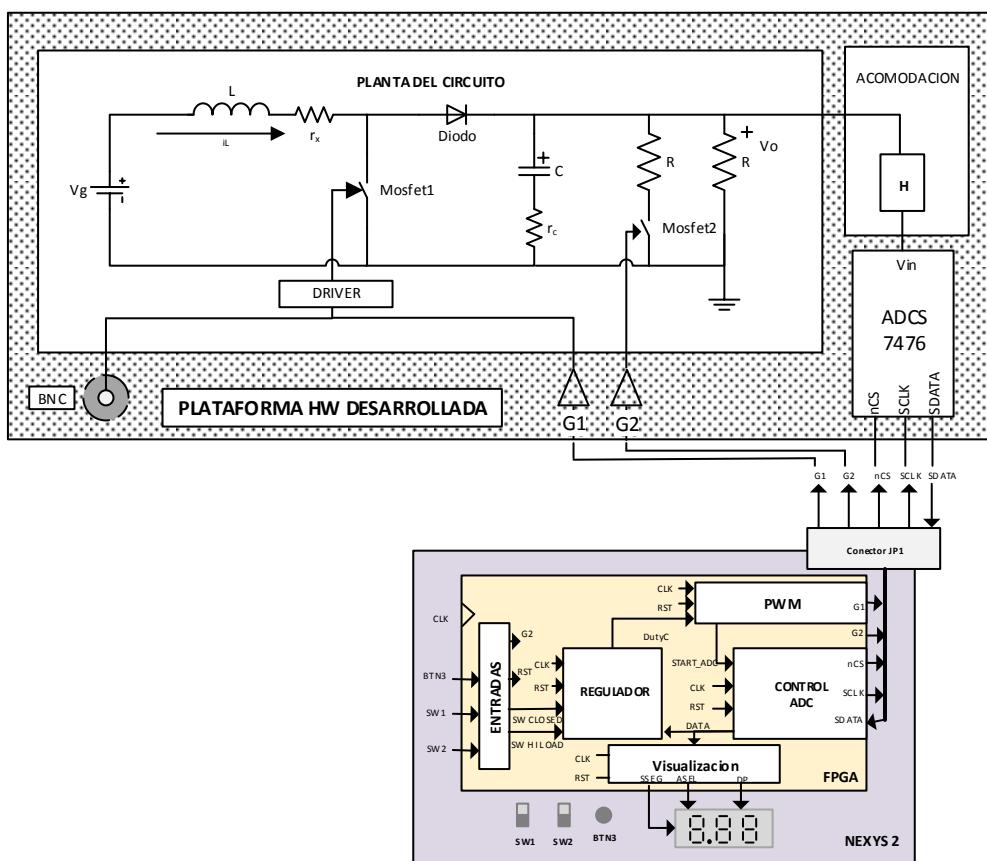

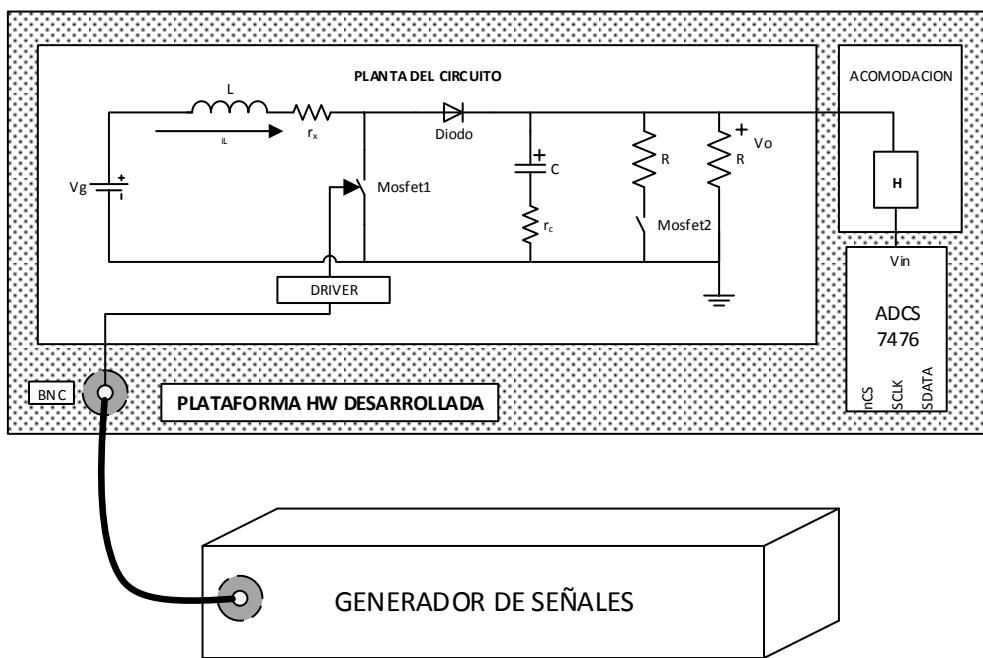

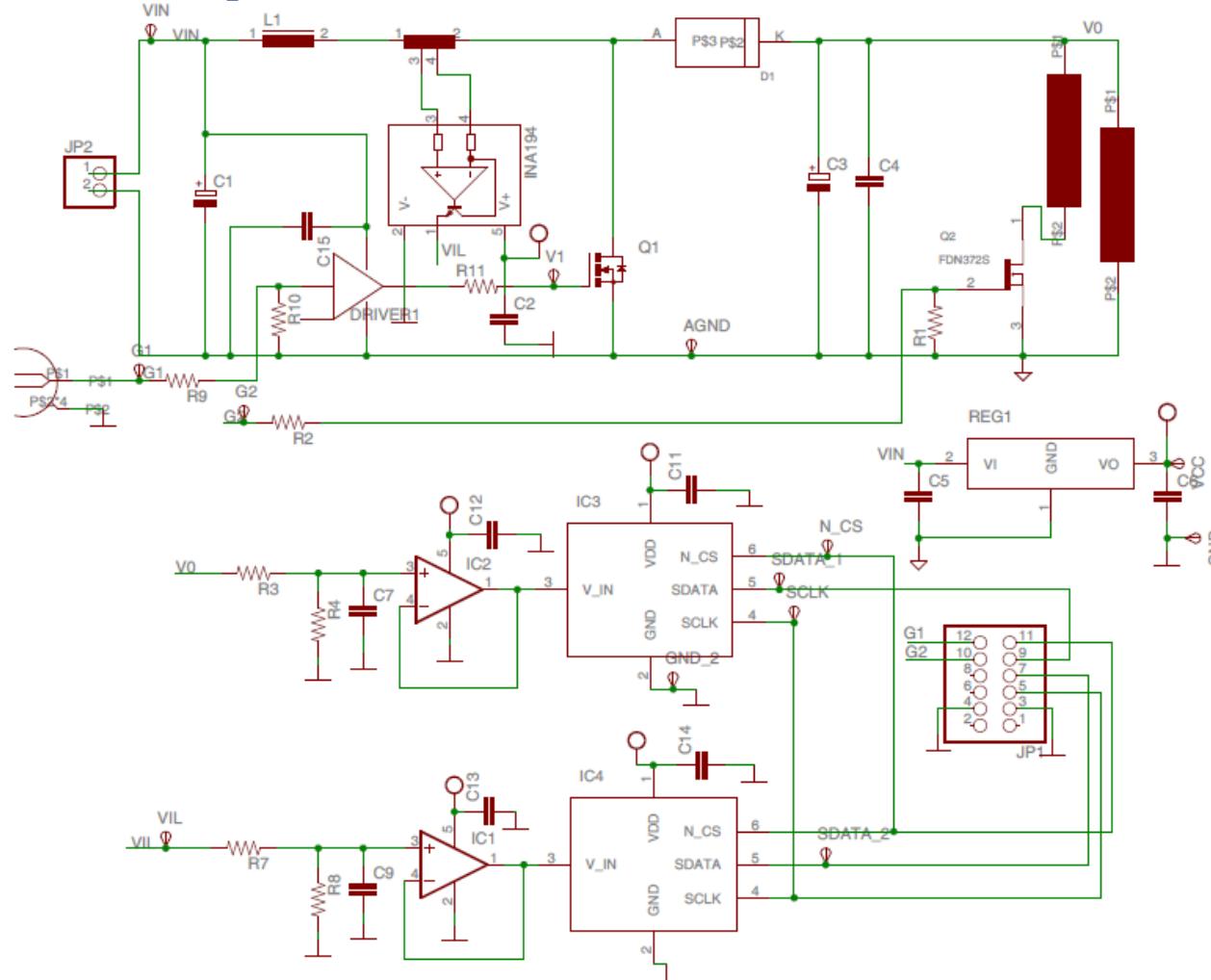

A continuación se muestra el esquema general, con cada uno de los bloques que componen el sistema completo, los cuales pueden apreciarse en la Fig. 1.

Fig. 1 Esquema general del sistema completo

Como se observa en la Fig. 1 existen dos sistemas bien diferenciados: la plataforma HW desarrollada y la tarjeta Nexys 2 de Diligent. Ambos sistemas comparten señales mediante el conector JP1.

La plataforma HW posee etapa de sensado de la corriente por la bobina, para permitir el control por corriente y de la tensión en la carga, para hacer control por tensión.

En la Fig. 2 se muestra el esquema que se ha utilizado para realizar el control por tensión y que ha sido validado experimentalmente.

Fig. 2 Esquema del sistema utilizado para realizar el control por tensión en la carga

Como se ha comentado anteriormente, se observan 2 bloques claramente diferenciados:

- **Plataforma HW desarrollada**, que consiste en la placa de circuito impreso que se ha diseñado y fabricado para este Trabajo Fin de Máster y que consta de 3 bloques:

- Convertidor Boost, o planta del circuito, con la topología característica del circuito electrónico del convertidor.

- Circuito de acondicionamiento, el cual realiza la adaptación de la tensión de salida a la tensión a la entrada del conversor analógico digital.

- Conversor analógico digital ADCS 7476, el cual transforma la tensión analógica a la entrada del conversor en una palabra digital de  $n$  bits que son enviados vía serie a la FPGA mediante la señal SDATA.

- **Plataforma Nexys 2** de Diligent, en la que hay una FPGA sobre la que se implementa el control digital. Esta plataforma posee una serie de pulsadores, interruptores y visualizadores sobre los que se actúa y que dota al sistema de funcionalidades adicionales. En esta plataforma se implementa el control digital del circuito, generando las siguientes señales:

- Señales  $nCS$  y  $SCLK$ , necesarias para realizar el protocolo de comunicaciones con el conversor analógico digital.

- Señal de disparo  $G1$ , encargada de disparar, mediante la señal PWM generada en la FPGA, el transistor del convertidor Boost, Mosfet1.

- Señal de disparo  $G2$ , encargada de disparar el Mosfet2, lo cual provoca una variación sobre la carga, y de esta forma, poder analizar la variación de la tensión de salida y el tiempo de respuesta del sistema.

Para la realización del diseño del convertidor y la selección de sus componentes, este Trabajo Fin de Master se ha basado en las especificaciones iniciales de diseño que aparecen en [5], éstas son:

- Tensión de entrada:  $V_g=5$  V

- Tensión de salida:  $V_o=12$  V

- Potencia en la carga:  $P_{out}=6$  W

- Frecuencia de conmutación:  $f_{sw}= 100$  kHz

En la Fig. 3 se muestran los bloques necesarios para la realización del control de tensión en la carga.

Fig. 3 Diagrama de bloques del sistema

El funcionamiento del sistema es el que se muestra a continuación:

1. Se alimenta la planta del sistema con una fuente de tensión  $Vg$  de 5 V

2. Se obtiene una tensión continua en la carga  $V_o$

3. Se realiza el acondicionamiento de la tensión obteniendo una tensión apta para el ADC.  $V_o'$

4. El conversor ADC proporciona una señal digital de 8 bits **DATA** proporcional a la tensión a su entrada.

5. El vector de 8 bits proporcionado por el conversor **DATA** se compara con un valor de referencia,  $V_{ref}$  que da como resultado el  $V_{error}$ .

6. A partir de este error, en el regulador se realizan una serie de operaciones que llevan al cálculo del nuevo ciclo de trabajo o **Duty**.

7. Se genera la señal PWM **G1**, que es aplicada a la puerta del Mosfet y que controla su conmutación.

## 1.4 Organización de la Memoria Técnica

El presente documento se divide en 5 capítulos, a continuación, con el fin de facilitar la lectura, se incluye un breve resumen de cada uno de ellos:

- **Capítulo 1: Introducción**, en este primer capítulo se describen los antecedentes de este TFM, los objetivos y alcance del proyecto, así como la descripción del sistema, con su diagrama de bloques y las especificaciones iniciales de diseño del convertidor.

- **Capítulo 2: Diseño y modelado del convertidor Boost**, en este capítulo se detalla el proceso de modelado y diseño del prototipo del convertidor Boost. Se obtiene la función de transferencia del convertidor y se indican los cálculos realizados para seleccionar la bobina, el condensador y la resistencia de carga del convertidor.

- **Capítulo 3: Diseño de la Plataforma Hardware desarrollada**, en este capítulo se muestra la placa de circuito impreso fabricada y los cálculos realizados para la obtención del resto de componentes.

- **Capítulo 4: Diseño del control digital**, en este capítulo se muestran los 5 reguladores calculados con la misma topología de 2 ceros y 2 polos, se selecciona el mejor de todos ellos comparando los resultados obtenidos ante una serie de funciones de mérito y se valida mediante simulación en Matlab.

- **Capítulo 5: Implementación del control digital**, en este capítulo se muestra el código implementado en la FPGA para realizar el control digital, centrándose especialmente en la implementación del regulador calculado en el capítulo 4. Primero se hace la implementación y validación en números reales y posteriormente en coma fija.

- **Capítulo 6: Resultados experimentales**, en este capítulo se muestra, por una parte, cómo se ha configurado la tarjeta Nexys2 para poder hacer ensayos y por otra parte, las medidas obtenidas con un osciloscopio en el laboratorio.

- **Capítulo 7: Conclusiones y líneas de trabajo futuras**, en este apartado se muestran las conclusiones obtenidas a partir de los resultados experimentales, indicando si se han cumplido los objetivos parciales o hitos que delimitan el alcance del Trabajo Fin de Máster. Por otro lado, en este mismo apartado, se proponen una serie de trabajos interesantes de realizar en el futuro y en el ámbito del presente Trabajo Fin de Máster.

Por último, al final de la Memoria, hay un apartado de Anexos en el que se incluyen desarrollos, planos, cálculos, código en VHDL... que sirven de apoyo a los distintos apartados de la Memoria.

## 2 Diseño y modelado del convertidor Boost

En este capítulo se detalla el proceso de modelado y diseño del prototipo del convertidor Boost.

El convertidor Boost tiene la característica principal de que la tensión continua de salida que se obtiene es mayor que la tensión a la entrada. Mediante la conmutación del transistor Mosfet se consigue regular esa tensión de salida, generando flujos de energía entre la bobina y el condensador.

Inicialmente se ha realizado un análisis teórico del comportamiento del convertidor frente a variaciones de pequeña señal. Este análisis se ha desarrollado con el fin de seleccionar los componentes (bobina, condensador y resistencias) que mejor se adapten a las especificaciones iniciales y que a su vez faciliten la implementación del regulador en la FPGA.

### 2.1 Análisis teórico del modelo de pequeña señal en modo de conducción continua

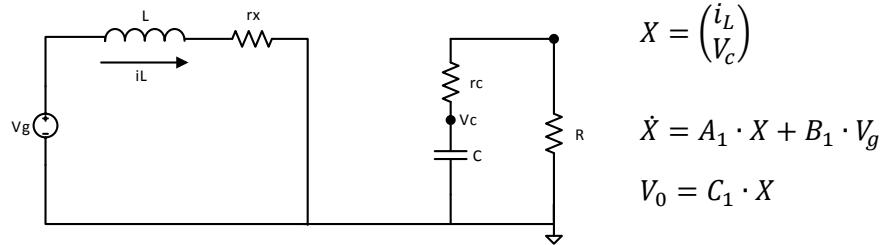

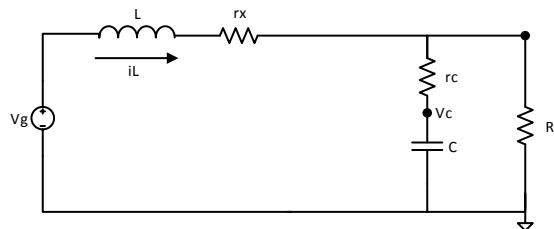

El circuito electrónico del convertidor Boost es el que se muestra en la Fig. 4, en él aparecen los componentes electrónicos típicos del convertidor Boost con los componentes parásitos más relevantes:

|                                            |

|--------------------------------------------|

| V <sub>g</sub> - Tensión de entrada (+5V)  |

| L - Inductancia de la bobina               |

| rx - Resistencia equivalente de la bobina  |

| i <sub>L</sub> – Corriente por la bobina   |

| Transistor Mosfet                          |

| Diodo de potencia                          |

| C - Condensador                            |

| rc - Resistencia del condensador           |

| V <sub>c</sub> – Tensión en el condensador |

| R - Carga a la salida del Boost            |

| V <sub>o</sub> – Tensión a la salida       |

Fig. 4 Circuito electrónico del convertidor Boost

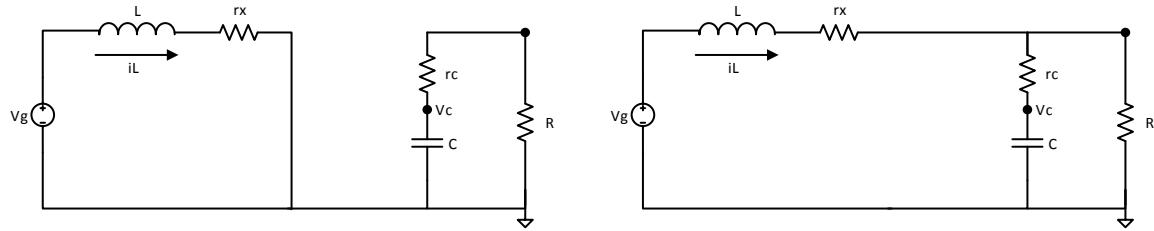

Dependiendo del estado del Mosfet, y por tanto de la señal PWM generada en la FPGA, se pueden generar dos circuitos equivalentes Fig. 5:

Estado 1: Mosfet ON (en conducción)

Estado 2: Mosfet OFF (en corte)

Fig. 5 Circuito equivalente del convertidor en función del estado del Mosfet

La ecuación general de la función de transferencia de pequeña señal del convertidor Boost en función del ciclo de trabajo o duty, desarrollada en [6], es la que se muestra a continuación:

$$G_{vd}(s) = \left. \frac{\hat{v}_o(s)}{\hat{d}(s)} \right| = C(sI - A)^{-1} [(A_1 - A_2) + (B_1 - B_2)V_g] + (C_1 - C_2)X \quad (1)$$

En el **ANEXO A**, se ha desarrollado la ecuación anterior (1), de allí se obtiene la siguiente función de transferencia:

$$G_{vd}(s) = \left. \frac{\hat{v}_o(s)}{\hat{d}(s)} \right| = \frac{K(-s^2 + \alpha_1 s + \alpha_0)}{s^2 + b_1 s + b_0}$$

Siendo,

$$\begin{aligned} K &= \frac{RV_g r_c}{D_1 R(D_1 R + r_c) + r_x(R + r_c)} \\ \alpha_1 &= \frac{D_1^2 R^2 r_c C - L(R + r_c) - C r_c r_x(R + r_c)}{L C r_c (R + r_c)} \quad (2) \\ \alpha_0 &= \frac{D_1^2 R^2 - r_x(R + r_c)}{L C r_c (R + r_c)} \\ b_1 &= \frac{1}{C(R + r_c)} + \frac{r_x + D_1 R r_c}{L(R + r_c)} \\ b_0 &= \frac{r_x(R + r_c) + D_1 R(D_1 R + r_c)}{L C(R + r_c)^2} \end{aligned}$$

$$D_1 = 1 - D$$

La función de transferencia resultante de la planta es un sistema de segundo orden, con un polo doble en  $f_0$  (3), un cero en  $f_{ESR}$  debido a la resistencia *ESR* del condensador (4) y un cero en el semiplano derecho a la frecuencia  $f_{RHP}$  (5).

$$f_0 = \frac{\sqrt{r_x(R + r_c) + D_1 R (D_1 R + r_c)}}{2\pi\sqrt{LC}(R + r_c)} \quad (3)$$

$$f_{ESR} = \frac{1}{2\pi(R + r_c)} \quad (4)$$

$$f_{RHP} = \frac{1}{2\pi} \left( \frac{D_1^2 R^2}{L(R + r_c)} + \frac{r_x}{L} \right) \quad (5)$$

## 2.2 Selección de los componentes del convertidor

Las especificaciones iniciales mostradas en el capítulo 1, imponen unos componentes y unos límites determinados.

La potencia en la carga, según las especificaciones es de 6 W, y la tensión es de 12 V, por tanto, el valor de la carga R es de:

$$R = \frac{V_0^2}{P_{out}} = \frac{144}{6} = 24 \Omega \quad (6)$$

De la misma forma, la corriente por la carga  $I_0$  es igual a:

$$I_0 = \frac{P_{out}}{V_0} = \frac{6}{12} = 0,5 A \quad (7)$$

La corriente media por la bobina en régimen permanente es aproximadamente (despreciando pérdidas) de:

$$I_{Lmin} = \frac{P_{in}}{V_{in}} = \frac{6 \text{ watos}}{5 \text{ voltios}} = 1,2 A \quad (8)$$

La tensión en la entrada es de 5 V, por lo que el duty nominal  $D$  y su complementario  $D1$  son:

$$D = \frac{V_0 - V_g}{V_0} = \frac{7}{12} \quad (9)$$

$$D1 = 1 - D = \frac{5}{12}$$

A continuación se detalla el proceso de selección de los valores del condensador  $C$  y de la inductancia  $L$  adecuados, colocando los polos y los ceros de la planta estratégicamente, para que, cumpliendo con las especificaciones iniciales, la planta del sistema sea lo más estable posible y de este modo la implementación del control sea más sencilla.

La hoja de aplicación de Texas Instruments [7] advierte la necesidad de que la frecuencia del cero  $f_{RHP}$  sea mucho mayor que la frecuencia del doble polo  $f_0$ , ya que si no se reducirían las condiciones de estabilidad. Por ello se ha establecido que este factor sea igual a 15:

$$\frac{w_{RHP}}{w_0} \geq M, \text{ siendo } M=15 \quad (10)$$

Seleccionando la frecuencia del cero 10 o 20 veces menor que la frecuencia de conmutación, se obtiene una  $f_{RHP}$  y un  $f_0$ :

$$\begin{aligned} f_{RHP} &= \frac{f_{sw}}{10 \text{ ó } 20} = \frac{100000}{10 \text{ ó } 20} \approx 7.500 \text{ Hz} \\ \frac{f_{RHP}}{f_0} &\geq 15 \rightarrow f_0 \leq \frac{7500}{15} = 500 \text{ Hz} \end{aligned} \quad (11)$$

La imposición de  $f_{RHP} \sim 7.500 \text{ Hz}$  y sustituyendo en (5) nos da el valor de la inductancia, (para ello se ha seleccionado unos valores típicos de  $r_x=120 \text{ m}\Omega$  y  $r_c=80 \text{ m}\Omega$ ):

$$f_{RHP} = \frac{1}{2\pi} \left( \frac{D_1^2 R^2}{L(R + r_c)} + \frac{r_x}{L} \right) = 7500 \text{ Hz} \quad (12)$$

Despejando en (12), el valor de la inductancia es:

$$L = \frac{\frac{D_1^2 R^2 + r_x(R + r_c)}{R + r_c}}{2\pi f_{RHP}} = 90,67 \mu\text{H} \quad (13)$$

Para asegurar la conducción continua por el circuito, el valor de la inductancia debe superior a:

$$L_{min} > \frac{V_g D}{2I_{min} f_{sw}} > \frac{5 * \frac{7}{12}}{2 * 1,2 * 100000} > 12 \mu\text{H} \quad (14)$$

Por lo que la inductancia calculada en (13) sería válida. En este caso seleccionamos el valor de inductancia comercial que más se aproxime a ese valor, en este caso se ha seleccionado una inductancia con un valor de  $100 \mu\text{H}$ .

Con este valor de inductancia la frecuencia del cero  $f_{RHP}$  es:

$$f_{RHP} = \frac{1}{2\pi} \left( \frac{D_1^2 R^2}{L(R + r_c)} + \frac{r_x}{L} \right) = 6800 \text{ Hz} \quad (15)$$

Con el valor de la inductancia seleccionada ( $100 \mu\text{H}$ ) y la imposición  $\frac{f_{RHP}}{f_0} \geq 15$  (11), se calcula el valor del condensador:

$$f_0 = \frac{f_{z2}}{15} = 453,333 \text{ Hz} \quad (16)$$

$$C = \frac{r_x(R + r_c) + D_1 R (D_1 R + r_c)}{L(2\pi f_0)^2 (R + r_c)^2} = 220 \mu\text{F} \quad (17)$$

En este caso sí que hay condensadores comerciales con este valor.

La función de transferencia resultante de la planta tiene dos ceros y dos polos complejos conjugados, tal y como se muestra a continuación en (18):

$$G_p(s) = -0,092584 \frac{(s + 5,682 \cdot 10^4) \cdot (s - 4,033 \cdot 10^4)}{s^2 + 1721s + 8,128 \cdot 10^6} \quad (18)$$

De donde se obtiene:

- El valor de la frecuencia del cero RHP  $\rightarrow f_{RHP} = 6,4 \text{ kHz}$

- El valor de la frecuencia del cero debido a la resistencia  $ESR$  del condensador  $\rightarrow f_{ESR} = 9 \text{ kHz}$

- El valor de la frecuencia natural del doble polo es de  $\rightarrow f_n = 453 \text{ Hz}$

- El valor del coeficiente de amortiguamiento del doble polo  $\rightarrow \zeta = 0,3$

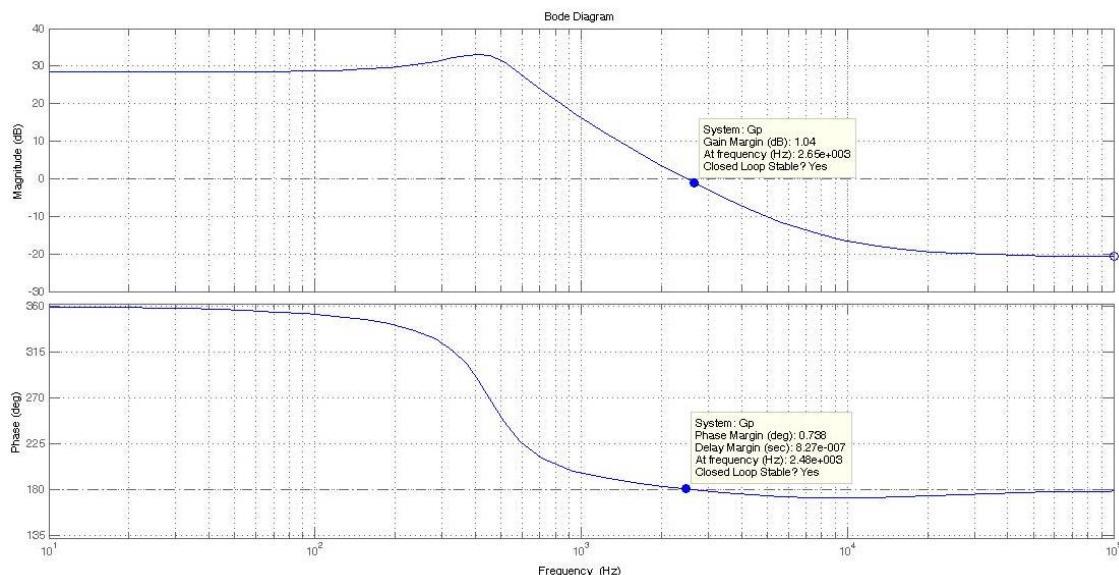

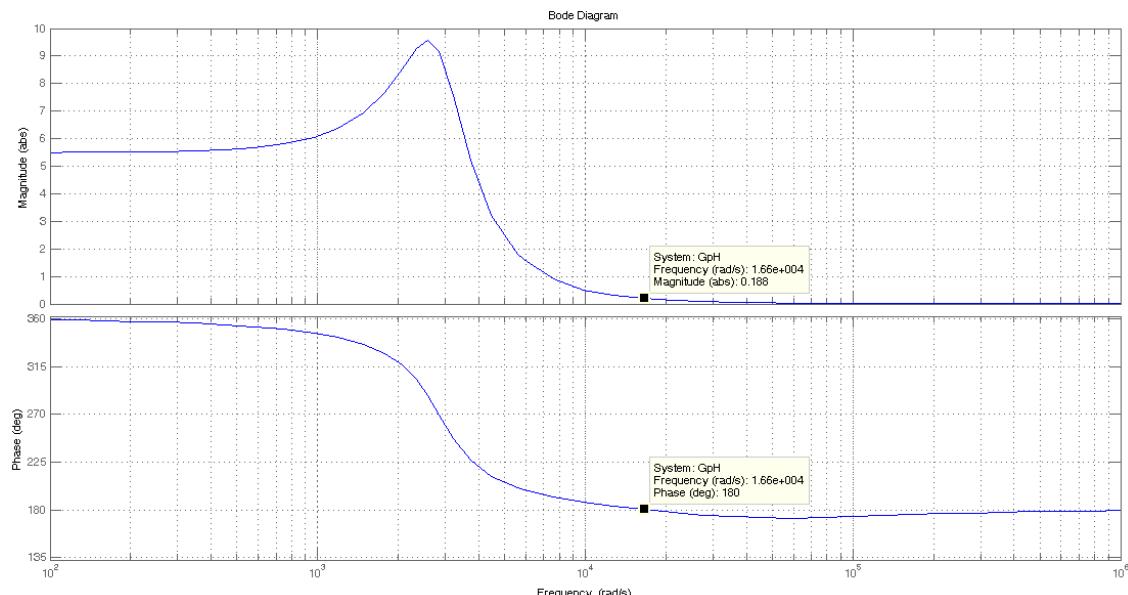

El diagrama de Bode correspondiente se muestra en la Fig. 6:

Fig. 6 Diagrama de bode de la planta  $G_p$

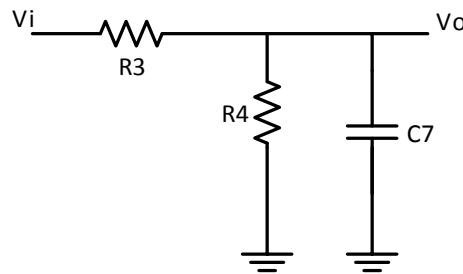

### Cálculo del circuito de acondicionamiento H:

A continuación se muestra cómo se ha calculado el circuito de acondicionamiento H, necesario para adaptar la tensión de salida del circuito a la tensión de entrada al conversor analógico digital.

El circuito es un filtro paso bajo de primer orden atenuador cuyos requisitos son los impuestos en [6]  $V_{REF} \geq 70\%$  del fondo de escala y [8]  $f_c = 50 \text{ kHz}$ .

#### Requisitos:

- Ganancia=2.5/12

- Frecuencia de corte=50kHz

Fig. 7 Circuito equivalente de la etapa de acondicionamiento

La ecuación del circuito de acondicionamiento es:

$$\frac{V_i - V_0}{R_3} = \frac{V_0}{R_4} + \frac{V_0}{1/C_7s} \rightarrow \frac{V_1}{R_3} = \frac{V_0}{R_4} + \frac{V_0}{R_3} + V_0 C_7 s \quad (19)$$

Por tanto,

$$\frac{V_0}{V_i} = \frac{R_3 R_4}{R_3 * (R_3 + R_4 + (R_4 R_3 C_7 s))} = \frac{\frac{R_4}{R_3 + R_4}}{1 + \frac{R_4 R_3}{R_4 + R_3} C_7 s} \quad (20)$$

Los componentes ideales serían:

- **R3=15,3 kΩ**

- **R4=4 kΩ**

- **C7=1 nF**

No hay resistencias de esos valores por lo que las resistencias que más se aproximan son:

Componentes seleccionados:

- **R3=15 kΩ**

- **R4=3,9 kΩ**

- **C7=1 nF**

La frecuencia de corte (50 kHz) no cumple el teorema de muestreo de Nyquist. Como propone [6] y [11] la solución se basa en sincronizar el muestreo del conversor con el periodo de conmutación. El muestreo se lanza por software siempre en el mismo momento de la conmutación, así se evitan problemas de aliasing debido al rizado.

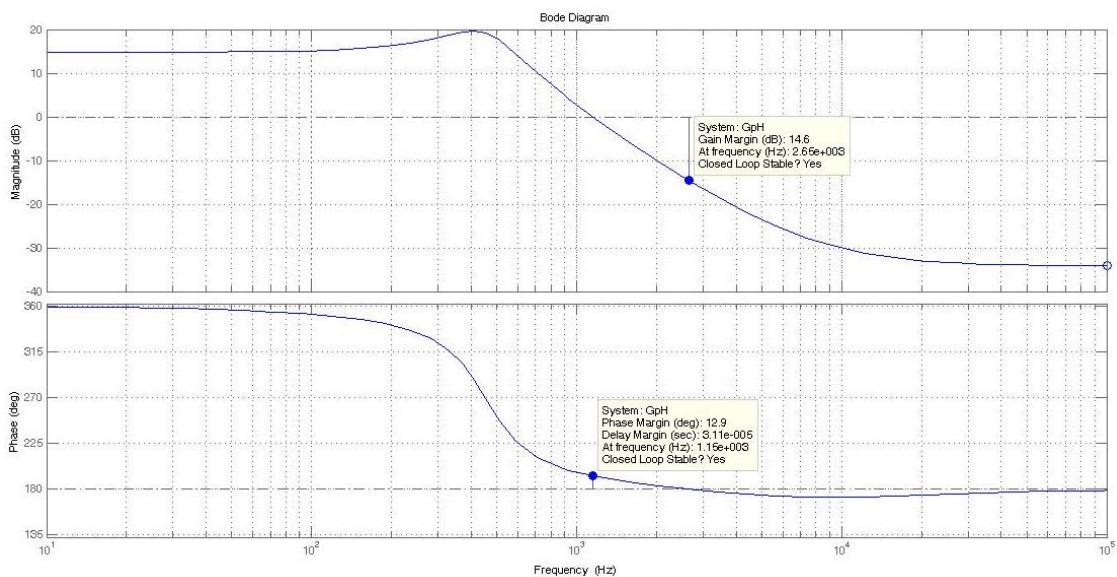

El diagrama de bode equivalente de la planta del circuito con el circuito de acondicionamiento se muestra en la Fig. 8.

Fig. 8 Diagrama de bode de la planta con el bloque de acondicionamiento  $G_p * H$

A continuación se muestran los componentes comerciales seleccionados:

**Bobina:**

La bobina seleccionada es una inductancia de ferrita de COILCRAFT cuyas características son:

- Valor de inductancia  $L=100 \mu\text{H}$

- Resistencia en serie ESR  $r_x=120 \text{ m}\Omega$

- Corriente eficaz nominal  $I_{\text{RMS}}=3\text{A}$ .

A continuación, Fig. 9, se muestran las gráficas de corriente y tensión por la bobina en el caso más desfavorable, carga de  $12 \Omega$ . Como puede observarse, en el régimen permanente no se superan los 3 A eficaces de la bobina seleccionada.

Fig. 9 Gráficas de corriente (A) y tensión (V) en régimen permanente por la bobina en el caso más desfavorable

### Condensador:

El condensador electrolítico seleccionado es uno de PANASONIC cuyas características son:

- Valor de  $C=220 \mu\text{H}$

- Resistencia en serie  $r_c=80 \text{ m}\Omega$

- Tensión nominal de 35 V

A continuación, Fig. 10, se muestran las gráficas de corriente y tensión por el condensador en el caso más desfavorable, carga de  $12 \Omega$ . Como puede observarse, en el régimen permanente no se superan los 35 V nominales del condensador seleccionado.

Fig. 10 Gráficas de corriente (A) y tensión (V) en régimen permanente por el condensador en el caso más desfavorable

### Resistencia de la carga:

Las resistencias seleccionadas son de WELWYN cuyas características son:

- Valor de  $R=24 \Omega$

- Potencia nominal 7 W

A continuación, Fig. 11, se muestran las gráficas de corriente y tensión por la carga.

Fig. 11 Gráficas de corriente (A) y tensión (V) en régimen permanente por la carga

$$P = I_{ef}^2 * R = 0.5^2 * 24 = 6 \text{ W} < 7 \text{ W} \quad (21)$$

Como puede observarse, en régimen permanente no se superan los 7 W nominales de la carga seleccionada.

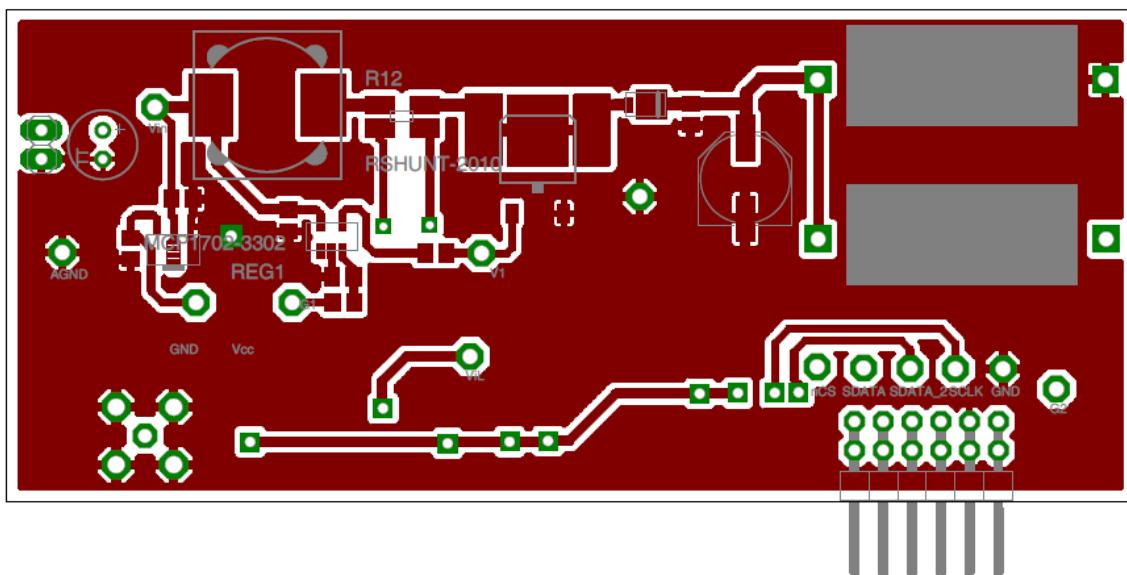

### 3 Diseño de la Plataforma Hardware desarrollada

En este apartado se describen las características de diseño de la plataforma Hardware desarrollada y la selección del resto de componentes que la componen.

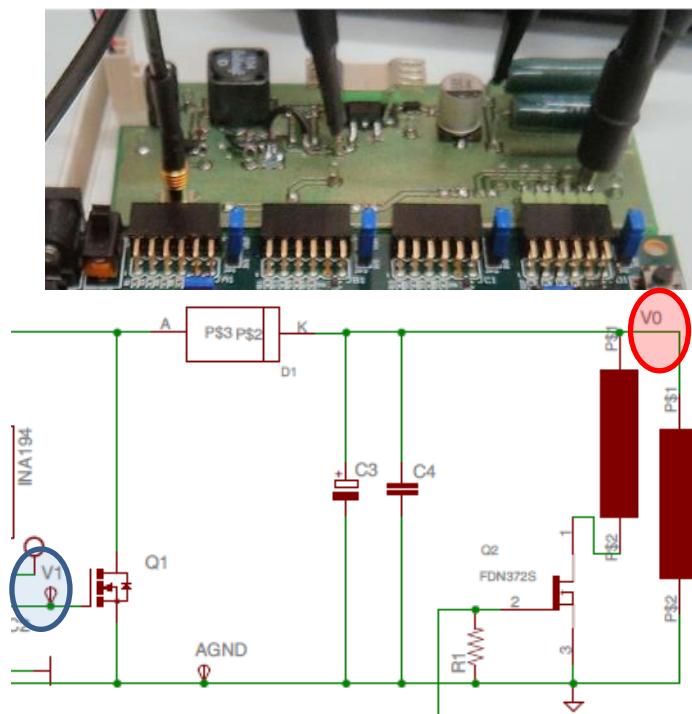

Teniendo en cuenta que esta plataforma se encuentra conectada a la tarjeta Nexys2 de Diligent, se ha buscado el conector específico PMOD para su conexión; por otra parte, se ha optimizado su diseño, de forma que la placa de circuito impreso sea de tamaño reducido. El resultado final es el que se observa en la Fig. 12.

Fig. 12 Fotografía de la plataforma Hardware desarrollada conectada a la tarjeta NEXYS 2

El diseño de la placa de circuito impreso se ha realizado con el software de diseño electrónico EAGLE. Se ha puesto un esfuerzo inicial en su diseño, ya que si se realiza de forma incorrecta, la PCB puede irradiar excesivo ruido electromagnético (EMI), el cual puede contribuir a la inestabilidad del circuito.

Los convertidores conmutados de continua contienen señales de alta frecuencia, debido a las conmutaciones de sus interruptores. Cualquier pista de la PCB puede actuar como una antena receptora e introducir ruido en el funcionamiento del circuito. La longitud y la anchura de la pista están directamente relacionadas con su inductancia y resistencia, y por lo tanto de su sensibilidad al ruido. La longitud de una pista es directamente proporcional a la resistencia e impedancia de la misma y la anchura es inversamente proporcional a la resistencia.

Las pistas de la etapa de potencia se han hecho anchas y cortas. Anchas, para que su resistencia sea pequeña y puedan disipar la potencia adecuada para que no se calienten en exceso. Cortas, para que la inductancia añadida sea pequeña.

Por este motivo, el diseño se ha dividido en dos partes:

- Por la cara TOP se han colocado los componentes de potencia.

- Por la cara BOTTOM se han colocado los componentes de control, los conversores analógico digitales y los amplificadores operacionales.

De esta forma el ruido producido por los componentes de potencia no afecta a la parte de control y medida. De la misma manera, se ha dejado la parte superior de la cara BOTTOM sin componentes, como plano de masa, para facilitar el camino de vuelta de la corriente por la GND de la fuente, tal y como se observa en la Fig. 13.

Fig. 13 Fotografía de la cara BOTTOM de la plataforma HW desarrollada

Con el fin de desarrollar una plataforma HW para uso didáctico, se han colocado en la PCB una serie de anillas de test sobre las que se puede pinchar con la sonda del osciloscopio y realizar las medidas correspondientes, como se muestra en la Fig. 14.

Fig. 14 Fotografía de la cara TOP de la plataforma HW desarrollada

En el **ANEXO B**, se muestran los planos de la PCB obtenidos con Eagle.

### 3.1 Selección del resto de componentes

Además de la inductancia, el condensador y las resistencias seleccionadas en el capítulo anterior, se ha realizado el cálculo del resto de los componentes que componen la tarjeta de circuito impreso.

#### Transistor Mosfet:

Se ha seleccionado un MOSFET IRFR024NPBF de canal N, cuyas características son:

- Intensidad máxima  $Id=16$  A.

- Tensión drenaje-fuente  $Vds=55$  V.

- Disipación de potencia  $Pd=38$  W.

A continuación, Fig. 15, se muestran las gráficas de corriente y tensión por el transistor Mosfet en el caso más desfavorable, carga de  $12\ \Omega$ . Como puede observarse, en el régimen permanente los valores máximos de corriente y tensión están por debajo de los límites del transistor seleccionado.

Fig. 15 Gráficas de corriente (A) y tensión (V) en régimen permanente por el transistor Mosfet en el caso más desfavorable

#### Diodo de Potencia:

El diodo seleccionado es el SS2P3L de Vishay, cuyas características son:

- Intensidad directa  $I_f(AV)$  2 A.

- Intensidad directa transitoria 60 A.

- Tensión inversa 30V.

A continuación, Fig. 16, se muestran las gráficas de corriente y tensión por el diodo en el caso más desfavorable, carga de  $12 \Omega$ . Como puede observarse, en el régimen permanente el valor medio de corriente está por debajo de los 2 A nominales y la tensión inversa es menor a los 30 V.

Fig. 16 Gráficas de corriente (A) y tensión (V) en régimen permanente por el diodo en el caso más desfavorable

#### Driver del Mosfet:

El driver seleccionado es el UCC27517ADBVT de Texas Instruments, con las siguientes características:

- Un único canal de alta velocidad

- Alimentación entre 4.5 y 18 Voltios

- Disparo compatible con señales TTL

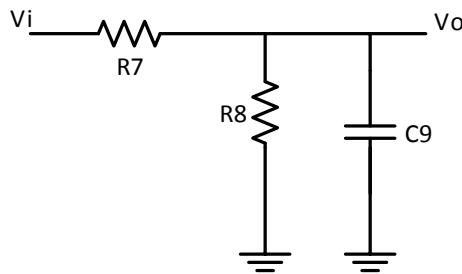

#### Círculo de acondicionamiento de la medida en corriente:

De la misma manera que se ha calculado el filtro paso bajo de primer orden para el acondicionamiento de la tensión de salida, se calcula el mismo filtro paso bajo atenuador para la corriente por la bobina.

Para convertir la corriente en tensión se ha utilizado un INA194 que tiene una ganancia de 50 y una resistencia shunt de valor  $R_{shunt}=0.039 \Omega$ .

Esto implica que si, por ejemplo, circulan 2.5 A por la bobina (corriente aproximada cuando la Resistencia de carga es  $12 \Omega$ ) la salida en tensión es de 4.875 V.

Para que la tensión de entrada al conversor ADC sea de 2.5 hay que dividir por 2, por lo que la ganancia del circuito es de 0.5. Con esta etapa de acondicionamiento, el rango de medida va desde 0 a 3.4 A.

#### Los requisitos son:

- Ganancia=0,5

- Frecuencia de corte=50 kHz

Fig. 17 Circuito equivalente de la etapa de acondicionamiento

Las ecuaciones del circuito de acondicionamiento son:

$$\frac{V_i - V_0}{R_7} = \frac{V_0}{R_8} + \frac{V_0}{1/C_9s} \rightarrow \frac{V_1}{R_7} = \frac{V_0}{R_8} + \frac{V_0}{R_7} + V_0 C_9 s \quad (22)$$

Por tanto,

$$\frac{V_0}{V_i} = \frac{R_7 R_8}{R_7 * (R_7 + R_8 + (R_8 R_7 C_9 s))} = \frac{\frac{R_8}{R_7 + R_8}}{1 + \frac{R_8 R_7}{R_8 + R_7} C_9 s} \quad (23)$$

Los componentes ideales serían:

- **R7=6,34 kΩ**

- **R8=6,34 kΩ**

- **C9=1 nF**

No hay resistencias de esos valores por lo que las resistencias que más se aproximan son:

Componentes seleccionados:

- **R7=6,2 kΩ**

- **R8=6,2 kΩ**

- **C9=1 nF**

En el **ANEXO C**, se muestra el listado de componentes completo.

## 4 Diseño del control digital

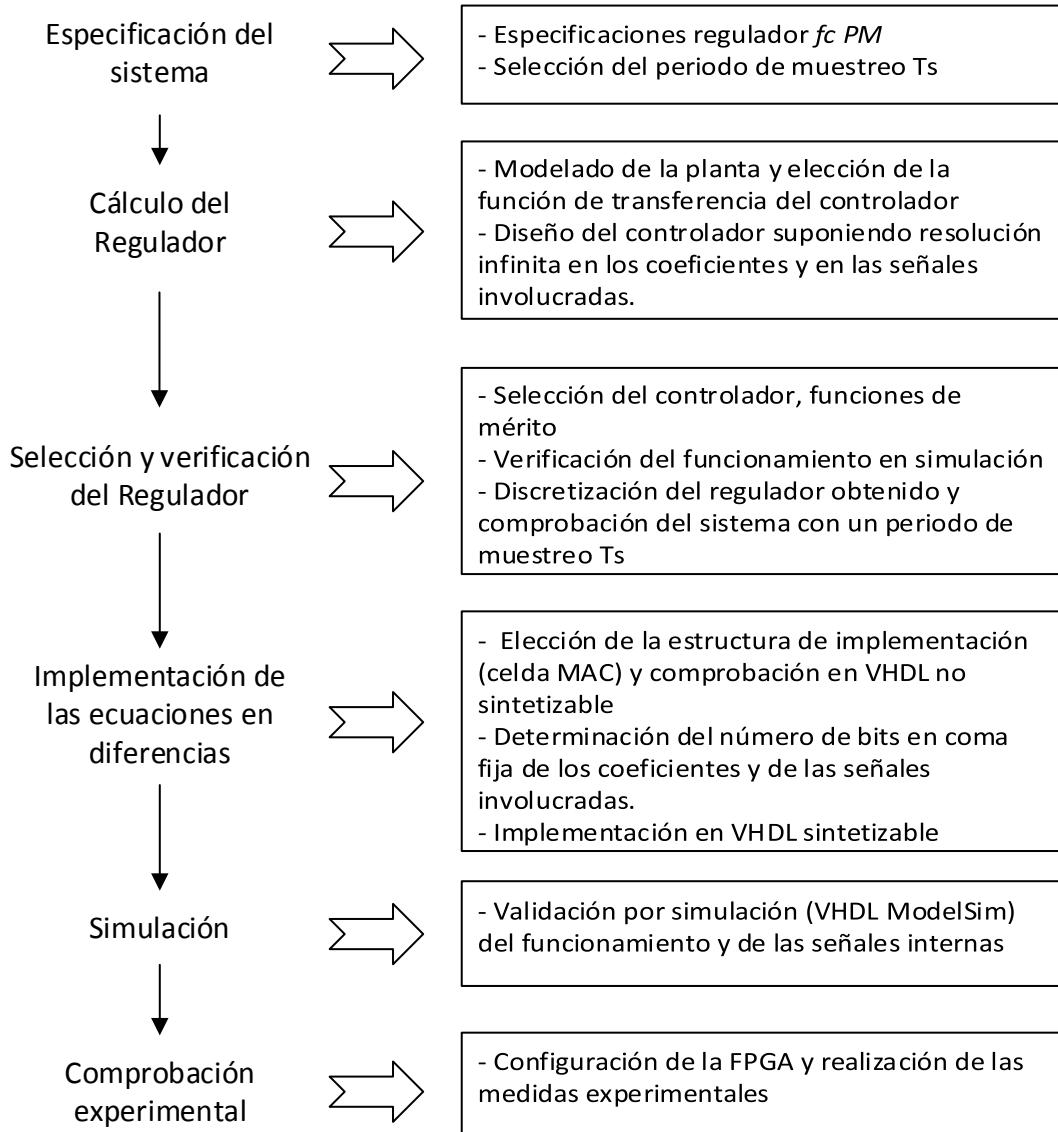

Este apartado describe el cálculo, selección y verificación del regulador implementado en la FPGA. Como se muestra en [12] los pasos a seguir para realizar el diseño de un regulador digital son los siguientes:

Fig. 18 Pasos seguidos para la realización y comprobación del regulador digital implementado

El primer paso de los arriba indicados, es analizar e imponer las especificaciones requeridas por el sistema. A partir de estas especificaciones iniciales de diseño se calcula el regulador.

Según [13], uno de los problemas del control del convertidor Boost es debido al cero  $f_{RHP}$  en el semiplano derecho, que provoca una respuesta inicial en el convertidor en la dirección opuesta a la ordenada por la señal de control, también conocido como realimentación positiva. Por ejemplo, si hay un aumento repentino de la carga de salida en el convertidor, su voltaje de salida

disminuirá y el convertidor responderá con un ciclo de trabajo más largo. Sin embargo, un ciclo de trabajo más largo, dará como resultado un tiempo de conducción del diodo más corto, y por tanto, una menor carga del condensador de salida, probocando inicialmente una mayor caída del voltaje.

Esto es confuso para el controlador, la solución es esperar y ver la tendencia del circuito antes de ajustar el ciclo de trabajo. Con el fin de lograr este objetivo, la frecuencia de corte,  $f_c$ , debe ser inferior a la frecuencia cero RHP y mayor a la frecuencia del polo doble  $f_o$ .

Se han seleccionado las siguientes condiciones: la frecuencia de corte  $f_c$  debe ser al menos 3 veces menor a la frecuencia del cero RHP y 3 veces mayor a la frecuencia del polo doble  $f_o$ .

$$\begin{aligned} f_c &< \frac{f_{RHP}}{3} \\ f_c &> 3 \cdot f_o \end{aligned} \tag{24}$$

Siendo la frecuencia del cero RHP:

$$f_{RHP} = \frac{1}{2\pi} \left( \frac{D_1^2 R^2}{L(R + r_c)} + \frac{r_x}{L} \right) = 6800 \text{ Hz} \tag{25}$$

Y la del polo doble:

$$f_o = \frac{f_{zz}}{15} = 453,333 \text{ Hz} \tag{26}$$

Nos da como resultado una frecuencia de corte aproximada de 1,5 kHz, mejor cuanto más nos alejemos del cero RHP pero sin acercarnos mucho a la frecuencia del doble polo.

Por lo tanto, las especificaciones que se requieren al sistema son las siguientes:

| Especificaciones iniciales de diseño |                                                                                                                                                                                                                                       |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $f_c$                                | <b>(Frecuencia de corte)</b> - Especificación inicial de diseño, cuyo valor debe ser de 1,5kHz                                                                                                                                        |

|                                      | <b>(Margen de Fase)</b> – Especificación inicial de diseño, cuyo valor debe ser de 55°.                                                                                                                                               |

| $PM$                                 | Cuanto mayor sea el parámetro PM, mayor será la estabilidad del sistema. Por regla general conviene tener $PM > 50^\circ$ .                                                                                                           |

| $f_{sw}$                             | <b>(Frecuencia de conmutación)</b> – Especificación inicial de diseño, cuyo valor debe ser de 100 kHz                                                                                                                                 |

| $Ts$                                 | <b>(Periodo de muestreo)</b> – Especificación inicial de diseño, cuyo valor es de 10 $\mu\text{s}$                                                                                                                                    |

| $e_p$                                | <b>(Error de posición)</b> – El error de posición debe ser cero, la salida debe de seguir exactamente a la referencia. Esto implica que la función de transferencia en lazo abierto tenga un polo en $s=0$ . Es decir, un integrador. |

Tabla 1 Especificaciones iniciales de diseño para el cálculo del regulador

## 4.1 Cálculo del Regulador

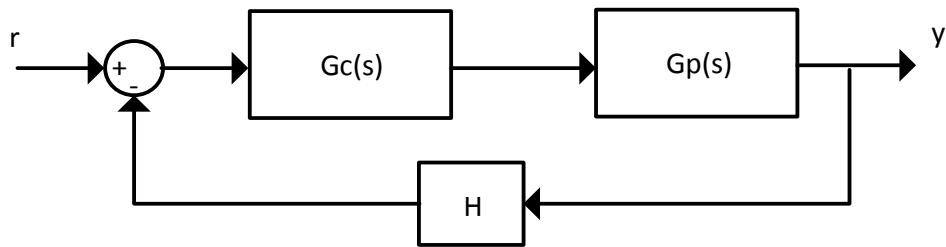

Para realizar el cálculo del regulador  $G_c(s)$  y seleccionar su función de transferencia, es necesario conocer la planta del sistema  $G_p(s)$ , que se ha calculado anteriormente en el apartado 2.1 y que se muestra en (27). A su vez, también es conocido el bloque  $H$  correspondiente al sistema de acondicionamiento necesario para adaptar la tensión de salida del Boost a la tensión de entrada al conversor analógico digital. Por lo que el sistema resultante es el mostrado en la Fig. 19.

Fig. 19 Diagrama de bloques del sistema

La función de transferencia de la planta obtenida anteriormente es la siguiente:

$$G_p(s) = -0,092584 \frac{(s + 5,682 \cdot 10^4) \cdot (s - 4,033 \cdot 10^4)}{s^2 + 1721s + 8,128 \cdot 10^6} \quad (27)$$

De donde se obtiene:

- El valor de la frecuencia del cero RHP  $\rightarrow f_{RHP} = 6,4 \text{ kHz}$

- El valor de la frecuencia del cero debido a la resistencia  $ESR$  del condensador  $\rightarrow f_{ESR} = 9 \text{ kHz}$

- El valor de la frecuencia del doble polo  $\rightarrow f_n = 453 \text{ Hz}$

- El valor del coeficiente de amortiguamiento del doble polo  $\rightarrow \zeta = 0,3$

La ganancia de la etapa de acondicionamiento calculada anteriormente es

$$H = \frac{2.5}{12} = 0.21 \quad (28)$$

A partir de ambas (27) y (28), se obtiene la función de transferencia en lazo abierto de la planta del sistema y la etapa de acondicionamiento  $L_u$ :

$$L_u = H * G_p(s) \quad (29)$$

El regulador se ha calculado siguiendo el método unificado del lugar de las raíces y de la respuesta en frecuencia [9], según este método se debe cumplir:

$$\begin{aligned} \angle G_c(jw_c) + \angle L_u(jw_c) &= -180^\circ + PM + \theta_{delay} \\ |G_c(jw_c)| * |L_u(jw_c)| &= 1 \end{aligned} \quad (30)$$

El término  $\theta_{delay}$  representa el retardo de transporte que depende del tipo de modulación PWM. Éste es analizado en [10], para el caso del modulador *trailing-edge* que ha sido el implementado, este retardo es equivalente a:

$$\theta_{delay} = 360D \frac{f_c}{f_s} \quad (31)$$

Por tanto, siendo  $f_c = 1.5 \text{ kHz}$ , nos da como resultado:

$$\theta_{delay} = 360D \frac{f_c}{f_s} = 3.24^\circ \quad (32)$$

Por otra parte, la fase y módulo de la función de transferencia en lazo abierto  $L_u$  obtenidos a la frecuencia  $f_c = 1.5 \text{ kHz}$  son los siguientes:

$$\angle L_u(jw_c) = -172.37^\circ \quad (33)$$

$$|L_u(jw_c)| = 0.5648 \quad (34)$$

Una vez obtenidos la fase y módulo de la función de transferencia en lazo abierto  $L_u$ , nos queda obtener la función de transferencia del regulador. Una vez analizadas las opciones, la función de transferencia del regulador que mejor se adapta a las especificaciones de diseño es la siguiente:

$$G_c(s) = \frac{K}{s} \frac{(1 + s/w_{z1}) \cdot (1 + s/w_{z2})}{(1 + s/w_p)} \text{ ó } \frac{K}{s} \frac{(s^2 + 2\zeta w_n s + w_n^2)}{(1 + s/w_p)} \quad (35)$$

Por lo que, a partir de la función de transferencia arriba indicada (35), de las especificaciones iniciales (Tabla 1), de la fase y módulo obtenidos en (33) y (34), y utilizando distintos métodos, se calculan 5 reguladores. Entre éstos, se ha seleccionado el que mejor cumple con las funciones de mérito que posteriormente serán explicadas.

Los reguladores obtenidos han sido los siguientes:

| CASO 1.-Cálculo del regulador por el método de Ziegler-Nichols                                                                    |                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| $G_c(s) = \frac{35.1064}{s} \frac{(s^2 + 19690s + 1.015e8)}{(s + 2.114e5)}$                                                       |                                                                                                     |

| CASO 2.-Cálculo del regulador con un cero real doble ( $\zeta=1$ )                                                                |                                                                                                     |

| $G_c(s) = \frac{1135,93}{s} \frac{(1 + s/2\pi \cdot 400)^2}{(1 + s/2\pi \cdot 6619,83)}$                                          | $K = 1135,93$ $w_{z1} = w_{z2} = 2\pi \cdot 400$ $w_p = 2\pi \cdot 6619,83$                         |

| CASO 3 Cálculo del regulador con 2 ceros reales ( $\zeta=1,1$ )                                                                   |                                                                                                     |

| $G_c(s) = \frac{1126,2}{s} \frac{(\frac{s}{2\pi \cdot 400})^2 + 2\frac{\zeta}{2\pi \cdot 400}s + 1}{(1 + s/2\pi \cdot 8209,976)}$ | $K = 1126,2$ $w_{z1} = 2\pi \cdot 623,25$ $w_{z2} = 2\pi \cdot 256,717$ $w_p = 2\pi \cdot 8209,976$ |

| CASO 4 Cálculo del regulador con 2 ceros complejos conjugados ( $\zeta=0.9$ )                                                                                            |                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| $G_c(s) = \frac{1148,56738}{s} \frac{\left(\frac{s}{2\pi \cdot 400}\right)^2 + 2 \frac{\zeta}{2\pi \cdot 400} s + 1}{\left(1 + \frac{s}{2\pi \cdot 5482,1366}\right)}$   | $K = 1148,56738$<br>$w_{z1} = 2\pi \cdot (360 + j174,37)$<br>$w_{z2} = 2\pi \cdot (360 - j174,37)$<br>$w_p = 2\pi \cdot 5482,1366$ |

| CASO 5 Cálculo del regulador por el método del factor K                                                                                                                  |                                                                                                                                    |

| $G_c(s) = \frac{553,47}{s} \frac{\left(1 + \frac{s}{2\pi \cdot 150}\right) \cdot \left(1 + \frac{s}{2\pi \cdot 500}\right)}{\left(1 + \frac{s}{2\pi \cdot 4500}\right)}$ | $K = 553,47$<br>$w_{z1} = 2\pi \cdot 150$<br>$w_{z2} = 2\pi \cdot 500$<br>$w_p = 2\pi \cdot 4500$                                  |

Tabla 2 Reguladores calculados durante el desarrollo del trabajo

A continuación se muestra la forma de obtención del Regulador 3, que es el que se ha seleccionado como el más adecuado.

Siendo (35) la función de transferencia del regulador, a partir de la fase y módulo obtenido en (16), con  $w_c = 2\pi \cdot 1500$ ,  $\zeta=1.1$ , seleccionando  $w_{z1} \neq w_{z2} < w_n$ ,  $w_z = 2\pi \cdot 400$ ,  $PM + \theta_{delay} = 55^\circ$  y sustituyendo todo en (30), se obtiene que la frecuencia del polo debe ser:

$$\begin{aligned} \angle G_c(jw_c) &= -90 + \angle\left(1 - \left(\frac{w_c}{w_z}\right)^2 + j2\zeta\frac{w_c}{w_z}\right) - \angle\left(1 + j\frac{w_c}{w_p}\right) = -180^\circ + 55^\circ - \angle Lu(jw_c) \\ \angle\left(1 + j\frac{w_c}{w_p}\right) &= -90^\circ + \angle\left(1 - \left(\frac{1500}{400}\right)^2 + j2 \cdot 1.1 \cdot \frac{1500}{400}\right) + 180^\circ - 55^\circ - 172.37^\circ \\ &= -137.37^\circ + 147.72^\circ = 10.354^\circ \end{aligned} \quad (36)$$

$$\frac{w_c}{w_p} = \tan(10.354^\circ) \rightarrow w_p = \frac{w_c}{\tan(10.354^\circ)} = 2\pi \cdot 8209.976$$

Y que la ganancia K del regulador resultante debe ser:

$$\begin{aligned} |G_c(jw_c)| &= \frac{K}{w_c} \frac{1 + \left(\frac{w_c}{w_z}\right)^2}{\sqrt{1 + \left(\frac{w_c}{w_p}\right)^2}} = \frac{K}{w_c} \frac{1 + (3.75)^2}{\sqrt{1 + \tan^2(10.354) \cdot 1500^2}} = \frac{1}{|Lu(jw_c)|} \\ K &= \frac{w_c \cdot \sqrt{1 + \tan^2(10.354) \cdot 1500^2}}{15.0625 \cdot |Lu(jw_c)|} = \frac{2\pi f_c \cdot \sqrt{1 + \tan^2(10.354) \cdot 1500^2}}{15.0625 \cdot 0.5648} = 1126.2 \end{aligned} \quad (37)$$

Por tanto, el regulador resultante que cumple con las especificaciones impuestas es:

$$G_c(s) = \frac{1126,2}{s} \frac{\left(\frac{s}{2\pi \cdot 400}\right)^2 + 2 \frac{\zeta}{2\pi \cdot 400} s + 1}{\left(1 + \frac{s}{2\pi \cdot 8209.976}\right)}$$

La obtención del resto de Reguladores se encuentra detallada en el **ANEXO D**.

## 4.2 Selección del Regulador

Para evaluar y seleccionar el regulador que mejor se comporta, se han evaluado la respuesta del regulador frente a una serie de funciones de mérito.

Estas funciones de mérito son analizadas en [15], [16], [6] y son las siguientes:

| Funciones de mérito                          |                                                                                                                                                                                                                             |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>GM</b>                                    | <b>(Margen de Ganancia)</b> - Cuanto mayor sea el parámetro GM, mayor será la estabilidad del sistema. Por regla general conviene tener $GM > 10\text{dB}$ .                                                                |

| <b>PO</b>                                    | <b>(Sobreoscilación)</b> – Cuanto menor sea este parámetro menor será la amplitud de la primera oscilación en porcentaje sobre el valor final de referencia.                                                                |

| <b><math>\ S\ _{\text{inf}}</math></b>       | <b>(Norma S infinito)</b> – S se denomina función de sensibilidad, que determina la capacidad del sistema al rechazo de perturbaciones, errores de modelado... Cuanto menor sea este parámetro más robusto será el sistema. |

| <b><math>\ Z_{cl}\ _{\text{inf}}</math></b>  | <b>(Norma <math>Z_{cl}</math> infinito)</b> - $Z_{cl}$ determina la impedancia de salida en bucle cerrado. Mejor cuanto más pequeña sea esta impedancia de salida.                                                          |

| <b><math>f_B</math></b>                      | <b>(Frecuencia <math>f_B</math>)</b> Determina la frecuencia a la que el módulo de S es $\frac{1}{\sqrt{2}}$ $ S(jf_B)  = \frac{1}{\sqrt{2}}$<br>Mejor cuanto más se aproxime $f_B$ a $f_c$                                 |

| <b><math>\ G_c * S\ _{\text{inf}}</math></b> | <b>(Norma <math>G_c * S</math> infinito)</b> Determina el esfuerzo del regulador y su grado de saturación.<br>Mejor cuanto más pequeño sea este término.                                                                    |

| <b><math>K_i</math></b>                      | <b>(Ganancia del integrador del regulador)</b> Mejor cuanto más pequeño sea $K_i$ para evitar ciclos límite y conseguir que el error de posición sea 0.                                                                     |

Tabla 3 Funciones de mérito evaluadas

En el **ANEXO E** se muestra cómo se obtienen cada una de éstas funciones de mérito.

En la Tabla 4 se muestran los resultados obtenidos, marcando los resultados para cada una de las funciones de mérito de la siguiente forma:

- Los **peores resultados** se han marcado con letra roja y con un tamaño de letra pequeño.

- Los **mejores resultados** se han marcado con letra verde oscuro y con un tamaño de letra mayor.

- El **resto de resultados** se han marcado con letra verde y en cursiva.

| REG          | fc             | PM          | GM            | PO              | $ S _{\text{inf}}$ | $ Z_{cl} _{\text{inf}}$ | $f_B$           | $\ G_c S\ _{\text{inf}}$ | $K_i$          |

|--------------|----------------|-------------|---------------|-----------------|--------------------|-------------------------|-----------------|--------------------------|----------------|

| <b>Caso1</b> | <b>2.07kHz</b> | <b>14.2</b> | <b>3.3dB</b>  | <b>2.16728</b>  | <b>4.21</b>        | <b>1.65</b>             | <b>1.31kHz</b>  | <b>111.2</b>             | <b>0.16448</b> |

| <b>Caso2</b> | <b>1.5kHz</b>  | <b>55</b>   | <b>16.7dB</b> | <b>1.1275</b>   | <b>1.282</b>       | <b>0.62</b>             | <b>1.01kHz</b>  | <b>8.7566</b>            | <b>0.01132</b> |

| <b>Caso3</b> | <b>1.53kHz</b> | <b>55.1</b> | <b>14.9dB</b> | <b>1.1333</b>   | <b>1.2576</b>      | <b>0.609</b>            | <b>1.03kHz</b>  | <b>1.1206</b>            | <b>0.01125</b> |

| <b>Caso4</b> | <b>1.47kHz</b> | <b>55.1</b> | <b>18.3dB</b> | <b>1.12</b>     | <b>1.314</b>       | <b>0.63267</b>          | <b>0.992kHz</b> | <b>7.134</b>             | <b>0.013</b>   |

| <b>Caso5</b> | <b>1.5kHz</b>  | <b>55</b>   | <b>19.7dB</b> | <b>1.087653</b> | <b>1.35</b>        | <b>0.59264</b>          | <b>1.04kHz</b>  | <b>5.892</b>             | <b>0.00555</b> |

Tabla 4 Tabla de resultados en las que se muestran los resultados obtenidos para las distintas funciones de mérito

Las dos primera columnas corresponden a las especificaciones iniciales de diseño, frecuencia de corte ( $f_c$ ) y Margen de Fase ( $PM$ ), que deben de ser 1,5kHz y 55° respectivamente.

En este caso, el regulador seleccionado es el del caso 3, marcado en la Tabla 4 sobre fondo gris claro, que tiene 3 mejores resultados, 4 resultados intermedios y ningún peor resultado.

#### CASO 3 Cálculo del regulador con 2 ceros reales ( $\zeta=1.1$ )

$$G_c(s) = \frac{1126,2 \left( \frac{s}{2\pi \cdot 400} \right)^2 + 2 \frac{\zeta}{2\pi \cdot 400} s + 1}{s \left( 1 + \frac{s}{2\pi \cdot 8209,976} \right)}$$

$K = 1126,2$

$w_{z1} = 2\pi \cdot 623,25$

$w_{z2} = 2\pi \cdot 256,717$

$w_p = 2\pi \cdot 8209,976$

A continuación se muestra cómo se han obtenido los valores para las distintas funciones de mérito.

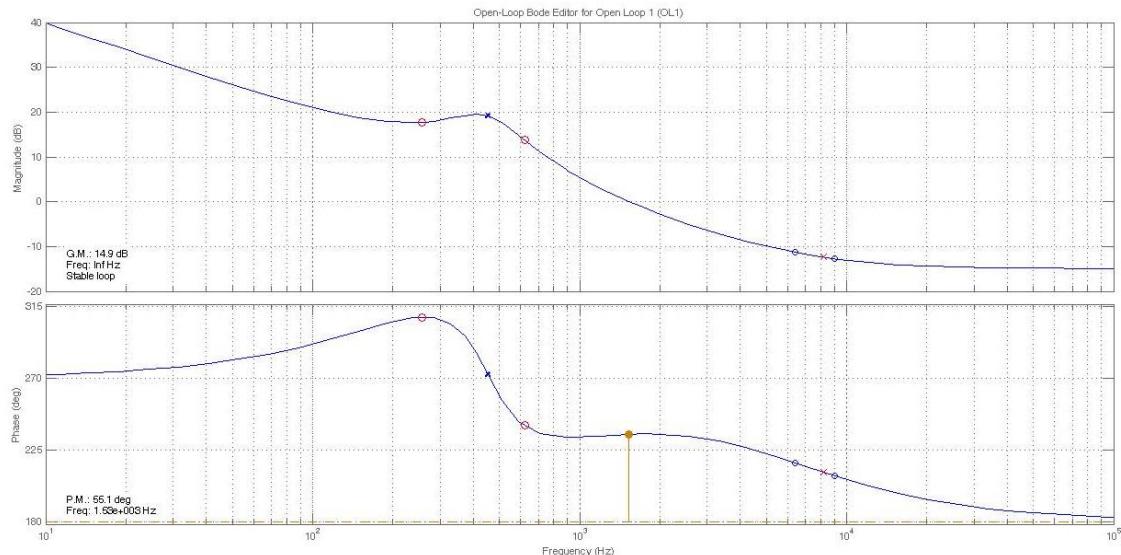

En primer lugar, el diagrama de bode en bucle abierto que se obtiene con este regulador es el siguiente (Fig. 20):

Fig. 20 Diagrama de bode del sistema en bucle abierto

Del que se obtienen los siguientes valores: **fc=1.53kHz, PM=55.1°, GM=14.9 dB-**

A partir del siguiente script en Matlab y de las gráficas que se obtienen, se calculan el resto de los valores de las funciones de mérito que se enumeraban anteriormente:

```

Sys1=series(Gc3,H*Gp)

Sys2=feedback(Sys1,1)

Sys3=1-Sys2           %Funcion sensibilidad

norm(Sys3,inf)        % |S|inf=1.257624590802233

%

Zo_cl=series(-Zo_ol,Sys3);

norm(Zo_cl,inf)        | Zcl | inf=0.6089852

%

```

```

bode(Zo_ol,Zo_cl)

[ystep,t]=step(Sys2);

norm(ystep,inf)

%

SO=1.133317460162967

bode(Sys3)

Sys4=series(Gc3,Sys3);

norm(Sys4,inf)

%

| Gc*S |_inf=1.1206

%

%

% Condicion de ciclos límite ---- G_o*H*Ki<1

% G_o*H=cte para todos los reguladores K*Ki<1

% Mejor cuanto menor sea Ki

Ki = lim(z - 1)

$$\frac{7.5137(z - 0.984)(z - 0.9616)}{(z - 1)(z - 0.5897)} = 0.01125$$

```

Tabla 5 Script en Matlab para la obtención de los valores de las funciones de mérito

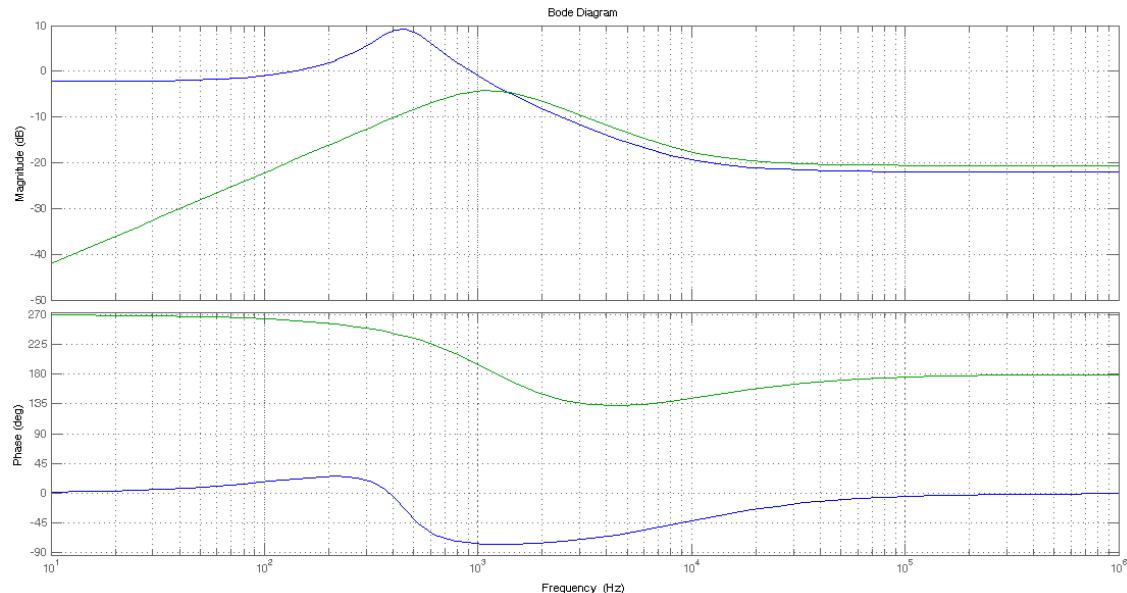

La siguiente Fig. 21, muestra la impedancia de salida ( $Zo_{ol}$  y  $Zo_{cl}$ ) en bucle abierto y bucle cerrado respectivamente:

Fig. 21 Diagrama de bode de la impedancia de salida en bucle abierto (azul) y en bucle cerrado (verde)

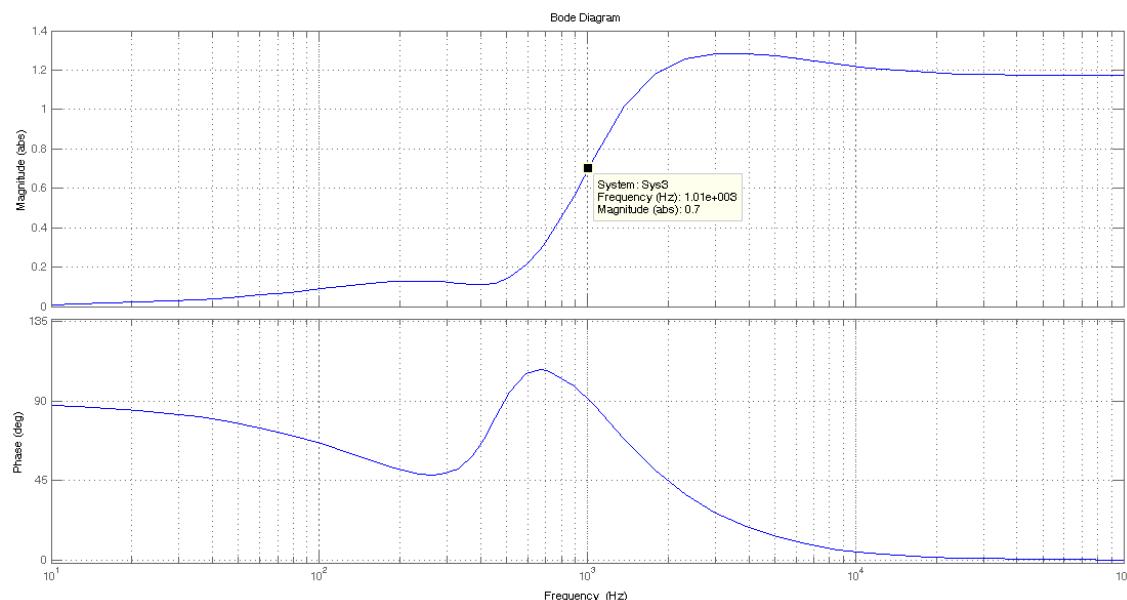

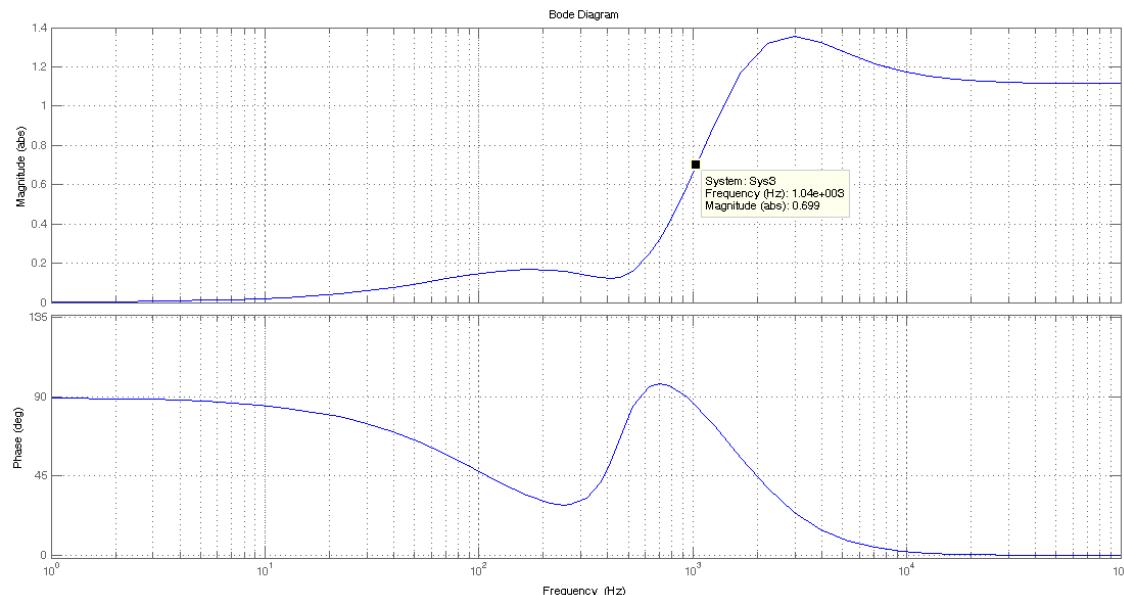

A partir de la Fig. 22 se obtiene  $f_B=1.03\text{kHz}$ .

Fig. 22 Diagrama de Bode de la función de sensibilidad S

En resumen, los valores obtenidos para cada función de mérito son los siguientes:

| REG   | fc      | PM   | GM     | PO     | S inf  | Zcl inf | f <sub>B</sub> | GcS inf | Ki      |

|-------|---------|------|--------|--------|--------|---------|----------------|---------|---------|

| Caso3 | 1.53kHz | 55.1 | 14.9dB | 1.1333 | 1.2576 | 0.609   | 1.03kHz        | 1.1206  | 0.01125 |

Estos mismos pasos se han seguido con todos los reguladores y se encuentran detallados en el ANEXO F.

### 4.3 Verificación mediante simulación

Para comprobar el comportamiento del sistema completo, se realiza su verificación mediante simulación utilizando la herramienta Matlab. Inicialmente se verifica el sistema en modo continuo, para posteriormente hacerlo en modo discreto.

Fig. 23 Modelo del sistema en modo continuo

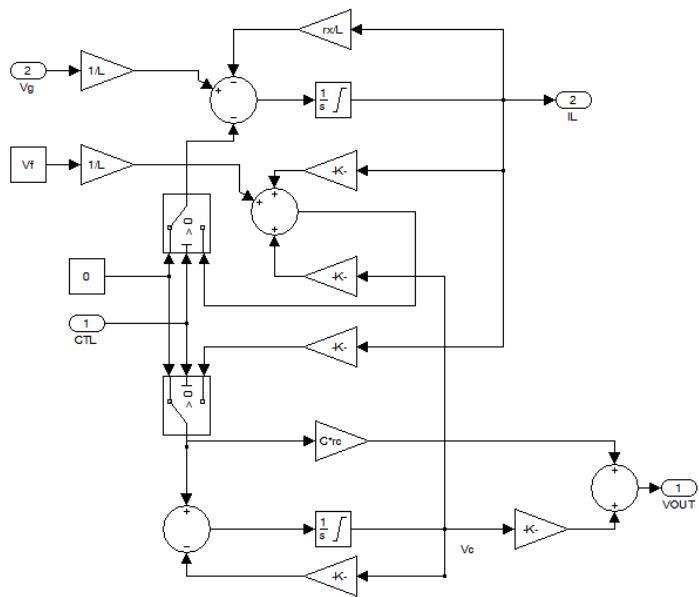

El circuito equivalente del modelo comutado del convertidor Boost (bloque sombreado en azul en la Fig. 23) desarrollado en [14], es el que se muestra en la Fig. 24.

MOSFET ON:

$$\frac{d}{dt} \begin{pmatrix} i_L \\ V_c \end{pmatrix} = \begin{pmatrix} -\frac{r_L}{L} & 0 \\ 0 & \frac{-1}{C(R+r_c)} \end{pmatrix} \begin{pmatrix} i_L \\ V_c \end{pmatrix} + \begin{pmatrix} 1/L \\ 0 \end{pmatrix} V_g$$

$$V_{out} = \begin{pmatrix} 0 & \frac{R}{R+r_c} \end{pmatrix} \begin{pmatrix} i_L \\ V_c \end{pmatrix}$$

MOSFET OFF:

$$\frac{d}{dt} \begin{pmatrix} i_L \\ V_c \end{pmatrix} = \begin{pmatrix} -\frac{1}{L(r_L+\frac{r_cR}{r_c+R})} & \frac{-R}{L(R+r_c)} \\ \frac{R}{C(R+r_c)} & \frac{-1}{C(R+r_c)} \end{pmatrix} \begin{pmatrix} i_L \\ V_c \end{pmatrix} + \begin{pmatrix} \frac{1}{L} \\ 0 \end{pmatrix} V_g$$

$$V_{out} = \begin{pmatrix} \frac{Rr_c}{R+r_c} & \frac{R}{R+r_c} \end{pmatrix} \begin{pmatrix} i_L \\ V_c \end{pmatrix}$$

Fig. 24 Circuito equivalente del convertidor Boost obtenido a partir de sus ecuaciones de estado

Hay dos estados posibles dependiendo del estado del Mosfet, ON/OFF, que dependen de la señal PWM generada en la FPGA.

Para convertir los coeficientes del controlador de modo continuo a modo discreto se utiliza la función c2d, siendo  $T_s=10 \mu s$  y el método de discretización es el bilineal con preajuste (prewarp).

La transformada bilineal transforma sistemas continuos en sistemas discretos y viceversa, tal y como se explica en [6], el preajuste se realiza para que ambos sistemas coincidan en la frecuencia de corte  $\omega_c$ .

Para ello se ha utilizado el siguiente script realizado en Matlab.

```

%% Regulador Caso 3

```

$$G_{c3}(s) = \frac{1126,2}{s} \frac{\left(\frac{s}{2\pi \cdot 400}\right)^2 + 2 \frac{1,1}{2\pi \cdot 400} s + 1}{(1 + \frac{s}{2\pi \cdot 8209,976})}$$

```

Tsw=10.0e-6; Ts=Tsw; % Período de conmutación

```

```

fc=1500; wc=2*pi*fc; % Frecuencia de corte

```

```

% Coeficientes del regulador

```

```

K=1126.2; wz=2*pi*400; wp=2*pi*8209.976; chi=1.1;

Cnum=[1/wz^2 2*chi/wz 1];

Gc3=tf(K*Cnum, [1/wp 1 0]);

```

```

zpk(Gc3);

sisotool(H*Gp, Gc3) % Comprobación mediante sisotool

```

```

% Transformación a digital

Gc3z=c2d(Gc3,Ts,'prewarp',wc)

zpk(Gc3z)

% 7.514 z^2 - 14.62 z + 7.109

% -----

% z^2 - 1.5897 z + 0.5897

```

Tabla 6 Script en Matlab para transformar el regulador de continuo a digital

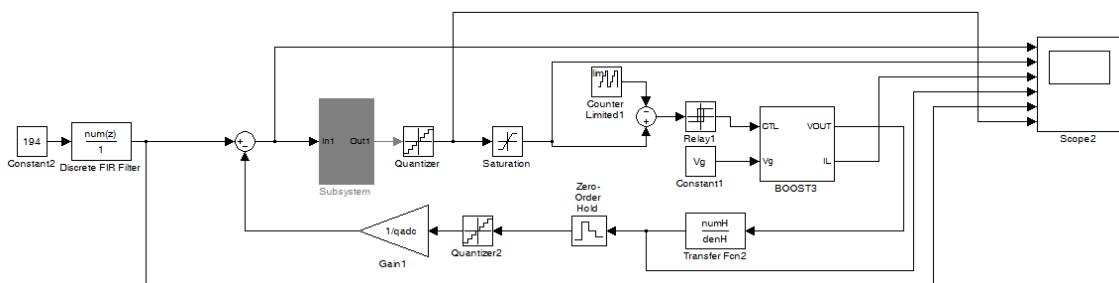

El modelo del sistema en modo discreto es el que se observa en la Fig. 25.

Fig. 25 Modelo del sistema en modo discreto

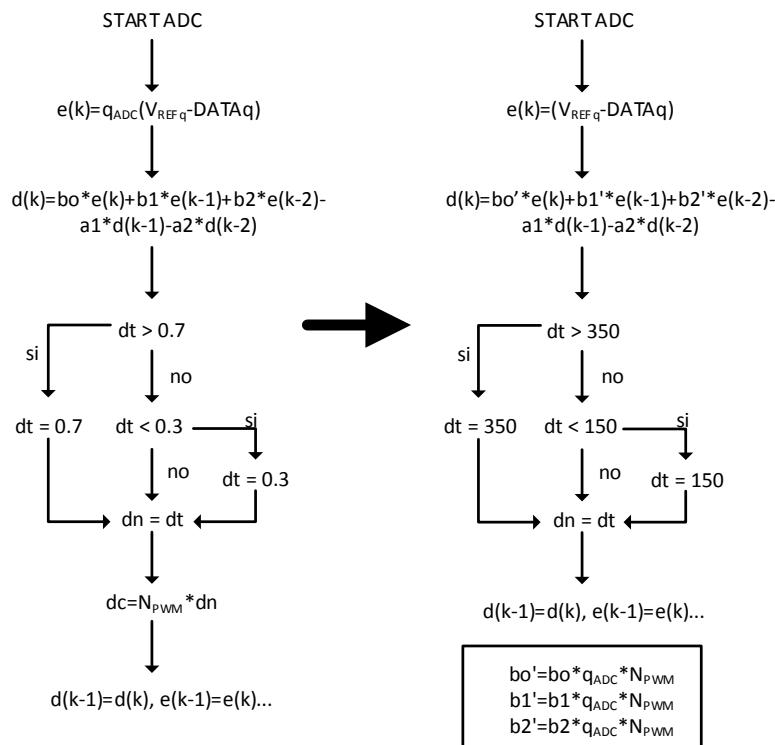

A la hora de discretizar el sistema hay que tener en cuenta que la resolución ya no es infinita y hay que considerar la resolución del ADC y de la PWM: