TESIS DE LA UNIVERSIDAD

# DE ZARAGOZA

Alexandra Ferrerón Labari

2016

216

# Exploiting Natural On-chip Redundancy for Energy Efficient Memory and Computing

Departamento Informática e Ingeniería de Sistemas

Director/es

Alastruey Benedé, Jesús Suárez García, Darío

Prensas de la Universidad Universidad Zaragoza

ISSN 2254-7606

Reconocimiento – NoComercial – SinObraDerivada (by-nc-nd): No se permite un uso comercial de la obra original ni la generación de obras derivadas.

© Universidad de Zaragoza Servicio de Publicaciones

ISSN 2254-7606

**Tesis Doctoral**

# EXPLOITING NATURAL ON-CHIP REDUNDANCY FOR ENERGY EFFICIENT MEMORY AND COMPUTING

Autor

Alexandra Ferrerón Labari

Director/es

Alastruey Benedé, Jesús Suárez García, Darío

# UNIVERSIDAD DE ZARAGOZA

Informática e Ingeniería de Sistemas

2016

Repositorio de la Universidad de Zaragoza – Zaguan http://zaguan.unizar.es

# EXPLOITING NATURAL ON-CHIP REDUNDANCY FOR ENERGY EFFICIENT MEMORY AND COMPUTING

Author: Alexandra ferrerón labari

Supervisors: dr. jesús alastruey benedé dr. darío suárez gracia

DISSERTATION Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Universidad de Zaragoza

Grupo de Arquitectura de Computadores Departamento de Informática e Ingeniería de Sistemas Instituto de Investigación en Ingeniería de Aragón Universidad de Zaragoza

October, 2016

Alexandra Ferrerón Labari © October, 2016 Exploiting Natural On-chip Redundancy for Energy Efficient Memory and Computing

#### ABSTRACT

Power density is currently the primary design constraint across most computing segments and the main performance limiting factor. For years, industry has kept power density constant, while increasing frequency, lowering transistors supply ( $V_{dd}$ ) and threshold ( $V_{th}$ ) voltages. However,  $V_{th}$  scaling has stopped because leakage current is exponentially related to it. Transistor count and integration density keep doubling every process generation (Moore's Law), but the power budget caps the amount of hardware that can be active at the same time, leading to *dark silicon*. With each new generation, there are more resources available, but we cannot fully exploit their performance potential. In the last years, different research trends have explored how to cope with dark silicon and unlock the energy efficiency of the chips, including Near-Threshold voltage Computing (NTC) and approximate computing.

NTC aggressively lowers  $V_{dd}$  to values near  $V_{th}$ . This allows a substantial reduction in power, as dynamic power scales quadratically with supply voltage. The resultant power reduction could be used to activate more chip resources and potentially achieve performance improvements. Unfortunately,  $V_{dd}$  scaling is limited by the tight functionality margins of on-chip SRAM transistors. When scaling  $V_{dd}$  down to values near-threshold, manufacture-induced parameter variations affect the functionality of SRAM cells, which eventually become not reliable.

A large amount of emerging applications, on the other hand, features an intrinsic error-resilience property, tolerating a certain amount of noise. In this context, approximate computing takes advantage of this observation and exploits the gap between the level of accuracy required by the application and the level of accuracy given by the computation, providing that reducing the accuracy translates into an energy gain. However, deciding which instructions and data and which techniques are best suited for approximation still poses a major challenge.

This dissertation contributes in these two directions. First, it proposes a new approach to mitigate the impact of SRAM failures due to parameter variation for effective operation at ultra-low voltages. We identify two levels of natural on-chip redundancy: cache level and content level. The first arises because of the replication of blocks in multi-level cache hierarchies. We exploit this redundancy with a cache management policy that allocates blocks to entries taking into account the nature of the cache entry and the use pattern of the block. This policy obtains performance improvements between 2% and 34%, with respect to block disabling, a technique with similar complexity, incurring no additional storage overhead. The latter (content level redundancy) arises because of the redundancy of data in real world applications. We exploit this redundancy compressing cache blocks to fit them in partially functional cache entries. At the cost of a slight overhead increase, we can obtain performance within 2% of that obtained when the cache is built with fault-free cells, even if more than 90% of the cache entries have at least a faulty cell.

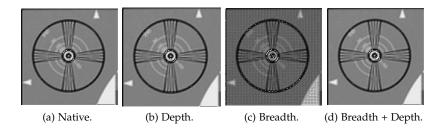

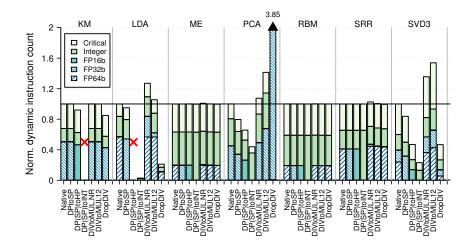

Then, we analyze how the intrinsic noise tolerance of emerging applications can be exploited to design an approximate Instruction Set Architecture (ISA). Exploiting the ISA redundancy, we explore a set of techniques to approximate the execution of instructions across a set of emerging applications, pointing out the potential of reducing the complexity of the ISA, and the trade-offs of the approach. In a proof-of-concept implementation, the ISA is shrunk in two dimensions: *Breadth* (i.e., simplifying instructions) and *Depth* (i.e., dropping instructions). This proof-of-concept shows that energy can be reduced on average 20.6% at around 14.9% accuracy loss.

#### PUBLICATIONS

Some ideas and figures have appeared previously or are currently under review in the following publications:

- A. Ferrerón. Exploiting Redundancy for Efficient Cache Operation at Nearthreshold Voltages. ACM Student Research Competition at Grace Hopper Celebration. 2015. Acceptance ratio 19/79 (24%), Bronze Medal.

- [2] A. Ferrerón, D. Suárez-Gracia, J. Alastruey-Benedé, T. Monreal-Arnal, and V. Viñals-Yúfera. "Block Disabling Characterization and Improvements in CMPs Operating at Ultra-low Voltages." In: 26<sup>th</sup> Int. Symp. on Computer Architecture and High Performance Computing. 2014, pp. 238–245. DOI: 10.1109/SBAC-PAD.2014.12. B CORE 2014; Google h5-index 12; Acceptance ratio 32.6%.

- [3] A. Ferrerón, D. Suárez-Gracia, J. Alastruey-Benedé, T. Monreal-Arnal, and V. Viñals-Yúfera. "Low Complexity Improvements for CMPs Shared Caches at Ultra-low Voltages." In: 10th International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems. HiPEAC, 2014, pp. 73–76.

- [4] A. Ferrerón, J. Alastruey-Benedé, D. Suárez-Gracia, T. Monreal-Arnal, P. Ibáñez, and V. Viñals-Yúfera. "A Fault-aware Cache Management Policy for CMPs Operating at Ultra-low Voltages." Submitted to IEEE Trans. on Parallel and Distributed Sytems. July 2016. IF: 2.661; JCR 2015: Q1 (9/105) Computer Science, Theory & Methods; Google h5-index 76 (1st in Computing Systems).

- [5] A. Ferrerón, J. Alastruey-Benedé, D. Suárez-Gracia, and U. R. Karpuzcu. "AISC: Approximate Instruction Set Architecture." Submitted to 2017 Design, Automation & Test in Europe Conf. Exhibition. Sept. 2016.

B CORE 2014; Google h5-index 39 (9th in Computer Hardware Design).

- [6] A. Ferrerón, D. Suárez-Gracia, J. Alastruey-Benedé, T. Monreal-Arnal, and P. Ibáñez. "Concertina: Squeezing in Cache Content to Operate at Near-Threshold Voltage." In: *IEEE Trans. on Computers (Special Section on Defect and Fault Tolerance in VLSI and Nanotechnology Systems)* 65.3 (2016), pp. 755–769. DOI: 10.1109/TC.2015.2479585. *IF:* 1.723; JCR 2015: Q1 (12/51) Computer Science, Hardware & Architecture; Google h5-index 45 (4th in Computer Hardware Design).

- [7] A. Ferrerón, J. Alastruey-Benedé, D. Suárez-Gracia, T. Monreal-Arnal, P. Ibáñez, and V. Viñals-Yúfera. "Gestión de contenidos en caches operando a bajo voltaje." In: XXVII Jornadas de Paralelismo. 2016, pp. 497–506.

#### ACKNOWLEDGMENTS

I want to start by thanking my supervisors, Chus and Darío, for their help and guidance during these years, and with whom during this time I have built not only a professional, but also a relationship of friendship. This dissertation had not seen the light without Pablo Ibáñez devoted guidance and work, who came to the rescue in the time I most needed someone like him. Thanks also to my co-authors and to the rest of the members of the computer architecture group. To all of you, I hope you enjoyed working with me as much as I enjoyed working with you.

Thanks to the external reviewers Rekai (Rodrigo Gónzalez-Alberquilla) and Adrian Sampson. I really appreciate the time you dedicated to thoroughly read my dissertation and your helpful suggestions.

I also want to thank to the supervisors of my research stays at Edinburgh, Minnesota, and Cambridge, and their teams, who welcomed me and made me feel like home. Mike O'Boyle gave me some great advice that has helped me to arrive to where I am, taking difficult decisions on the way. Ulya Karpuzcu has been an example of work, tenacity, and self-improvement, and became a great support during the last part of my PhD. Roxana Rusitoru, thanks for making my stay at ARM a great and really fun experience.

On the technical part, I have to thank Jorge Albericio, Marta Ortín, and Javier D. Maag for their help with the simulation infrastructure and simulation methodology.

Special thanks to all my friends and colleagues who have been there during all these years, supporting and encouraging me at every step of the way. I hope you forgive me for not naming you all here. María and Alejandro, you are family to me; thanks for being always there.

Finally, I have to thank my family, the ones that are and the ones that left, for all these years of support and patience, always believing in me. And Markus, who has shared many sacrifices, including the pain of reading this dissertation.

And with all my heart, I dedicate this work to Rosa, whose light slowly faded, and who I will always miss; wherever I go, I will always have the memory of your love with me.

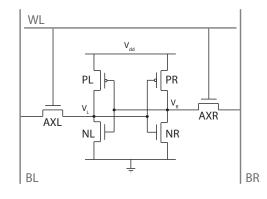

## CONTENTS

| Ι | PR          | ELIMINARIES 1                                                                                                     |  |  |  |  |  |

|---|-------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1 | INT         | RODUCTION 3                                                                                                       |  |  |  |  |  |

|   | 1.1         | Rationale 3                                                                                                       |  |  |  |  |  |

|   | 1.2         | Objectives and Dissertation Overview 6                                                                            |  |  |  |  |  |

|   |             | Contributions 6                                                                                                   |  |  |  |  |  |

|   |             | Project Framework 7                                                                                               |  |  |  |  |  |

|   | TY          | NAME AND ANOVED FERICIENT CACHE OPERATION                                                                         |  |  |  |  |  |

| Π |             | PLOITING REDUNDANCY FOR EFFICIENT CACHE OPERATION<br>NEAR-THRESHOLD VOLTAGES 9                                    |  |  |  |  |  |

| 2 |             | IPUTING AT VOLTAGES NEAR THE THRESHOLD 11                                                                         |  |  |  |  |  |

| - | 2.1         | T . 1                                                                                                             |  |  |  |  |  |

|   | 2.2         | Process Variations in SRAM cells 12                                                                               |  |  |  |  |  |

|   | 2.2         | 2.2.1 Reference SRAM Reliability Study 14                                                                         |  |  |  |  |  |

|   | 2.3         | Related Work 15                                                                                                   |  |  |  |  |  |

|   | 2.5         |                                                                                                                   |  |  |  |  |  |

|   |             | 2.3.1Circuit Solutions152.3.2Micro-architectural Solutions16                                                      |  |  |  |  |  |

| 2 | EVD         | -                                                                                                                 |  |  |  |  |  |

| 3 |             |                                                                                                                   |  |  |  |  |  |

|   | -           | Overview of the Modeled System     21       Simulation Framework     22                                           |  |  |  |  |  |

|   | -           |                                                                                                                   |  |  |  |  |  |

|   | 3.3         | Workloads and Methodology 22                                                                                      |  |  |  |  |  |

|   |             | 3.3.1Multiprogrammed Workloads233.3.2Parallel Workloads24                                                         |  |  |  |  |  |

|   | 2.4         |                                                                                                                   |  |  |  |  |  |

|   | 3.4         |                                                                                                                   |  |  |  |  |  |

| 4 |             |                                                                                                                   |  |  |  |  |  |

|   |             |                                                                                                                   |  |  |  |  |  |

|   |             | Impact of BD on Large Shared Caches at Low Voltages28Exploiting Inclusive Hierarchies for Low Voltage Operation29 |  |  |  |  |  |

|   | 4.3         | 4.3.1 BDOT Limitations 30                                                                                         |  |  |  |  |  |

|   | 4 4         |                                                                                                                   |  |  |  |  |  |

|   | 4.4         | 4.4.1Baseline NRR Replacement Algorithm31                                                                         |  |  |  |  |  |

|   |             | 4.4.2 Reused-based and Fault-aware Management for BDOT                                                            |  |  |  |  |  |

|   |             | Caches 32                                                                                                         |  |  |  |  |  |

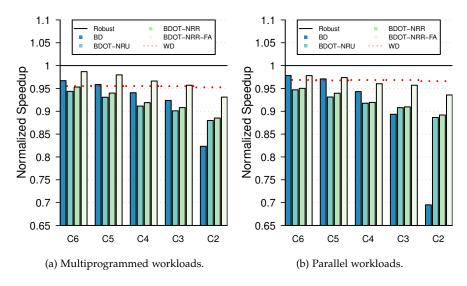

|   | 4.5         | Evaluation 36                                                                                                     |  |  |  |  |  |

|   | 4.9         | 4.5.1 Multiprogrammed Workloads 36                                                                                |  |  |  |  |  |

|   |             | 4.5.2 Parallel Workloads 37                                                                                       |  |  |  |  |  |

|   |             | 4.5.3 Comparison with Prior Work 38                                                                               |  |  |  |  |  |

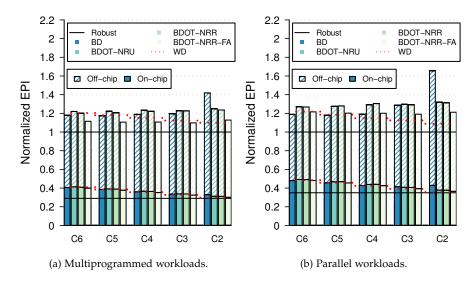

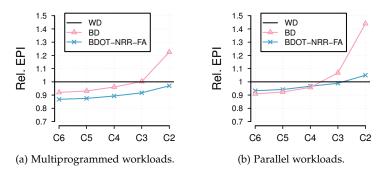

|   | 4.6         | System Impact 40                                                                                                  |  |  |  |  |  |

|   | 4.0         | 4.6.1 Performance 40                                                                                              |  |  |  |  |  |

|   |             | 4.6.2 Area and Energy 41                                                                                          |  |  |  |  |  |

|   | 4.7         | Summary and Conclusions 43                                                                                        |  |  |  |  |  |

| 5 | • •         | LOITING REDUNDANCY AT CONTENT LEVEL 45                                                                            |  |  |  |  |  |

| ) | 5.1         | Introduction 45                                                                                                   |  |  |  |  |  |

|   | 5.2         | Compression for Caches Operating at Low Voltages 46                                                               |  |  |  |  |  |

|   | J. <u> </u> | 5.2.1 Compression Scheme Requirements for Caches Oper-                                                            |  |  |  |  |  |

|   |             | ating at Low Voltages 46                                                                                          |  |  |  |  |  |

|   |             | 5.2.2 Exploiting Zero Redundancy to Compress Cache Blocks 48                                                      |  |  |  |  |  |

|   | 5.3         | Concertina Architecture 49                                                                                        |  |  |  |  |  |

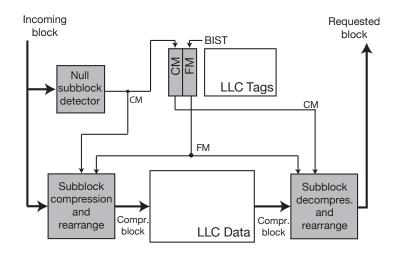

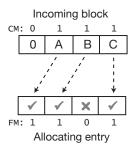

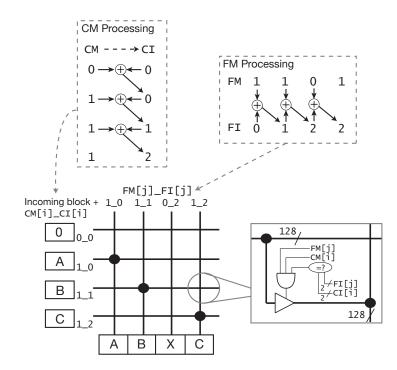

|   | J.J.        | 5.3.1 Operation and Component Description 49                                                                      |  |  |  |  |  |

|   |             |                                                                                                                   |  |  |  |  |  |

6

55

68

6.3.1 Approximate Computing Techniques 71

73

- EXPERIMENTAL FRAMEWORK 7

- 7.1 Workloads 73

- 7.2 Methodology 75

- 7.2.1 Evaluation Metrics 75

- AISC: APPROXIMATE INSTRUCTION SET COMPUTER 8 79

- 8.1 Introduction 79

- 8.2 AISC: Proof-of-Concept Implementation 80

- 8.2.1 Depth Techniques 81

- 8.2.2 Breadth Techniques 81

- 8.2.3 Breadth + Depth Techniques 82

- 8.3 Evaluation 82

- 8.3.1 Evaluation Setup: Energy Modeling 83

- 8.3.2 AISC Proof-of-Concept Evaluation 83

- Conclusion and Discussion 8.4 87

- IV CONCLUSION 89

- CONCLUSIONS AND FUTURE WORK 91 9

- 9.1 Faulty Last-level SRAM Caches at Near-threshold Voltages 91

- 9.2 Approximate Computing at the ISA layer 92

- 9.3 Future Work 92

BIBLIOGRAPHY 95

## LIST OF FIGURES

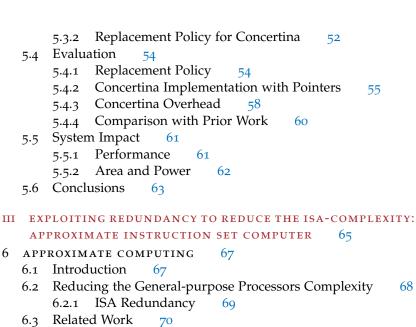

| Figure 1.1  | Dark silicon and post-Dennard scaling 4                    |

|-------------|------------------------------------------------------------|

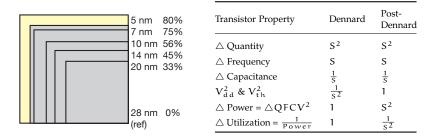

| Figure 2.1  | Energy per operation and delay with respect to $V_{dd}$ 12 |

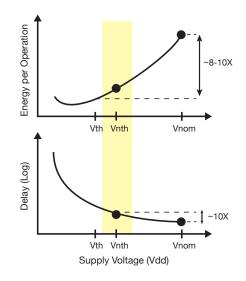

| Figure 2.2  | 6T SRAM cell architecture 13                               |

| Figure 2.3  | Cache capacity tracking faults at finer granularities 17   |

| Figure 3.1  | Tiled CMP with 8 processors 21                             |

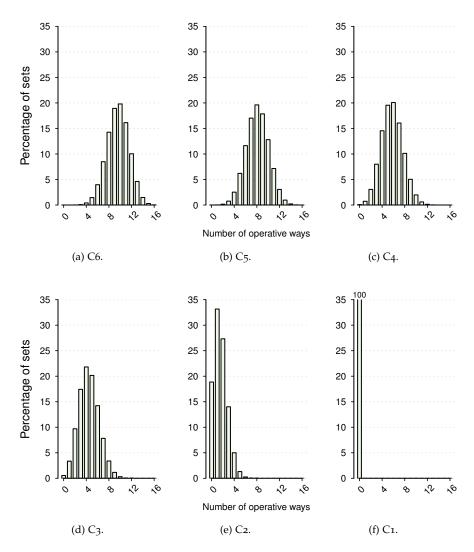

| Figure 4.1  | Available associativity of a 16-way cache at 0.5 V 29      |

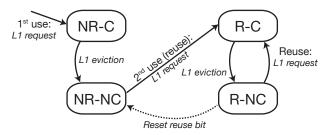

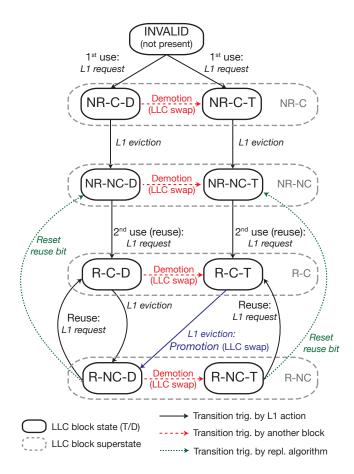

| Figure 4.2  | Reuse and inclusion states for a block in LLC 32           |

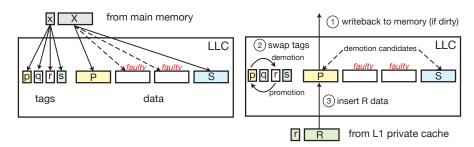

| Figure 4.3  | Insertion and promotion actions 33                         |

| Figure 4.4  | Reuse and inclusion states for a block in LLC (BDOT) 35    |

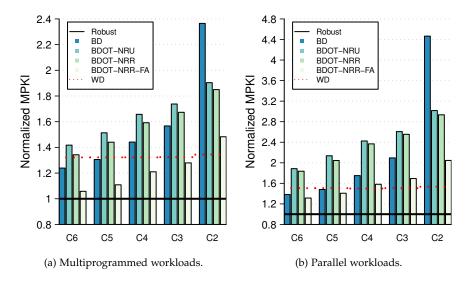

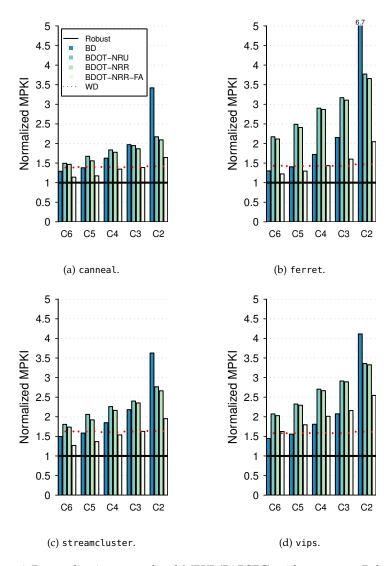

| Figure 4.5  | Average MPKI for different proposals 38                    |

| Figure 4.6  | Per-application LLC MPKI (parallel workloads) 39           |

| Figure 4.7  | Average speedup for different proposals 40                 |

| Figure 4.8  | Average EPI for different proposals 42                     |

| Figure 4.9  | EPI with fine-grained block power gating 42                |

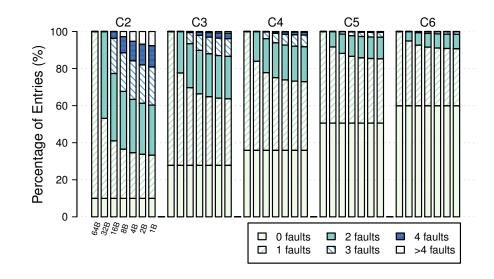

| Figure 5.1  | Distribution of faulty subentries 46                       |

| Figure 5.2  | Average percentage of LLC blocks with at least one         |

|             | null subblock 48                                           |

| Figure 5.3  | Concertina design overview 50                              |

| Figure 5.4  | Example of compressible block to be stored at a faulty     |

|             | cache entry 51                                             |

| Figure 5.5  | Implementation of the compression and rearrange-           |

| 0 11        | ment stage 51                                              |

| Figure 5.6  | LLC MPKI for the different replacement alternatives 55     |

| Figure 5.7  | LLC MPKI for the different compression alternatives 58     |

| Figure 5.8  | Performance for the compression alternatives 61            |

| Figure 5.9  | Per-application performance analysis (1B 3Ptrs, C3) $61$   |

| Figure 5.10 | System power consumption 62                                |

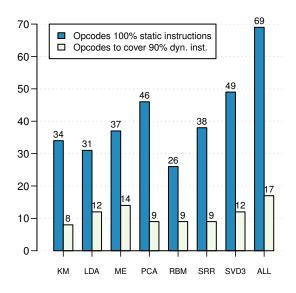

| Figure 6.1  | Opcodes distribution (native execution) 69                 |

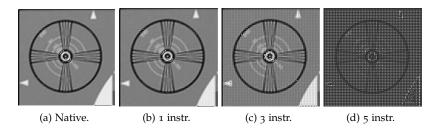

| Figure 8.1  | SRR output under representative AISC techniques 81         |

| Figure 8.2  | Impact on instruction mix and count 83                     |

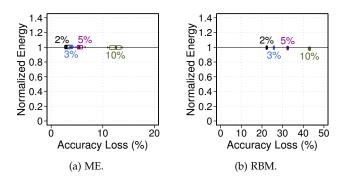

| Figure 8.3  | Energy vs. accuracy trade-off 84                           |

| Figure 8.4  | Accuracy of SRR output under Static-Drop 85                |

| Figure 8.5  | Energy vs. accuracy trade-off for Dynamic-Drop 86          |

| 0 5         |                                                            |

## LIST OF TABLES

| Table 1.1 | Dark silicon and post-Dennard scaling 4                |    |

|-----------|--------------------------------------------------------|----|

| Table 2.1 | Percentage of fault-free entries in a cache at 0.5 V 1 | 5  |

| Table 3.1 | Main characteristics of the modeled CMP system 2       | 2  |

| Table 3.2 | LLC MPKI for parallel workloads 24                     |    |

| Table 5.1 | Compression ratio required to store a 64-byte block    | 47 |

| Table 5.2 | Concertina storage requirements and fault coverage     | 56 |

| Table 5.3 | FM and CM overhead 59                                  |    |

| Table 7.1 | Benchmarks deployed (input parameters) 75              |    |

| Table 7.2 | Benchmarks deployed (outputs and accuracy metrics)     | 77 |

Part I

PRELIMINARIES

#### INTRODUCTION

It would appear that we have reached the limits of what it is possible to achieve with computer technology, although one should be careful with such statements, as they tend to sound pretty silly in 5 years.

John von Neumann, 1949

#### 1.1 RATIONALE

For the last 50 years, industry has enjoyed a long run of continuous technology improvements fueled by Moore's Law [114] and Dennard Scaling [46]. Scaling until 65 nm was rather straightforward, improving performance and power, while providing, at the same time, economic benefits. With each new generation, chips became smaller, more powerful, and cheaper to produce. However, semiconductor design has gotten more complicated, and after 22 nm, double patterning [138], 3D transistors [47], or new substrate materials such as FD-SOI [63] came into play, raising the production costs without yielding obvious power or performance benefits. With high-volume manufacturing at 7 nm scheduled for 2018 to 2019—and still not a clear substitute for CMOS—industry faces a complete paradigm shift: from designing for performance, to designing to satisfy the thermal design power of the end product.

Dennard Scaling Law has driven the semiconductors industry for the last decades. It states that as transistors get smaller, their power density stays constant, as both voltage and current scale down with length. In particular, the performance of a transistor can improve while preserving its operational characteristics if the parameters of a device (i.e., dimensions, voltages, and doping concentration densities) are scaled by a dimensionless factor S (Table 1.1). This technique is also called *constant field scaling* because as both voltage and distance shrink, the electric fields remain the same.

Industry generally scales process generations with  $S = \sqrt{2}$  (also called a 30% shrink). This way, the area of a transistor is reduced by a factor of 2. A 30% shrink with Dennard scaling translates into a 40% improvement in clock frequency, and it cuts power consumption per gate by a factor of 2. This power decrease allows to integrate more transistors in accordance to Moore's Law, keeping the same power budget. Over the last four decades, microprocessors featured size has improved more than two orders of magnitude, transistor budgets have multiplied by more than five orders of magnitude.

Unfortunately, CMOS scaling may be ultimately limited by leakage power. Scaling supply voltage ( $V_{dd}$ ) usually entails scaling the threshold voltage ( $V_{th}$ ) to keep performance<sup>1</sup>. But as  $V_{th}$  decreases, subtreshold leakage power

<sup>1</sup>  $V_{th}$  is the minimum transistor's gate-to-source voltage differential needed to create a conducting path between the source and drain terminal; the gate delay time decreases as the ratio  $V_{th}/V_{dd}$  does.

#### 4 INTRODUCTION

increases exponentially [156]. In the post-Dennard regime, smaller devices are more prone to leakage, and subtreshold leakage has changed from being negligible, to being a substantial fraction of the total power, reaching the same magnitude as the circuit's dynamic power [86]. Thus,  $V_{dd}$  and  $V_{th}$  are no longer scaling parameters, rather they are set by the results of a power optimization.  $V_{dd}$  and  $V_{th}$  have remained fairly constant (around 1 V and 300 mV, respectively) since the 65 nm node to limit leakage. In addition to this, variability increases as transistor dimensions shrink, as described by Pelgrom's model: the variance on the threshold voltage, the current factor, and the substrate factor are inversely proportional to the transistor area [121]. With each new process generation the complexity increases, reliability issues exacerbate, and new problems arise.

At the 65 nm node and beyond, scaling benefits, in terms of performance and power, started to diminish, but the engineering costs keep escalating. Scaling still provides a competitive advantage in a cutthroat industry, and vendors have taken advantage of the extra transistors integrating several processor cores on the chip in the form of homogeneous and heterogeneous chip multiprocessors (CMPs). However, integrating more resources on-chip does not mean that all the resources can be used simultaneously, because the power budget caps the amount of hardware that can be active at the same time. Hence, an exponentially increasing fraction of the chip area remains underclocked or dark—hence the term *dark silicon* [53, 147].

Table 1.1 describes the differences between Dennard and post-Dennard scaling. In the post-Dennard scaling era, for each new process generation, the total chip utilization for a fixed power budget drops by  $S^2$ , as a consequence of non-scaling  $V_{dd}$  and  $V_{th}$  parameters. The effect is illustrated in Figure 1.1, which shows ARM's prediction on dark silicon (assuming no design mitigation) for the next process generations [165]. The shaded regions on Figure 1.1 represent the percentage of dark silicon (i.e., transistors that cannot be turned on) expected at different technology nodes, with respect to a 28 nm reference process chip's power budget. Dark silicon is predicted to reach 80% of the chip's silicon at the 5 nm process<sup>2</sup>. Real products are likely to achieve better results through technology and design innovations, but power consumption is clearly a severe design constraint.

Figure 1.1 & Table 1.1: Dark silicon percentage with no design mitigation ([165]) as a consequence of post-Dennard scaling.

Improving system efficiency in the dark silicon era, without neglecting performance improvements, has led designers toward heterogeneous solutions [139]. These solutions include CMPs with multiple voltage domains [62,

<sup>2</sup> Dark silicon should not be understood as "useless" silicon, but as silicon that it is not used all the time or at its full frequency. For example, caches are dark silicon friendly: they contribute to the performance of the system, consuming power only on special situations.

129], integrated graphics processing units (GPUs) [22, 45], heterogeneous multi-cores with specialized accelerators [59], and intensive industry and academia research in novel technologies, including novel memory structures [112] and 3D integration [71]. We can expect to see an increase in the amount of resources dedicated to accelerators, and architectural changes focus on exploiting the characteristics of the emerging applications, such as approximate computing [113], accelerators for machine learning [97], or processing in memory [99]. In this dissertation, we focus on two trends to improve the energy efficiency of present and future systems: near-threshold voltage computing and approximate computing.

A very effective way of reducing the on-chip power consumption is reducing the supply voltage. Reducing V<sub>dd</sub> to values near the threshold voltagea technique known as Near-Threshold voltage Computing (NTC)-can decrease energy per operation up to 10x, at the cost of slower devices [30, 49]. The resulting power reduction could be used to activate more chip resources and potentially achieve performance improvements. Unfortunately, one of the main limitations of  $V_{dd}$  scaling is the tight margins of the on-chip Static Random Access Memory (SRAM) cache transistors. Excessive parameter variations in SRAM cells limit the voltage scaling of memory structures to a minimum voltage, below which SRAM cells may not operate reliably, and show a behavior consistent with a hard-fault. In this context, microarchitectural techniques can alleviate the performance and energy degradation that appears as a consequence of the reduction in the number of functional cache entries. In particular, the organization of the memory hierarchy on-chip and the applications running on the CMP themselves are a natural source of redundancy, offering a great opportunity to counteracting the performance degradation that appears as a result of the cache capacity degradation. SRAM reliability at near-threshold voltages is the focus of Part II of this dissertation, where we present micro-architectural techniques to mitigate the impact of SRAM cell failure when running at voltages near the threshold, based on exploiting the intrinsic redundancy of the memory hierarchy and the applications.

At the same time, as semiconductor industry advances and circuits become more sensitive to parameter variations and faults, it is highly energy inefficient to ensure fault-free computations. Fortunately, an increasingly large number of emerging applications, which are commonly referred as Recognition, Mining, and Synthesis (RMS), feature an intrinsic errorresilience property [37]. These applications often process noisy inputs (e.g., from sensors), run iterative probabilistic algorithms, and they usually do not require to compute a unique valid output, rather many outputs might be "acceptable" or "precise enough" [35]. Thus, approximate computing has drawn significant attention over the last years [113, 161]. The idea is to allow certain approximation or occasional violation of the specifications of a given algorithm, exploiting the gap between the level of accuracy required by the application and that provided by the computing system, potentially unlocking large energy gains. The main obstacle for approximate computing is effectively selecting which parts of the application code and data can be approximated [133]. Wrong decisions might lead to unacceptable results, which need to be re-computed, diminishing any potential energy benefit, or even worse, applications might crash or incur in security violations. Approximate computing is the focus of Part III of this dissertation, where we explore the possibilities of approximating the Instruction Set Architecture (ISA) itself, and analyze the impact of several ISA-shrinkage techniques on energy and accuracy.

#### 1.2 OBJECTIVES AND DISSERTATION OVERVIEW

The overall goal of this dissertation is to explore new approaches to improve the energy efficiency of future systems in the dark silicon era. We explore sources of natural on-chip redundancy and take advantage of them in the context of computing at voltages near the threshold and approximate computing. The rest of this dissertation is organized as follows:

- Part II presents our micro-architectural proposals to mitigate the impact of SRAM cell failures in last-level caches caused by process variations. It starts with an introduction to near-threshold voltage computing, discussing the reliability issues associated with it and the related work in Chapter 2. Chapter 3 details our methodology. Part II also includes two proposals, both based on taking advantage of the natural redundancy of content in the cache hierarchy. Chapter 4 explores how to take advantage of the memory hierarchy organization to minimize the performance loss in the presence of faulty cells, with minimal changes in the coherence protocol, by means of an intelligent cache management policy; Chapter 5 presents a novel approach based on compressing cache blocks, so they fit into cache entries with faults.

- Part III explores approximation at the ISA level to improve the energy efficiency of processors. As Part II, it begins with an introduction to approximate computing in Chapter 6, where we discuss the reasons of the increasing popularity of approximate computing and cover the related work. The methodology is discussed in Chapter 7. We explore the possibilities of approximating the ISA in several dimensions, e.g., simplifying instructions (Breadth) or even dropping them (Depth), and present a proof-of-concept in Chapter 8.

- Part IV concludes and discusses future research lines in Chapter 9.

#### 1.3 CONTRIBUTIONS

At the time this dissertation is being written, a large part of the work presented here has been published in peer-reviewed national and international conferences and journals, or is currently under review process.

The main contributions of this dissertation are:

- Contributions on SRAM reliability at near-threshold voltages (Part II):

- Based on block disabling techniques [142], we introduce a low complexity mechanism for inclusive cache hierarchies that permits cache blocks to use the non-functional last-level cache (LLC) data entries, by keeping operational the tag array. Thus, blocks allocated to disabled entries can be present in the private caches. We propose a fault-aware cache management policy that predicts the usefulness of a block based on its use pattern, and guides block allocation to faulty and non-faulty cache entries, accordingly.

This work has been published in the 26th International Symposium on Computer Architecture and High Performance Computing (October *2014).* An extended version of this work has been submitted to *IEEE Transactions on Parallel and Distributed Systems (submitted July 2016).*

- We provide the first analysis of requirements for compression techniques for shared LLCs running at ultra-low or near-threshold voltages. We propose the use of compression to improve cache utilization at ultra-low voltages, with a low-complexity combination-and remapping-free mechanism, maintaining the regular nature of SRAM cells. We present and evaluate cache management policies that match compressed blocks with faulty cache entries. This work has been published in *IEEE Transactions on Computers, Special Section on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (March 2016)*.

- Contributions on approximate computing (Part III):

- We propose to reduce the complexity of the ISA by shrinking it in two dimensions (Breadth and Depth) and approximate the execution of emerging RMS applications, exploiting the intrinsic noise tolerance of their algorithms. We present a proof-of-concept implementation and analyze the sensitivity of these applications to Breadth and Depth ISA shrinkage.

This work has been developed in collaboration with the Altai group of the University of Minnesota, and it has been submitted to *Design, Automation, and Test in Europe 2017 (submitted September 2016).*

#### 1.4 PROJECT FRAMEWORK

The realization of this dissertation was possible thanks to the support of the following awards and fellowships:

- 4-year PhD FPI grant from Spanish *Ministerio de Ciencia e Innovación,* including two complementary short stay grants:

- Compiler and Architecture Design Group, University of Edinburgh, United Kingdom (April - October 2013).

- Altai Lab, University of Minnesota, Twin Cities, United States of America (May August 2015).

- 4-month research stay at ARM Research, co-funded by HiPEAC PhD industrial internship program (October 2015 January 2016)

- Google Anita Borg Memorial Scholarship<sup>3</sup>, including €7,000 donation.

- Travel and assistance grants: Grace Hopper Celebration (2015, ABI, ACM, & Google), ISCA Conference (2015, IEEE), SBAC-PAD Conference (2014, U. Zaragoza), PACT Conference (2013, IEEE), ARCS Conference (2013, U. Zaragoza), HiPEAC Conference (2012, HiPEAC), JJ-PAR Conference (2012, U. Zaragoza) ACACES Summer School (2011 and 2014, HiPEAC).

Part of the work of this dissertation has been awarded the 3rd position at the ACM Student Research Competition<sup>4</sup> at the Grace Hopper Celebration of Women in Computing (October 2015), which included a \$300 donation.

<sup>3</sup> http://www.google.com/anitaborg/emea/

<sup>4</sup> http://src.acm.org/

#### 8 INTRODUCTION

This dissertation was realized in the framework of the following projects: *Interconexión y Memoria en Computadores Escalables* (TIN2010-212911) and *Memoria, Interconexión y Aplicaciones para Computadores Eficientes* (TIN2013-46957). HiPEAC has been a great supporter funding two Summer Schools, a conference grant, and partially funding an internship at ARM Research.

# Part II

# EXPLOITING REDUNDANCY FOR EFFICIENT CACHE OPERATION AT NEAR-THRESHOLD VOLTAGES

#### FROM DARK TO DIM SILICON: COMPUTING AT VOLTAGES NEAR THE THRESHOLD

One of the main obstacles to voltage scaling to values near the threshold is the minimum voltage supply of the SRAM on-chip structures. At lower voltages, devices are more sensitive to process variations, which impact circuit functionality, and eventually limit supply voltage reduction. SRAM cells are specially vulnerable because they are aggressively sized to meet high density requirements. In this chapter, we introduce near-threshold voltage computing and its challenges, including variability on SRAM cells at low supply voltage. Then, we present our reference SRAM reliability model and cover the related work.

#### 2.1 INTRODUCTION

Voltage scaling is one of the most effective ways to reduce the chip power consumption, as dynamic power scales quadratically with voltage. Modern chips implement Dynamic Voltage and Frequency Scaling (DVFS) schemes to run at different predefined voltage points and frequencies, trading off power consumption and performance, with a fixed (non-scaling) V<sub>th</sub> [65]. However, concerns about robustness and performance set the lower bound of supply voltage around 70% of the nominal V<sub>dd</sub> in commercial applications. As a matter of fact, CMOS circuits operate at very low voltages, and remain functional even at voltages below the threshold (V<sub>dd</sub> < V<sub>th</sub>)—this is called subthreshold computing—, but due to the large performance loss, their application is restricted to niche markets [85, 141, 154].

Figure 2.1 shows the energy per operation and delay when supply voltage scales down. By reducing  $V_{dd}$  from a nominal 1 V ( $V_{nom}$  in Figure 2.1) to 400-500 mV ( $V_{nth}$ ), we can obtain as much as 10x energy efficiency gain without incurring in the exponential performance degradation of subtreshold computing ( $V_{dd} < 300$  mV). This technique is referred to as Near-Threshold voltage Computing (NTC) [49]. While reducing  $V_{dd}$  below  $V_{th}$ reaches the minimum point of energy per operation, the consequent performance degradation may be unacceptable for the vast majority of applications [23].

Researchers have looked at x86-based NTC implementations [67] and 3D many-core ARM-based implementations [48], but several key challenges have prevented the general adoption of NTC, namely: i) 10x loss in performance due to the frequency degradation, ii) 5x increase in performance variation due to parameter variations, and iii) five orders of magnitude increase in functional failure rate of memory as well as increased logic failures.

To compensate for the performance loss, the power budget resulting from scaling  $V_{dd}$  can be used to switch on more cores. Throughput applications, such as graphics-like workloads with minimal emphasis on each thread, or parallel applications, such as high-performance computing ones, are the strongest matches for NTC. These applications can take advantage of a big pool of cores, even if they run at slower frequencies. As power consumption decreases more from operating at low  $V_{dd}$  than it increases from operating

Figure 2.1: Energy per operation and delay with respect to supply voltage.

more cores in parallel, the result is still a power reduction [30]. Single-thread performance could still be achieved with voltage/frequency boosting of a low-power core, or by a high-performance core added to the system [122].

Parameter variations-the deviation of device parameters from their nominal specifications—are already present at nominal V<sub>dd</sub> [20]. The sources of parameter variations include manufacturing-induced sources (process variations) and environmental ones (supply voltage and temperature). CMOS gates are robust, and they generally work correctly when parameters vary enormously. However, in the presence of parameter variations, chips have regions that run at different speed and have different power consumption. Designers usually account for parameter variations inserting conservative margins or guardbands to cover against the worst-case variation, increasing nominal voltage up to 20% [70]. This worst-case guided design incurs in large performance and power losses, as the worst case might be far from the nominal specifications, and the worst case condition can be severe, but infrequent [126]. At NTC the problem exacerbates, because the same amount of variation causes larger changes in the device speed and power [106], and relying on the worst-case operating margins is not practical, as frequency is already low. Architectural and circuit solutions can provide variation tolerance and adaptivity [49, 78, 79].

Next, we cover the main causes of functional failure of on-chip memory structures when running at near-threshold voltages.

#### 2.2 PROCESS VARIATIONS IN SRAM CELLS

Static Random Access Memory (SRAM) is the most widely used form of on-chip memory. They are faster than their dynamic counterparts (DRAM), avoiding the periodic refresh phases, but require more area per bit. SRAMs use a memory cell with internal feedback that retains its value as long as a power is applied. A traditional 6T SRAM cell, such as the one shown in Figure 2.2, consists of four transistors that form two cross-coupled inverters (PL-NL and PR-NR), and two access transistors (AXL and AXR).

Figure 2.2: 6T SRAM cell architecture.

A 6T SRAM cell is susceptible to five types of failures: read upset, during read operation, the cell flips its content; read access, during read operation, the time needed to produce a voltage difference between the two bitlines, BL and BR, exceeds the period that the wordline, WL, stays high; write stability, during write operation, even if the write duration is extended to infinity, the cell cannot change its logic state; write timing, during write operation, the cell is unable to change its logic state by the end of the designated time duration; and *hold*, the value of the cell is flipped by excessive leakage on the constituent transistors. To ensure both read stability and writability, the transistors must satisfy ratio constraints. The stability and writability of the cell are quantified by the hold margin, the read margin, and the write margin, which are determined by the static noise margin of the cell in its various modes of operation. The hold margin increases with  $V_{dd}$  and  $V_{th}$ ; read margin improves by increasing  $V_{dd}$  or  $V_{th}$ , or by reducing the WL voltage relative to V<sub>dd</sub>; the write margin improves as the access transistor becomes stronger, the pull-up becomes weaker, or the wordline voltage increases. Therefore, write and read improvements are conflicting with each other.

SRAM structures are especially vulnerable to process variations [18], since they are aggressively sized to meet high density requirements, and due to the vast number of cells that comprise the on-chip memory structures, which nowadays account for even more than half of the chip area [26]. Process variations can be classified into inter-die and intra-die. Inter-die variations eventually cause performance differences across chips, and they can be handled by adding enough margin and rejecting chips that do not meet certain specifications. Intra-die variations are gaining importance as technology scales, because chips integrate millions or billions of transistors, and, very likely, some of them will fail outside the specification corners. Intradie variation has a systematic and a random component. The systematic component is typically caused by lithographic irregularities, mainly affecting channel length. The random component is caused by varying dopant fluctuations (Random Dopant Fluctuation or RDF), and it is the main cause of  $V_{th}$  variation [146]. Specifically,  $V_{th}$  is determined by the number and location of dopant atoms implanted in the transistor channel region. The stochastic nature of ion implantation leads to different  $V_{th}$  values across the chip.

The resultant threshold mismatch reduces the available cell noise margins, creating a distribution of read, write, and hold margins across the SRAM

structure, and some of the cells become unstable. An unstable cell flips during a read operation, fails to switch during a write operation, or loses its state during hold, causing a circuit behavior consistent with a hard fault. Because the static noise margins depend on  $V_{dd}$ , SRAMs have a minimum voltage at which they can reliably operate. This voltage is  $V_{dd_{min}}$  and it is typically of the order of 0.7–1.0 V in current technology nodes, when 6T cells are employed, and presents an obstacle to continued voltage scaling.

Modern CMPs implement multi-level on-chip SRAM cache hierarchies, usually composed of two or three cache levels, with different cell design objectives, depending on the importance of performance and leakage. In general, first-level caches occupy little area and their access time often determines the processor cycle time; circuit techniques such as larger 8T SRAM cells [29] are utilized to minimize the impact of variation [91]. Last-level caches (LLCs), on the other hand, have larger size and associativity, and occupy a great percentage of the chip area; smaller and less leaky cells are preferred to achieve more density, but the structure is more prone to errors due to variability [18].

To allow circuit operation at lower V<sub>dd</sub>, some commercial processors have different voltages for logic and memory. For instance, Intel® Medfield operates the L2 cache at 1.05 V, while the CPU cores can scale down to 0.7 V [166]. Separate voltage domains complicate chip design [105], and scaling will likely increase the differences between voltage domains for logic and memory, eventually increasing the number of voltage domains required, and diminishing the power reduction benefit of operating chips at lower voltages. Our objective is to reduce the supply voltage of the whole chip and mitigate the impact of process variations on the SRAM cells of the large on-chip cache structures (i.e., the LLC). We achieve this objective through micro-architectural techniques, which take into account the organization of the memory hierarchy within a CMP, and the nature of the applications running on them. We identify two levels of natural on-chip data redundancy: cache level and content level. The first arises because of the natural replication of blocks in inclusive cache hierarchies, designed to exploit the temporal locality of the data. The latter arises because of the redundancy of data in real world applications. We exploit these two levels of redundancy through fault-aware cache management policies, relying on the underlying coherence protocol and replacement policy.

#### 2.2.1 Reference SRAM Reliability Study

Many authors have extensively analyzed the robustness of SRAM cells under the  $V_{dd_{min}}$  range [3, 4, 24, 27, 32, 77, 83, 167]. Zhou *et al.* describe six 6T SRAM cells of different sizes in 32 nm technology, and how their probabilities of failure change with the voltage supply and the size of the constituent transistors [170]. According to Zhou *et al.*, at 0.5 V (our target near-threshold voltage) the probability of failure ( $P_{fail}$ ) of a standard SRAM cell ranges between 10<sup>-3</sup> and 10<sup>-2</sup>. Larger cells have a lower probability of failure because non-uniformities in channel doping average out with larger transistors, resulting in more robust devices, but at the price of larger area, and higher energy consumption. Table 2.1 describes the six SRAM cells of Zhou's study (C1, C2, C3, C4, C5, and C6) with their areas relative to the smallest cell (C1), as well as the percentages of non-faulty entries of a cache implemented with

the cells at 0.5 V, assuming 64-byte cache entries<sup>1</sup>. An entry is considered faulty if it contains at least one defective bit. Failures are randomly distributed, but uniform within a given chip [2, 36], so they can be modeled following the Bernouilli distribution with  $p = p_{fail}$ . As Table 2.1 shows, only 10% of the cache entries are non-faulty for the small C2 cell at our target voltage of 0.5 V. If the cache is implemented with the more robust C6 cells, the percentage of non-faulty cache entries rises to 60%, but at the cost of a 41.1% increase in area (relative to C2) and the consequent increase in leakage, which is not a viable option for a large structure such as the on-chip LLC.

Table 2.1: Area relative to cell C1 and percentage of non-faulty 64-byte entries in a cache operating at 0.5 V, for the six bit cells introduced in [170].

| Cell type     | C1   | C2   | C3   | C4   | C5   | C6   |

|---------------|------|------|------|------|------|------|

| Relative area | 1.00 | 1.12 | 1.23 | 1.35 | 1.46 | 1.58 |

| % non-faulty  | 0.0  | 9.9  | 27.8 | 35.8 | 50.6 | 59.9 |

In this dissertation, we use Zhou's study as SRAM reliability model to test our proposals on a wide range of failure probabilities. We consider C2 to C6 operating at 0.5 V, as at such voltage, a cache built with C1 cells would have all its capacity compromised.

#### 2.3 RELATED WORK

Solutions proposed to date to address the variability in SRAM cells at ultralow voltages can be arranged into two groups: circuit and micro-architectural techniques.

#### 2.3.1 Circuit Solutions

Circuit solutions include proactive methods that improve the bit cell characteristics by increasing the SRAM cell size or adding assist/spare circuitry.

Larger transistors reduce  $V_{th}$  variability, since nonuniformities in channel doping average out, and result in more robust devices with a lower probability of failure [170]. Another approach to reducing variability is to add assist read/write circuitry by increasing the number of transistors per SRAM cell. Some examples are 8T [29], 10T [24], or Schmitt Trigger-based (ST) SRAM cells [90]. Increasing the SRAM cell size or the number of transistors per cell comes at the cost of significant increases in the SRAM area (lower density) and in energy consumption. For example, the use of ST SRAM cells doubles the area of the SRAM structure, which is not practical for large structures such as on-chip LLCs.

Spare rows/columns can be used to replace faulty rows/columns and improve yield [137], but this technique has obvious limitations in the amount of faulty rows/columns it can handle, due to resource limitations, area scaling rate, and design complexity. For example, Intel includes 2 bits per cache entry to replace defective bits [26].

<sup>1</sup> In this dissertation, we assume 64-byte cache entries without any loss of generality; all techniques described here could be easily applied to other cache entry sizes.

A different approach is to provide separate voltages for logic and memory [166], but separate voltage domains complicate chip design [92, 105]. Moreover, scaling will likely increase the differences between voltage domains for logic and memory, which eventually increases the number of voltage domains required, and diminishes the potential benefit of operating chips at low voltages.

#### 2.3.2 Micro-architectural Solutions

From the micro-architectural perspective, excessive parametric variability can cause circuit behavior consistent with a hard fault. Several runtime methods have been proposed to mitigate its impact, including redundancy through Error Correcting Codes (ECCs), disabling techniques, and the combination of faulty resources to recreate functional ones.

ECCs are extensively employed to protect designs against soft errors, and they have also been studied in ultra-low voltage contexts to protect against hard errors [6, 39]. To store an ECC, the capacity of the cache must be extended or part of its effective capacity has to be sacrificed. ECCs are usually optimized to minimize their storage requirements, at the cost of more complex logic to detect and correct errors. Thus, correcting more than two errors requires a high latency overhead or encodings with more check bits as described in [39], where half of the cache capacity is dedicated to storing the ECC. To reduce storage overhead, Chen *et al.* propose to store ECCs in the unused fragments that appear as a result of compression [33]. Finally, it is worth noting that the use of ECCs to protect against hard errors will jeopar-dize resilience to soft errors.

A simple approach to mitigating hard faults is to disable faulty entries<sup>2</sup> (cache entries with faulty bits, which cannot store a complete cache block) [142]. This technique, called *block disabling*, is already implemented in modern processors to protect against hard faults [26, 44]. Block disabling has been studied at ultra-low voltages because of its easy implementation and low overhead (1 bit per entry sufficing). However, the large number of faults at low operating voltages implies a large percentage reduction in cache capacity and associativity. For instance, for C2, although defective bits represent around 0.5% of the total, only 9.9% of the capacity is available (Table 2.1). Lee *et al.* examine performance degradation by disabling cache lines, sets, ways, ports, or the complete cache in a single processor environment [94]. To compensate for the associative loss, Ladas *et al.* propose the implementation of a victim cache in combination with block disabling [93].

Ghasemi *et al.* propose the use of heterogeneous cell sizes, so when operating at low voltages, ways or sets of small SRAM cells are deactivated if they start to fail [56]. Khan *et al.* propose a mixed-cell memory design, where a small portion of the cache is implemented with robust cells, which store dirty cache blocks, and the remainder with non-robust cells [81]. They modify the replacement policy to guide the allocation of blocks based on the type of request (load or store). Zhou *et al.* combine spare cells, heterogeneous cell sizes, and ECCs into a hybrid design to improve on the effectiveness obtained by any of the techniques applied alone [170].

16

<sup>2</sup> In this dissertation we make the distinction between cache block and cache entry: block is the transfer unit, the content *per se*; entry is the physical set of cells that store a block.

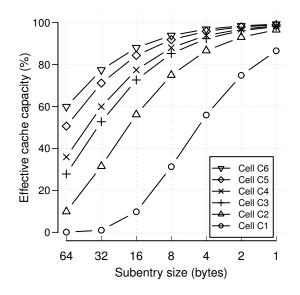

Figure 2.3: Potential cache capacity that can be used by tracking faults at finer granularities for different SRAM cell sizes.

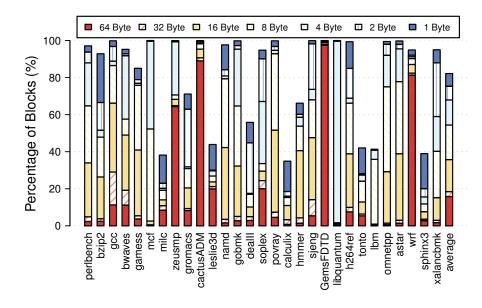

The granularity of the disabled storage might be finer, but at the cost of a larger overhead. Cache entries can be divided into subentries of a given size. A defective cell implies disabling just the subentry which it belongs to, rather than the whole entry. Figure 2.3 shows for the six SRAM cells from Zhou's study, the potential cache capacity that can be used by tracking faults at finer granularities (different subentry sizes). For example, a cache implemented with cells C3-C6 could potentially use more than 80% of the cache capacity by disabling 8-byte subentries.

Previous proposals take advantage of this observation. Word disabling tracks defects at word-level granularity, and then combines two consecutive cache entries into a single fault-free entry, halving both associativity and capacity [157]. Abella *et al.* bypass faulty subentries rather than disabling full cache lines, but this technique is suitable only for the first-level cache, where accesses are word wide [1]. Palframan *et al.* follow a similar approach, patching faulty words from other microprocessor structures, such as the store queue or the miss status holding register [118].

More complex schemes couple faulty cache entries using a remapping mechanism [12, 17, 88, 104]. They rely on the execution of a complex algorithm to group collision-free cache entries from the same or different cache banks, and on additional structures to store the mapping strategy. For example, Archipelago divides the cache into autonomous islands, where one entry is sacrificed to allocate data portions of other entries; they use a configuration algorithm (based on minimum clique covering) to create the islands [12]. The remapping mechanism adds a level of indirection to the cache access (increasing its latency), and the combination of cache entries to recreate a cache block adds complexity.

All of these combination or remapping strategies have a major inconvenience: to reconstruct cache blocks several cache accesses are needed, increasing the energy consumption and/or the latency per block access. Unlike the aforementioned proposals, an ideal fault-tolerant mechanism would not compromise cache capacity, associativity, or latency.

#### 2.3.2.1 Cache Management Techniques

Our first main contribution relies on a smart insertion and replacement policy to handle faulty and non-faulty cache entries. In the context of ultra-low voltages, Keramidas *et al.* use a PC-indexed spatial predictor to orchestrate the replacement decisions among fully and partially usable entries in firstlevel caches [80]. We base our allocation predictions in the reuse patterns, which simplifies the hardware, and we do not consider the use of partially faulty entries.

Regarding the implementation of our techniques, it is worth referring to the work of Jaleel *et al.* [68]. In inclusive hierarchies, the private caches filter the temporal locality and hot blocks (i.e., blocks being actively used by the processor) are degraded in the replacement stack of the LLC to be eventually evicted. The authors address this problem by protecting blocks present in the private caches and preventing their replacement in the LLC through several techniques, including: sending hints to the LLC, identifying temporal locality via early invalidation, or querying the private caches about the presence of blocks. We also protect private copies on all our replacement policies using the coherence information and assuming non-silent evictions of clean blocks.

Albericio *et al.* base the replacement decisions on the block reuse locality [9]. They propose the *Not-Recently Reused* (NRR) algorithm, which protects blocks present in the private caches and blocks that have shown reuse in the LLC. Their simple yet efficient implementation improves the performance of more complex techniques such as RRIP [69]. We build our cache management policy on top of this algorithm.

#### 2.3.2.2 Compression Techniques

Our second main contribution relies on compressing cache blocks to fit into the still available LLC capacity. This approach avoids complex cache block remapping, and the combination of faulty cache entries to recreate fully functional ones.

Several compression mechanisms have been proposed in the literature to increase the effective storage capacity of all the on-chip cache levels, potentially reducing misses and improving performance [8, 34, 51, 87, 119, 135, 162]. In general, these proposals seek to maximize the compression ratio either to store more than one block in each cache entry, or to reduce the energy consumption of each LLC access. However, ultra-low voltage operation sets different requirements for the compression scheme: most of the blocks need to be compressed to fit into faulty entries, but the compression ratio is relatively small. In an ideal case, where all blocks could be compressed to fit into the available space, neither capacity nor associativity would decrease. Similar requirements may be observed in the context of Non-Volatile Memories (NVM) to enlarge their durability [57, 160].

We combine the compression mechanism with a smart allocation/replacement policy, which assigns cache blocks to faulty entries based on their compressibility. Two recent studies have indicated the importance of taking compression information into account for a replacement policy tailored to on-chip caches implementing compression [14, 120]. Both studies are based on the fact that several blocks are allocated to the same cache entry and, therefore, prioritizing the replacement of large blocks might allow the allocation of several smaller blocks to the same space. In ultra-low voltage operation, the compression ratio must be taken into account in the replacement decision as well, but in order to even out the pressure on the entries of a cache set.

# EXPERIMENTAL FRAMEWORK

This chapter presents the experimental framework used during Part II of the dissertation, including the modeled system, the experimental set-up, and the metrics to quantify the impact of the proposed techniques. Specific details might change for the evaluation of some of the ideas of this dissertation. In that case, those details are properly explained when required.

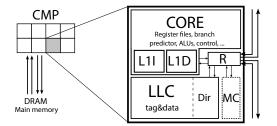

# 3.1 OVERVIEW OF THE MODELED SYSTEM

Our baseline system consists on a tiled chip multiprocessor (CMP), with an inclusive two-level cache hierarchy, where the second level or last-level cache (LLC) is shared and distributed among the processor cores. Tiles are interconnected by means of a two dimensional mesh, in a similar way as Phytium's Mars [76]. Each tile has a processor core with a private first level cache (L1) split in instructions and data, and a bank of the shared LLC, both connected to the router (Figure 3.1). The cache write policies are writeback and write-allocate. LLC banks are interleaved by cache line address, and inclusion is enforced at the LLC; i.e., when a cache line is inserted in L1, it is also inserted in the LLC, and when a line is evicted from the LLC, it is replaced from the private levels, too. Two memory controllers are distributed on the edges of the chip. Table 3.1 shows the parameters of the baseline processor, memory hierarchy, and interconnection network. During the next chapters, when necessary, we will detail the parameters that differ from the baseline configuration system.

Figure 3.1: Tiled CMP with 8 processors.

At lower voltages near to the threshold voltage, frequency degrades about 5 to 10x [49]. We assume a frequency of 1 GHz at 0.5 V, our target  $V_{dd}$ . Note that the DRAM module voltage is not scaled as the rest of the system. Thus, the relative speed of main memory with respect to the chip gets faster as the voltage decreases. This model is consistent with prior work [12, 157].

Our baseline coherence protocol relies on a full-map directory with MESI states (Modified, Exclusive, Shared, and Invalid). We use explicit eviction notification of both shared and exclusively owned blocks. L1 caches are built with robust SRAM cells and, therefore, they can run at lower voltages without suffering from parameter variations, while LLC banks are built with conventional 6T SRAM cells, so they are sensitive to failures [91].

| Cores                 | 8, Ultrasparc III Plus, in-order, 1 instr/cycle, single-threaded 1 GHz at $\rm V_{dd}$ 0.5 V                                                                                                                    |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Coherence<br>Protocol | MESI, directory-based full-map dist. among LLC cache banks                                                                                                                                                      |

| Consistency           | Sequential                                                                                                                                                                                                      |

| L1 cache              | Private, 64 KB data and inst. caches, 4-way, 64 B block size, LRU 2-cycle hit access time                                                                                                                       |

| LLC cache             | Shared, 1 bank/tile, 1 MB/bank, 16-way, 64 B block size, pseudo-LRU <sup>a</sup><br>Inclusive, interleaved by line address<br>8-cycle hit access time (4-cycle tag access)                                      |

| Memory                | 2 memory controllers, distributed on the edges of the chip<br>Double Data Rate (DDR3 1333 MHz), 2 channels, 8 Gb/channel<br>8 banks, 8 KB page size, open page policy<br>Raw access time 50 cycles <sup>b</sup> |

| NoC                   | Mesh, 2 Virt. Networks (VN): requests and replies<br>16-byte flit size, 2-stage routers, 1-cycle latency hop                                                                                                    |

Table 3.1: Main characteristics of the modeled CMP system.

<sup>*a*</sup> Chapter 4 assumes NRU [145], while Chapter 5 assumes LRU; in both cases, the baseline replacement policy protects the private copies of the blocks [68].

<sup>*b*</sup> When the CMP runs at 1 GHz/0.5  $V_{dd}$ .

#### 3.2 SIMULATION FRAMEWORK

Regarding our experimental set-up, we use *Simics*, a multiprocessor fullsystem simulator, running the *Solaris 10* operating system [102]. To model a detailed and cycle-accurate on-chip memory hierarchy and interconnection network, we use the *ruby* plugin from GEMS Multifacet's multiprocessor simulator toolset [107]. During this dissertation, we enlarge the ruby module to faithfully model our different proposals. In order to get a detailed performance and energy DDR<sub>3</sub> DRAM model, we incorporated DRAMSim2 into our simulation infrastructure [128]. To get timing, area, and energy consumption we use McPAT framework [95] for the on-chip components, and DRAMSim2 for the DRAM module.

#### 3.3 WORKLOADS AND METHODOLOGY

We consider two sets of multiprocessor workloads exhibiting different kinds of parallelism. On the one hand, multiprogrammed workloads are a combination of several sequential programs of different nature and behavior running at the same time in the system; i.e., there are as many independent tasks as processor cores. These workloads are representative of, for example, desktop systems running different applications or servers running different user requests. We use the 29 programs from the SPEC CPU 2006 benchmark suite [61]. SPEC CPU 2006 is an industry-standardized, CPUintensive benchmark suite, stressing a system's processor, memory subsystem, and compiler. It contains two suites that focus on two different types of compute intensive performance: the CINT2006 (integer) suite measures compute-intensive integer performance, and the CFP2006 (floating point) suite measures compute-intensive floating point performance. On the other hand, parallel workloads are shared-memory applications; i.e., one task is divided along the available processor cores. Parallel applications are mainstream in today's CMPs. We use applications from the PAR-SEC benchmark suite [19]. The PARSEC suite focuses on emerging workloads and was designed to contain a diverse selection of applications that is representative of next-generation shared-memory programs for CMPs.

Next, we present the selected workloads and methodology in depth.

#### 3.3.1 Multiprogrammed Workloads

To select the appropriate number of workloads, we use a set of 100 workloads built as random combinations of the 29 SPEC CPU 2006 programs, with no special distinction between integer and floating point. The applications appear from 16 to 35 times, the average number of occurrences is 27.6, with a standard deviation of 4.5.

In order to locate the end of the initialization phase, all the SPEC binaries with the reference inputs were run until completion with hardware counters enabled. To ensure that no application was in its initialization phase, each multiprogrammed mixed was run for as many instructions as the longest initialization phase, and a checkpoint was created at that point. From that point, we run cycle-accurate simulations including 300 million cycles warm-up of the memory hierarchy and 700 million cycles of statistics collection.

To reduce the experimental workload, highly loaded with the Monte Carlo simulations discussed in the following sections, we compute the minimum number of mixes needed to obtain statistically representative results. Following statistical sampling [153], and assuming a confidence interval of  $(1 - \alpha) = 0.95$  and error tolerance  $\varepsilon = 5\%$ , we can compute the minimum number of mixes n as:

$$n \ge \left(\frac{z * V_x}{\varepsilon}\right)^2 \tag{3.1}$$

where z is the  $100[1 - \frac{\alpha}{2}]$  percentile of the standard normal distribution, and  $V_x$  is the coefficient of variation of the population. As  $V_x$  of the entire population is not available, we use sample  $\hat{V}_x$ . Our initial sample size is n = 100 (mixes). We obtain the coefficient of variation  $\hat{V}_x = 0.10901$ , based on the total number of instructions executed for each mix. As z = 1.96, the minimum number of mixes is  $n \ge 18.26$ .

Thus, we select 20 workloads built as random combinations of the SPEC CPU 2006 programs. Each application appears on average 5.5 with a standard deviation of 2.5.

To evaluate the behavior of multiprogrammed workloads for the different proposals, we use LLC Misses Per Kilo Instruction (MPKI) and speedup. Speedup for a given mix is computed as in Equation 3.2, where  $IPC_i^A$  is the number of executed instructions per cycle of program i when it runs in system *A*, and  $IPC_i^{Base}$  is the number of executed instructions per cycle when it runs in the Base system (baseline). Note that as we always run a

#### EXPERIMENTAL FRAMEWORK

fixed number of cycles, this is equivalent to using the number of instructions executed.

Speedup =

$$\sqrt[n]{\prod_{i=1}^{n} \frac{IPC_{i}^{A}}{IPC_{i}^{Base}}}$$

(3.2)

As the different mixes are run for equal parts on the baseline system, as well as on the different configurations, the arithmetic mean of individual speedups is used when summarizing results for all the workloads [72].

#### 3.3.2 Parallel Workloads

We use a selection of shared-memory parallel applications from PARSEC with a significant memory footprint when using the *sim-large* input (i.e., MPKI<sub>LLC</sub>  $\ge$  1 in the baseline system, Table 3.2).

Table 3.2: LLC MPKI for parallel workloads (baseline system).

|                     | canneal | ferret | streamcluster | vips |

|---------------------|---------|--------|---------------|------|

| MPKI <sub>llc</sub> | 4.26    | 1.59   | 1.00          | 1.19 |

Parallel applications should run until completion in order to compare the performance of different design alternatives. However, in our applications, no OS activity appeared when parallel applications were run, and the ratio of load of work among the different threads was practically constant between simulations. Thus, following the same approach as [10], we use sampling, and the same way than for multiprogrammed workloads, we run 300 million cycles of warm-up of memory structures once the parallel phase has started, and then collect statistics for 700 million execution cycles.

The speedup is computed as in Eq. 3.3, where  $I_i^A$  is the number of executed instructions of thread i when it runs in system A, and  $I_i^{Base}$  is the number of executed instructions when it runs in the Base system.

$$Speedup = \frac{\sum_{i=1}^{n} I_i^A}{\sum_{i=1}^{n} I_i^{Base}}$$

(3.3)

#### 3.4 SRAM FAILURE MODEL

Random intra-die variations are modeled as random variables and used as inputs to determine the failure probability or  $P_{fail}$  of a given SRAM cell. We can assume that failures are randomly distributed, but uniform within a given chip [2, 36]. Thus, we create fault maps with different distribution of failures for each  $P_{fail}$  point. We follow Zhou *et al.* study, described in Chapter 2, and modeled five configurations (C2-C6) with 6T SRAM cells of different sizes (i.e.,  $P_{fail}$  points) [170]. To create the fault maps for each configuration, we compute the faultiness of each memory cell randomly and independently of other cells, obtaining configurations with similar number of faults, but different locations, and run Monte Carlo simulations as follows.

24

For each design point, we run N configurations (fault maps) and compute the sample mean ( $\bar{X}$ ). The accuracy of the sample mean will improve as we increase the number of samples (number of fault maps or N), but if we set the number of samples too large, we will do unnecessary computation without gaining meaningful accuracy.

To obtain representative results, we follow the methodology summarized below. Our target error is  $\varepsilon = 5\%$  with a confidence level  $(1 - \alpha) = 0.95$ .

- Step 1. We set an initial value of samples N and collect results to compute the sample mean  $\bar{X}$  and the sample variance of a selected metric S<sup>2</sup> according to equation  $3.4^{1}$ .

- Step 2. Given the confidence level  $(1 \alpha) = 0.95$  and error tolerance  $\varepsilon = 5\%$ , we check if equation 3.5a is satisfied<sup>2</sup>. If so, we claim that the stopping criteria has been achieved and stop the simulation. Otherwise, we increase the number of samples N' according to equation 3.5b, and repeat from Step 1.

$$\bar{X} = \frac{x_0 + x_1 + \dots + x_{N-1}}{N}$$

(3.4a)

$$S^{2} = \frac{\sum_{i=0}^{N-1} (x_{i} - \bar{X})^{2}}{N-1}$$

(3.4b)

$$\left(\frac{\mathsf{t}_{[\mathsf{N}-1,\frac{\alpha}{2}]} \times \mathsf{S}}{\mathsf{N} \times \bar{\mathsf{X}}}\right)^2 \leqslant \varepsilon \tag{3.5a}$$

$$\mathsf{N}' \ge \left(\frac{\mathsf{t}_{[\mathsf{N}-1,\frac{\alpha}{2}]} \times \mathsf{S}}{\varepsilon \times \bar{\mathsf{X}}}\right)^2 \tag{3.5b}$$

Note that we could use different metrics in Step 1 to compute the sample mean and sample variance to check if we have reached our target error. Nevertheless, as we are interested in comparing throughput by means of speedups, we also consider speedup to compute the error.

For the sake of clarity, we avoid plotting error bars in the different results graphs of this dissertation, providing that all the results are within the error and confidence levels here described.

<sup>1</sup> Note that we use (N - 1) to compute the unbiased S<sup>2</sup> (Bessel's correction).

$<sup>2 \</sup> t_{[N-1,\frac{\alpha}{2}]}$  is obtained from the t-distribution function with N-1 degrees of freedom.

# 4

# EXPLOITING REDUNDANCY AT CACHE LEVEL

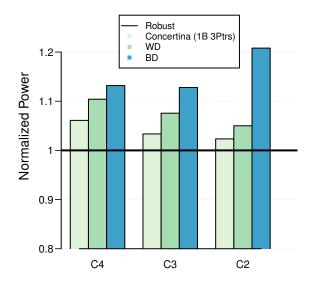

This chapter presents a cache management policy to enable efficient last-level cache (LLC) operation at low or near-threshold voltages. We base our proposal on block disabling, a micro-architectural technique that tolerates faults by deactivating faulty cache entries. Block disabling's main drawback is that, given the random component of SRAM cell faults, both cache associativity and capacity rapidly degrade as the number of defective cells increases. We take advantage of the on-chip coherence and replacement mechanisms to enhance block disabling performance, without any additional cost. For that, we exploit the natural redundancy of multi-level inclusive cache hierarchies and extend the LLC with a fault-aware cache management policy, which maps blocks with a higher probability of being used to operative cache entries. Our evaluation shows that this fault-aware management can reduce MPKI by up to 37.3% for multiprogrammed workloads, and by 54.2% for parallel ones, with respect to block disabling. This translates into performance enhancements of up to 13% and 34.6% for multiprogrammed and parallel workloads, respectively.

# 4.1 INTRODUCTION

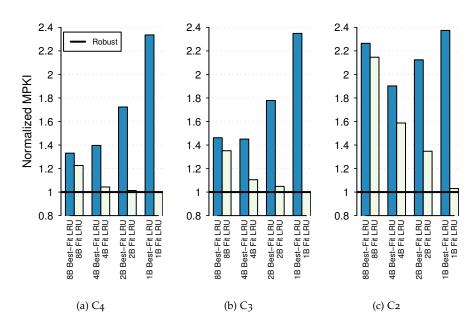

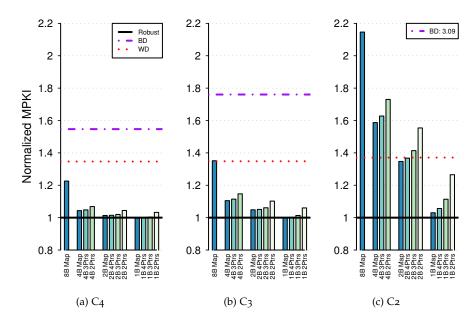

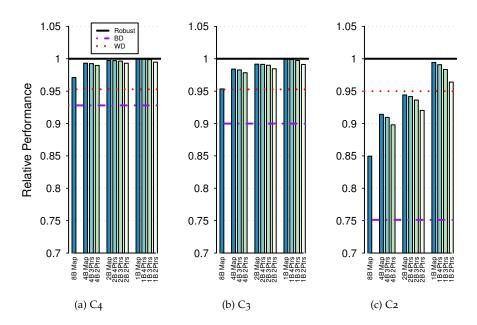

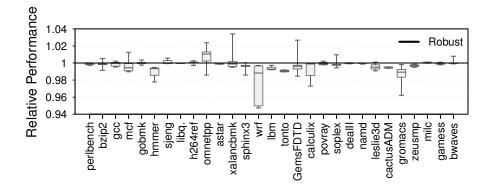

Modern chip multi-processors (CMPs) include several cache levels to reduce the gap between the speed of the processor and the access latency to the main memory. On-chip caches are usually built with SRAM cells, which are sensitive to process variations, specially when operating at low or nearthreshold voltages [18]. First-level caches are usually private, occupy little area, and their access time often determines the processor cycle time. Commercial processors, such as the Intel Nehalem family, use robust 8T SRAM cells to build reliable first-level caches, since it represents an affordable overhead [91]. On the contrary, LLCs are usually shared and have larger size and associativity, accounting for much of the die area [26]. Thus, minimumgeometry 6T cells are preferred to achieve higher density, with the consequent higher sensitivity to failures.