2011

24

Francisco Aznar Tabuenca

# CMOS receiver design for gigabit short-range optical communications

Departamento

Ingeniería Electrónica y Comunicaciones

Director/es

Celma Pueyo, Santiago Calvo Lopez, Belen Teresa http://zaguan.unizar.es/collection/Tesis

#### **Tesis Doctoral**

# CMOS RECEIVER DESIGN FOR GIGABIT SHORT-RANGE OPTICAL COMMUNICATIONS

**Autor**

Francisco Aznar Tabuenca

Director/es

Celma Pueyo, Santiago Calvo Lopez, Belen Teresa

#### UNIVERSIDAD DE ZARAGOZA

Ingeniería Electrónica y Comunicaciones

2011

# CMOS RECEIVER DESIGN FOR GIGABIT SHORT-RANGE OPTICAL COMMUNICATIONS

Francisco Aznar Tabuenca

Grupo de Diseño Electrónico – I3A Departamento de Ingeniería Electrónica y Comunicaciones Facultad de Ciencias Universidad de Zaragoza

# DISEÑO DE RECEPTOR CMOS PARA COMUNICACIONES ÓPTICAS GIGABIT DE CORTO ALCANCE

Memoria de la tesis doctoral realizada por

D. Francisco Aznar Tabuenca

Bajo la dirección de los doctores

Dr. Santiago Celma Pueyo y Dra. Belén Calvo López

Para optar al grado de

Doctor en Física

Grupo de Diseño Electrónico – I3A Departamento de Ingeniería Electrónica y Comunicaciones Facultad de Ciencias – Universidad de Zaragoza

# CMOS RECEIVER DESIGN FOR GIGABIT SHORT-RANGE OPTICAL COMMUNICATIONS

A thesis submitted to the University of Zaragoza in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in Physics

By

#### Francisco Aznar Tabuenca

Thesis Supervisors

Prof. Santiago Celma Pueyo and Belén Calvo López

Electronic Design Group – I3A

Department of Electronic Engineering and Communications

Faculty of Sciences – University of Zaragoza

## **AGRADECIMIENTOS**

En muchas ocasiones es difícil encontrar las palabras adecuadas para expresarse como uno realmente desea. En las siguientes líneas intentaré llevar a cabo esta tarea sin olvidarme de nadie, aunque ya adelanto que no prometo nada.

Lo primero de todo, como no podía ser de otra manera, debo agradecer a mis directores de tesis, Santiago Celma y Belén Calvo, el trabajo de supervisión y dirección realizado durante estos años. A su lado, me he enriquecido enormemente como persona y como investigador, en ese orden.

A Nicolás, Concha, Pedro, Pepe por el conocimiento mostrado en las clases antes de formar parte de este grupo, y por la acogida y buenos momentos que me han hecho disfrutar. A Oscar, por todos los favores que le he tenido que pedir y por animarme cuando llevaba horario de mañanas.

A todos los que alguna vez han sido miembros del GDE, ya coincidieramos por un largo periodo de tiempo o solo unos pocos días, la cooperación prestada y apoyo mutuo ha sido de gran ayuda y un punto de apoyo desde el que mover todo. Mil gracias, y posiblemente me quedo corto.

Expresar mi gratitud al Instituto de Microelectrónica de Barcelona (IMB) adscrito al Centro Nacional de Microelectrónica (CNM) por las dos estancias realizadas allí, tan breves pero tan fructíferas en resultados. En especial quiero dar las gracias a Fortia Vila, tutor de la estancia en ambas ocasiones, cuya experiencia en el manejo de la máquina de puntas resultó más que útil. El equipo humano perteneciente al centro merece un agradecimiento.

Debo agradecer también al *Institute of Electrodynamics, Microwave and Circuit Engineering* adscrito a la *Vienna University of Technology* la colaboración prestada durante mis dos estancias. Gracias a Horst Zimmermann, director del instituto, por dar el visto bueno a mi estancia y por toda la supervisión del trabajo realizado. Agradecer a todo el grupo de investigación su colaboración, y en especial a Robert Swoboda, Wolfgang Gaberl, Kerstin Schneider-Hornstein, Franz Schlögl y Bernhard Goll por ser

capaces de resolver cualquier cuestión, ya estuviera relacionada con el trabajo llevado a cabo, o fuera una cuestión meramente logística. Además, no me puedo olvidar de todas las visitas que tuve durante mi estancia, lograron que disfrutara muchisimo más de una ciudad tan espectacular como Viena. Y para colmo, como aficionado al fútbol, presencio en vivo y en directo la conquista española de la Eurocopa 2008.

Por supuesto, gracias a toda mi familia, desde todos los que ya me esperaban cuando llegué a este mundo, hasta los que se han ido uniendo, que en los últimos años no han sido pocos. En especial, a mis padres y mi hermana, cuyo apoyo y ánimo han sido fundamentales en muchos momentos. A todos, espero que esteis tan orgullosos de mí, como yo de vosotros.

Dicen que los amigos son la familia que tú eliges tener. Es evidente que hay otros factores que influyen en tu vida, pero no me puedo quejar ni lo más mínimo de los amigos que he tenido y tengo. El camino ha sido muy fácil recorrerlo a su lado. Quiero dar las gracias a todas las personas con las que me he reido, por cada vez que lo han conseguido.

Siento decirlo, pero por encima de todos tengo a Mary. Mi compañera de viaje. Ella es la razón por la que hago muchas cosas, pero sin duda me siento recompensado por todas ellas. La conocí durante la carrera y, curiosamente, bajó mi nota promedio. Cosas que pasan, sin embargo estoy convencido de que soy mejor persona desde que la conozco y de que la querré siempre. Nos quedan muchas historias que compartir y aventuras por disfrutar. Además, es mi constante.

Gracias a Spock, por todas las veces que me saca a pasear, por el meneo de rabo tan constante y gracioso, y por todas las veces que me arranca una sonrisa.

También quisiera expresar mi agradecimiento a las instituciones que han financiado el desarrollo de este trabajo: Ministerio de Ciencia e Innovación a través de proyectos en colaboración con el Fondo Europeo de Desarrollo Regional (TEC2005-00285/MIC, TEC2008-05455/TEC y PET2006-0022) y la beca predoctoral FPU (AP2006-01434), la Diputación General de Aragón en colaboración con el Fondo Social Europeo (PIP187/2005, PI127/08), y la Universidad de Zaragoza (UZ2007-TEC) y la Caja de Ahorros de la Inmaculada a través del Programa CAI-Europa (IT5/08, IT21/09) de ayudas para estancias de investigación.

Por último, agradecer el esfuerzo a todo aquel que se lea esta tesis, solo me queda esperar que encuentre lo que busque.

# **CONTENTS**

| List of F | GIGURES                                | V    |

|-----------|----------------------------------------|------|

| LIST OF T | TABLES                                 | XI   |

| LIST OF S | SYMBOLS                                | XIII |

| List of A | ABBREVIATIONS                          | XVII |

| 1. Inte   | RODUCTION                              | 1    |

| 1.1.      | Optical Communications                 | 2    |

| 1.1.1.    | A Look at History                      | 2    |

| 1.1.2.    | Emerging Applications                  |      |

| 1.1.3.    | Comparison between Communication Links | 7    |

| 1.1.4.    | Optical Link Architecture              |      |

| 1.2.      | CMOS Technology                        | 10   |

| 1.3.      | State of the Art                       |      |

| 1.4.      | Objectives                             |      |

| 1.5.      | Thesis Organization                    |      |

| 1.6.      | References                             |      |

|           | ICAL SIGNAL TRANSMISSION               |      |

| 2.1.      | Data Signal                            |      |

| 2.1.1.    | Time Domain                            |      |

| 2.1.2.    | Frequency Domain                       |      |

| 2.1.3.    | Pseudorandom Bit Sequence              |      |

| 2.2.      | Optical Channels                       |      |

| 2.2.1.    | Fundamentals of Optical Fibers         |      |

| 2.2.2.    | Glass Optical Fibers                   |      |

| 2.2.3.    | Plastic Optical Fibers                 |      |

| 2.3.      | Transceiver Front-end                  |      |

| 2.3.1.    | Serializer                             |      |

| 2.3.2.    | Laser Diode                            |      |

| 2.3.3.    | Photodiode and Front-end               |      |

| 2.3.4.    | Deserializer                           |      |

| 2.4.      | Key Parameters                         |      |

| 2.4.1.    | Eye Diagram                            |      |

| 2.4.2.    | Bit Error Ratio                        |      |

| 2.4.3.    | Sensitivity                            | 48   |

|           |                                        |      |

|    | 2.4.4. | Dynamic Range                                | . 56 | ( |

|----|--------|----------------------------------------------|------|---|

|    | 2.5.   | Conclusions                                  |      |   |

|    | 2.6.   | References                                   | . 59 | ) |

| 3. | TRA    | NSIMPEDANCE AMPLIFIER                        |      |   |

|    | 3.1.   | Optimum Bandwidth                            | . 62 | ) |

|    | 3.2.   | Shunt Feedback TIA                           |      |   |

|    | 3.3.   | Review of TIA Topologies                     |      |   |

|    | 3.4.   | Input Dynamic Range Extension Techniques     |      |   |

|    | 3.4.1. | Variable Feedback Resistor                   |      |   |

|    | 3.4.2. | Compression Technique                        |      |   |

|    | 3.5.   | Proposed TIA Design                          |      |   |

|    | 3.5.1. | 180-nm Transimpedance Amplifier Architecture |      |   |

|    | 3.5.2. | 90-nm Transimpedance Amplifier Architecture  |      |   |

|    | 3.6.   | Experimental Verification                    |      |   |

|    | 3.6.1. | 90-nm TIA                                    |      |   |

|    | 3.6.2. | 180-nm TIA                                   |      |   |

|    | 3.7.   | Conclusions                                  |      |   |

|    |        | References                                   |      |   |

| 1  |        | T-AMPLIFIER                                  |      |   |

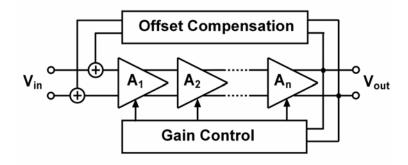

| ᅻ. | 4.1.   | Amplifier Core                               |      |   |

|    | 4.1.1. | •                                            |      |   |

|    | 4.1.2. | S .                                          |      |   |

|    | 4.1.2. | Automatic Gain Control                       |      |   |

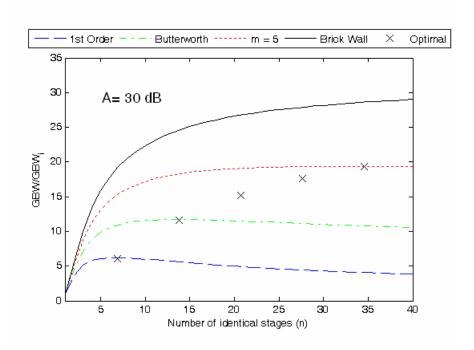

|    | 4.2.1. | Linear-in-dB Gain Distribution               |      |   |

|    |        |                                              |      |   |

|    | 4.2.2. | Discrete Gain Distribution                   |      |   |

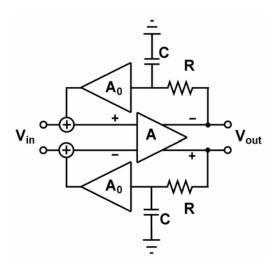

|    | 4.3.   | Offset Compensation                          |      |   |

|    |        | Proposed AGC Design                          |      |   |

|    | 4.4.1. | Amplifier Core Architecture                  |      |   |

|    | 4.4.2. | Programmable Gain                            |      |   |

|    | 4.4.3. | AGC Loop                                     |      |   |

|    | 4.4.4. | Offset Compensation Loop                     |      |   |

|    |        | Experimental Verification                    |      |   |

|    | 4.5.1. | PGA Implementation                           |      |   |

|    | 4.5.2. | AGC Implementation                           |      |   |

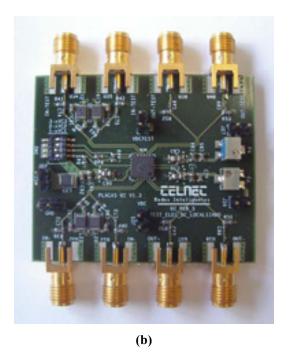

|    | 4.5.3. | PCB Characterization                         |      |   |

|    | 4.5.4. | On-wafer Characterization                    |      |   |

|    | 4.6.   | Conclusions                                  |      |   |

|    |        | References                                   |      |   |

| 5. | POF    | Receiver                                     |      |   |

|    | 5.1.   | Plastic Optical Fiber                        |      |   |

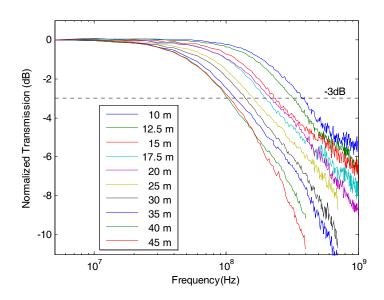

|    | 5.1.1. | Optical Fiber Bandwidth                      |      |   |

|    | 5.1.2. | Bandwidth-Length Dependency                  |      |   |

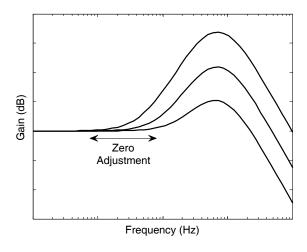

|    | 5.2.   | Equalization                                 |      |   |

|    | 5.2.1. | Equalization Techniques                      |      |   |

|    | 5.2.2. | Adaptive Equalization                        | 155  | , |

|    | 5.3.   | Receiver Architecture                        |      |   |

|    | 5.3.1. | Preamplifier with PD Monitor                 | 158  | 3 |

|    | 5.3.2. | Adaptive Equalizer Implementation            | 160  | ) |

|    | 5 4    | Experimental Verification                    | 168  | 2 |

|    | 5.4.1.  | Receiver Implementation                | . 168 |

|----|---------|----------------------------------------|-------|

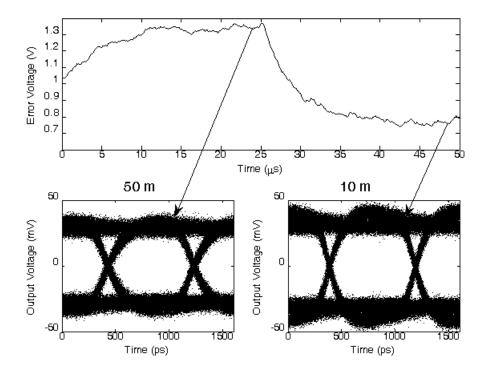

|    | 5.4.2.  | Results                                | . 169 |

|    | 5.5.    | Conclusions                            | . 172 |

|    | 5.6.    | References                             | 173   |

| 6. | Con     | CLUSIONS                               | . 177 |

|    | 6.1.    | General Conclusions                    | . 177 |

|    | 6.2.    | Further Research Directions            | . 179 |

| A  | . APP   | ENDIXES                                | 181   |

|    | A.1.    | Measurement Considerations             | . 181 |

|    | A.1.1.  | S parameters                           | . 181 |

|    | A.1.2.  |                                        |       |

|    | A.1.3.  | De-embedding                           | 185   |

|    | A.2.    | PRBS Generator                         | . 186 |

|    | A.3.    | Technological Parameters               | . 189 |

|    | A.3.1.  | UMC 0.18 µm Mixed-Mode/RF CMOS Process | . 190 |

|    | A.3.2.  | UMC 90 nm Logic and Mixed-Mode Process | . 191 |

|    | A.4.    | References                             | . 192 |

| Li | ST OF C | OWN PUBLICATIONS                       | 193   |

# **LIST OF FIGURES**

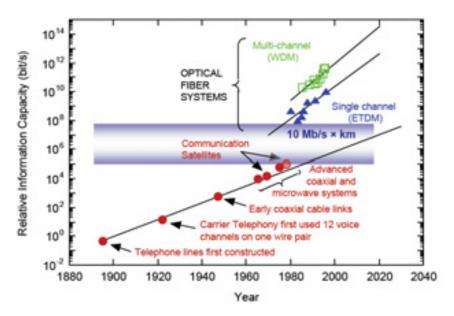

| Fig. | 1.1. Evolution of communication technologies [MIT05]                               | 4  |

|------|------------------------------------------------------------------------------------|----|

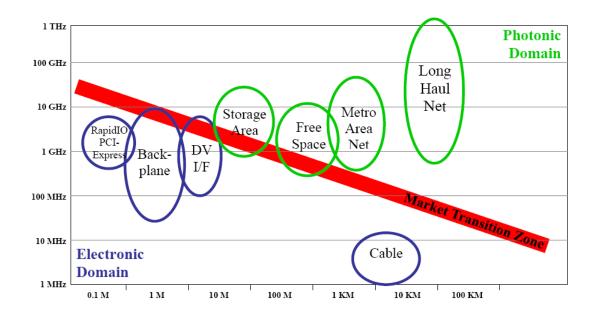

|      | 1.2. Bandwidth - distance market map [MIT05]                                       |    |

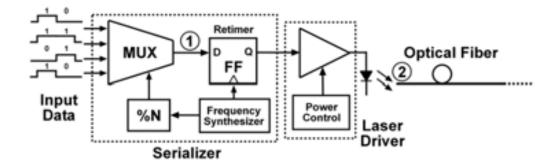

| Fig. | 1.3. Complete diagram of transmitter system.                                       | 10 |

| Fig. | 1.4. Complete diagram of receiver system.                                          | 11 |

| Fig. | 1.5. Signal propagation through transmission path.                                 | 11 |

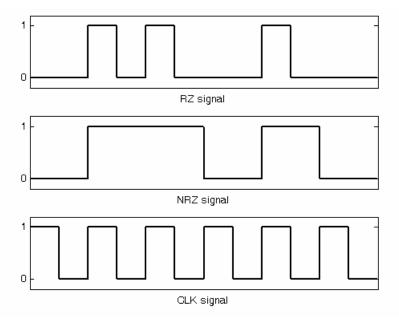

| Fig. | 2.1. '0101100' sequence codified as NRZ signal and clock signal with same pulse    | e  |

|      |                                                                                    | 20 |

| Fig. | 2.2. NRZ compared with RZ and 4-PAM for 0011010010 bit sequence and the            |    |

|      | same data rate.                                                                    | 21 |

| Fig. | 2.3. RZ as a composition of NRZ and clock.                                         | 21 |

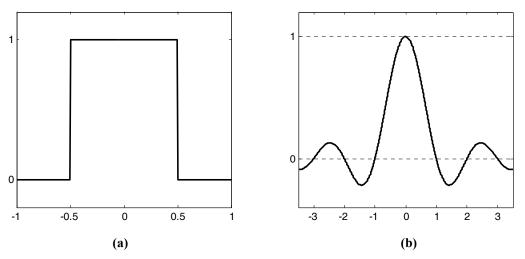

| Fig. | 2.4. (a) Pulse and (b) Sinc function.                                              | 23 |

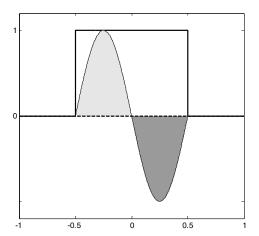

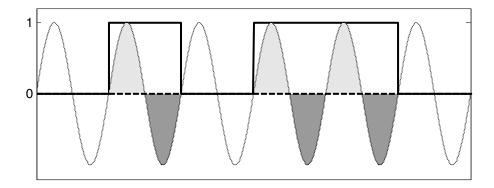

| Fig. | 2.5. Example of sinusoidal signals (first and second) which are not included in    |    |

|      | pulse function spectrum as the positive (light grey) and negative (dark grey) area | l  |

|      |                                                                                    | 24 |

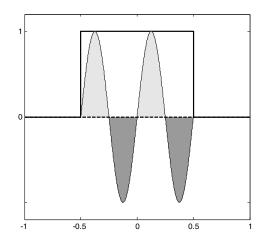

| Fig. | 2.6. Example of sinusoidal signal which is not included in NRZ spectrum as         |    |

|      | positive (light grey) and negative (dark grey) area included in pulses cancels     | 24 |

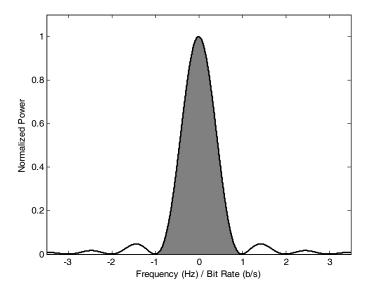

| Fig. | 2.7. NRZ frequency spectrum. Grey area represents the 90 % of the total power      |    |

|      |                                                                                    | 25 |

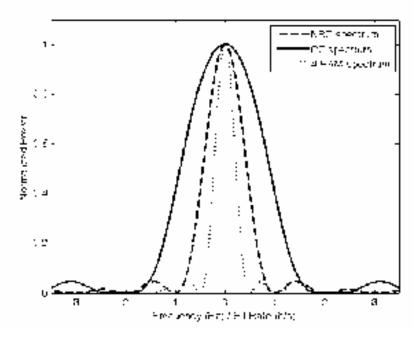

| _    | 2.8. Comparison between NRZ, RZ and 4-PAM frequency spectrum                       |    |

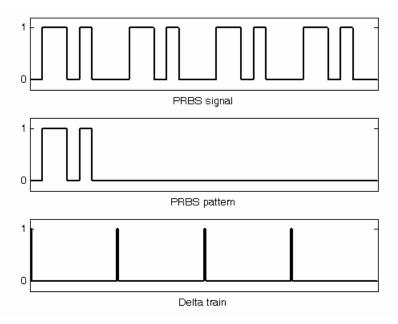

| _    | 2.9. PRBS as a composition of its pattern 0110100 and delta train.                 |    |

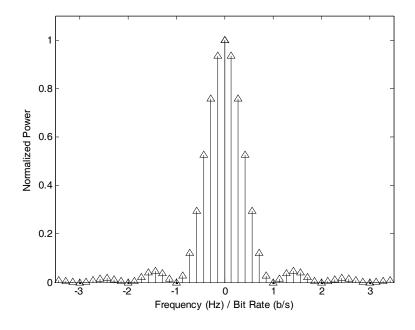

| _    | 2.10. NRZ frequency spectrum for PRBS with pattern length of 7 bits                |    |

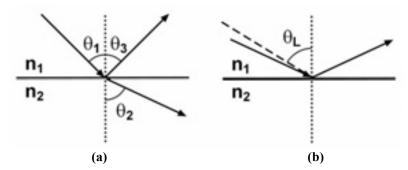

| _    | 2.11. (a) Reflected and refracted beam and (b) total reflection effect             |    |

| _    | 2.12. Light transmission in optical fiber.                                         |    |

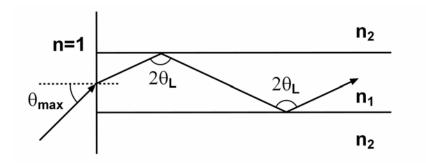

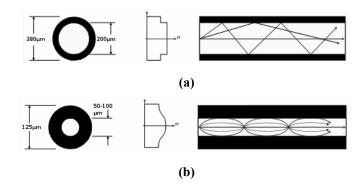

| _    | 2.13. (a) Single mode and (b) Multi mode fiber.                                    |    |

| _    | 2.14. (a) Step index and (b) graded index fiber.                                   |    |

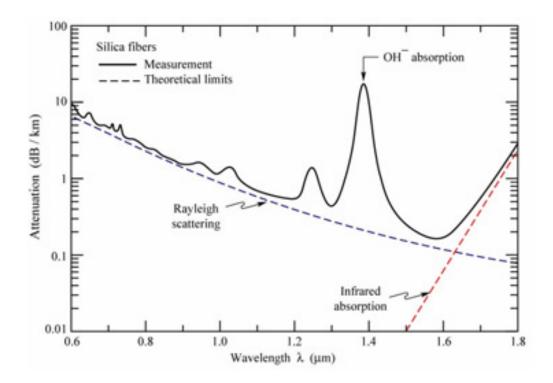

| _    | 2.15. Attenuation along a typical single-mode glass optical fiber                  |    |

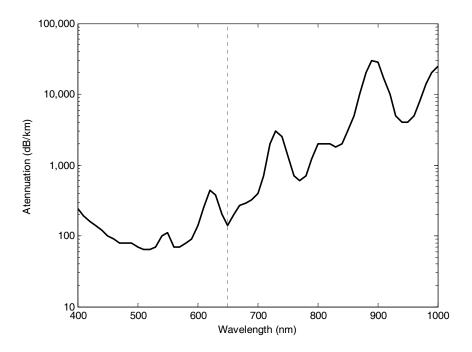

| _    | 2.16. Attenuation along a typical PMMA plastic optical fiber.                      |    |

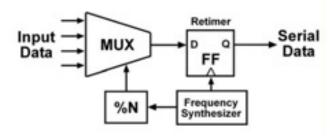

| _    | 2.17. Basic serializer block diagram.                                              |    |

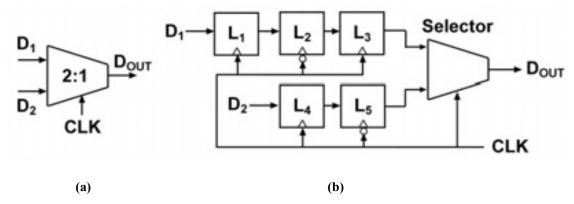

| _    | 2.18. 2:1 MUX: (a) symbol and (b) typical architecture.                            |    |

| Fig. | 2.19. Universal MUX: symbol (top) and its implementation based on tree (left) and  |    |

|      | shift register architecture (right).                                               |    |

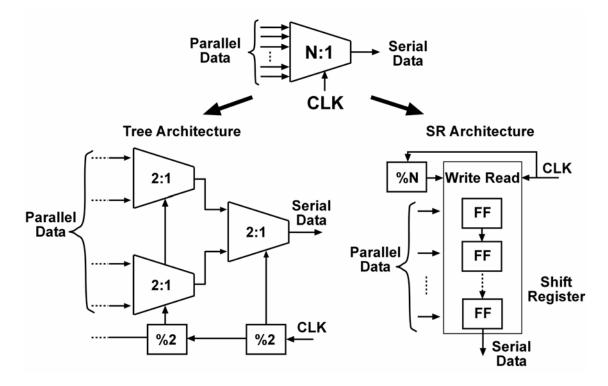

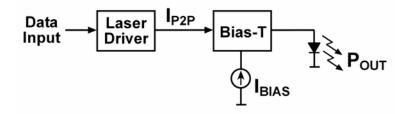

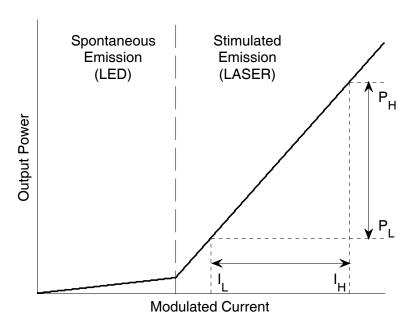

| _    | 2.20. Basic transmitter block diagram.                                             |    |

| Fig. | 2.21. Amplitude modulation principle.                                              | 36 |

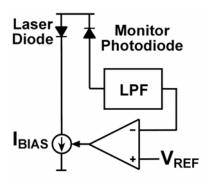

| Fig.  | 2.22. Power control system.                                                           | . 37      |

|-------|---------------------------------------------------------------------------------------|-----------|

| _     | 2.23. Optical receiver block diagram.                                                 |           |

| _     | 2.24. Photodiode symbol (top), layer structure and band diagram (bottom)              |           |

|       | 2.25. Photodiode response for several semiconductor materials.                        |           |

|       | 2.26. Photodiode model for inverse region.                                            |           |

| _     | 2.27. Basic deserializer block diagram.                                               |           |

| _     | 2.28. Typical PLL topology.                                                           |           |

| _     | 2.29. Eye diagram construction                                                        |           |

| _     | 2.30. Noisy eye diagram for ideal PRBS including finite rise-fall times               |           |

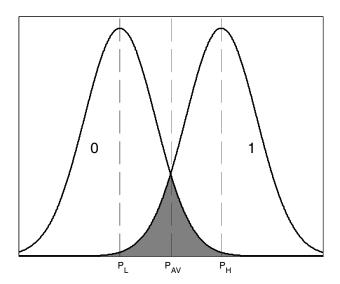

| _     | 2.31. Probability density for Gaussian noise model.                                   |           |

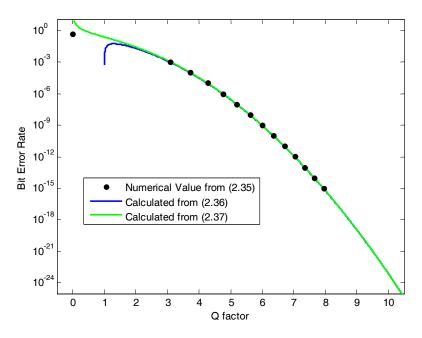

| Fig.  | 2.32. Bit Error Rate depending on Q factor.                                           | . 48      |

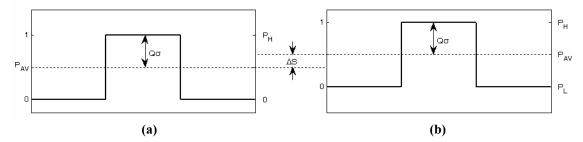

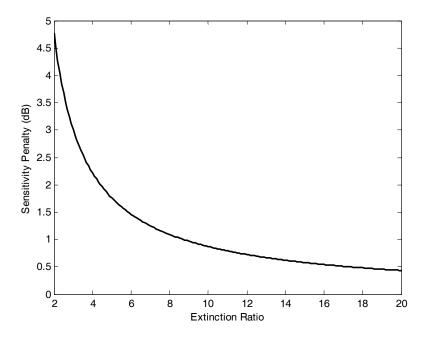

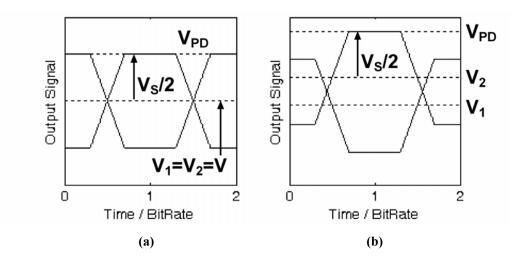

|       | 2.33. Transmission pulse with (a) infinity and (b) non-ideal extinction ratio         |           |

|       | 2.34. Sensitivity penalty due to extinction ratio.                                    |           |

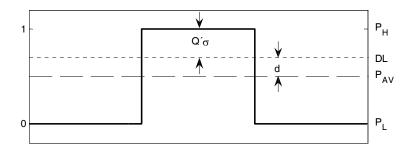

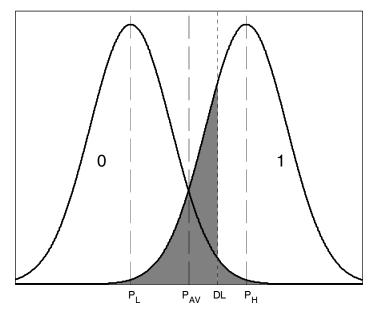

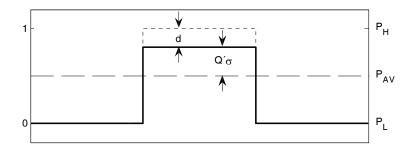

|       | 2.35. Asymmetry on Gaussian model due to decision offset                              |           |

|       | 2.36. BER contributions with decision offset.                                         |           |

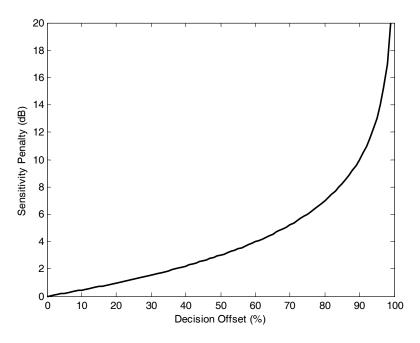

| _     | 2.37. Sensitivity penalty due to decision offset.                                     |           |

| _     | 2.38. Transmission pulse degraded by inter-symbol interference                        |           |

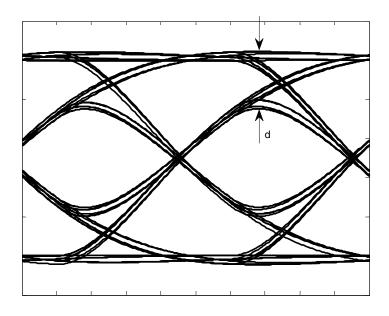

| _     | 2.39. Eye diagram degraded by inter-symbol interference.                              |           |

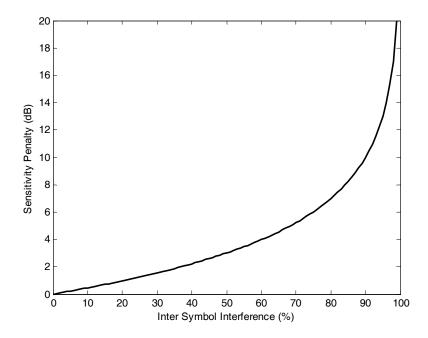

| _     | 2.40. Sensitivity penalty due to inter-symbol interference                            |           |

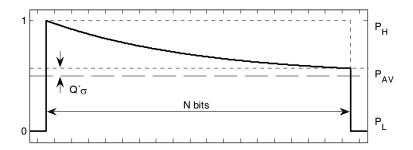

| _     | 2.41. Long transmission pulse degraded by lower cut-off frequency.                    |           |

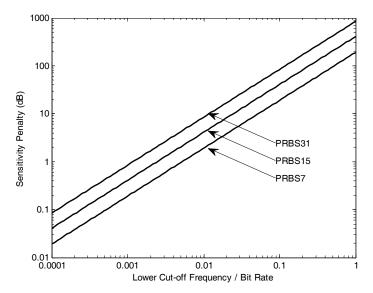

|       | 2.42. Sensitivity penalty due to lower cut-off frequency.                             |           |

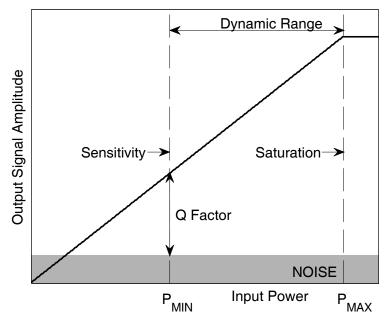

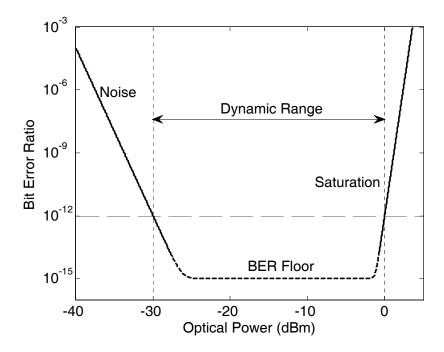

| _     | 2.43. Input dynamic range of the optical receiver.                                    |           |

| _     | 2.44. Typical BER plot depending on the signal level.                                 |           |

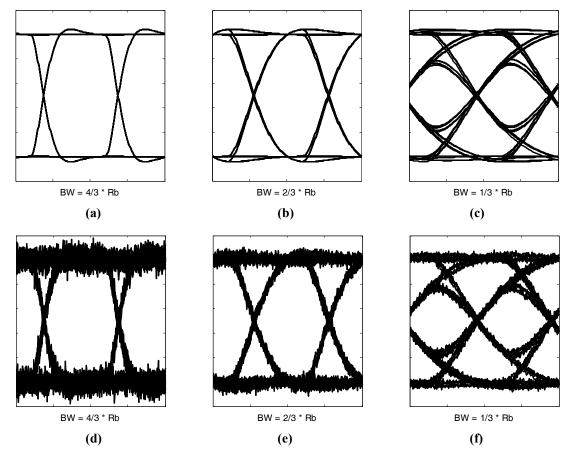

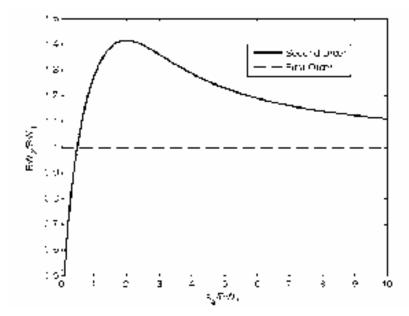

| _     | 3.1. Noiseless (a-c) and noisy (d-f) eye diagrams at different normalized             | ,         |

| 5.    | bandwidths assuming Butterworth frequency response and white noise. (e)               |           |

|       | represents the realistic optimum case.                                                | . 62      |

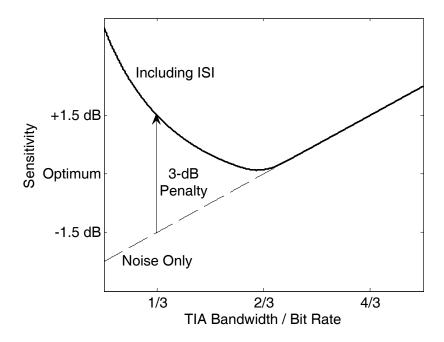

| Fig   | 3.2. Sensitivity depending on bandwidth including white noise and sensitivity         | . 02      |

| 5.    | penalty due to ISI.                                                                   | 63        |

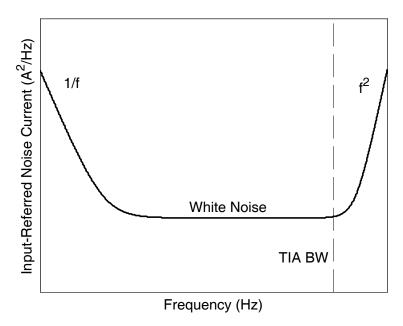

| Fig   | 3.3. Input referred noise from TIA. Both axes in log scale.                           |           |

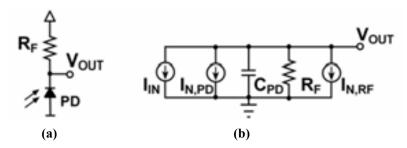

|       | 3.4. Simple I-V conversion by using a resistor $R_F$ : (a) circuit and (b) equivalent |           |

| - 15. | model                                                                                 | . 65      |

| Fig   | 3.5. Basic structure of a shunt feedback TIA: (a) circuit and (b) equivalent mode     |           |

| 8.    | (a) <b>(a) (a) (b) (b)</b>                                                            |           |

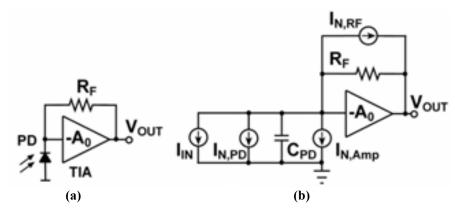

| Fig   | 3.6. Second order TIA bandwidth.                                                      |           |

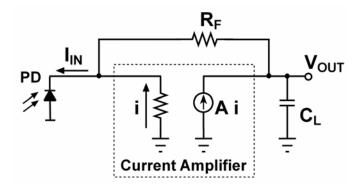

|       | 3.7. Current-mode TIA.                                                                |           |

| _     | 3.8. Common-gate TIA.                                                                 |           |

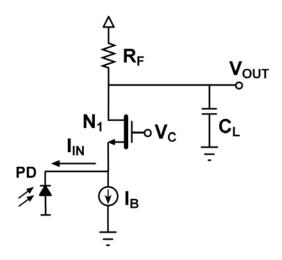

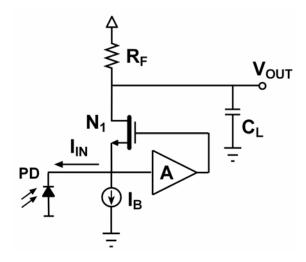

|       | 3.9. Regulated cascode TIA.                                                           |           |

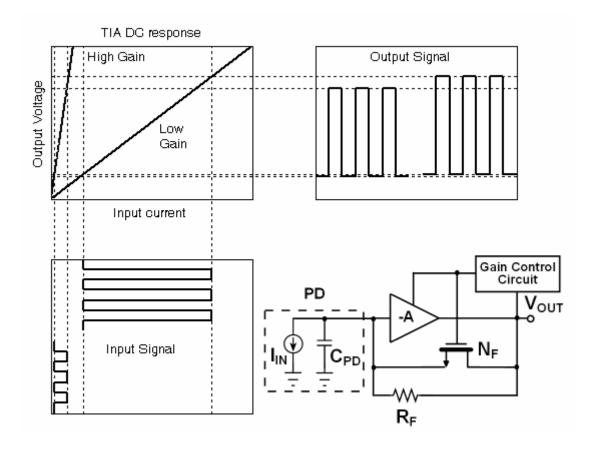

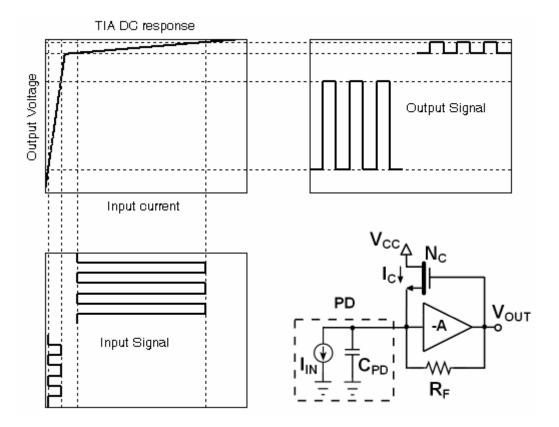

|       | 3.10. Operation (top-left) and simplified diagram (bottom-right) of a TIA with        | . 70      |

| 1 15. | variable feedback resistor.                                                           | 71        |

| Fiσ   | 3.11. Operation (top-left) and simplified diagram (bottom-right) of a TIA with        | . / 1     |

| 1 15. | compression technique.                                                                | 73        |

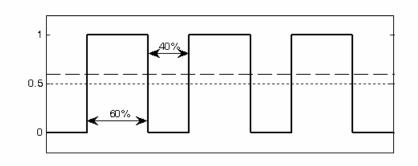

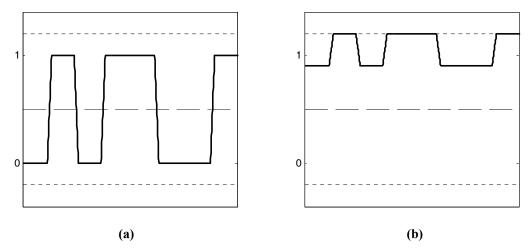

| Fiσ   | 3.12. Clock signal with duty cycle distortion due to pulse width.                     |           |

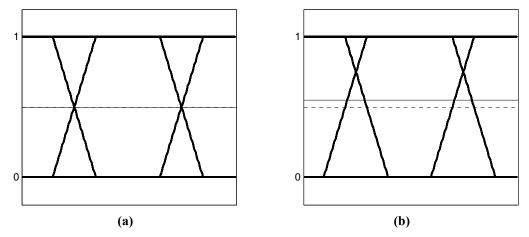

|       | 3.13. (a) Ideal eye diagram and (b) with duty cycle distortion.                       |           |

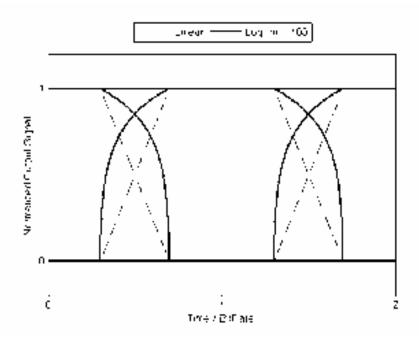

|       | 3.14. Normalized linear and logarithmical functions.                                  |           |

|       | 3.15. Linear and logarithmical eye diagrams.                                          |           |

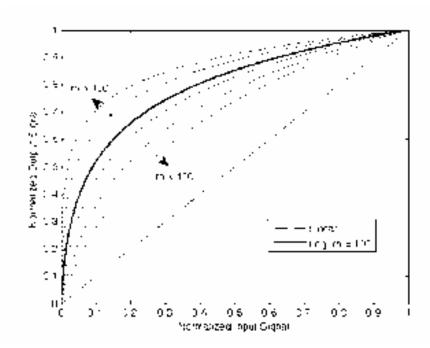

|       | 3.16. Estimated duty cycle distortion for logarithmical function with m = 100         | . 13      |

| 1 1g. | depending on the input signal amplitude                                               | 76        |

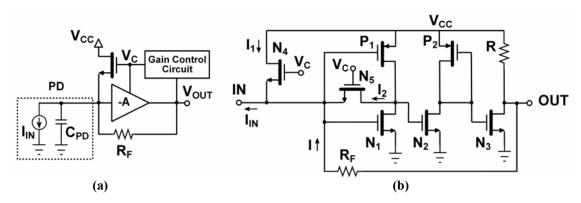

| Fiσ   | 3.17. (a) Simplified diagram including photodiode model and (b) complete circu        |           |

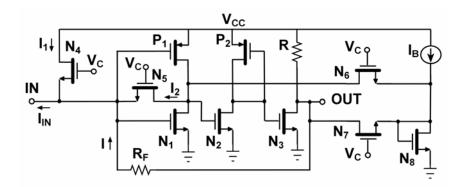

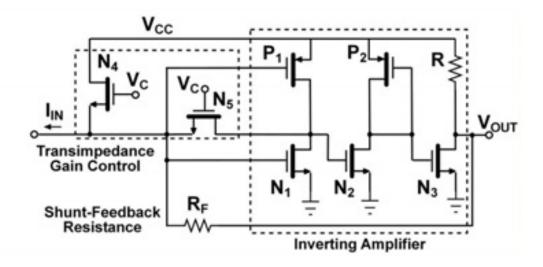

| 1 15. | of the proposed transimpedance amplifier                                              | 111<br>77 |

|       | VI AIN DIVINING HAIBIIIIDAAIIN AIIIDIIIDA                                             | . , ,     |

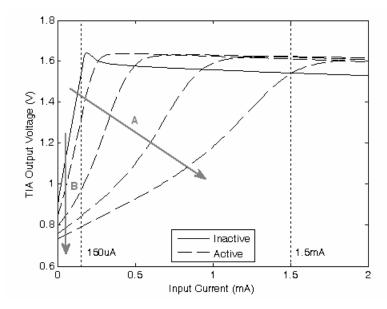

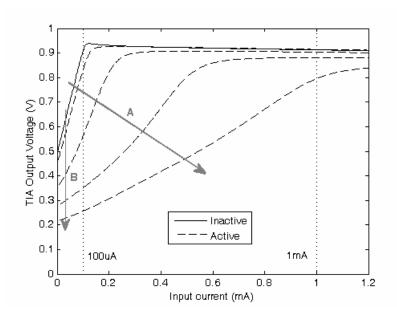

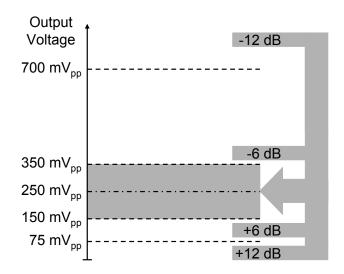

| Fig.  | 3.18. DC response of the TIA over the whole control voltage swing (inactive: 900 mV, active: $V_C = 1.5$ V to 1.8 V, 100 mV step). The input dynamic range extension technique causes a transimpedance reduction (A) and a voltage drop | (B).        |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

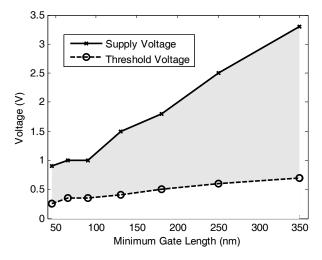

| Fig.  | 3.19. Available voltage swing depending on CMOS technology.                                                                                                                                                                             |             |

| Fig.  | 3.20. DC response of the TIA over the whole control voltage swing (inactive: $V_C = 700 \text{ mV}$ to 1 V, 100 mV step). The input dynamic range extension technique causes a transimpedance reduction (A) and a voltage drop          | (B).        |

| Fig.  | 3.21. Complete circuit of the proposed transimpedance amplifier for 90 nm CN technology.                                                                                                                                                | 4OS         |

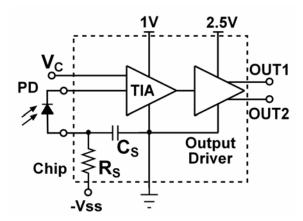

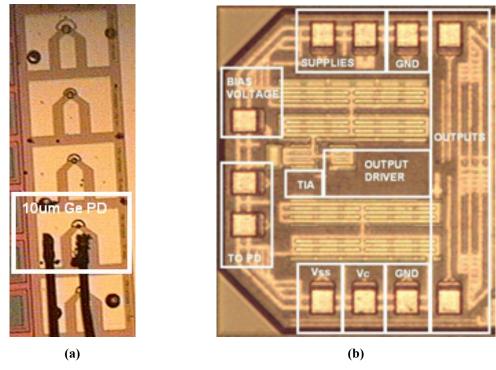

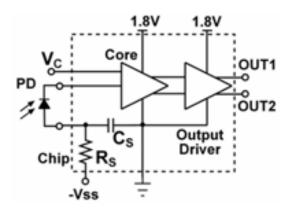

| Fig.  | 3.22. Block diagram of the implemented chip for 90-nm TIA.                                                                                                                                                                              | 82          |

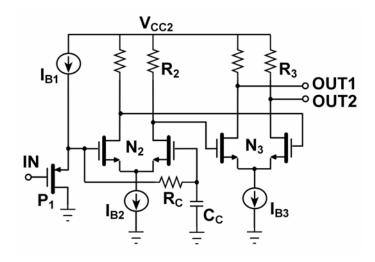

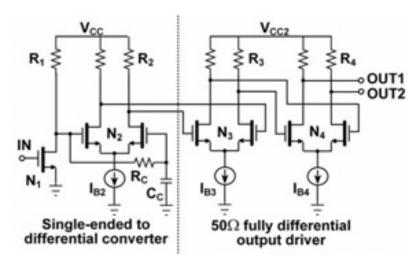

| _     | 3.23. Output driver for 90-nm TIA.                                                                                                                                                                                                      |             |

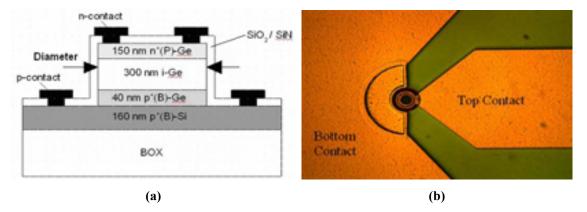

| Fig.  | 3.24. (a) Section and (b) vertical view of Ge photodiode.                                                                                                                                                                               | 83          |

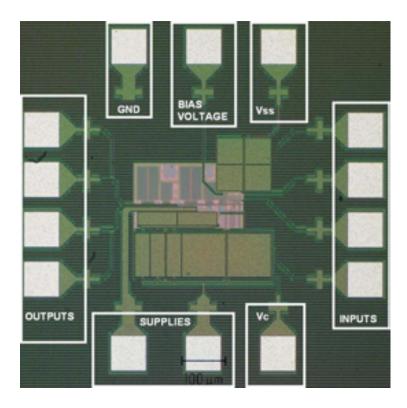

| Fig.  | 3.25. (a) Photodiode and (b) TIA chip microphotograph                                                                                                                                                                                   | 84          |

| Fig.  | 3.26. Characterization of Ge photodiode with 10 µm diameter                                                                                                                                                                             | 84          |

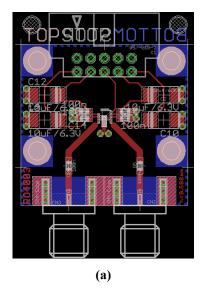

|       | 3.27. (a) Layout and (b) photo of PCB for optical characterization                                                                                                                                                                      |             |

| Fig.  | 3.28. (a) Photodiode with aligned optical fiber and (b) bounded TIA chip                                                                                                                                                                | 85          |

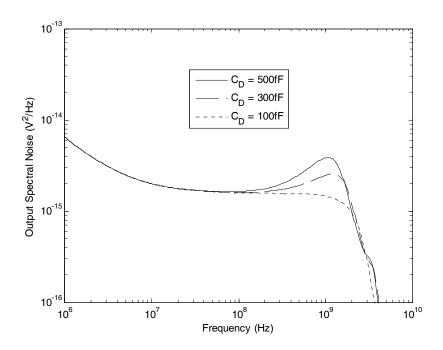

| Fig.  | 3.29. Simulated noise performance depending on photodiode capacitance                                                                                                                                                                   | 86          |

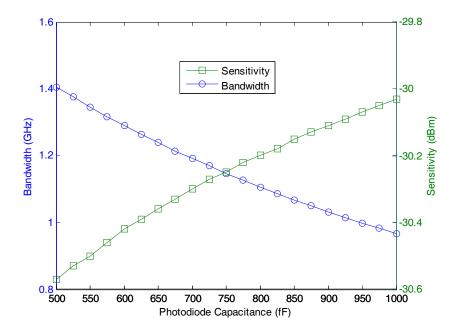

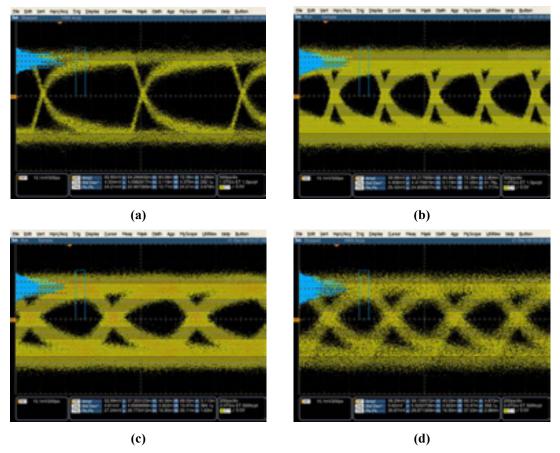

| _     | 3.30. Simulated bandwidth and sensitivity depending on photodiode capacitand 3.31. Measured eye diagrams at (a) 500 Mb/s, (b) 1 Gb/s, (c) 1.5 Gb/s and (d) 2.                                                                           |             |

|       | Gb/s                                                                                                                                                                                                                                    |             |

|       | 3.32. Block diagram of the 180-nm version.                                                                                                                                                                                              |             |

|       | 3.33. 180-nm output stage.                                                                                                                                                                                                              |             |

|       | 3.34. 180-nm prototype including de-embedding circuit.                                                                                                                                                                                  |             |

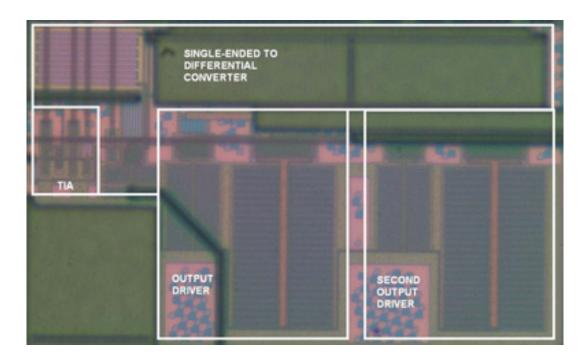

| Fig.  | 3.35. Detail of the active area. The second output driver is added for de-embed                                                                                                                                                         | ding.<br>91 |

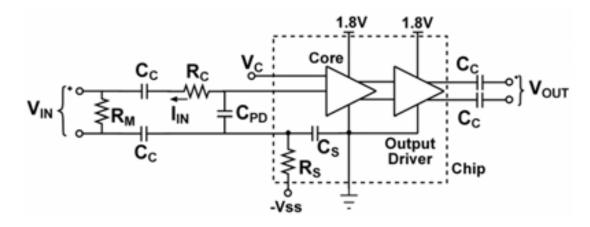

| Fig.  | 3.36. Block diagram of the implemented chip with measurement setup for elec characterization, including coupling capacitors $C_C$ , an input matching resistor and resistor $R_C$ and capacitor $C_D$ modeling the photodiode.          | $R_M$       |

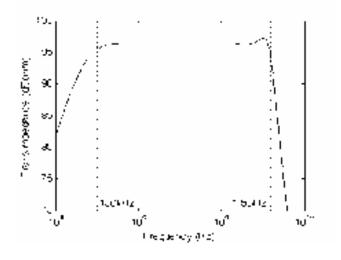

| Fiσ   | 3.37. Measured frequency response in inactive region.                                                                                                                                                                                   |             |

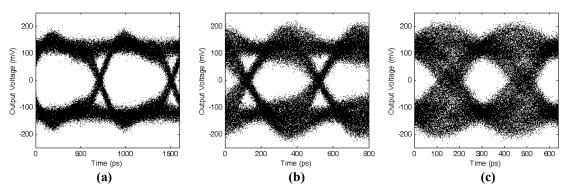

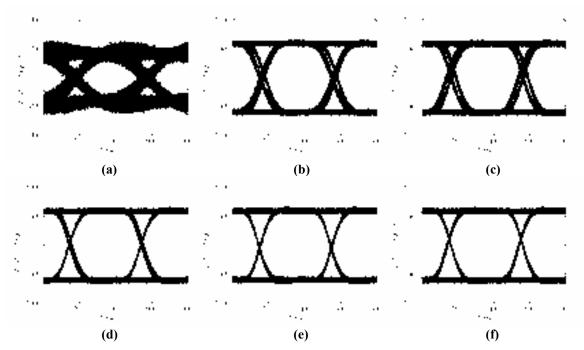

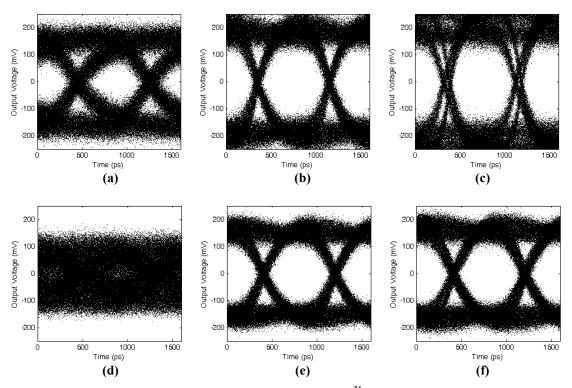

|       | 3.38. Measured eye diagrams for 2.5 Gb/s PRBS 2 <sup>31</sup> – 1 for an input level of (a)                                                                                                                                             |             |

| 1 15. | 26 dBm, (b) $-16$ dBm, (c) $-13$ dBm in the inactive region and (d) $-11$ dBm ( $V$                                                                                                                                                     | C =         |

| ъ.    | 1.5 V), (e) $-1$ dBm and (f) 0 dBm ( $V_C = 1.8$ V) in the active region                                                                                                                                                                |             |

|       | 3.39. Measured bit error rate versus input signal level.                                                                                                                                                                                |             |

| _     | 4.1. Basic post-amplifier diagram.                                                                                                                                                                                                      |             |

|       | 4.2. Gain bandwidth product extension.                                                                                                                                                                                                  |             |

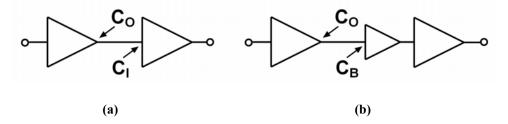

|       | 4.3. Two identical stages (a) without and (b) with inter-stage buffer.                                                                                                                                                                  |             |

| _     | 4.4. Two consecutive stages (a) without and (b) with inverse scaling                                                                                                                                                                    |             |

| _     | 4.5. Miller effect.                                                                                                                                                                                                                     |             |

|       | 4.6. Differential stage (a) without and (b) with negative Miller capacitances<br>4.7. Simplified block diagrams of (a) feedback and (b) feedforward AGCs                                                                                |             |

| _     |                                                                                                                                                                                                                                         |             |

| _     | 4.8. Simplified AGC loop block diagram                                                                                                                                                                                                  |             |

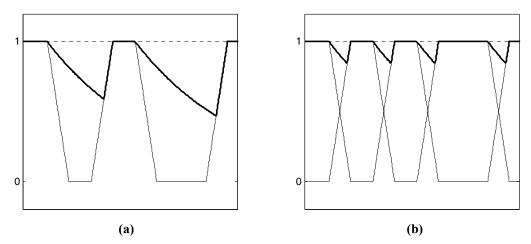

| ı ıg. | 4.9. Time responses depending on gain distribution. (a) finear and (b) finear-in                                                                                                                                                        |             |

| Fig   | 4.10. Gain variation diagram.                                                                                                                                                                                                           |             |

|       | 4.11. Improved gain variation diagram.                                                                                                                                                                                                  |             |

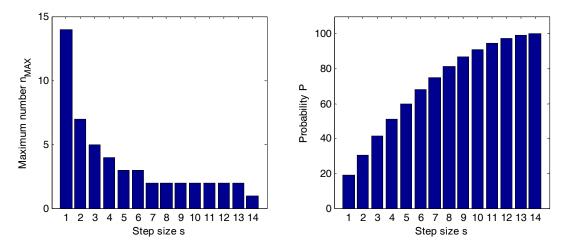

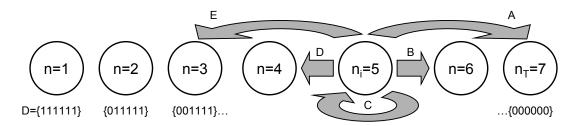

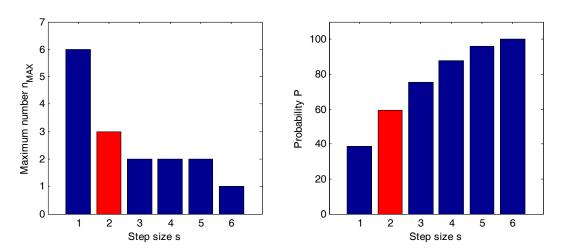

|       | 4.12. Characteristics of sequential distribution depending on step size for $n_T$ =                                                                                                                                                     |             |

| - 15. | 4.12. Characteristics of sequential distribution depending on step size for $n_1$                                                                                                                                                       | 112.        |

| Fig.       | 4.13. Signal amplified without compensation (a) ideally and (b) affected by input    | ıt  |

|------------|--------------------------------------------------------------------------------------|-----|

|            | offset.                                                                              |     |

| Fig.       | 4.14. Detected peak value (a) ideally and (b) affected by input offset               | 113 |

|            | 4.15. Typical offset compensation circuit.                                           |     |

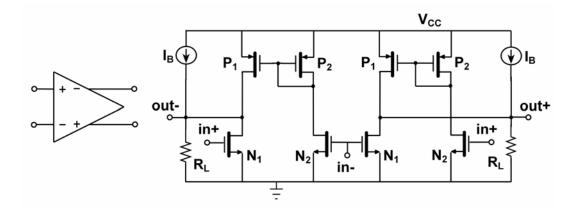

| Fig.       | 4.16. Frequency response with offset compensation circuit.                           | 115 |

|            | 4.17. Snelgrove cell.                                                                |     |

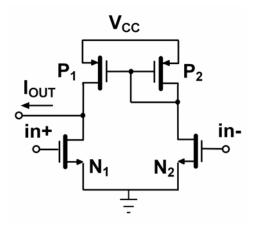

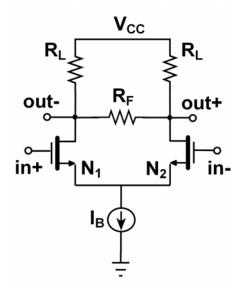

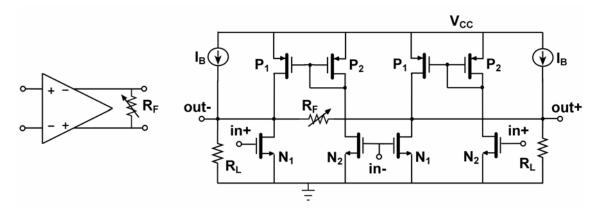

| Fig.       | 4.18. Differential gain stage based on Snelgrove cell.                               | 117 |

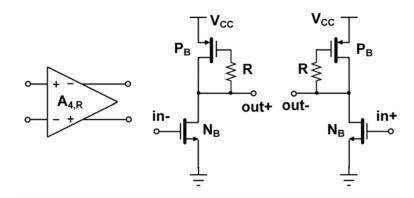

| Fig.       | 4.19. Fourth stage schematic.                                                        |     |

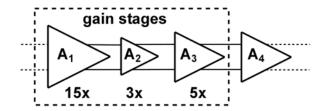

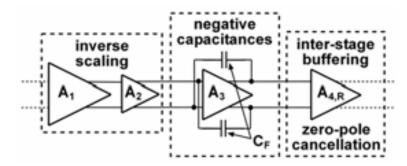

| Fig.       | 4.20. Proposed multi-stage amplifier indicating scaling ratio among gain stages      |     |

|            | with lowest integer numbers.                                                         |     |

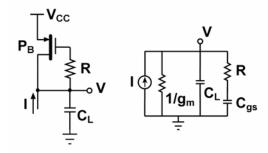

| Fig.       | 4.21. Fourth stage with a resistor to enhance the bandwidth.                         | 119 |

| Fig.       | 4.22. Small signal equivalent model of fourth stage.                                 | 119 |

| Fig.       | 4.23. Post-amplifier architecture indicating all broadband techniques applied        | 120 |

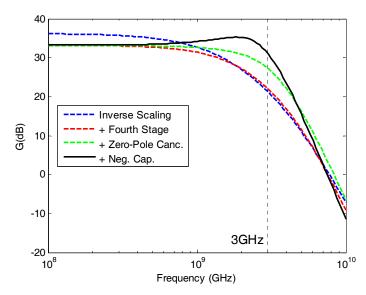

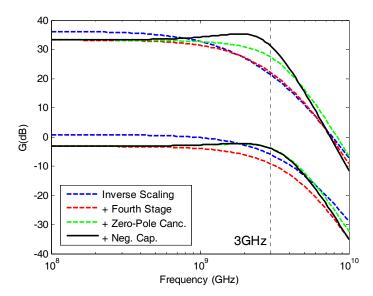

|            | 4.24. Simulated bandwidth enhancement of the post-amplifier                          |     |

| Fig.       | 4.25. Differential gain stage including variable load resistor.                      | 121 |

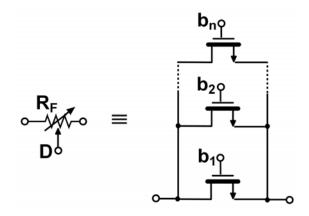

| Fig.       | 4.26. Proposed gain stage including variable load resistor.                          | 122 |

| Fig.       | 4.27. Implementation of $R_F$ with a NMOS array.                                     | 122 |

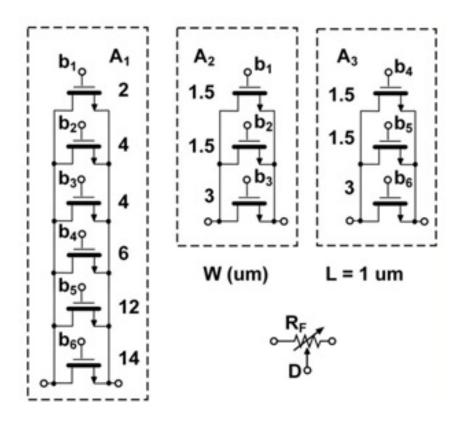

| Fig.       | 4.28. Proposed NMOS arrays for the three gain stages.                                | 123 |

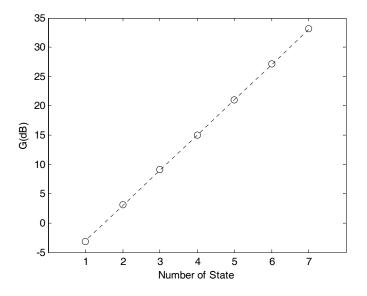

| Fig.       | 4.29. Simulated gain distribution.                                                   | 123 |

| _          | 4.30. Gain variation diagram.                                                        |     |

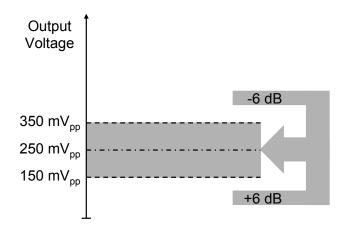

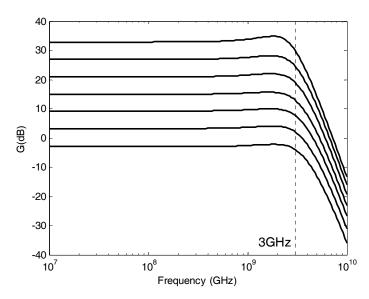

| Fig.       | 4.31. Frequency response over the whole gain range.                                  | 124 |

| Fig.       | 4.32. Frequency response of highest and lowest gain state                            | 125 |

| _          | 4.33. Proposed state diagram.                                                        |     |

| Fig.       | 4.34. Characteristics of sequential distribution depending on step size for this car | se  |

|            | $(n_T = 7)$ , with the selected step size highlighted in red                         |     |

| _          | 4.35. Proposed gain variation diagram.                                               |     |

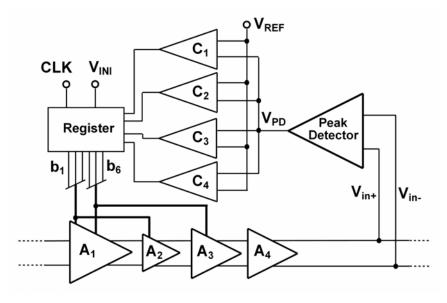

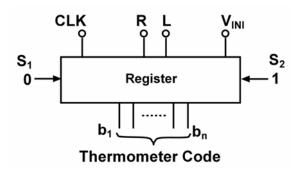

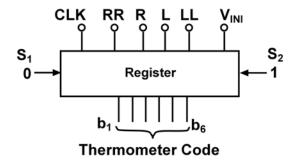

| _          | 4.36. AGC loop block diagram.                                                        |     |

| _          | 4.37. Generic double-direction shift register.                                       |     |

| _          | 4.38. Designed shift register.                                                       |     |

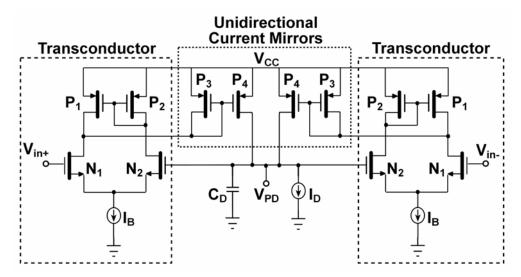

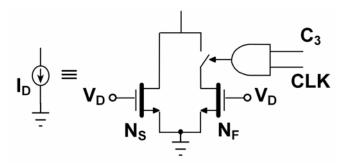

| _          | 4.39. Peak detector schematic.                                                       |     |

|            | 4.40. Detected peak value for (a) single-ended and (b) differential signal           |     |

|            |                                                                                      | 129 |

| _          | 4.42. Comparator schematic.                                                          |     |

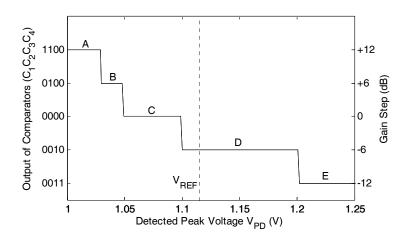

|            | 4.43. Comparator output response.                                                    |     |

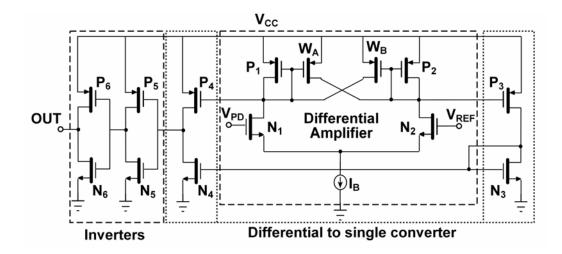

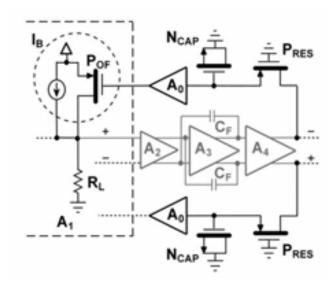

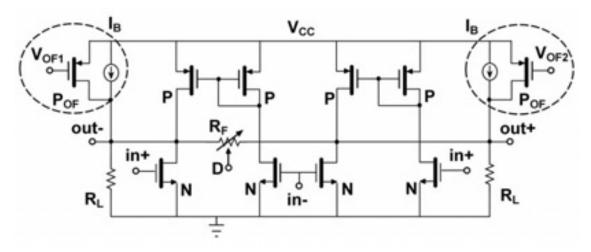

| Fig.       | 4.44. Implemented offset compensation circuit.                                       | 133 |

|            | 4.45. Detail of first stage $A_1$ including offset compensation control              | 133 |

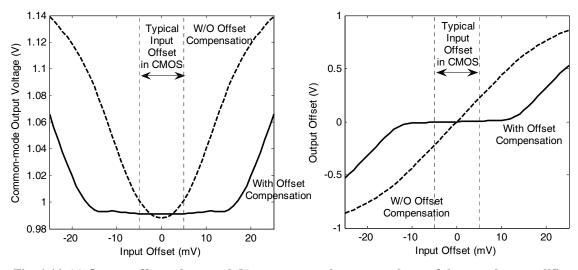

| Fig.       | 4.46. (a) Output offset voltage and (b) common-mode output voltage of the            |     |

|            | complete amplifier with highest gain when offset compensation is not used (das       |     |

|            | line) and when it is used (solid line).                                              |     |

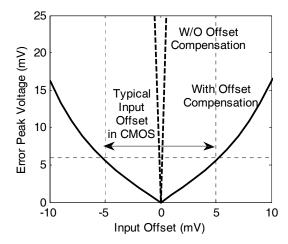

| Fig.       | 4.47. Simulated error peak voltage with highest gain when offset compensation        |     |

|            | not used (dashed line) and when it is used (solid line)                              |     |

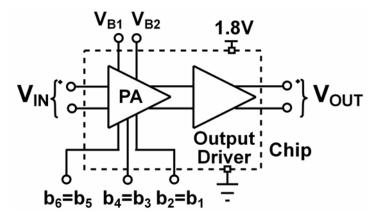

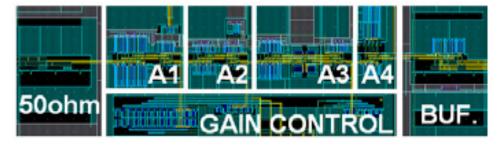

|            | 4.48. Programmable post-amplifier implementation for PCB.                            |     |

|            | 4.49. Programmable post-amplifier implementation tested on-wafer                     |     |

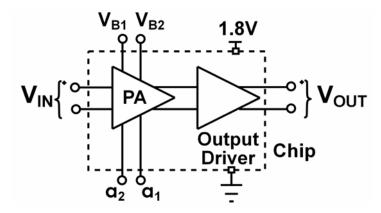

| _          | 4.50. AGC post-amplifier implementation.                                             |     |

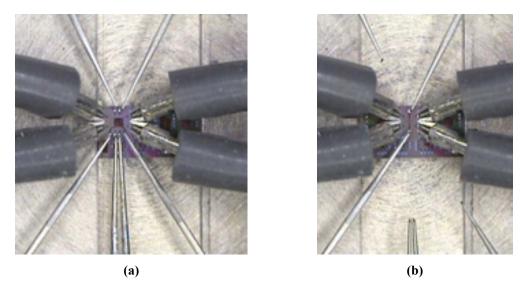

| Fig.       | 4.51. Fabricated PCBs to be biased (a) with bias-tee and (b) through input network   |     |

|            |                                                                                      |     |

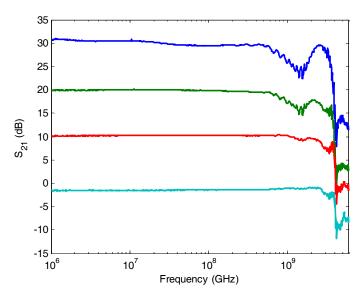

|            | 4.52. Measured S <sub>21</sub> parameter for PGA on PCB after de-embedding           |     |

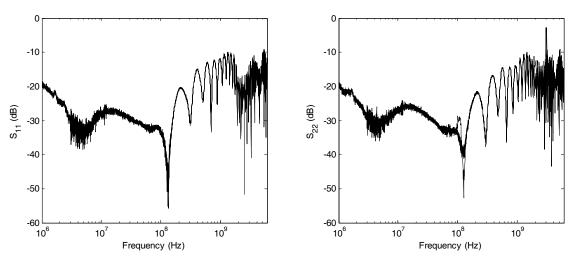

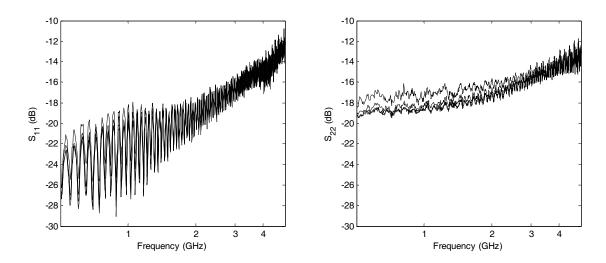

| _          | 4.53. Measured $S_{11}$ and $S_{22}$ parameters for PGA on PCB.                      |     |

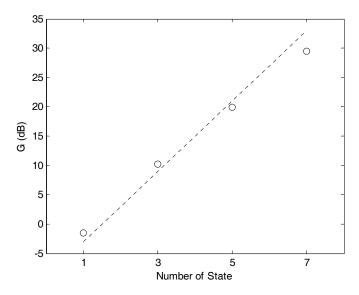

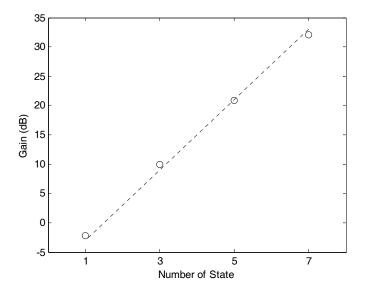

| $Fi\sigma$ | 4.54 Measured gain compared to expected distribution                                 | 138 |

| Fig. 4.55. On-wafer probe station.                                                              | . 139 |

|-------------------------------------------------------------------------------------------------|-------|

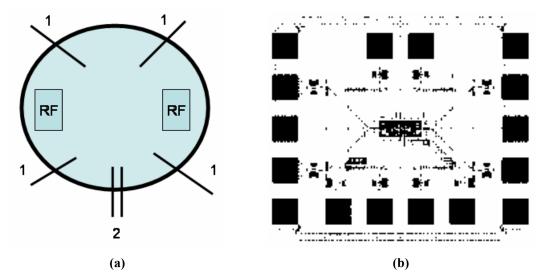

| Fig. 4.56. (a) Maximum pin-out and (b) layout adapted to on-wafer characterization              |       |

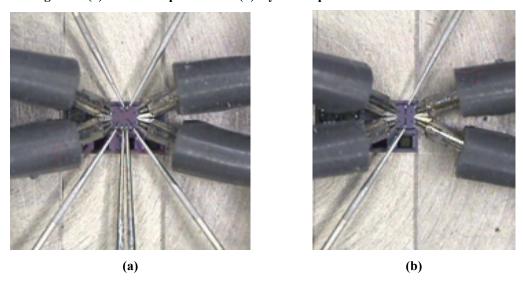

| Fig. 4.57. (a) PGA prototype and (b) driver with measurement probes                             | . 140 |

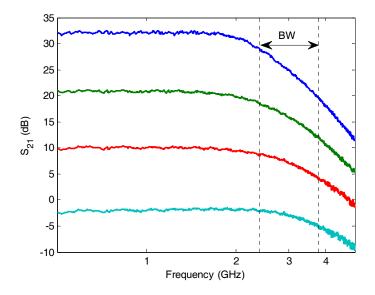

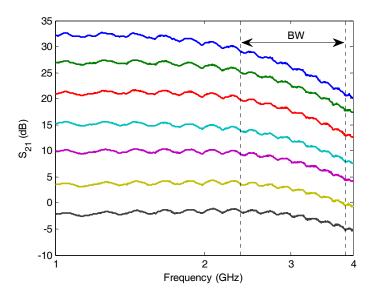

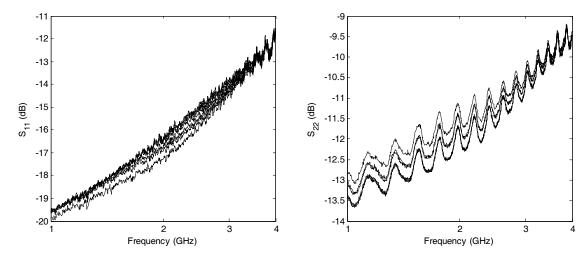

| Fig. 4.58. Measured $S_{21}$ parameter for PGA implementation after de-embedding                | . 141 |

| Fig. 4.59. Measured $S_{11}$ and $S_{22}$ parameters for PGA implementation                     | . 141 |

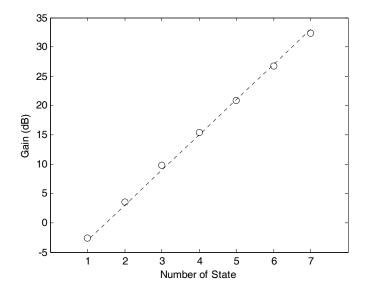

| Fig. 4.60. Measured gain distribution for PGA implementation                                    |       |

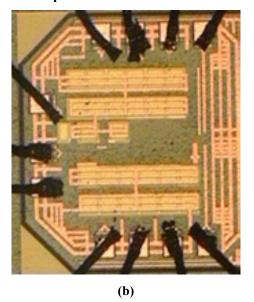

| Fig. 4.61. (a) AGC prototype and (b) driver with measurement probes                             |       |

| Fig. 4.62. Measured $S_{21}$ parameter for AGC implementation after de-embedding                | . 143 |

| Fig. 4.63. Measured $S_{11}$ and $S_{22}$ parameters for AGC implementation                     | . 143 |

| Fig. 4.64. Measured gain distribution for AGC implementation.                                   |       |

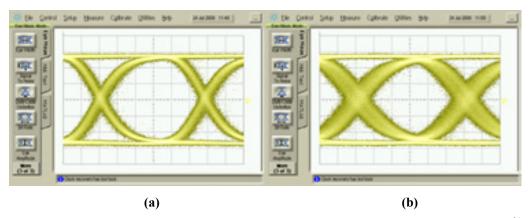

| Fig. 4.65. (a) 2.5 Gb/s and (b) 3.125 Gb/s measured eye diagrams NRZ data with Pl               | RBS   |

| of 2 <sup>31</sup> –1 at 250 mV output amplitude peak-to-peak for highest gain state            | . 144 |

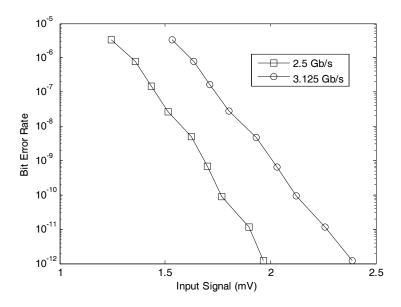

| Fig. 4.66. Measured bit rate versus input signal level.                                         |       |

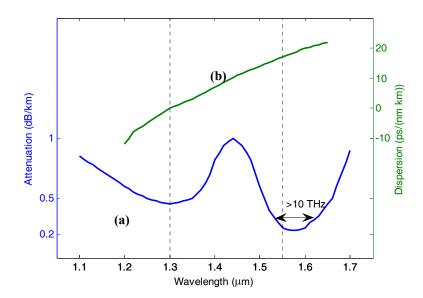

| Fig. 5.1. Attenuation and dispersion of a typical single-mode GOF                               | . 152 |

| Fig. 5.2. Bandwidth-length dependency.                                                          |       |

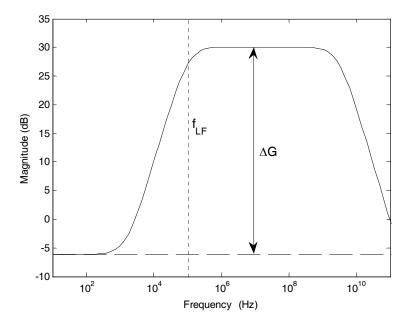

| Fig. 5.3. Adaptive equalizer frequency response                                                 | . 155 |

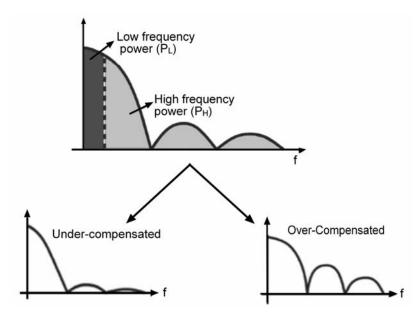

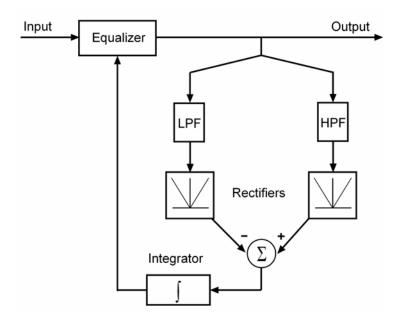

| Fig. 5.4. Spectrum power estimator diagram.                                                     | . 156 |

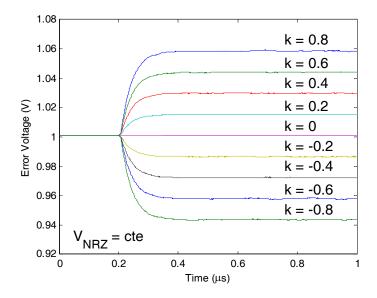

| Fig. 5.5. Entire and low-pass filtered signal power.                                            | . 161 |

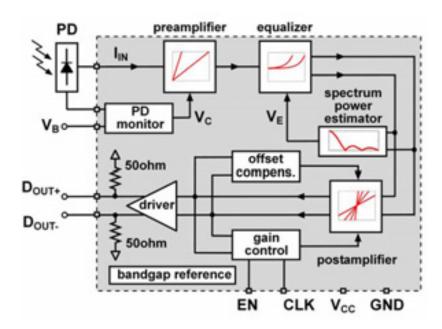

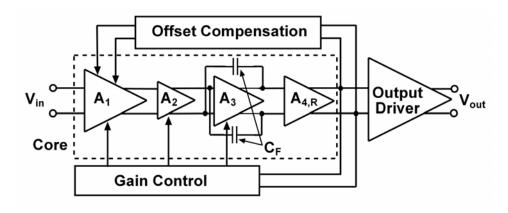

| Fig. 5.6. Optical receiver block diagram.                                                       | . 157 |

| Fig. 5.7. Photodiode monitor schematic.                                                         | . 159 |

| Fig. 5.8. Proposed equalizer with differential output.                                          | . 162 |

| Fig. 5.9. Low-pass filter schematic.                                                            |       |

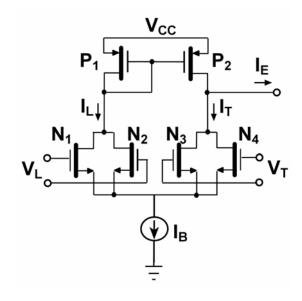

| Fig. 5.10. Power error detector schematic.                                                      | . 165 |

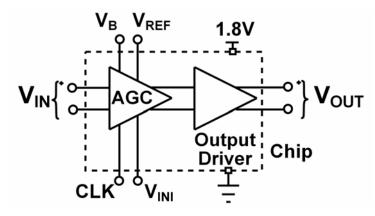

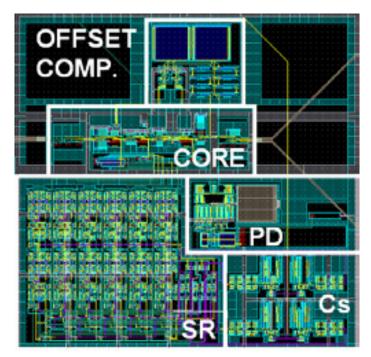

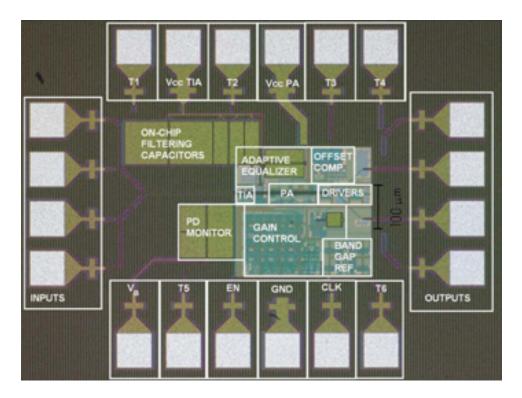

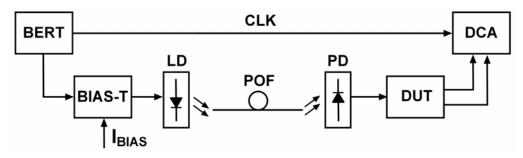

| Fig. 5.11. Chip microphotograph.                                                                | . 168 |

| Fig. 5.12. Block diagram of the experimental setup.                                             | . 169 |

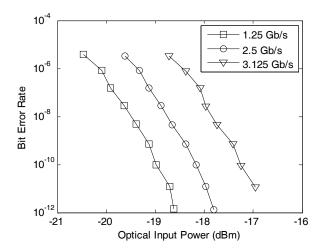

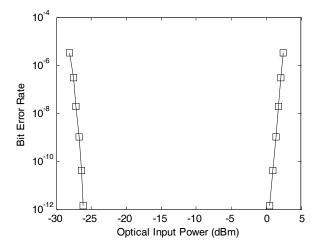

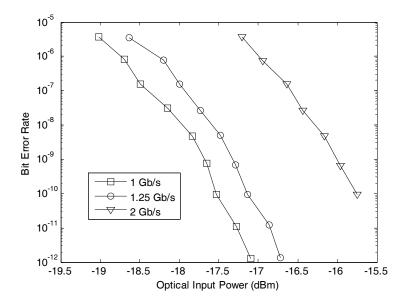

| Fig. 5.13. Measured BER versus input optical power.                                             | . 170 |

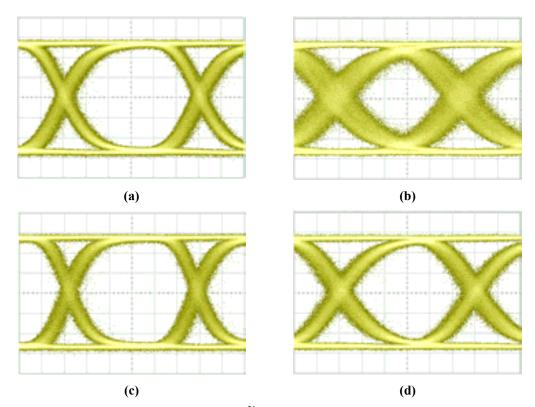

| Fig. 5.14. Eye diagrams for 1.25 Gb/s (left) and 2 Gb/s (right) NRZ PRBS 2 <sup>31</sup> -1 for | an    |

| optical input power nearby sensitivity (-16 dBm).                                               | . 171 |

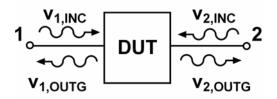

| Fig. A.1. Input and output signals seen as incident and outgoing waves                          | . 182 |

| Fig. A.2. Calibration kit Rohde & Schwartz ZV-Z132.                                             | . 184 |

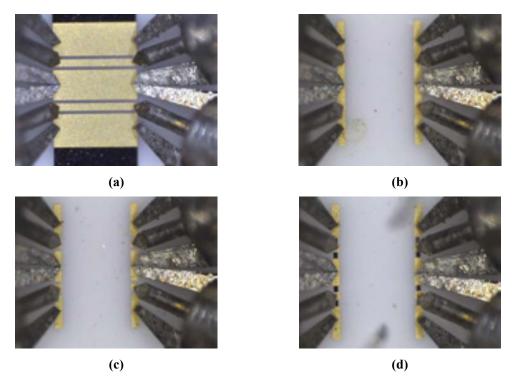

| Fig. A.3. Calibration process: (a) through, (b) short, (c) open, (d) load                       | . 184 |

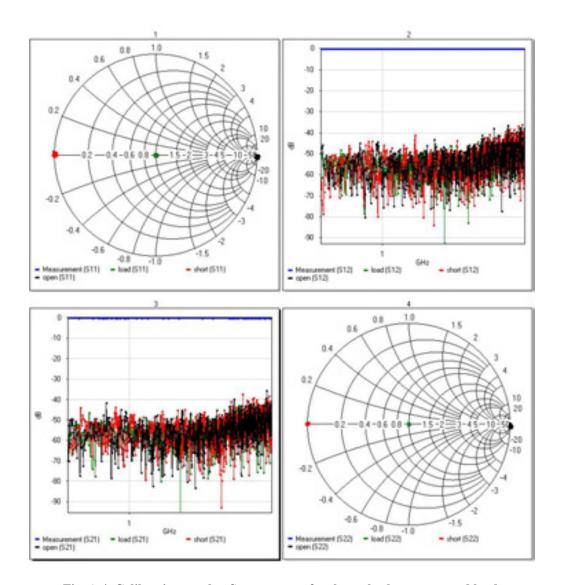

| Fig. A.4. Calibration results: S parameters for through, short, open and load                   | . 185 |

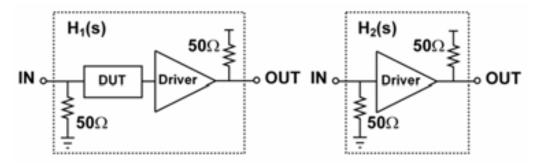

| Fig. A.5. De-embedding technique.                                                               |       |

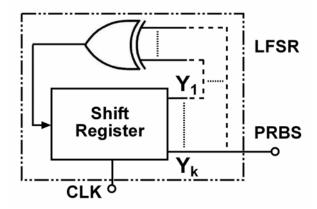

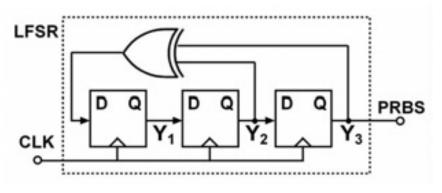

| Fig. A.6. Pseudorandom bit sequence generator.                                                  | . 187 |

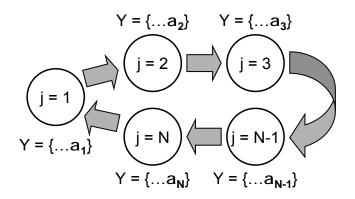

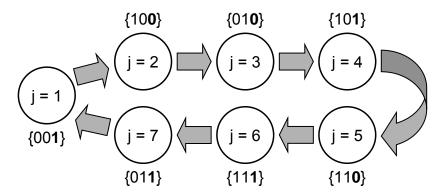

| Fig. A.7. State diagram of a PRBS generator.                                                    |       |

| Fig. A.8. Pseudorandom bit sequence generator with $k = 3$ .                                    | . 189 |

| Fig. A.9. State diagram of a PRBS generator with $k = 3$ .                                      | . 189 |

# LIST OF TABLES

| Table 1.1. Generations of optical fiber for long haul applications [AGR97, GRA02,    |        |

|--------------------------------------------------------------------------------------|--------|

| SAL09]                                                                               |        |

| Table 2.1. Comparison of several line codes.                                         | 23     |

| Table 2.2. Relationship between Bit Error Rate and Q factor. In bold, reference case | es. 48 |

| Table 2.3. Reference values for optical interconnects depending on the application.  | 58     |

| Table 3.1. Design parameters for 0.18 μm TIA.                                        | 77     |

| Table 3.2. Design parameters for 90 nm TIA                                           |        |

| Table 3.3. Design parameters for 90 nm output driver                                 | 83     |

| Table 3.4. Design parameters for 180 nm output driver                                | 89     |

| Table 3.5. Comparison of several transimpedance amplifiers                           | 96     |

| Table 4.1. Design parameters for amplifier core.                                     |        |

| Table 4.2. Simulated bandwidth depending on the broadband techniques applied         |        |

| Table 4.3. Simulated bandwidth for highest and lowest gain state.                    | . 125  |

| Table 4.4. Design parameters for peak detector.                                      |        |

| Table 4.5. Gain changes possibilities.                                               |        |

| Table 4.6. Common design parameters for comparators                                  |        |

| Table 4.7. Particular design parameters for each comparator.                         |        |

| Table 4.8. Digital control gain of programmable post-amplifier tested on-wafer       |        |

| Table 4.9. Comparison of several post-amplifiers                                     |        |

| Table 5.1. Design parameters of photodiode monitor.                                  |        |

| Table 5.2. Design parameters of proposed equalizer                                   |        |

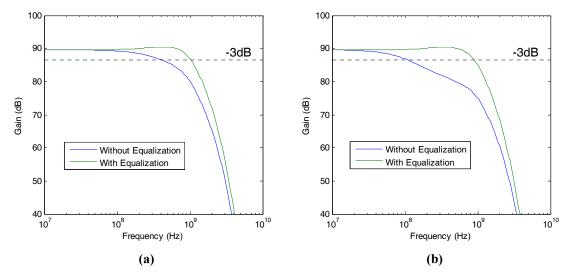

| Table 5.3. Gain and bandwidth combinations depending on frequency response of I      |        |

|                                                                                      |        |

| Table 5.4. Design parameters of low-pass filter.                                     |        |

| Table 5.5. Design parameters of power error detector.                                |        |

| Table 5.6. Summary of receiver performance for 10 m SI-POF.                          |        |

| Table A.1. Maximal length sequence properties.                                       |        |

| Table A.2. States for a LFSR with $k = 3$ .                                          |        |

| Table A.3. Run distribution for $k = 7$ .                                            |        |

| Table A.4. Comparison between chosen CMOS technologies                               |        |

| Table A.5. Key device parameters                                                     |        |

| Table A.6. Key design rules.                                                         |        |

| Table A.7. Key core devices parameters.                                              | . 191  |

|                                                                                      |        |

#### LIST OF TABLES

| Гable A.8. Key I/O devices parameters | 192 |

|---------------------------------------|-----|

| Table A.9. Kev design rules.          | 192 |

# **LIST OF SYMBOLS**

| Constant      | Description                  | Value                   | Unit        |

|---------------|------------------------------|-------------------------|-------------|

| K             | Boltzmann's constant         | $1.38065 \ 10^{-23}$    | J/K         |

| h             | Planck's constant            | $6.626\ 10^{-34}$       | $J \cdot s$ |

| q             | Electron charge              | $1.6022  10^{-19}$      | C           |

| $arepsilon_0$ | Vacuum dielectric constant   | $8.8542 \ 10^{-12}$     | F/m         |

| $\mu_0$       | Vacuum magnetic permeability | $4 \cdot \pi \ 10^{-7}$ | H/m         |

| c             | Vacuum light speed           | 299,782,465             | m/s         |

| Symbol   | Description                        |

|----------|------------------------------------|

| BW       | Bandwidth                          |

| $BW_N$   | Noise bandwidth                    |

| $C_F$    | Feedback or filtering capacitance  |

| $C_{gs}$ | MOS gate-source capacitance        |

| $C_I$    | Input capacitance                  |

| $C_L$    | Load capacitance                   |

| CLK      | Clock signal                       |

| $C_O$    | Output capacitance                 |

| $C_{OX}$ | Oxide capacitance per unit of area |

| $C_{PD}$ | Photodiode capacitance             |

Decision level DLENEnable FExcess noise factor Clock frequency  $f_{CLK}$ Low-frequency cut-off  $f_{LF}$  $f_T$ Transition frequency G or AGain MOS transconductance  $g_m$  $G_m$ Cell transconductance GNDGround H(s)Transfer function Bias current  $I_B$  $I_{DS}$ Drain-source current  $I_H$ Current for high state  $I_{IN}$ Input current Current for low state  $I_L$  $I_N$ Noise current Leakage current under specific conditions  $I_{OFF}$  $I_{DS}$  current under specific conditions  $I_{ON}$ j Complex LTransistor length Refraction index n  $P_{AV}$ Average power  $P_H$ Power for high state  $P_{IN}$ Input power  $P_L$ Power for low state  $P_{LPF}$ Power of low-pass filtered signal  $P_{OV}$ Overload power  $P_{TOT}$ Power of entire signal Q Q factor R Responsitivity  $R_{h}$ Bit rate  $R_F$ Shunt-feedback or floating load resistance Load resistance  $R_L$

S Sensitivity  $S_a$ Dominant pole  $S_{xy}$ S parameters (x and y = 1 or 2) TTemperature Pulse width  $T_b$  $T_{OX}$ Gate-oxide thickness of a MOS transistor Transresistance  $T_R$  $\nu$ Velocity  $V_B$ Bias voltage  $V_C$ Control voltage Supply voltage  $V_{CC}$  $V_{CM}$ Common-mode voltage  $V_E$ Error signal  $V_{INI}$ Initializing signal  $V_L$ Low-pass filtered voltage signal  $V_{PD}$ Peak detected voltage  $V_{REF}$ Reference voltage  $V_{SW}$ Voltage swing  $V_T$ Entire voltage signal Transistor threshold voltage  $V_{TH}$ WTransistor width Dielectric constant З ζ Damping ratio Quantum efficiency η  $\theta$ Angle  $\theta_L$ Limit angle λ Wavelength Magnetic permeability μ Electron mobility  $\mu_N$ Hole mobility  $\mu_P$ Standard deviation σ Time constant τ Probability density Efficiency slope χ

- Ψ Wave function

- $\omega$  Angular frequency

- $\omega_0$  Characteristic frequency

# **LIST OF ABBREVIATIONS**

Acronym Significance

AC Alternate Current

AGC Automatic Gain Control

ASIC Application Specific Integrated Circuit

ASK Amplitude-Shift Keying

BER Bit Error Rate

BERT Bit Error Rate Tester

BIPM Bureau International des Poids et Mesures

CDR Clock and Data Recovery circuit

CG Common-Gate

CMOS Complementary Metal-Oxide-Semiconductor

DC Direct Current

DCA Digital Communications Analyzer

DFB Distributed FeedBack

DMUX DeMUltipleXer

DR Dynamic Range

DSP Digital Signal Processor

DUT Device Under Test

DWDM Dense Wavelength-Division Multiplexing

EMI Electro-Magnetic Interference

ER Extinction Ratio F.O.M. Figure Of Merit FET Field Effect Transistor

FF Flip-Flop FP Fabry-Perot

FSG Fluorine doped Silicate Glass

FTTH Fiber-To-The-Home

GBW Gain-Bandwidth Product

GI Graded-Index

GOF Glass Optical Fiber

GSG Ground-Signal-Ground

HPF High-Pass Filter

HVT High Threshold Voltage

IC Integrated Circuit

IDC International Data Corporation

IEEE Institute of Electrical and Electronics Engineers

ISI Inter-Symbol Interference

LA Limiting Amplifier

LAN Local Area Network

LASER Light Amplification by Stimulated Emission of Radiation

LED Light-Emitting Diode

LFSR Linear Feedback Shift Register

LL Low Leakage

LPF Low-Pass Filter

LVT Low Threshold Voltage

MAN Metropolitan Area Network

MIM Metal-Insulator-Metal

MLS Maximal Length Sequence

MM Multi-Mode Fiber or Mixed Mode

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MOST Media Oriented System Transport

MUX MUltipleXer

NMOS Metal-Oxide-Semiconductor N

NRZ Non Return to Zero

PA Post-Amplifier

PAM Pulse Amplitude Modulation

PCB Printed Circuit Board

PD PhotoDiode or Peak Detector PGA Programmable Gain Amplifier

PLL Phased-Locked Loop

PMMA Poly-Methyl MethAcrylate

PMOS Metal-Oxide-Semiconductor P

POF Plastic Optical Fiber

PP Power Penalty

PRBS PseudoRandom Bit Sequence

PSK Phase-Shift Keying

PVT Process-Voltage-Temperature

QFN Quad-Flat No-lead package

RCLED Resonant Cavity Light Emitting Diode

RF RadioFrequency

RMS Root-Mean-Squared

RVT Regular Threshold Voltage

RZ Return to Zero

SI Step-Index

SM Single-Mode Fiber

SMA SubMiniature – Version A

SNR Signal to Noise Ratio

SOLT Short Open Load Through

SP Standard Performance

SR Shift Register

TAT TransAtlantic Telecommunications cable

TIA TransImpedance Amplifier

UMC United Microelectronics Corporation

USB Universal Serial Bus

VCO Voltage-Controlled Oscillator

VCSEL Vertical-Cavity Surface-Emitting Laser

VGA Variable Gain Amplifier

VNA Vector Network Analyzer

WDM Wavelength-Division Multiplexing

#### CHAPTER 1

## 1. Introduction

- 1.1. Optical Communications

- 1.2. CMOS Technology

- 1.3. State of the Art

- 1.4. Objectives

- 1.5. Thesis Organization

- 1.6. References

Physics has been characterized by a continuous progress. In this progress, some remarkable leaps can be identified over the ages that have led to the rapid development of particular fields of knowledge. The first great physicist who comes to our mind is Isaac Newton who is considered the most important scientist of all times. His work, *Philosophiæ Naturalis Principia Mathematica* (Mathematical Principles of Natural Philosophy), published in 1687, includes two main scientific contributions: universal gravitation and the laws of motion. Both establish the basis for classical mechanics that governed the scientific view of the physical universe for the next three centuries until relativity was confirmed.

Based on Newton's mechanics, Gottfried Leibniz postulated the conservation of a quantity connected with motion denominated *vis viva*. In 1783, Antoine Lavoisier and Pierre-Simon Laplace reviewed the concept of *vis viva* and the caloric theory, suspecting that there was a relationship. Eventually, the conservation of energy was described and broadly assumed. Thomas Young introduced the well-known concept of energy in 1807. The generalization of the conservation of energy is one of the basic principles of thermodynamics and it is still valid.

1

In the nineteenth century, three research fields of physics were under study: electric and magnetic fields, and light. James Clerk Maxwell expounded the unified field theory based on the laws introduced by Carl Friedrich Gauss, André-Marie Ampère, and Michael Faraday. Maxwell's equation appears for the first time in the article "A Dynamical Theory of the Electromagnetic Field," published in 1864. The unification of the electric and magnetic fields predicts an electromagnetic wave traveling at the speed of light thereby confirming the wave behavior of light as defended by Christiaan Huygens.

The last leap in physics was achieved by the most important physicist of the twentieth century and the most famous scientist ever, Albert Einstein. In 1905, he postulated the special theory of relativity in one of the *Annus Mirabilis papers* entitled *Zur Elektrodynamik bewegter Körper* (On the Electrodynamics of Moving Bodies), which is considered the starting point of "modern physics." Then, in 1915, Einstein published an extension of relativity by including gravitation denominated as the general theory of relativity. Some predictions of these path-breaking theories have been confirmed. Nevertheless, he received the Nobel Prize in 1921 for the explanation of the photoelectric effect, a confirmation of the particle nature of light leading to particle-wave duality, and eventually to quantum physics, another research field that saw great development during the twentieth century.

There has been another leap from Einstein's time to the present. Even though research in physics is multidimensional and growing all over the world rapidly, making identification of major changes difficult, microelectronics might be considered as the new leap. The world has changed enormously with the advent of microelectronic technology. Computers and mobiles go with us wherever we go, and a continuous connection to the world is available for everyone.

#### 1.1. Optical Communications

Within the revolution of microelectronics, optical transmission is the key to create broadband communication networks. The increase in users and the capacity per user are only fulfilled by this kind of transmission. In this section, a historical introduction, a brief discussion about emerging applications, a comparison between different communication links, and an overview of an optical link are included.

#### 1.1.1. A Look at History

Rudimentary communications systems based on light were used in antiquity, such as fire beacons and smoke signals. Despite the very limited information capacity of this technique when compared to the information carried by messengers, two advantages must be highlighted: the message could reach several receivers simultaneously and the speed of the transmission is unbeatable. Therefore, this method was preferred for alarm signals, especially in periods of war. For example, the Greek tragedian Aeschylus describes how the message of the fall of Troy (1184 BC) was sent by fire signals via an unbroken line of beacon-fires from Asia Minor to Mycenae (Greece) covering a distance of 600 km in the Oresteia trilogy (458 BC).

By these systems, only a limited number of predetermined messages could be transmitted because of the lack of a transmission code. In "The Histories," the Greek historian Polybius describes the first known telegraph developed by Aeneas. Based on a water level, the entire Greek alphabet could be transmitted by fire signals using a two-digit, five-level code. By means of torches, a protocol was established to start and stop the emptying of identical receptacles simultaneously. Thus, the level of water corresponded to a predetermined message.

There were no significant advances for transmission based on light until the French revolution in the eighteenth century. The civilian Claude Chappe, a former priest, invented a mechanical—optical telegraph. It consisted of a column with a movable crosswise beam and two arms. Each arm had seven positions, and the crosswise beam had four more, permitting a 196-combination code. The equipment acting as repeater stations stood on rooftops of towers located approximately 10–25 km apart. The first telegraph line of this sort was put into operation in 1794 between Lille and Paris. It consisted of 22 stations over 240 km, completing a message transfer in only 2–6 minutes, whereas riding couriers would require 30 hours to perform the same task. Other lines were built, including a line from Paris to Toulon, 765 km via 120 stations, connecting the capital of France with the Mediterranean Sea, and another extending the line via Lille to Brussels in 1803 and Amsterdam in 1810.

The era of electrical communication began in 1838 through the invention of the electrical telegraph by Samuel Morse. In contrast to the optical telegraph that was not suitable for transmission at night even with the lamps attached to the arms, the new transmission method could be used at night and at an increased data rate of about 10 bit per second. The first successful transoceanic telegraph cable between the United States and Europe was put into service in 1865. Later, the telephone was invented by Alexander Graham Bell in 1876 and radio communication was made possible by the contributions of Maxwell (1873), Hertz (1887), and Marconi (1895). Electrical communication systems have evolved considerably since then and bit rates of hundreds of Mb/s have been achieved. However, the distance between the repeaters for a high-speed system is rather small (~ 1 km), which makes it relatively expensive to operate.

The interest in using light as carrier of communication is reflected in one anecdote. Alexander Graham Bell also invented the photophone in 1880. He considered this discovery greater than his previous one, the telephone. In the photophone, vibrations in the voice from the emitter caused movements in a mirror. Then, light reflected on this mirror excited a selenium crystal to vibrate in the receiver. Although the invention was tested successfully, it failed at night, in rain, or while passing through an obstacle.

All the problems in optical transmission are related to the lack of a transmission channel. However, scientists have realized that the bandwidth-length product of the transmission system can be enhanced if optical waves were used as the carriers. Unfortunately, neither a coherent optical source nor a suitable transmission medium was available until 1970. Optical fibers were suggested as the transmission medium and the advent of the laser in the early 1960s solved the first problem. However, despite the introduction of cladding by Abraham van Heel, the attenuation of the purest glass produced was too high (1000 dB/km) for long-distance transmission.

Fig. 1.1. Evolution of communication technologies [MIT05].

In 1966, Charles Kao and George Hockam published an article [KAO66] that predicts the feasibility of this kind of communication if the transmission loss was reduced to <20 dB/km. Moreover, they proved that there were no fundamental technicalities that would prevent this loss from being achieved. It represents such a milestone that Charles Kuen Kao was awarded the Nobel Prize in Physics in the year 2009 "for groundbreaking achievements concerning the transmission of light in fibers for optical communication." He shared this honor jointly with Willard S. Boyle and George E. Smith "for the invention of an imaging semiconductor circuit – the CCD sensor" [NOB09]. Four years later, in 1970, the goal of reducing transmission loss to <20 dB/km was achieved by Robert Maurer, Donald Keck, and Peter Schultz of the Corning Glass Corporation. The attenuation was reduced by doping the fiber with titanium. In 1980s, the attenuation loss was reduced further thereby defining the first generation of long-haul optical links that target a superior distance between the repeaters than its electrical counterpart. The first international undersea link, from England to Belgium, was installed in 1986. Two years later, the first intercontinental optical fiber system, TAT-8 between the United States and Europe, was put into service with a total spanned distance of 6100 km and a distance between the repeaters of about 40 km.

Table 1.1 summarizes the evolution of long-haul optical communications. Every generation is characterized by a considerable increase in the bit rate-distance product. Second and third generations were based on the development of lasers and detectors operating at longer wavelengths, minimizing the attenuation and the dispersion of the fiber. Once minimal losses were achieved, optical amplifiers were introduced to regenerate the signal, extending the electrical repeater space hugely. At the same time, bit rate was increased by wavelength-division multiplexing (WDM). Both improvements represent the fourth generation. The era of terabit communications systems has truly arrived with the fifth generation [GRA02], which is based on dense wavelength-division multiplexing (DWDM), forward error correction, distributed Raman amplification and solitons (transmitted pulses that are not degraded due to the compensation between dispersion and nonlinearity). In 2009, an article on transmission

was published [SAL09], which targeted a bit-rate distance product exceeding 100 Pb/s over 155 channels by digital coherent detection and phase-shift keying [GNA05]. The revolution in communications showing the crossover point to optical technology is illustrated in Fig. 1.1.

| Gen  | Year | Bit Rate Rs. | Distance D | R <sub>c</sub> D Product | .~       | Achievements / Properties                                                                   |

|------|------|--------------|------------|--------------------------|----------|---------------------------------------------------------------------------------------------|

| 18:1 | 0861 | 45 Mb/s      | 10 km      | 150 Mb/s - Am            | uni 8 O  | superior repeater space<br>than electrical communication<br>graded-index fiber              |

| 2119 | 1987 | 17.0%        | 50 km      | 85 Gbs · km              | 13 pm    | single-mode fiber<br>minimum dispersion<br>liber loss - 1 dB/km                             |

| Зrd  | 0061 | 2.5 Glvs     | 70 km      | 175 Gb/s - km            | 1.55 µm  | ninimal loss (* 0.2 dB/km)<br>dispersion-shitted fiber                                      |

| Í    | 9061 | \$ Glv's     | 11300 km   | 56.5 Tb/s+km             | 1.55 µm  | erbium-doped<br>optical amplifiers                                                          |

| Ē    | 2000 | 100 Cib/s    | 9000 km    | 900 Th/s · km            | 1.55 pm  | wavelength-division<br>multiplexing (WDM)                                                   |

| Đ.   | 2002 | L 28 Tb/s    | 4000 km    | 5120 Tb/s · km           | 1 S5 µm  | solitons distributed Raman amplification forward error correction dense waveleneth-division |

|      |      |              |            |                          |          | muliplesing (DWDM)                                                                          |

|      | 2009 | 15.5 Tb/s    | 7200 km    | 112 Pb/s · km            | 1.55 gun | phase-shift keying (PSK)<br>digital coherent detection                                      |

Table 1.1. Generations of optical fiber for long haul applications [AGR97, GRA02, SAL09].

## 1.1.2. Emerging Applications

Historically, as only optical links satisfy the demands for bit rate-distance product they have been traditionally exploited for long-haul communications. The considerable cost of the optical system is shared among a large number of potential users. If a cost-effective solution is achieved, a wide range of applications could be covered. In the following sections, more possibilities that are promising are discussed.

#### **Short-Haul Networks**

Currently, bandwidth demands for short-distance communications are increasing exponentially [ZIE08]. Thus, the conversion from electrical to optical transmission, as for long-haul communications, could be more beneficial than the improvements in transmission through cooper wires. Despite the advantages, the definition of beneficial is purely based on cost.

To make short-distance fiber communication affordable, the industry has developed low-cost solutions such as high-bandwidth multimode fibers and 850 nm transceivers. Eventually, fiber optics will spread in local area networks (LANs) and new systems like fiber-to-the-home (FTTH) will be commercially available [BRI08]. Home networking is commencing; even as the required bit rate in FTTH applications is 100 Mb/s over 50 m, the goal set by some telecom operators for home networking is to achieve speeds of several Gb/s.

#### **In-Car Fiber-Optic Networks**

Optoelectronic systems have also become increasingly attractive for communication inside cars [FRE04]. To connect the ever-increasing number of in-car electrical devices, plastic optical fiber (POF) is used. In addition to the already mentioned benefits, POF networks provide a low-cost solution with an ease of handling and installation, compared to glass optical fiber.

Several protocols are employed, which can be differentiated in two main types: multimedia and security, where the priority is speed and total reliability, respectively. In 1998, an international consortium of car manufacturers and suppliers set up an open standard, the Media Oriented System Transport (MOST), which can connect the radio, the CD/DVD player, the navigation system, a Bluetooth interface, telephones, games consoles, and a voice-recognition system inside a car. Another multimedia protocol is the IDB-1394, the automotive version of IEEE-1394. Security protocols have been developed to communicate with the rapidly growing number of sensors, actuators, and electronic control units within cars. For instance, BMW's Series 7 models implement byteflight for control of the car's air-bar systems, whereas FlexRay is the standard that will be used in the next-generation drive-by-wire systems.

All currently in-car optical data bus systems are basically the same components: standard poly-methyl methacrylate (PMMA) POF, red (650 nm) emitting LEDs, and large silicon photoreceivers. Recently, 1 mm step index-POF (SI-POF) has been standardized as A4a.2 and is being used massively in the automotive sector (25 Mb/s) and industrial automation (100 Mb/s).

Fig. 1.2. Bandwidth - distance market map [MIT05].

#### **High-Speed Optical Interconnects**

The highest number of transistors per unit of area within a single chip has been doubled every 18–24 months according to Moore's prediction [MOO65]. Therefore, the processing speed has also been considerably enhanced and interconnects are becoming a bottleneck. Moreover, over the next decade, the bandwidth of interconnects inside a computer is expected to increase by an order of magnitude, from 1 GHz to 10 GHz, requiring some kind of internal optical data-bus to overcome this problem.

According to experts in the field, optics could be playing a role in board-to-board links soon although it will take some years before optical interconnects will be employed for chip-to-chip communication [SAV02, GRA04]. Optical interconnects has been suggested even to connect the subsystems within a single chip, but this approach is under intense discussion.

## 1.1.3. Comparison between Communication Links

Optical communications systems compete with electrical wire data transmission and wireless communications. The superior performance of optical communications, defined by bandwidth-distance product, has motivated a gradual conversion into photonic domain crossing the market transition zone to attain higher transmission speed, as illustrated in Fig. 1.2.

Very high performance fiber optic systems are relatively expensive; therefore, they are limited for applications where the cost is shared among a certain amount of users. For short reach applications, where several possibilities (electrical, optical, and wireless) of solving the same demand are offered in the market, two variables represent the breakpoint for the choice: cost and mobility.

The obvious advantage of wireless communications is the mobility. Particular users mandate devices permanently connected. Mobile and WiFi communications offers this possibility, although they cannot be considered a counterpart of optical communications. Neither mobile nor WiFi targets gigabit communications and their emitters and receivers must be connected by some communication system. In particular, the optical and WiFi combination is a very attractive idea.

Low-cost optical links are available and are very competitive with wire technology, spreading optical transmission to the mentioned emerging applications [HER07]. Although optical systems are more expensive than their electrical counterparts, their advantages and improvements could represent a more important factor than the difference of cost. Eventually, a reduction in terms of cost and design time for optical systems cannot be dismissed. Furthermore, the unlimited supply of sand to manufacture optical fibers avoids future price increases.

The dielectric character of optical fibers offers advantages over electrical counterparts, which make them interesting for certain types of applications. A brief discussion of these advantages is presented in the following sections.

Electromagnetic Interference. Optical carrier has no charge whereas an electrical one has. That little difference between optical and electrical data transmission leads to a great advantage. An electrical wire conducting a high-speed signal may act as a transmitting antenna and radiate noise, possibly causing interference-related problems in neighboring circuits. On the other hand, electromagnetic noise from the outside world may disturb data transmission. This issue has been traditionally solved by using heavy shielded cables or balanced lines with differential drivers and receivers. Optical fiber systems directly avoid electromagnetic interference (EMI), being an alternative for transmission through areas with an important electromagnetic pollution. For instance, they are applicable in industrial environments, where a considerable electromagnetic noise is caused by heavy industrial machinery. In the other direction, optical fibers are very attractive for applications with restrictions on the tolerable electromagnetic radiation, easing the noise immunity requirements for the subcircuits in large systems. The lack of emission also makes the optical fiber unbeatable for secure data or voice transmission, ensuring confidentiality.

**Galvanic Separation.** Ground potential may vary depending on the location. Thus, when an electrical signal is transmitted over a certain distance, ground loops need being solved. They manifest as currents flowing through the shield or ground wire of the interconnecting cable because of differences in the local reference potentials. Balanced lines, differential circuits, and optocouplers are commonly used to solve these issues. Optical transmission offers an ideal solution as it provides an inherent isolated data path.

**Security.** In some areas, safety must be maximized. Optical transmission offers an improvement, as no electrical current is conveyed. As a clear example, in an area with volatile chemicals any spark generated may lead to a catastrophe. In addition, fiber cables are not affected by corrosion, being well suited for corrosive environments. Furthermore, if the communication system must be manipulated, there is no possibility of electrocution or short circuit hazard.

**Weight.** An optical fiber is much lighter than an electrical wire for a given length. The light weight and small size make the fiber interesting for specific applications such as "fly by wire" technique in airplanes. The lightness of the fiber also enables a weightless to carry communication system, which is, for example, of interest in military tactical operations.

**Environment.** Electrical wires and optical fibers are manufactured from different raw materials. Glass for optical fibers is obtained from sand without affecting the environment in contrast with the extraction of copper. Therefore, based on ecological considerations, optical links must be chosen as it helps conservation of earth's resources.

## 1.1.4. Optical Link Architecture

This section presents an overview of the whole transmission system [RAZ03], from electrical to optical conversion and vice versa. The system consists of the transmitter, the transmission channel, and the receiver (Fig. 1.3). A similar subdivision can be easily observed in the transmitter and receiver, taking into account the digital and analog signal processing and the conversion between the electrical and optical signals.

The transmitter is subdivided as a serializer, a driver, and a light emitter. Several synchronous digital signals are multiplexed into a transmitted digital signal by the serializer. It consists of a multiplexer (MUX) and a frequency synthesizer, based on a phased-locked loop (PLL). Non-idealities caused by the MUX are absorbed by the retimer. The laser driver must provide the proper modulated current to the light emitter and usually incorporates power control. A laser is commonly used as the light emitter because of the higher output power and more spectral purity. For low cost solutions, a light-emitting diode (LED) can be adopted as the light emitter.

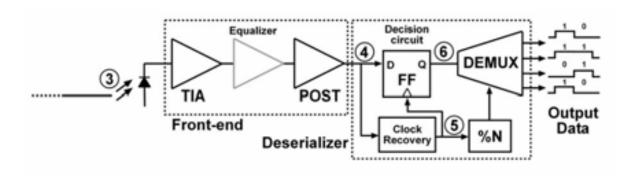

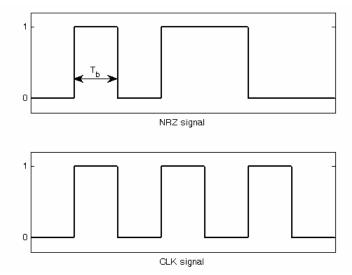

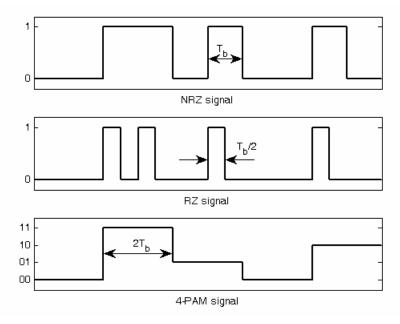

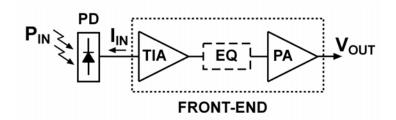

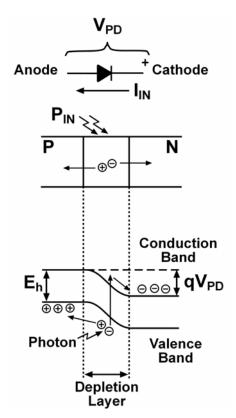

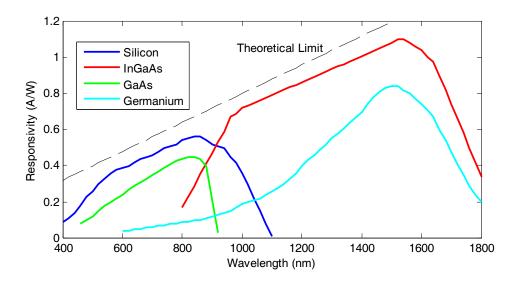

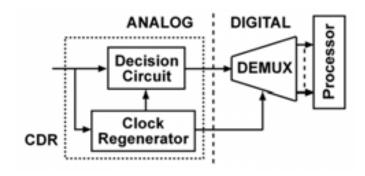

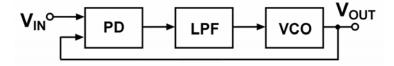

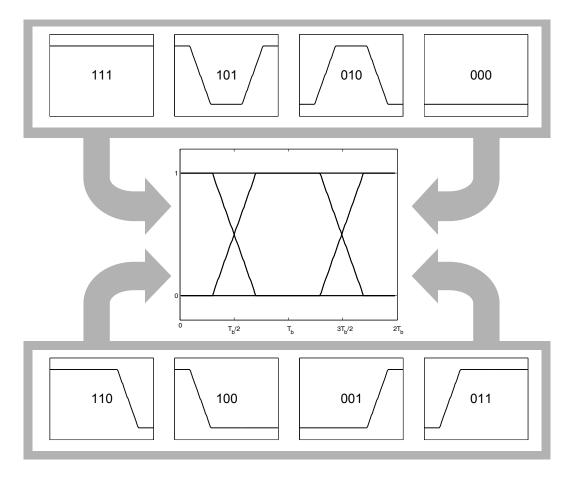

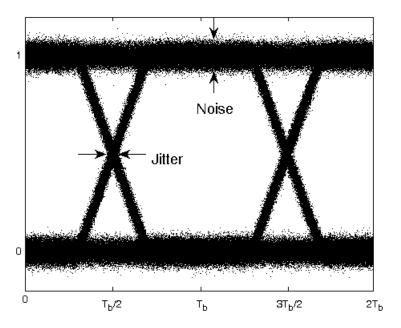

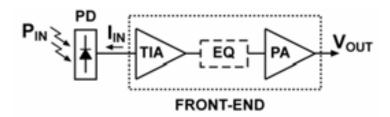

The receiver consists of a photodiode, a front-end, and a deserializer, as illustrated in Fig. 1.4. The photodiode converts the transmitted optical power into a current, which can be electronically processed by the front-end to provide a signal with sufficient quality. The front-end is basically formed by a transimpedance amplifier and a post-amplifier, which converts the photocurrent into a voltage and boosts such a voltage swing to logical levels, adequate for subsequent digital circuitry, respectively. A post-amplifier may consist of a simpler cascade amplifier chain, denominated as the limiting amplifier, or present additional circuitry to control the gain, denominated as automatic gain control (AGC) amplifier. This latter implementation offers linear operation for a wider range of input signal amplitude, permitting analog signal processing to be performed on the output signal. The equalizer is widely employed when the channel or photodiode causes band-limited effect, for instance, in POF channels or with complementary metal-oxide semiconductor (CMOS)-integrated photodiode. The deserializer must target two main functions: clock and data recovery and demultiplexing. First, from the received signal, it must recover the associated clock signal. Then, the received signal is converted to a digital signal by deciding between the two possible states indicated by the recovered clock. Finally, the digital signal is demultiplexed.

Fig. 1.3. Complete diagram of transmitter system.

This diagram can be generalized with optical wavelength multiplexing, including an array of transmitters and receivers [MUL07], one pair for each wavelength. Therefore, the required data rate for each transmitter/receiver is relaxed but the power consumption of the system is increased.

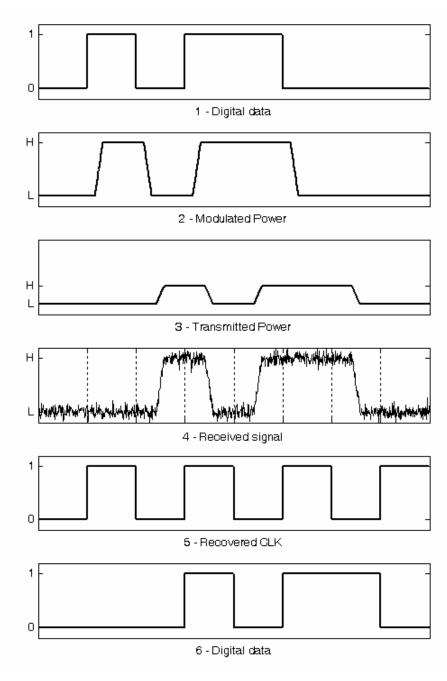

To summarize, Fig. 1.5 shows the typical signal along the transmission path. Corresponding places between these signals and Fig. 1.3 and Fig. 1.4 are indicated by numbers within circles. First, the serialized digital data is converted to a modulated optical signal by the driver. This signal is attenuated and dispersed along the optical fiber, and so, it must be processed by the front-end to recover the original data. The electronic noise from the front-end represents the main contribution to the output noise. Clock and data recovery circuit regenerates the clock and the transmitted data.

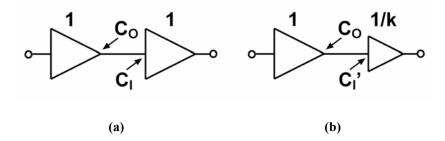

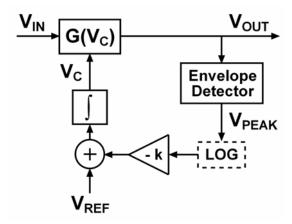

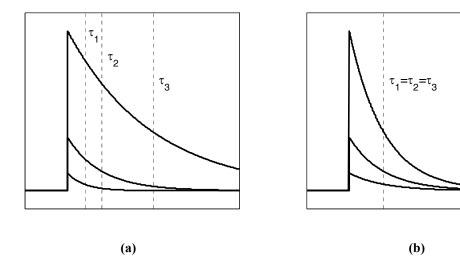

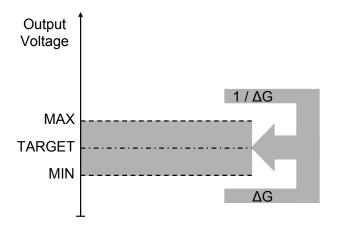

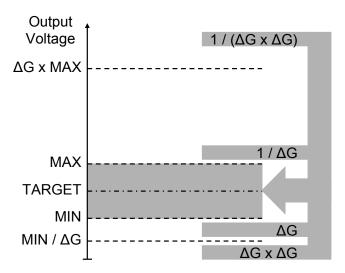

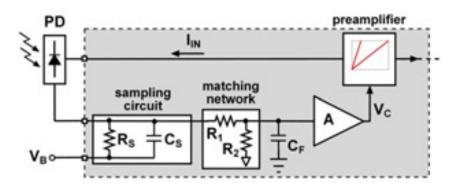

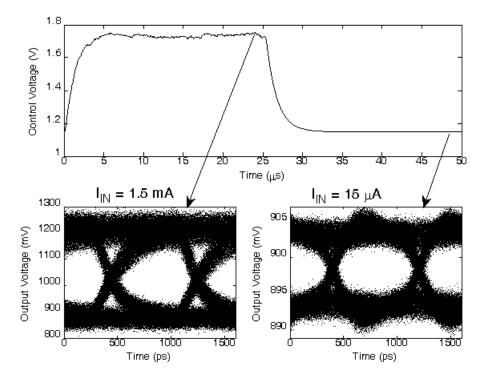

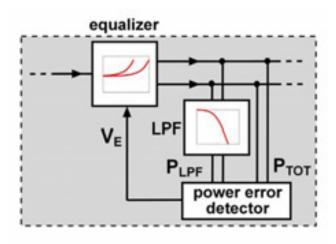

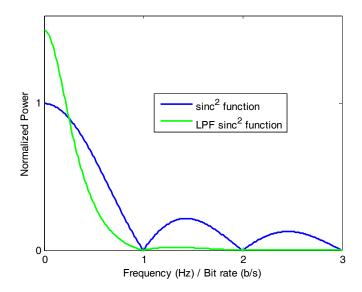

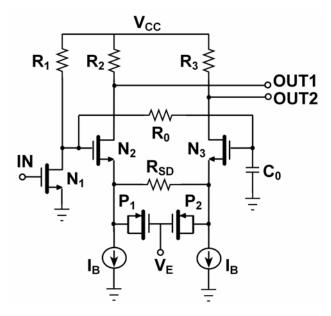

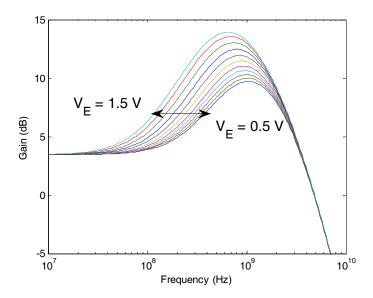

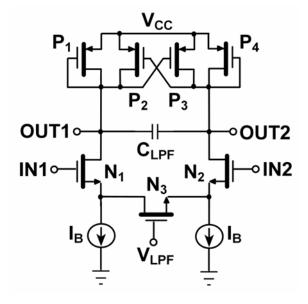

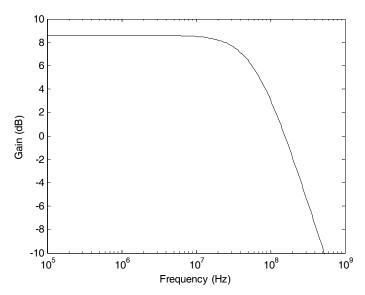

## 1.2. CMOS Technology