UNIVERSIDAD DE ZARAGOZA

ESCUELA UNIVERSITARIA DE INGENIERIA

TÉCNICA INDUSTRIAL DE ZARAGOZA

Escuela

Universitaria

Ingeniería

Técnica

Industrial

**ZARAGOZA**

Memoria del proyecto fin de carrera:

Sistema de control para máquina

cortacésped basado en

microcontrolador PSoC

Dirigido por:

Antonio Bono Nuez

Realizado por:

Víctor Arnal Herguedas

## **INDICE**

|                                                                               |           |

|-------------------------------------------------------------------------------|-----------|

| <b>1. INTRODUCCIÓN.....</b>                                                   | <b>5</b>  |

| 1.1 Motivación y objetivos.....                                               | 6         |

| 1.2 Descripción y alcance del proyecto.....                                   | 6         |

| <br>                                                                          |           |

| <b>2. REVISION HISTÓRICA DE MÁQUINAS CORTACÉSPED Y SITUACIÓN ACTUAL .....</b> | <b>7</b>  |

| 2.1 Introducción .....                                                        | 7         |

| 2.2 Historia de las máquinas cortacésped.....                                 | 7         |

| 2.3 Grillo S.p.A. .....                                                       | 9         |

| 2.4 Electrónica en máquinas cortacésped.....                                  | 11        |

| 2.5 Conclusiones finales.....                                                 | 11        |

| <br>                                                                          |           |

| <b>3. SISTEMA DE CONTROL BASADO EN PSoC .....</b>                             | <b>12</b> |

| 3.1 Propuesta de sistema de control .....                                     | 12        |

| 3.1.1 Microcontroladores: MC9S08.....                                         | 13        |

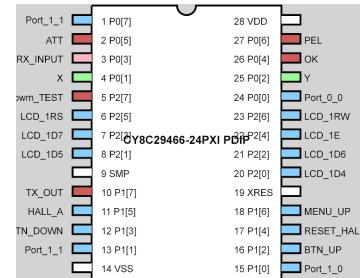

| 3.2 PSoC CY8C29466-24PXI.....                                                 | 16        |

| 3.2.1 Introducción/Generalidades .....                                        | 17        |

| 3.2.2 Arquitectura.....                                                       | 21        |

| 3.2.2.1 PSoC Core (Núcleo del PSoC).....                                      | 22        |

| 3.2.2.2 Sistema Analógico.....                                                | 23        |

| 3.2.2.2.1 Interfaz, array y comunicación del sistema analógico.....           | 24        |

| 3.2.2.3 Sistema Digital .....                                                 | 26        |

| 3.2.2.3.1 Interfaz, array y comunicación del sistema digital.....             | 27        |

| 3.2.2.4 System Resources (Recursos del sistema).....                          | 30        |

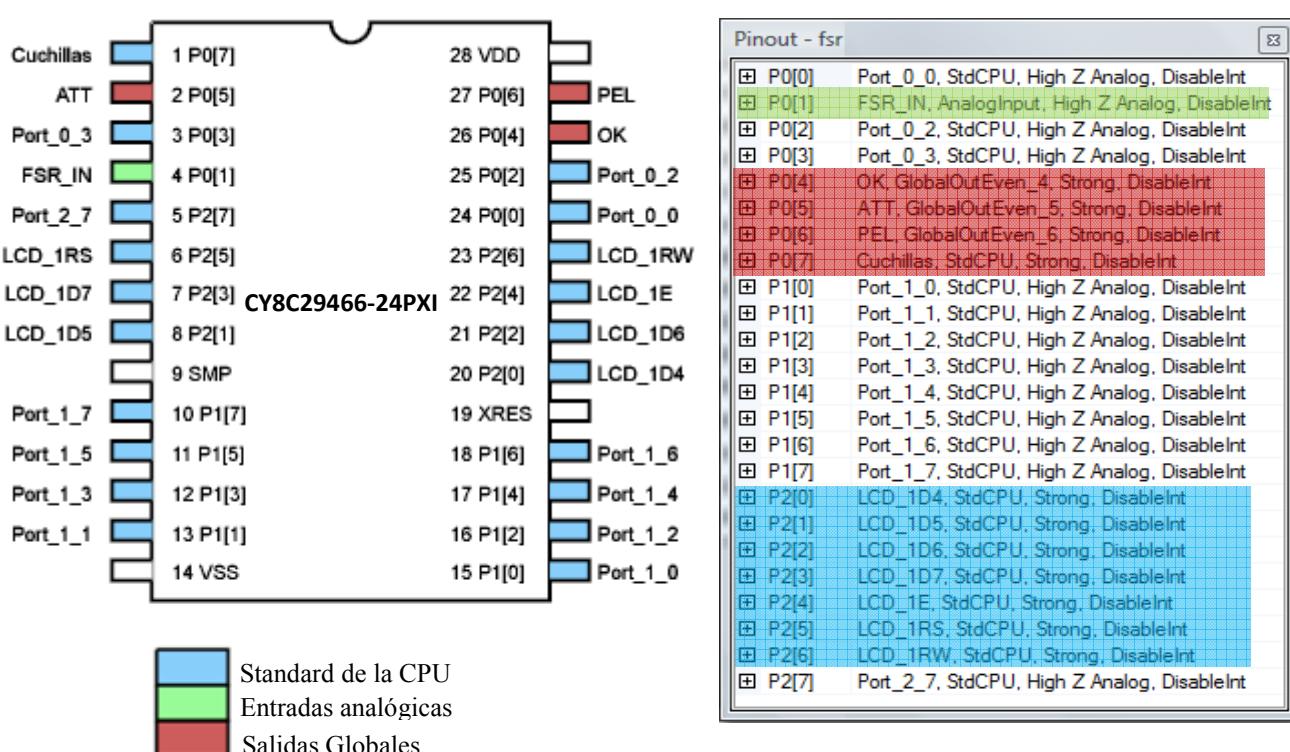

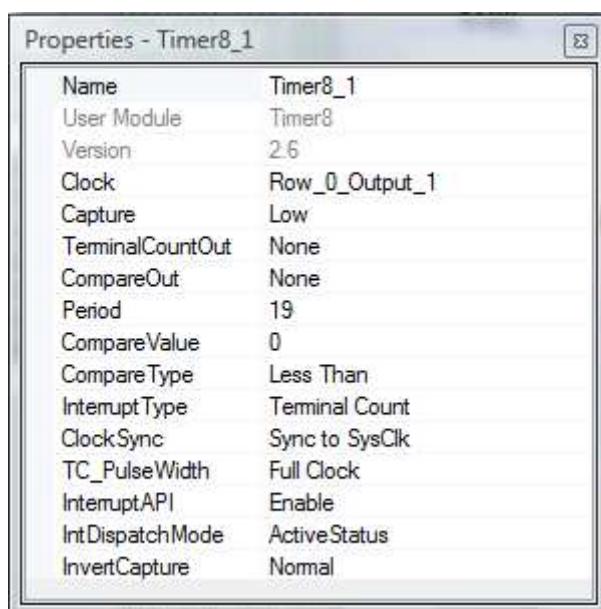

| 3.2.3 Entradas/Salidas - General Purpose Input Output(GPIO).....              | 35        |

|                                                            |    |

|------------------------------------------------------------|----|

| 3.3 Hardware y Software de diseño/programación PSoC .....  | 38 |

| 3.3.1 CY3210-PSoC EVAL 1 .....                             | 38 |

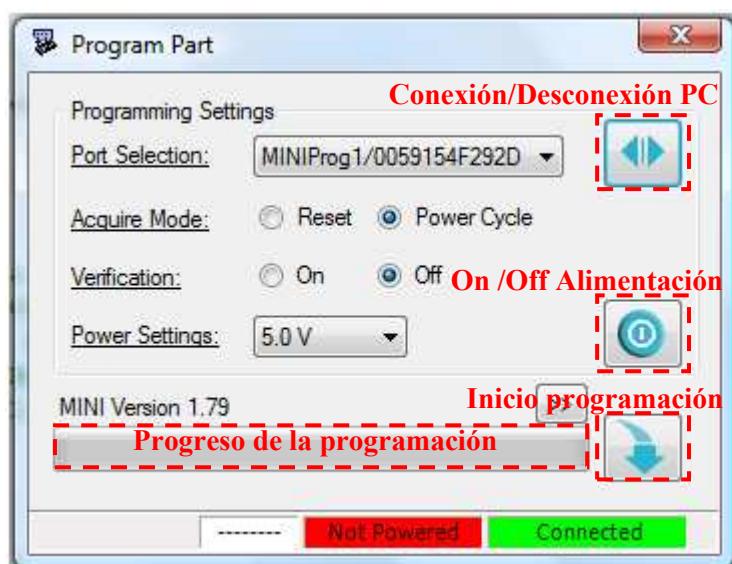

| 3.3.1.1 Placa de programación y mini programador .....     | 39 |

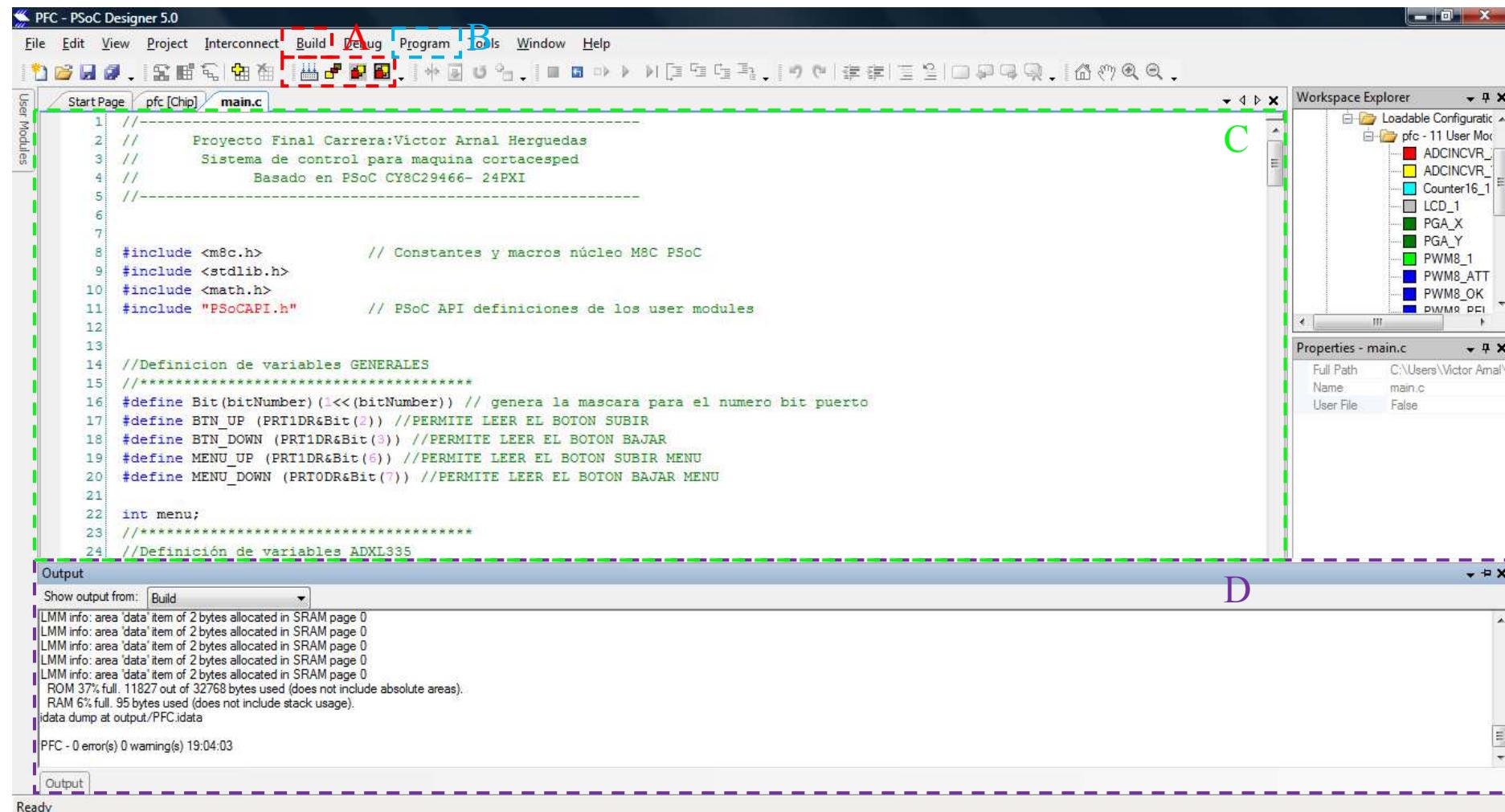

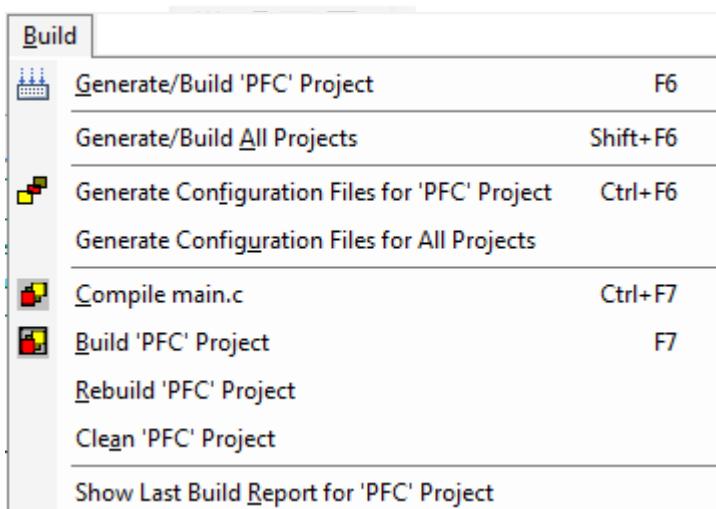

| 3.3.2 PSoC Designer .....                                  | 42 |

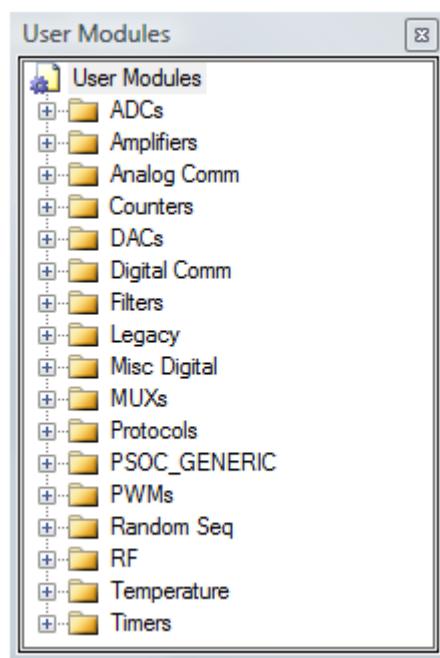

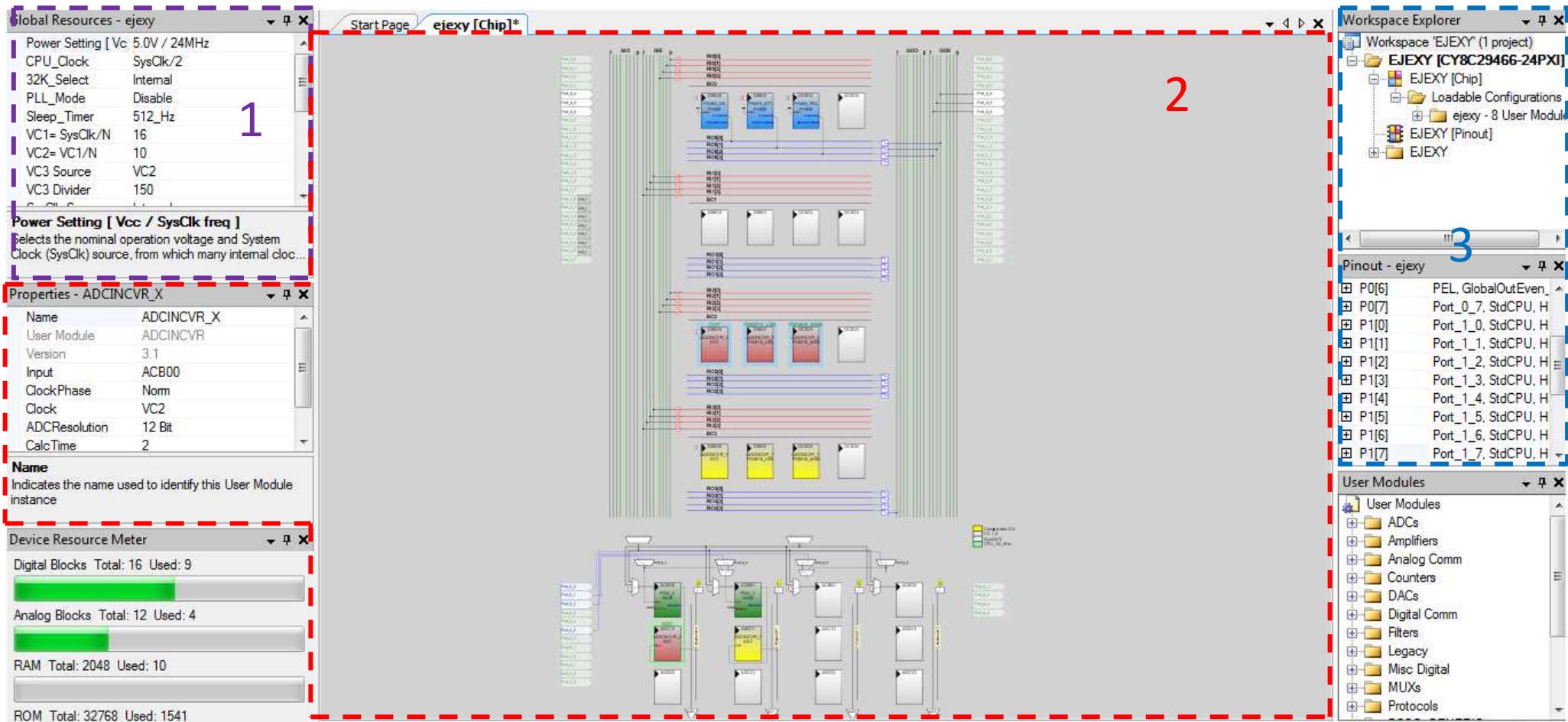

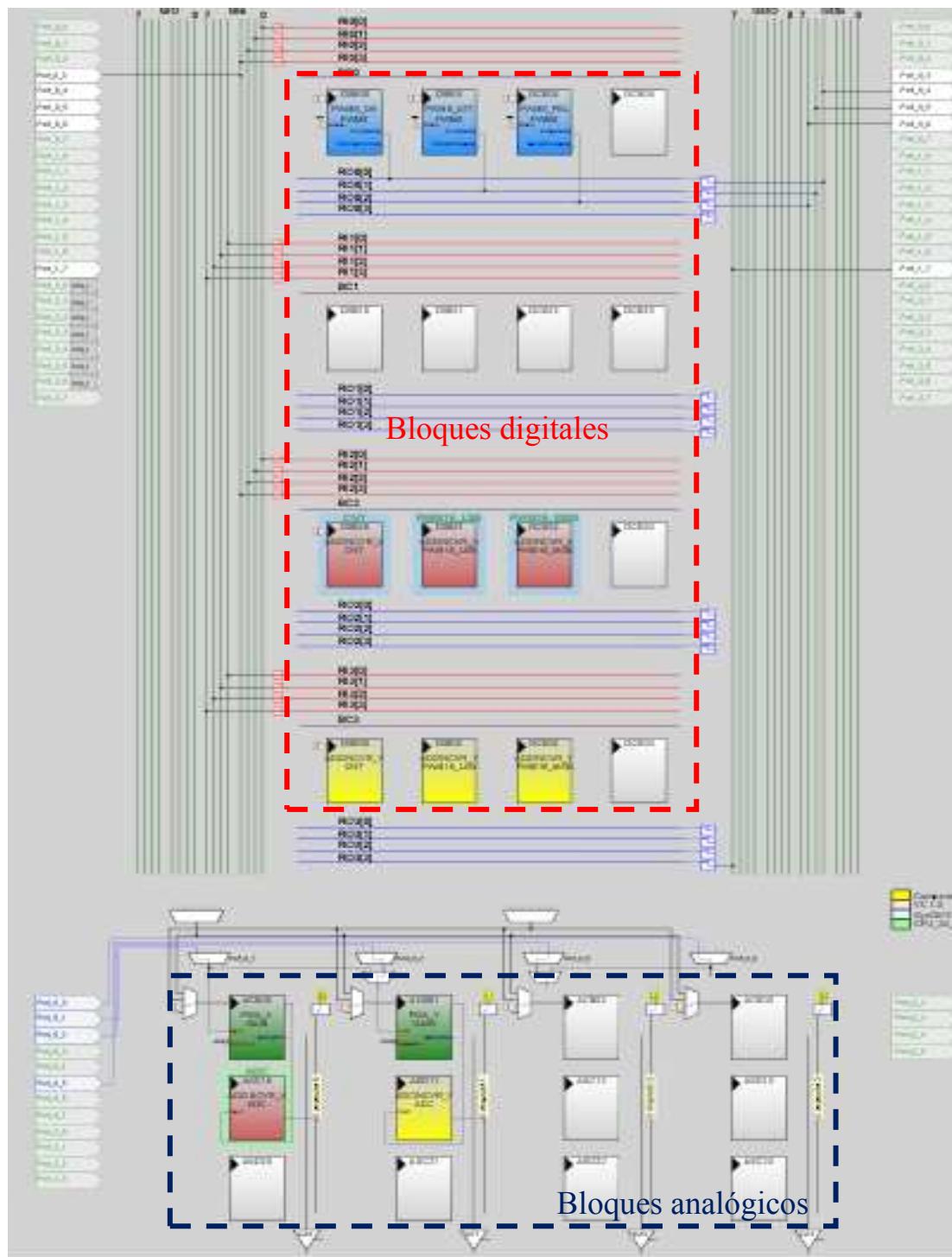

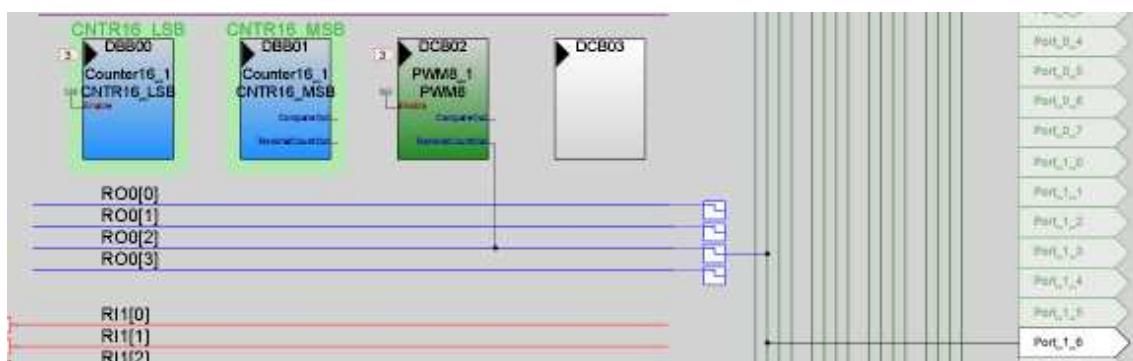

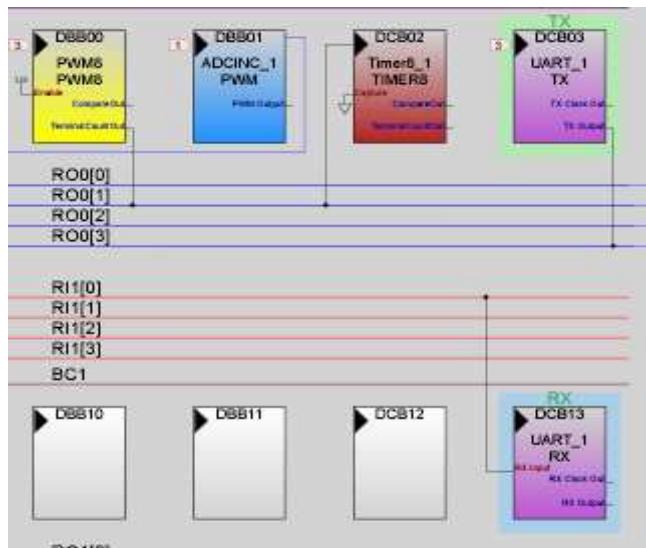

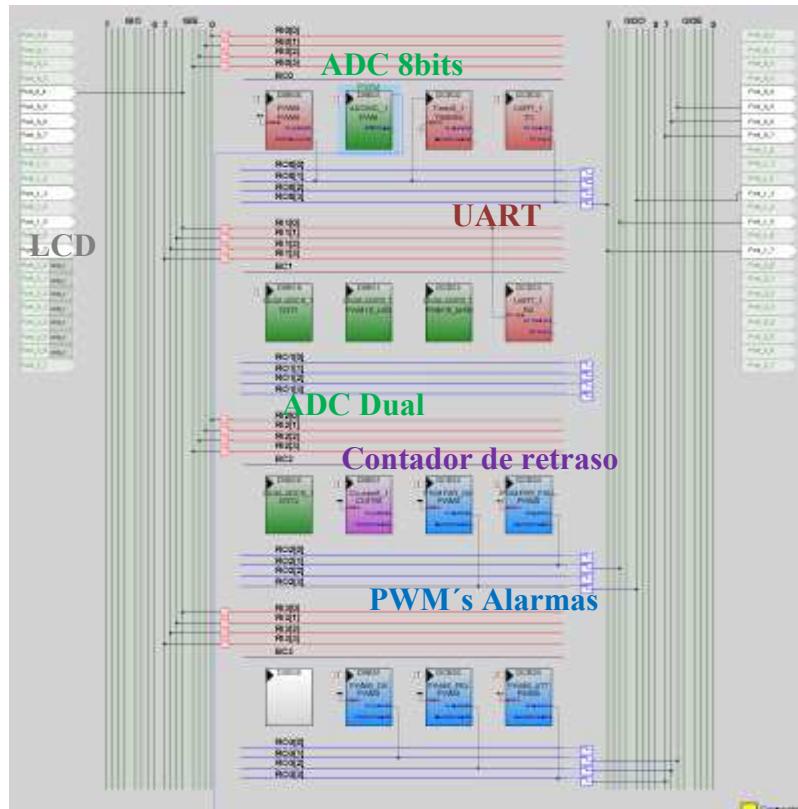

| 3.3.2.1 Editor de hardware (Device Editor) .....           | 43 |

| 3.3.2.2 Editor de software: .....                          | 48 |

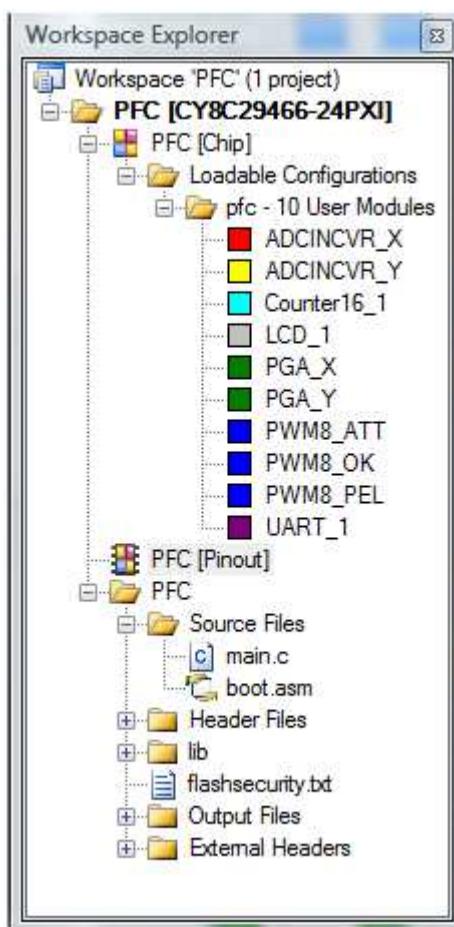

| 3.3.3 Módulos de usuario .....                             | 50 |

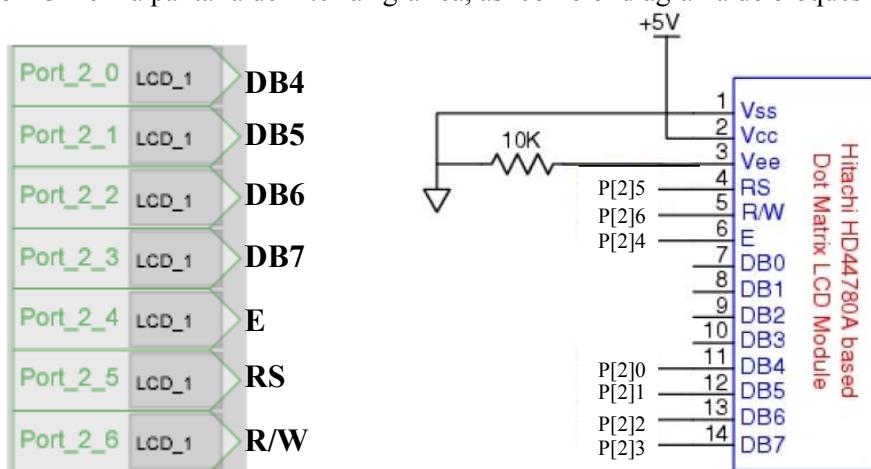

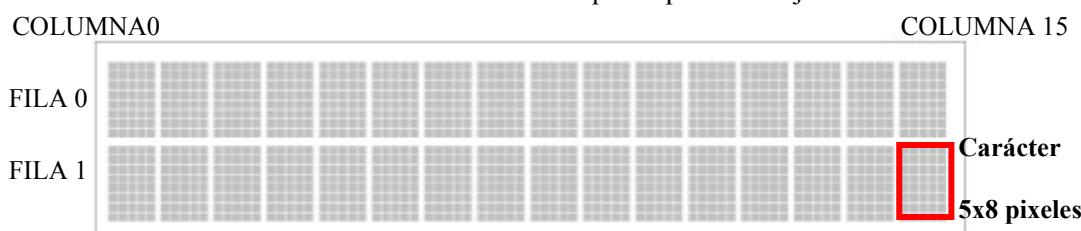

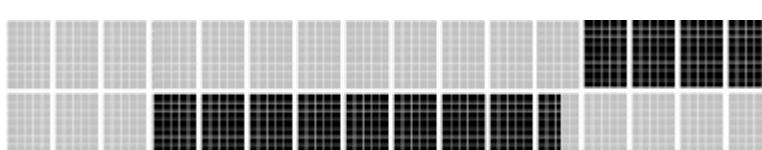

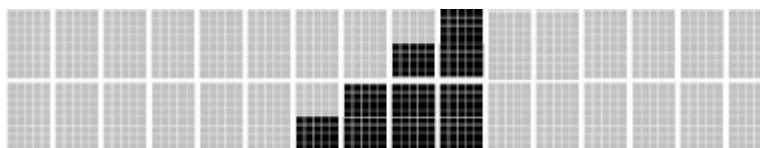

| 3.3.3.1 LCD.....                                           | 50 |

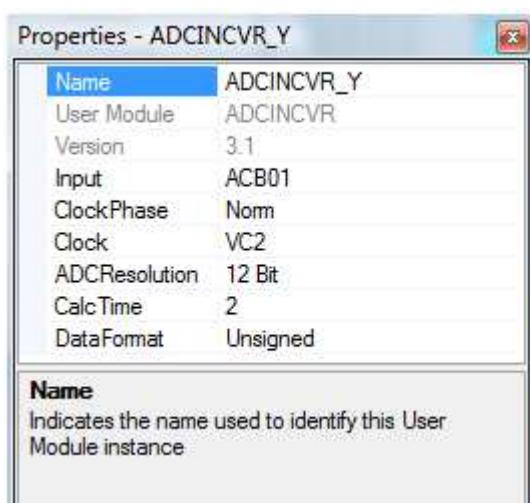

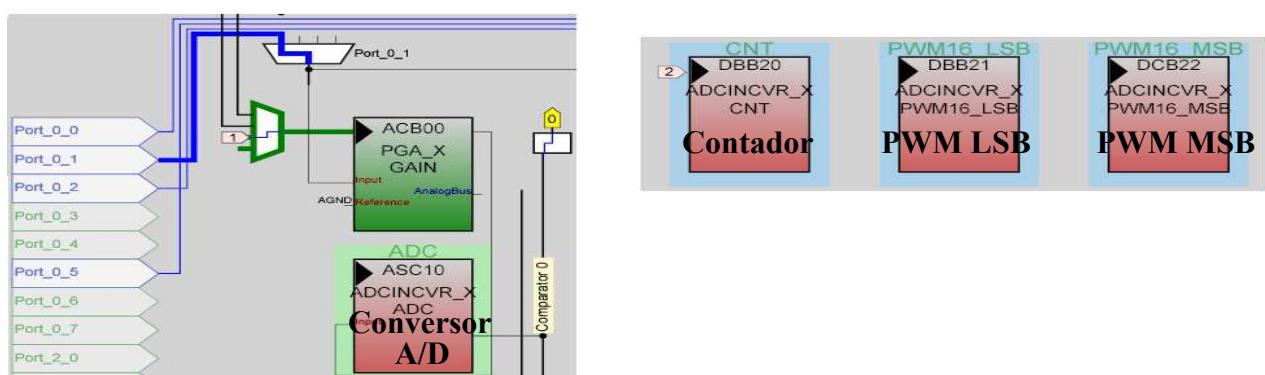

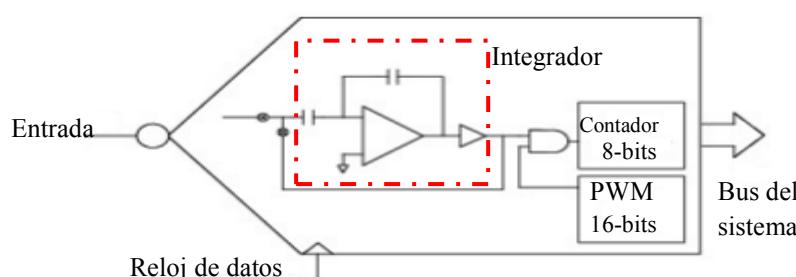

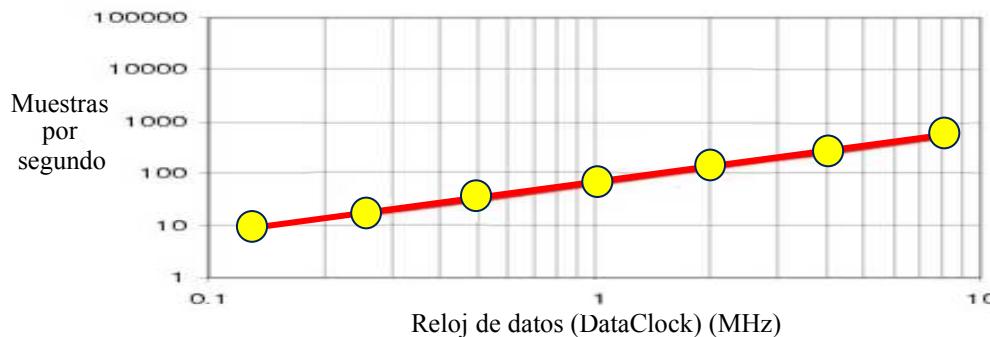

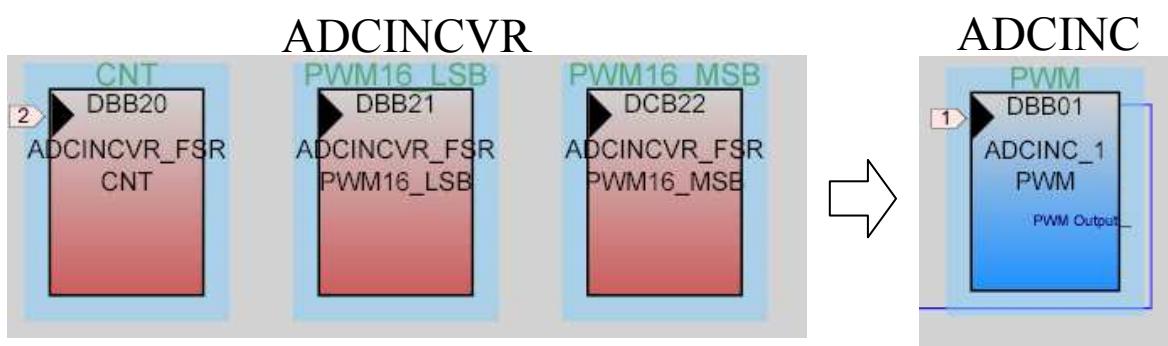

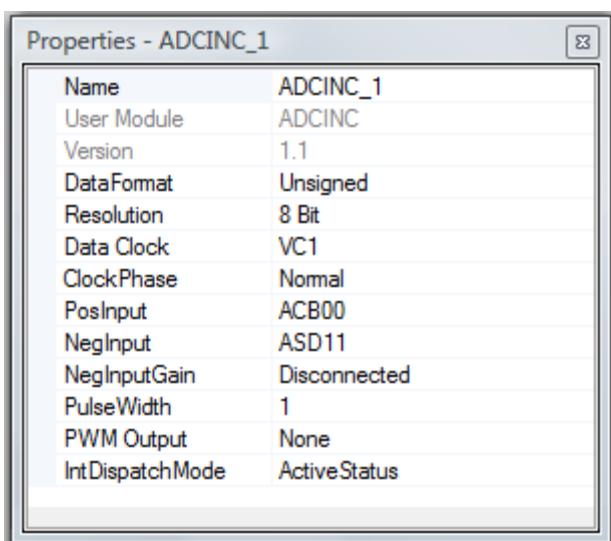

| 3.3.3.2 Conversores A/D.....                               | 53 |

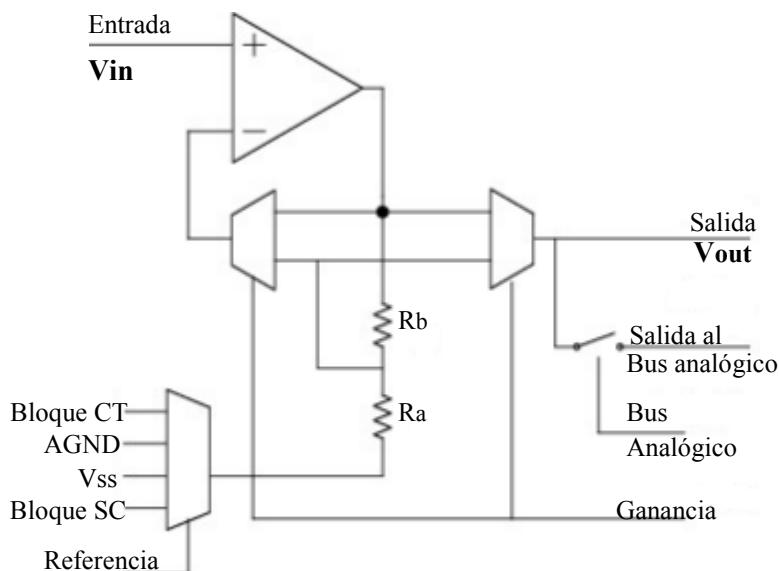

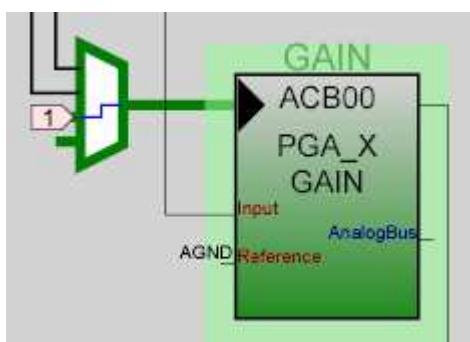

| 3.3.3.3 Amplificadores de ganancia programable (PGA) ..... | 57 |

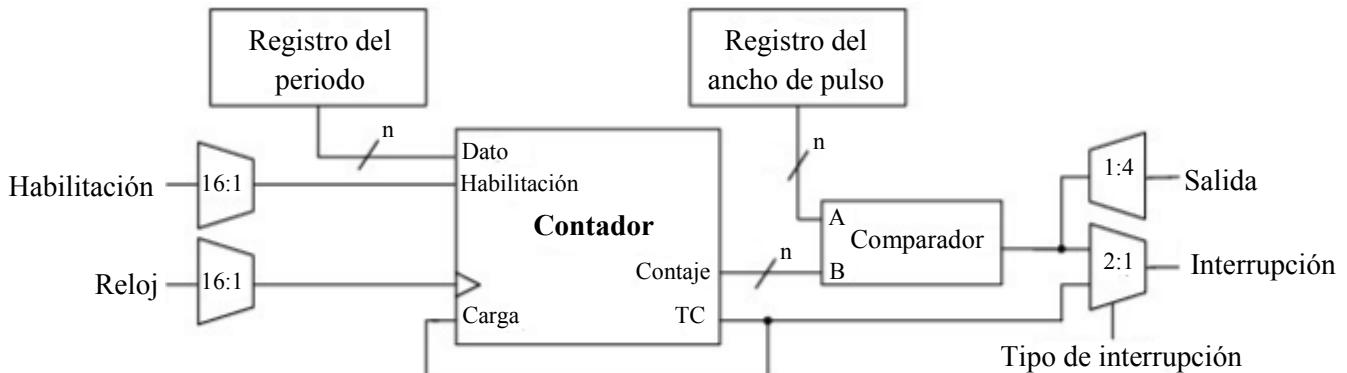

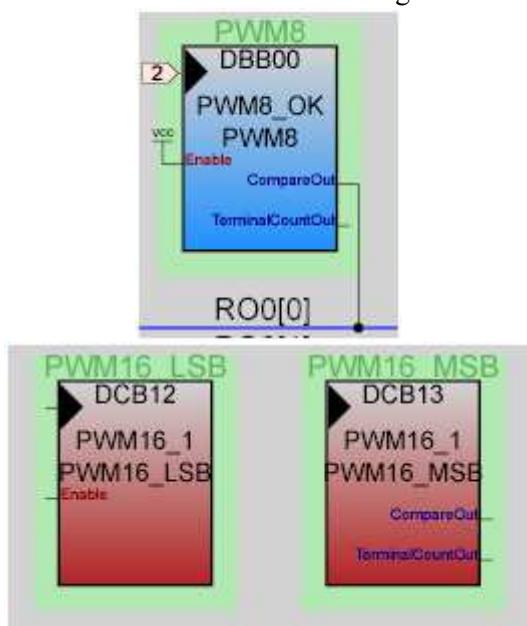

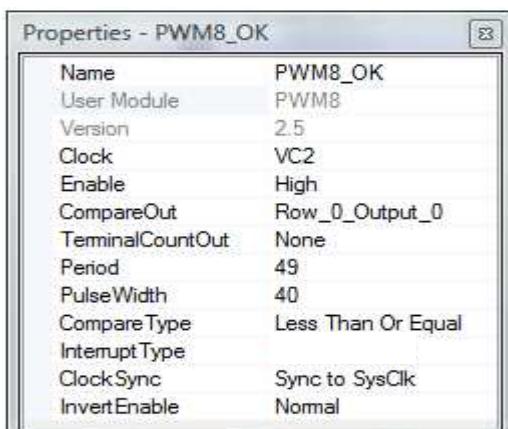

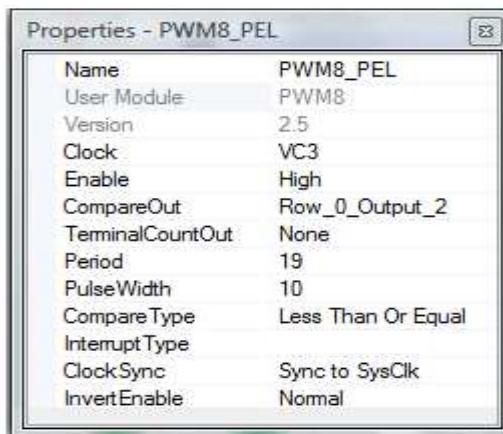

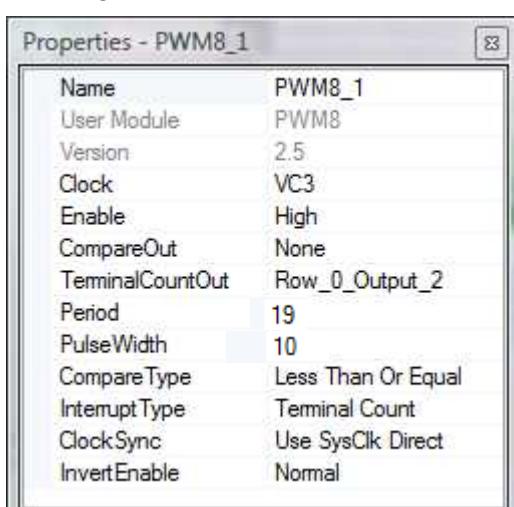

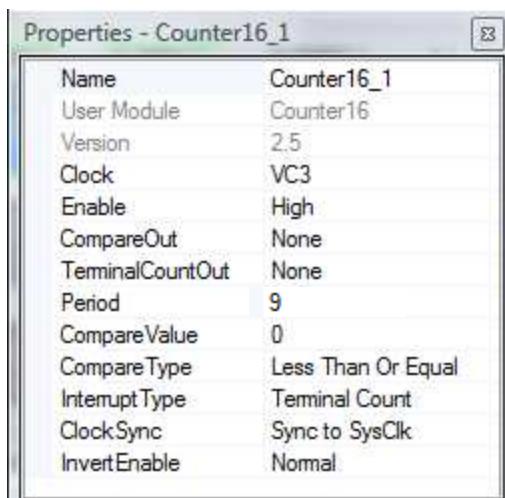

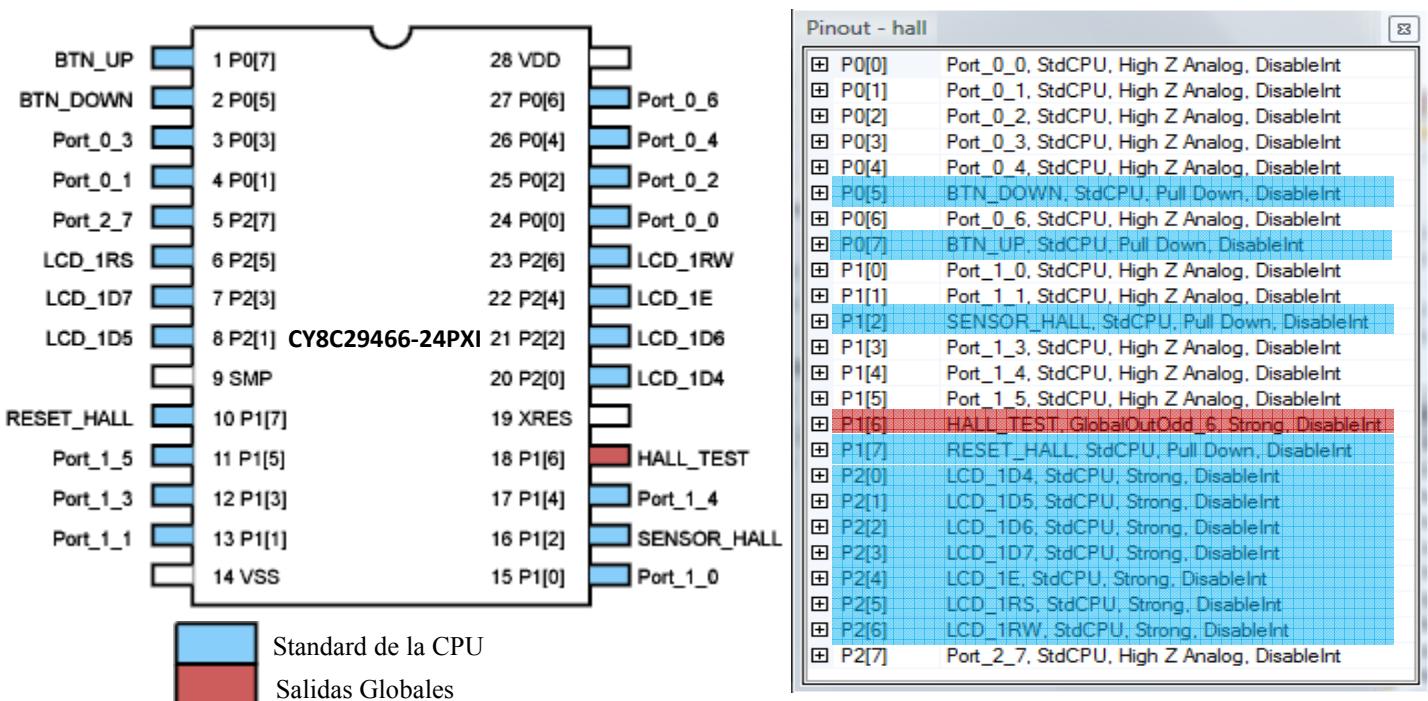

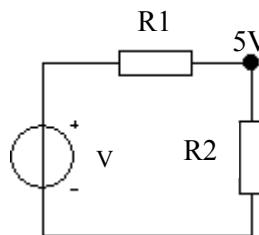

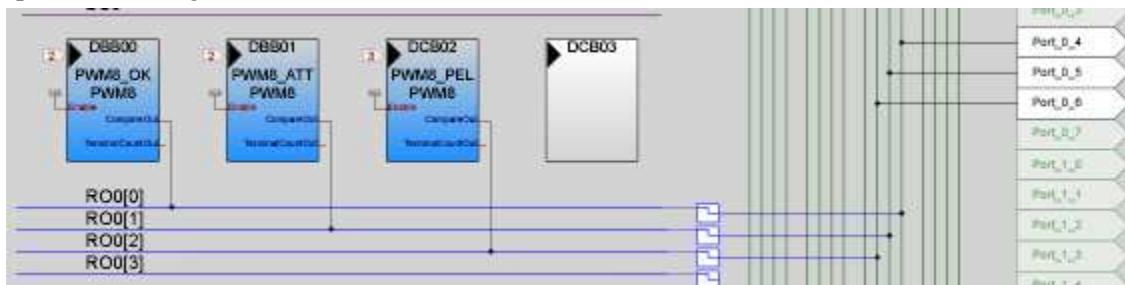

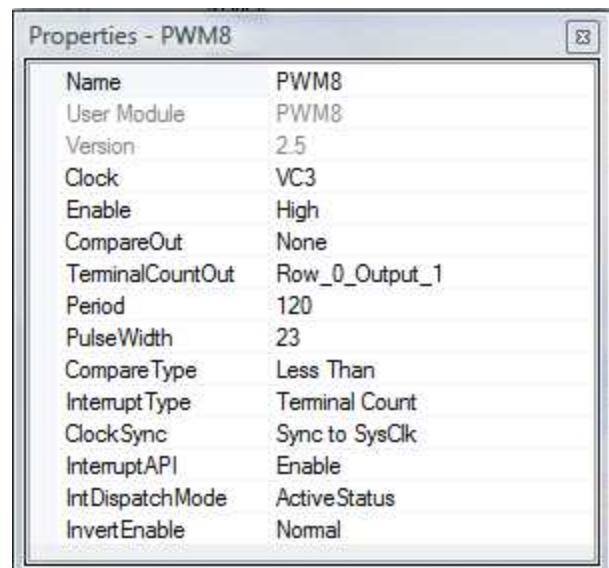

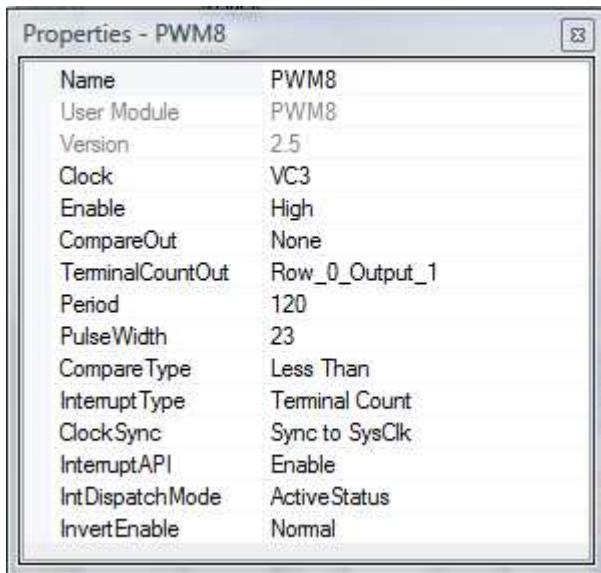

| 3.3.3.4 PWM's .....                                        | 59 |

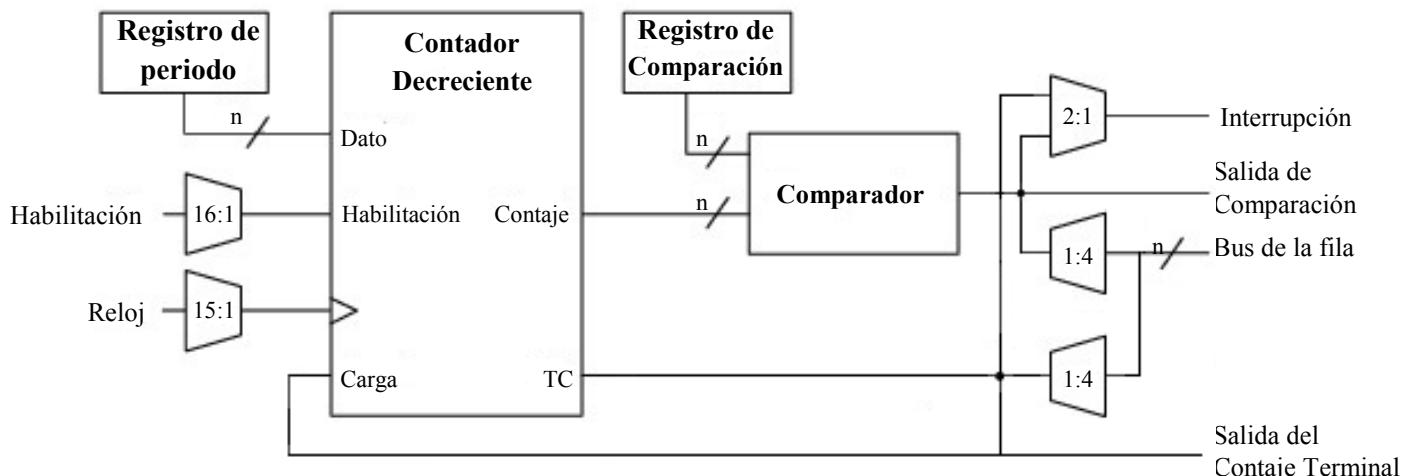

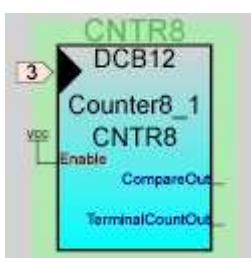

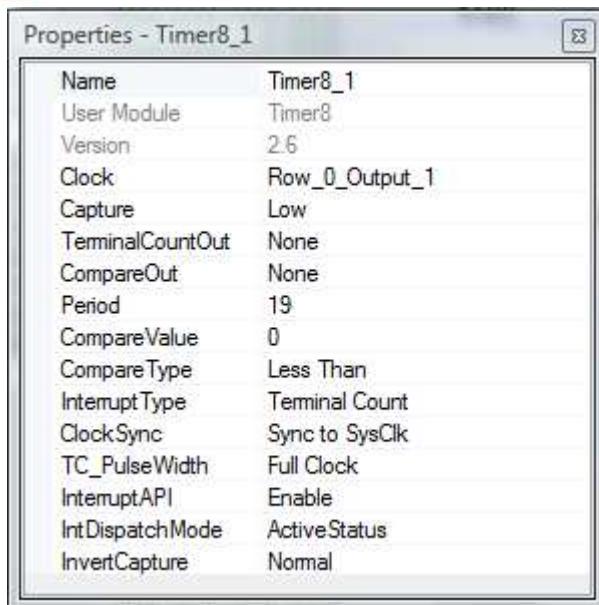

| 3.3.3.5 Contadores.....                                    | 62 |

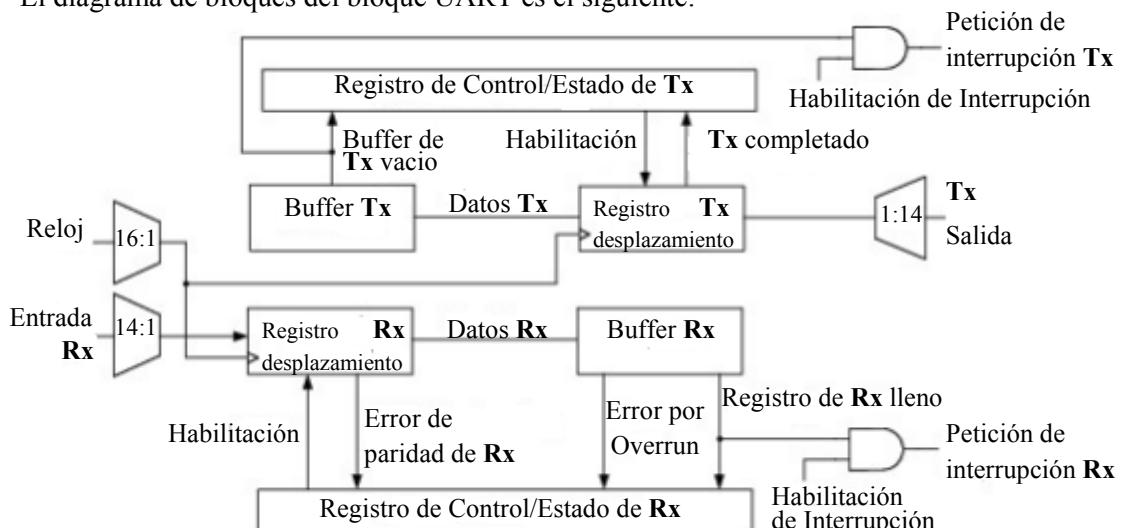

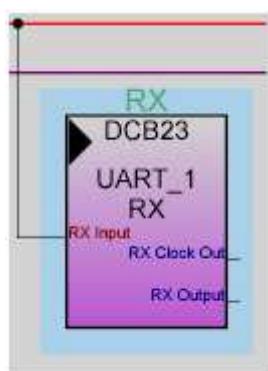

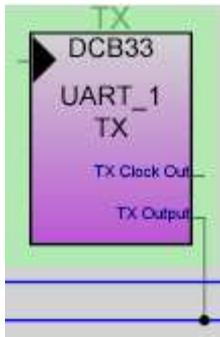

| 3.3.3.6 UART .....                                         | 64 |

#### **4. SISTEMA DE CONTROL ESTÁNDAR PARA MÁQUINAS CORTACÉSPED.....68**

|                                                              |    |

|--------------------------------------------------------------|----|

| 4.1 Introducción al sistema: Requerimientos .....            | 68 |

| 4.2 Descripción de variables/sensores a controlar.....       | 69 |

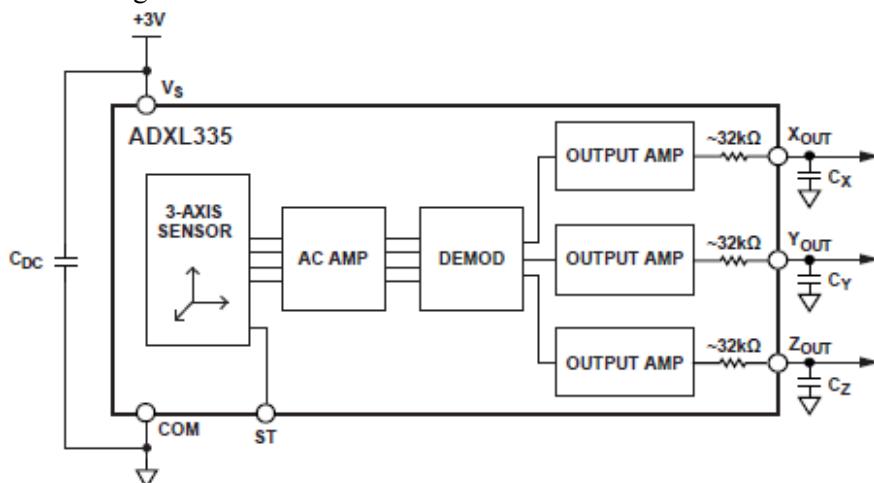

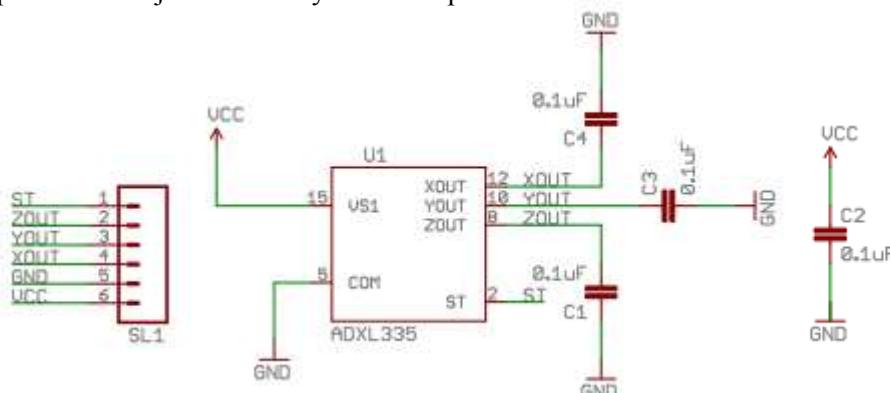

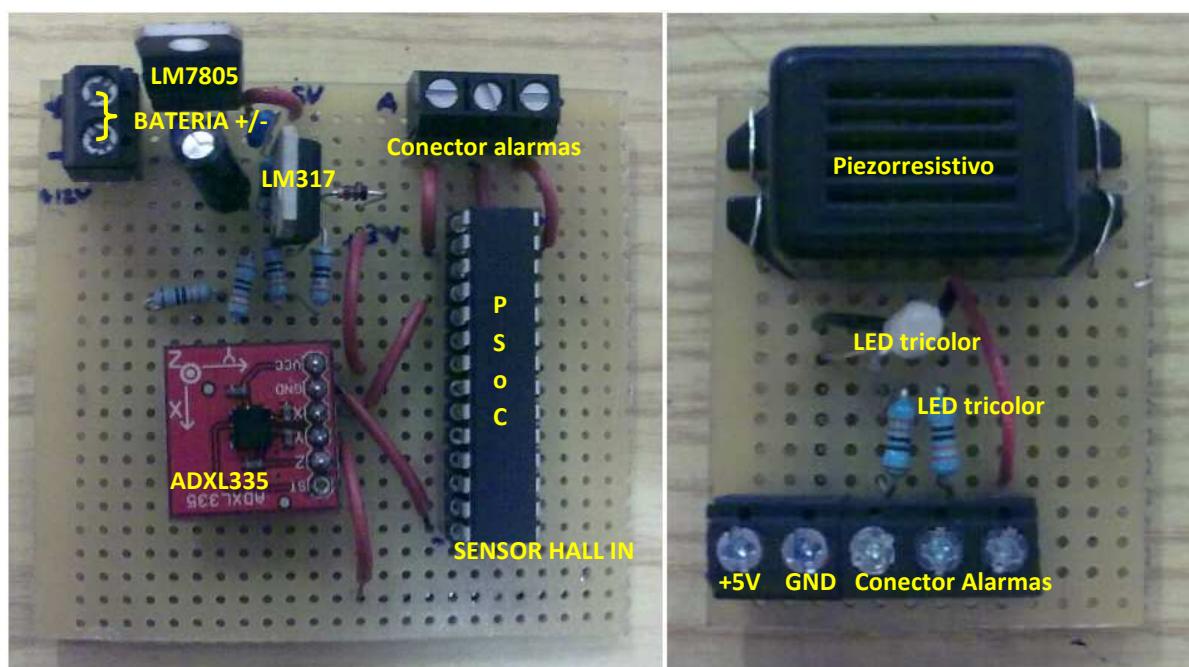

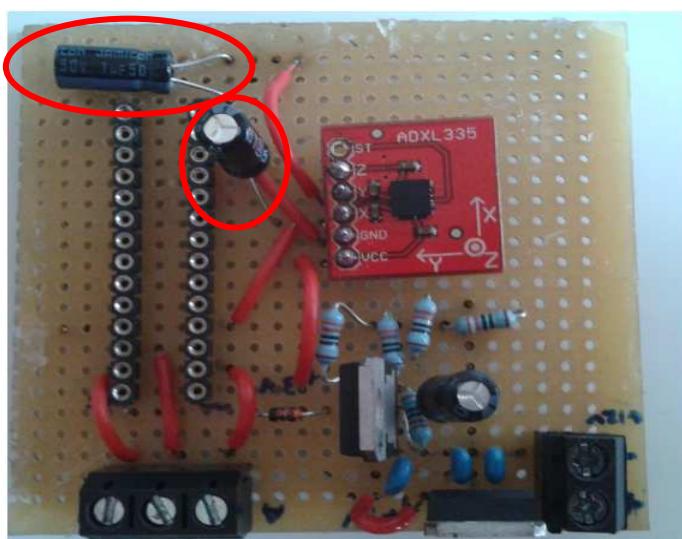

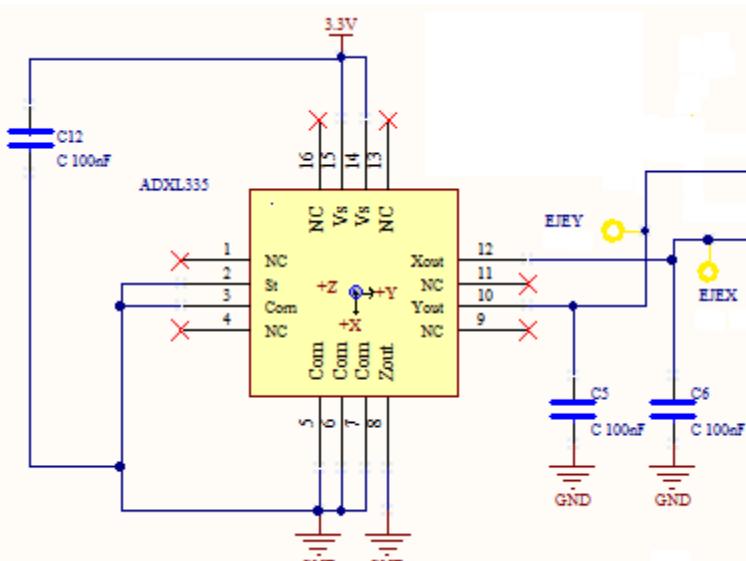

| 4.2.1 Variable/Sensor de inclinación (ADXL335).....          | 70 |

| A. Sensor de inclinación ADXL335.....                        | 71 |

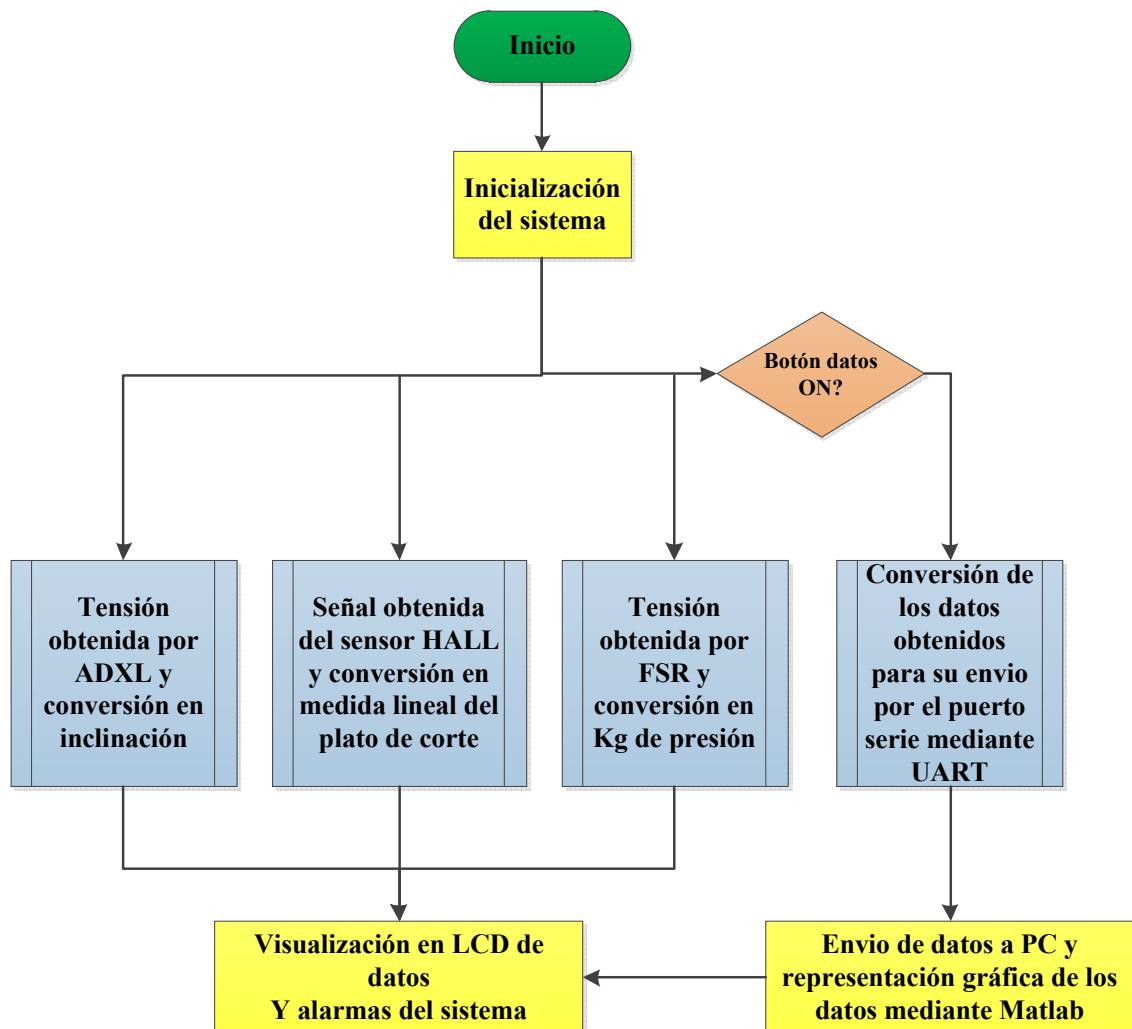

| B. Diagrama de bloques del sistema de control .....          | 73 |

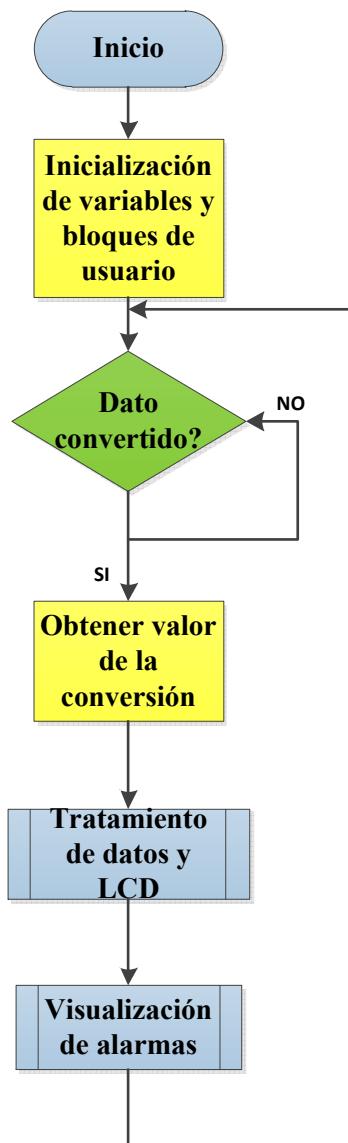

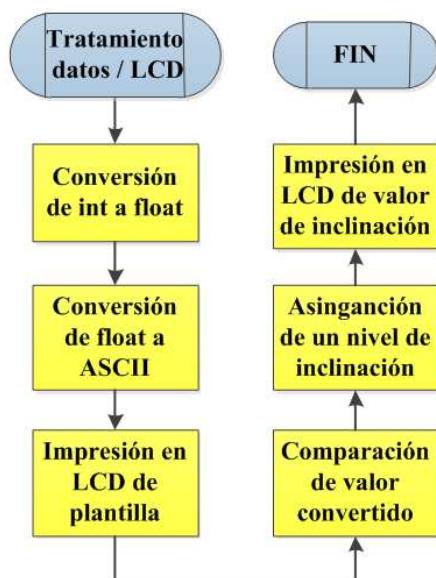

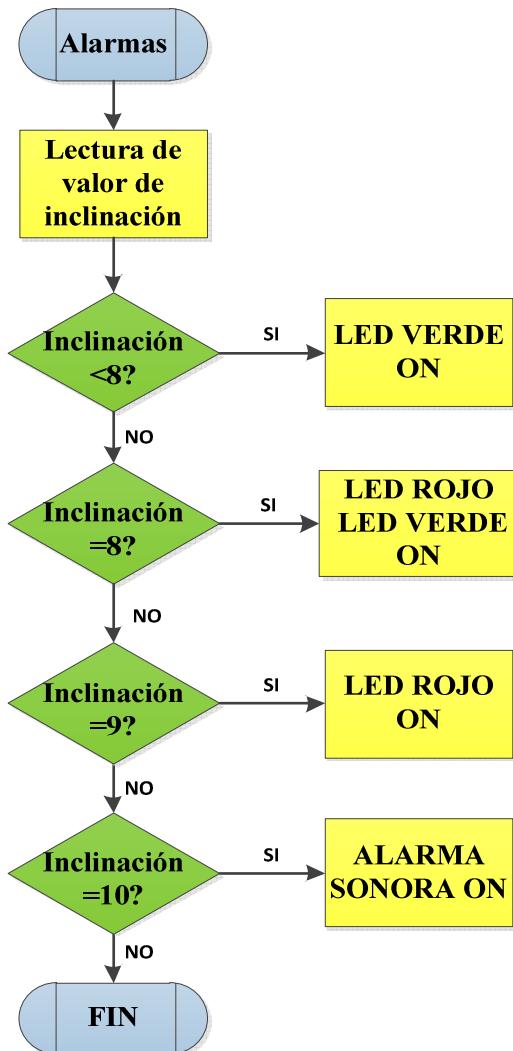

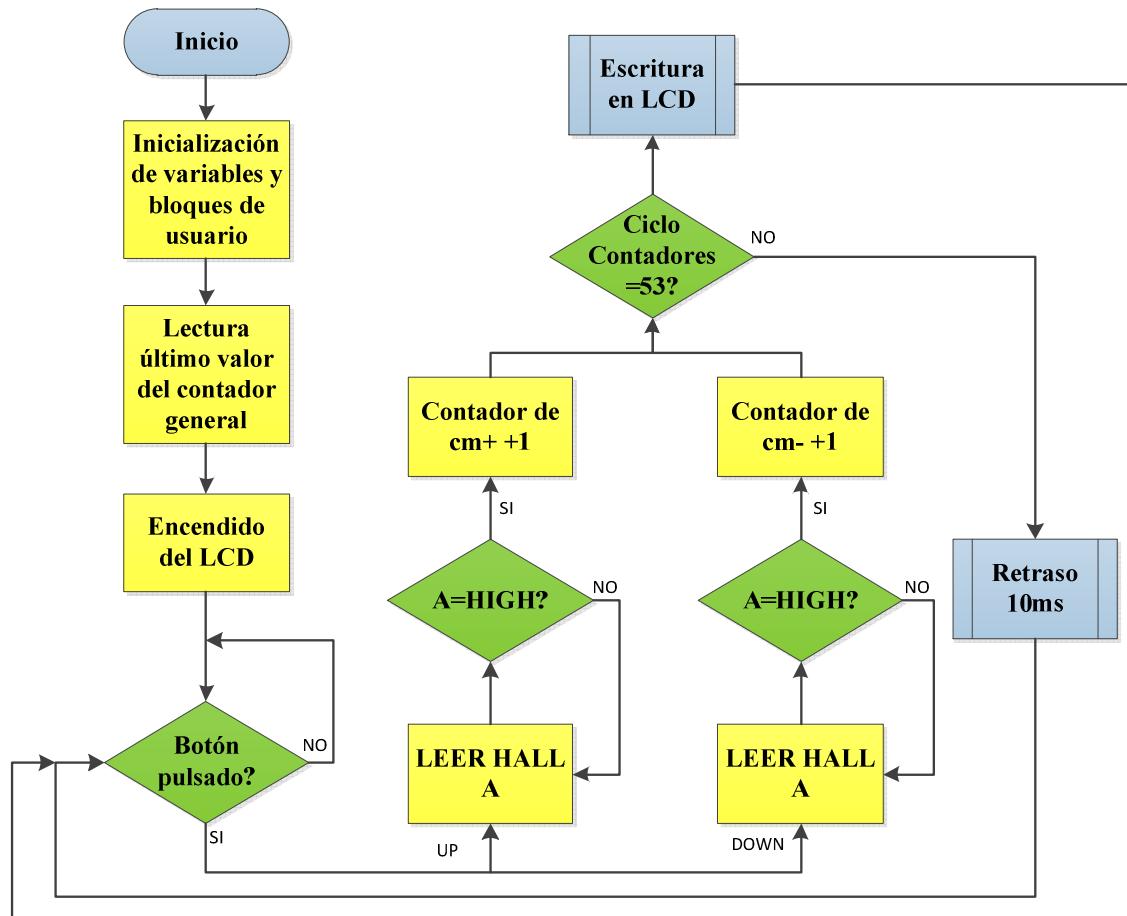

| C. Software del sistema .....                                | 74 |

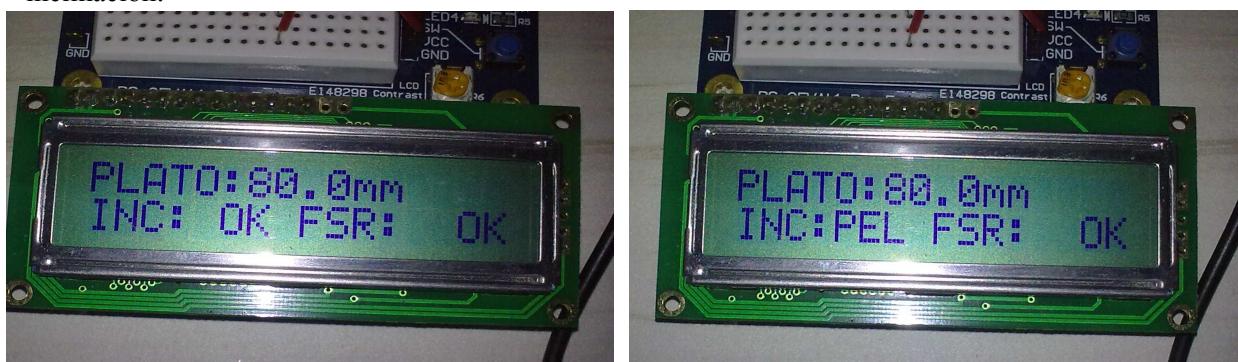

| D. Desarrollo en placa de puntos, pruebas y resultados ..... | 82 |

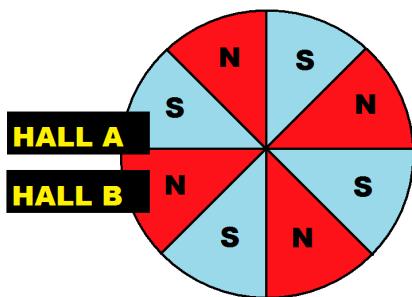

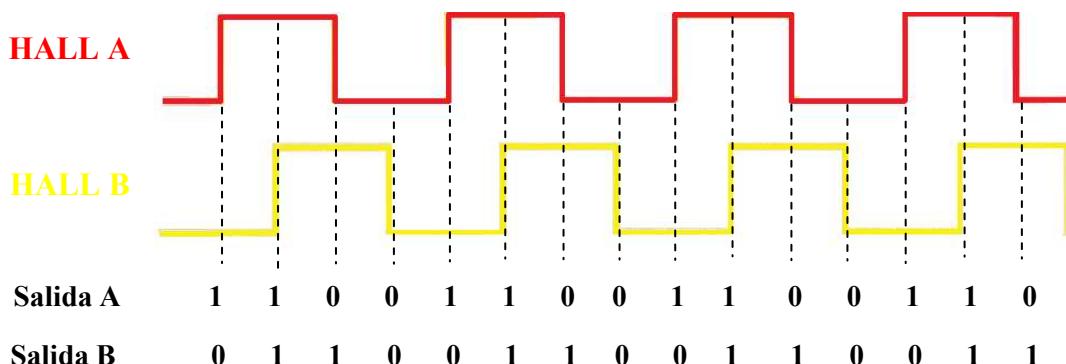

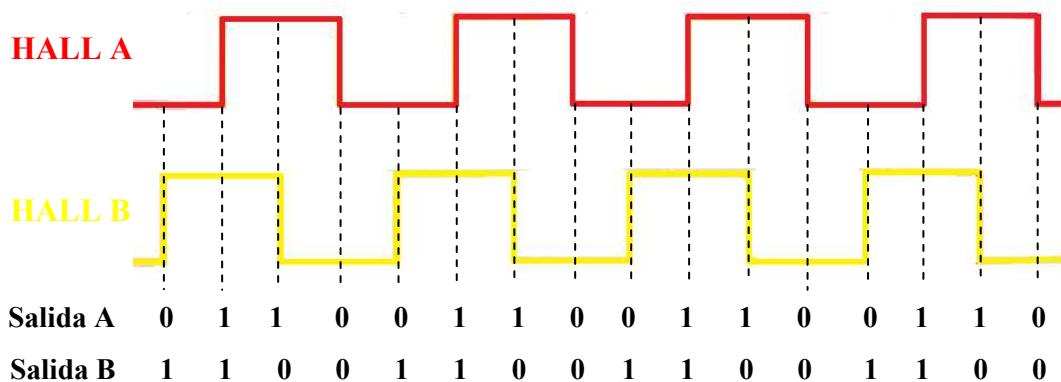

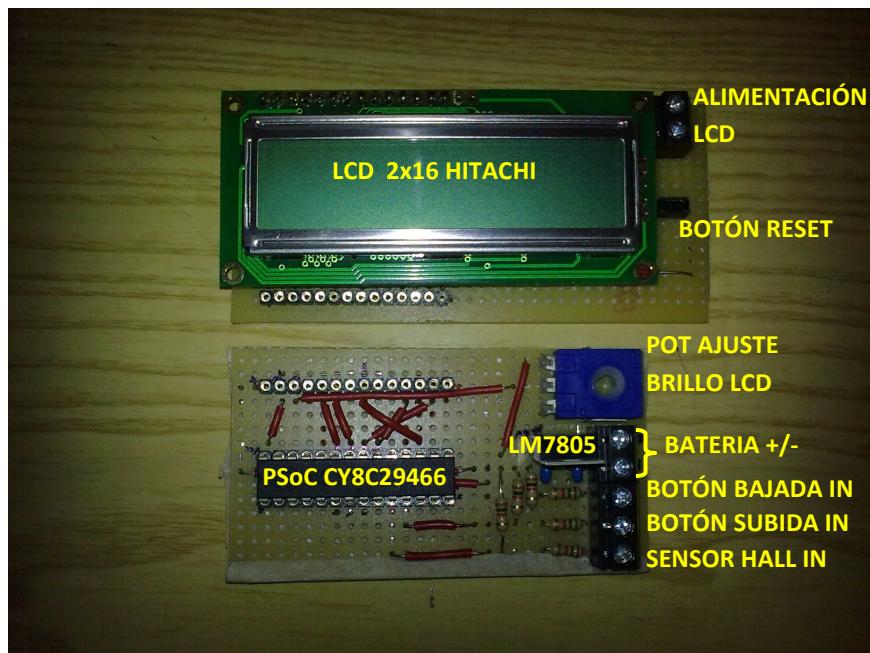

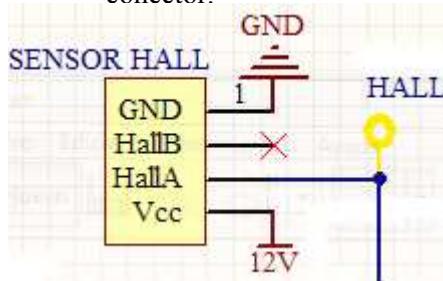

| 4.2.2 Altura del plato de corte mediante sensor Hall .....   | 85 |

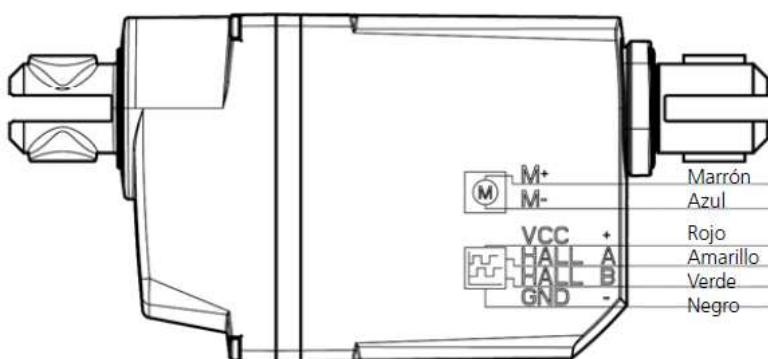

| A. Sensor Hall Linak LA23.....                               | 85 |

| B. Diagrama de bloques del sistema de control .....          | 88 |

| C. Software del sistema .....                                | 89 |

| D. Desarrollo en placa de puntos, pruebas y resultados ..... | 93 |

|                                                                         |            |

|-------------------------------------------------------------------------|------------|

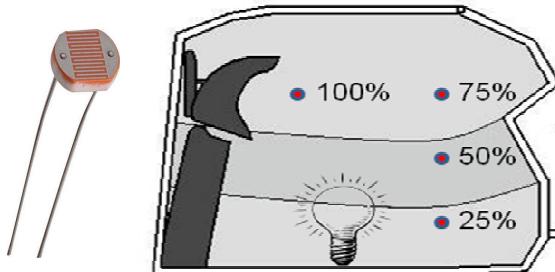

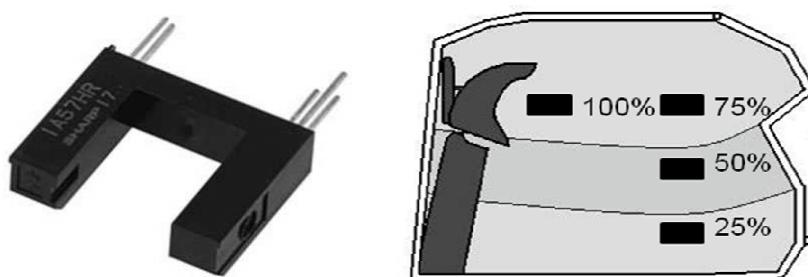

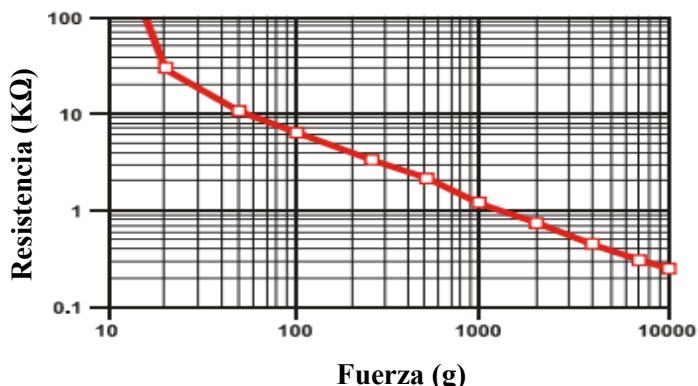

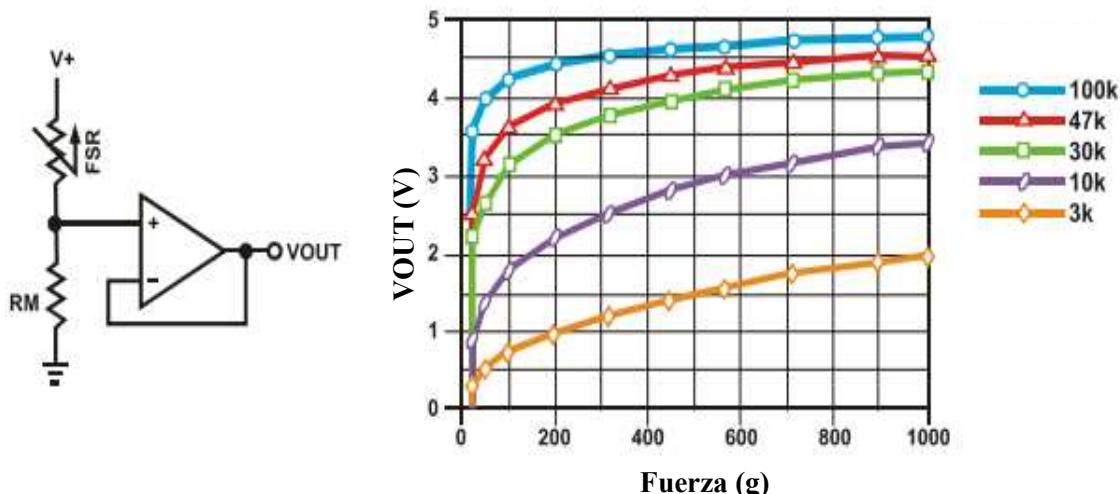

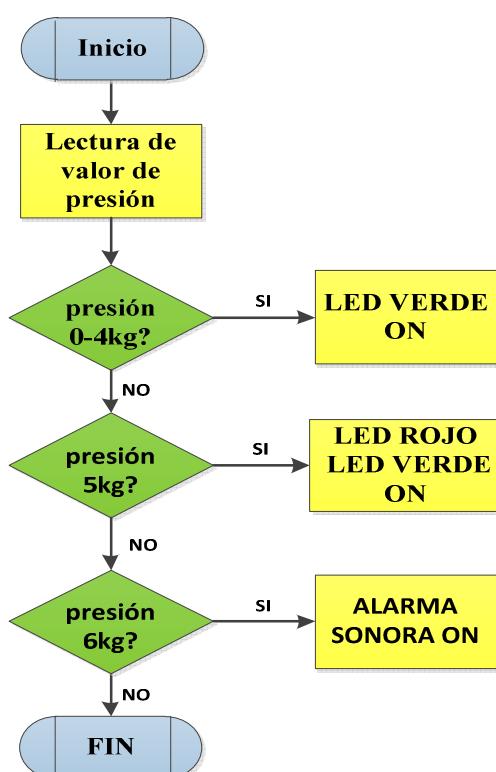

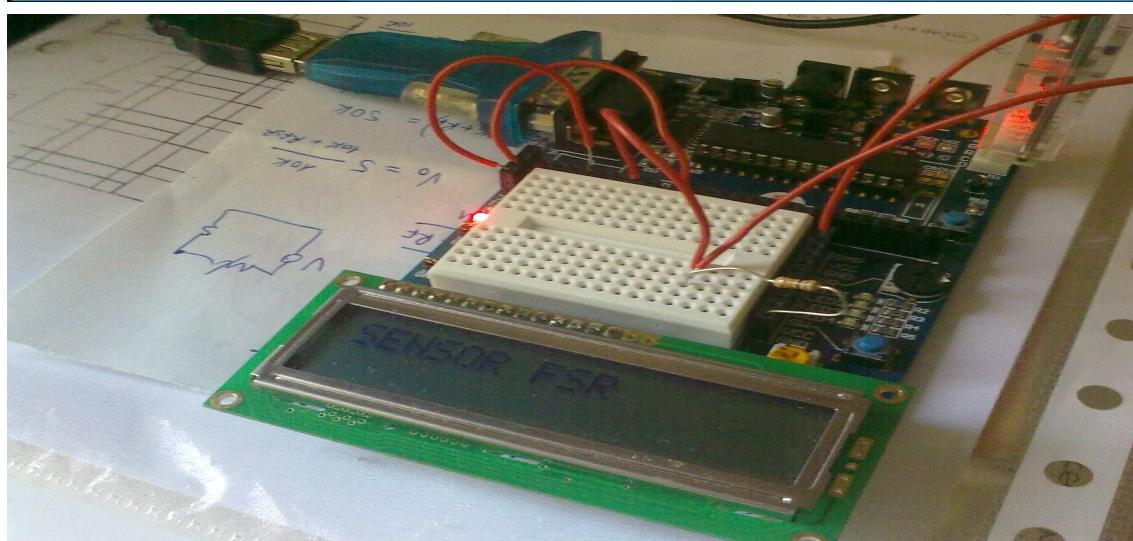

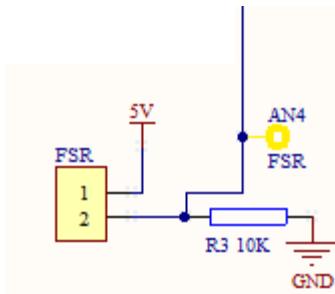

| 4.2.3 Sensor de llenado del cesto de recogida basado en sensor FSR..... | 95         |

| A. Sensores FSR.....                                                    | 97         |

| B. Diagrama de bloques del sistema de control .....                     | 99         |

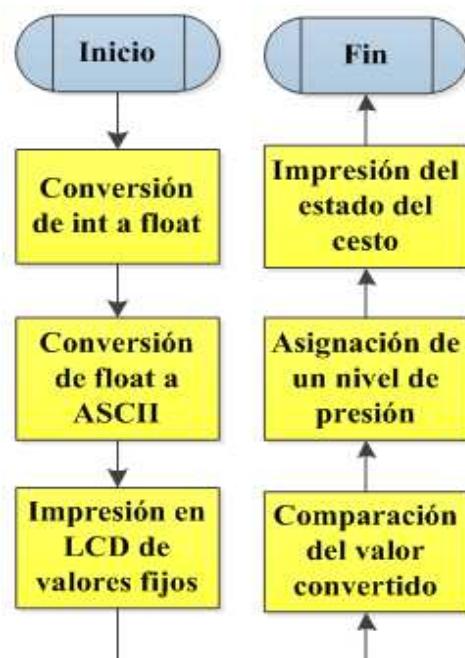

| C. Software del sistema .....                                           | 100        |

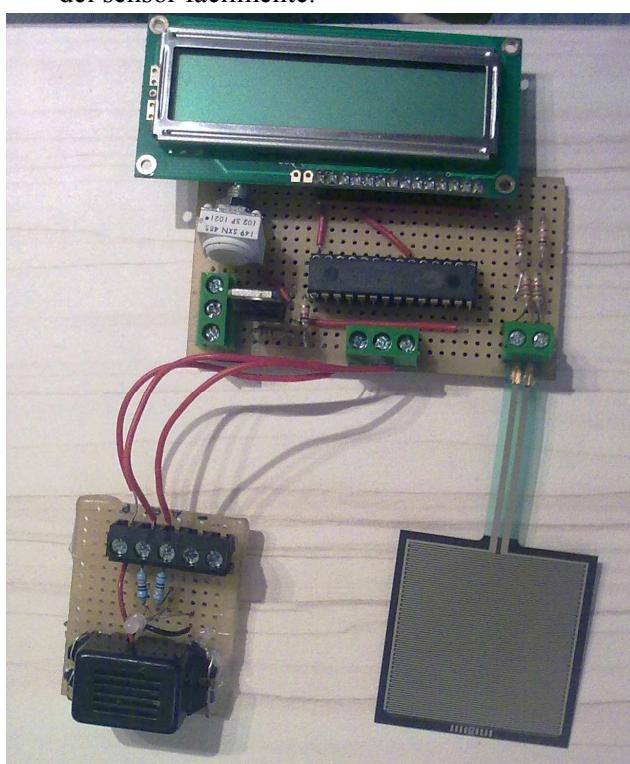

| D. Desarrollo en placa de puntos, pruebas y resultados .....            | 105        |

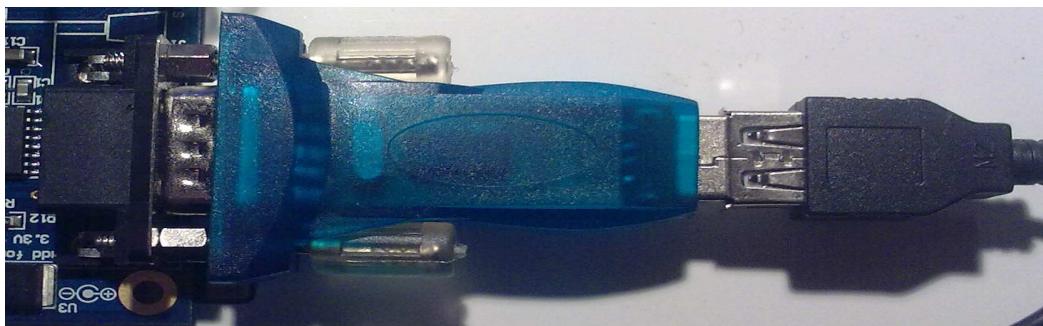

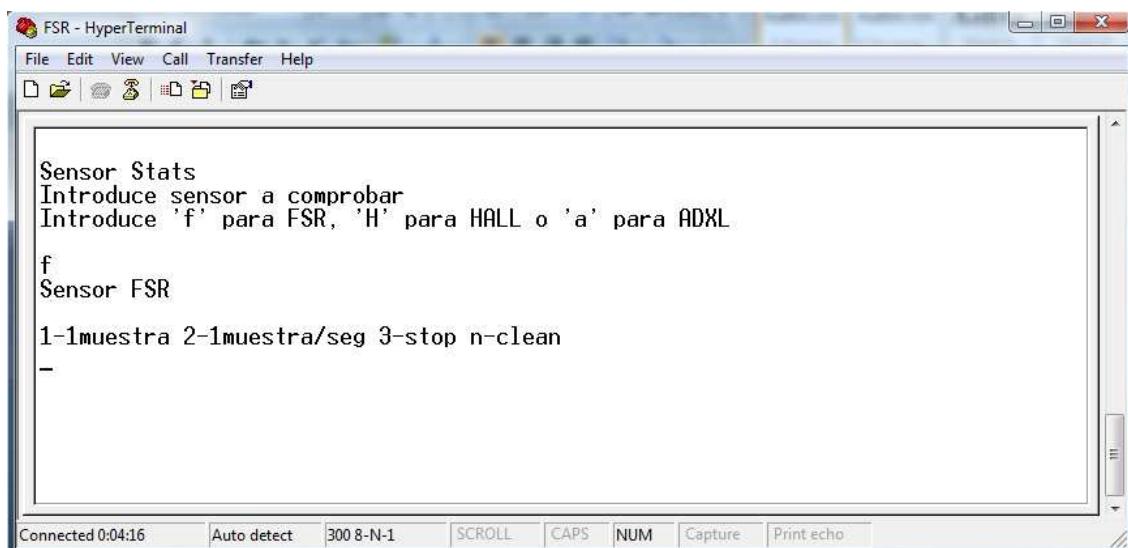

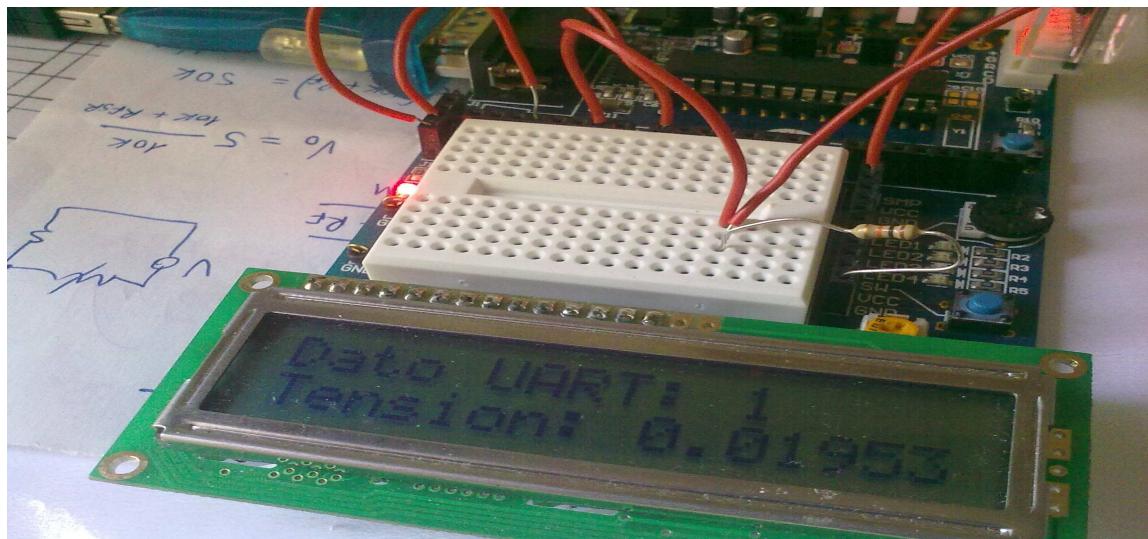

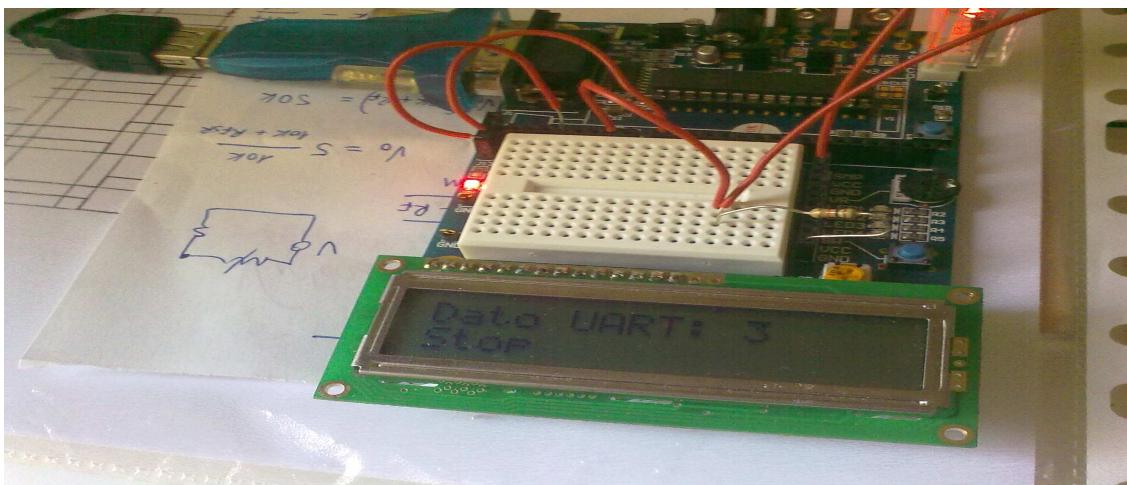

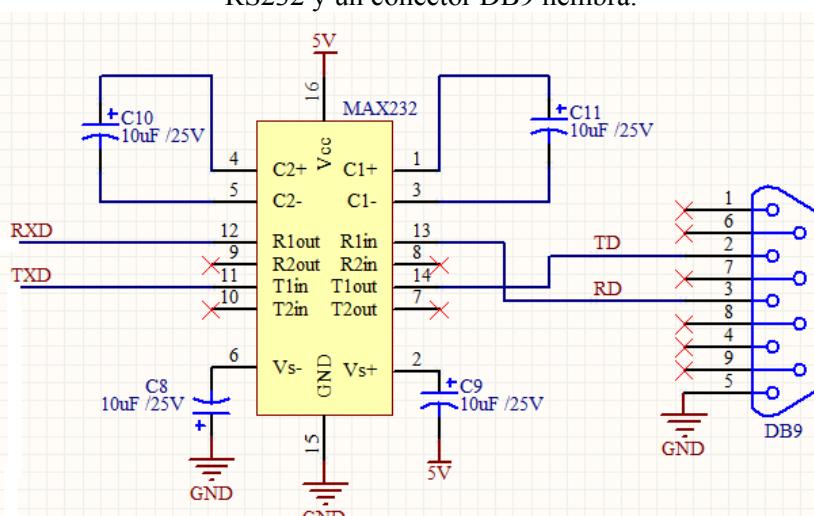

| 4.3 Comunicación de datos a PC por puerto serie (UART) .....            | 106        |

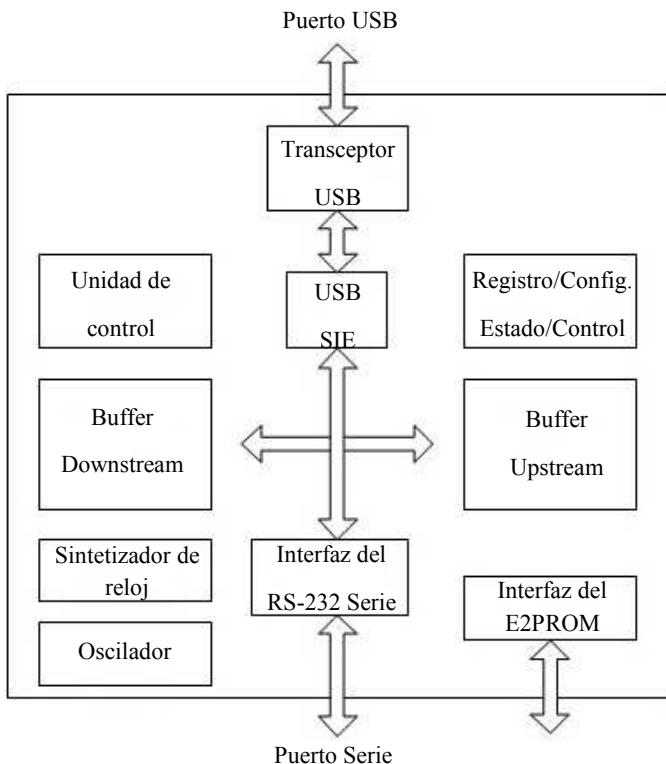

| A. Hardware USB a RS232.....                                            | 106        |

| B. Diagrama de bloques del sistema de control .....                     | 109        |

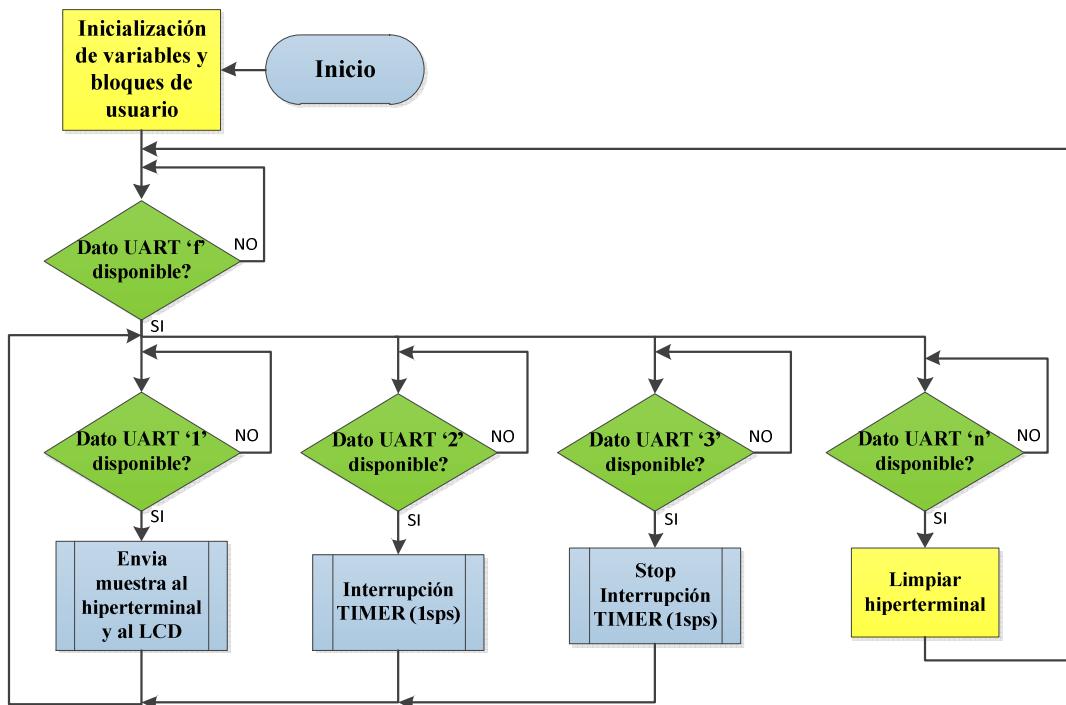

| C. Software del sistema.....                                            | 110        |

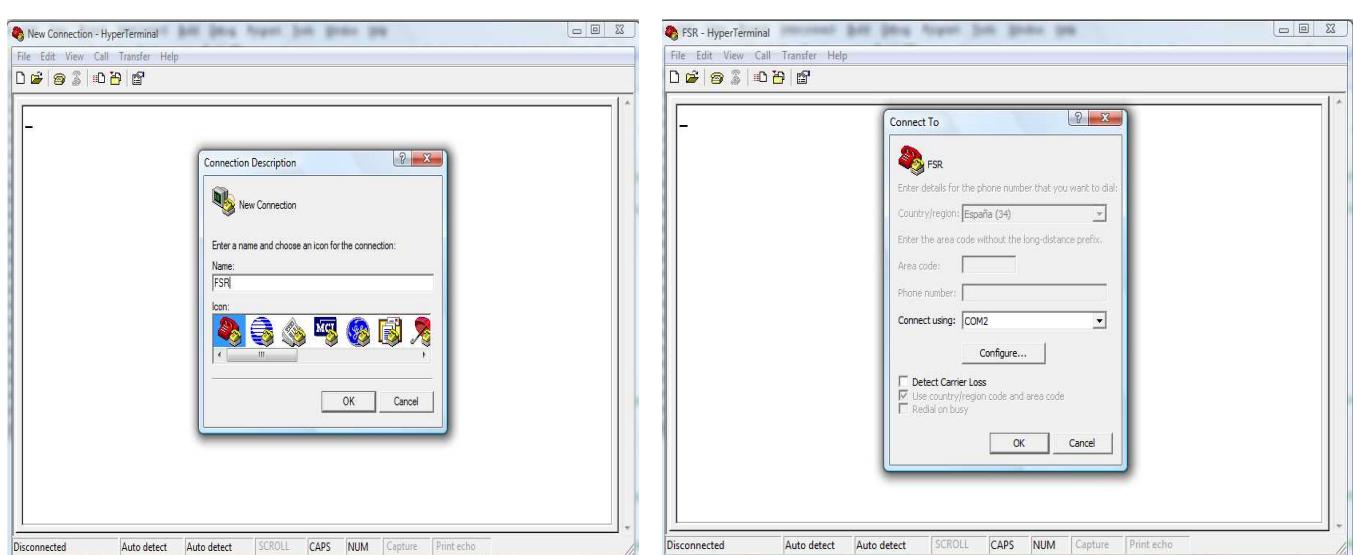

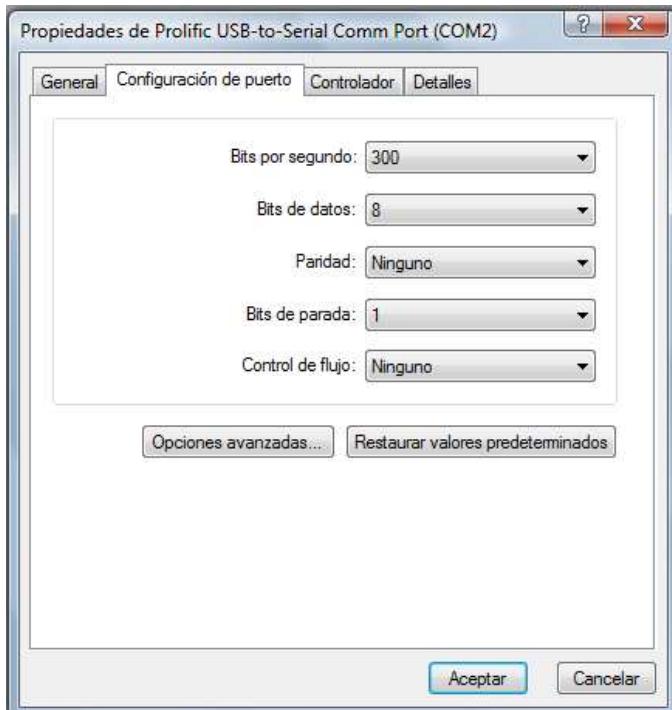

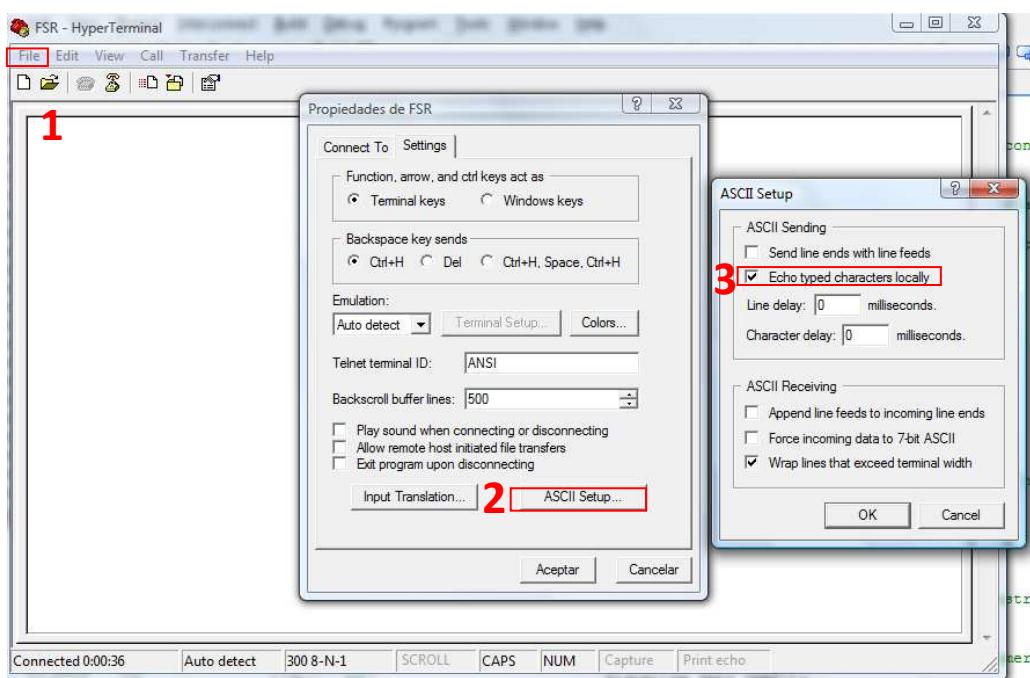

| D. Comprobación de funcionamiento, pruebas y resultados.....            | 116        |

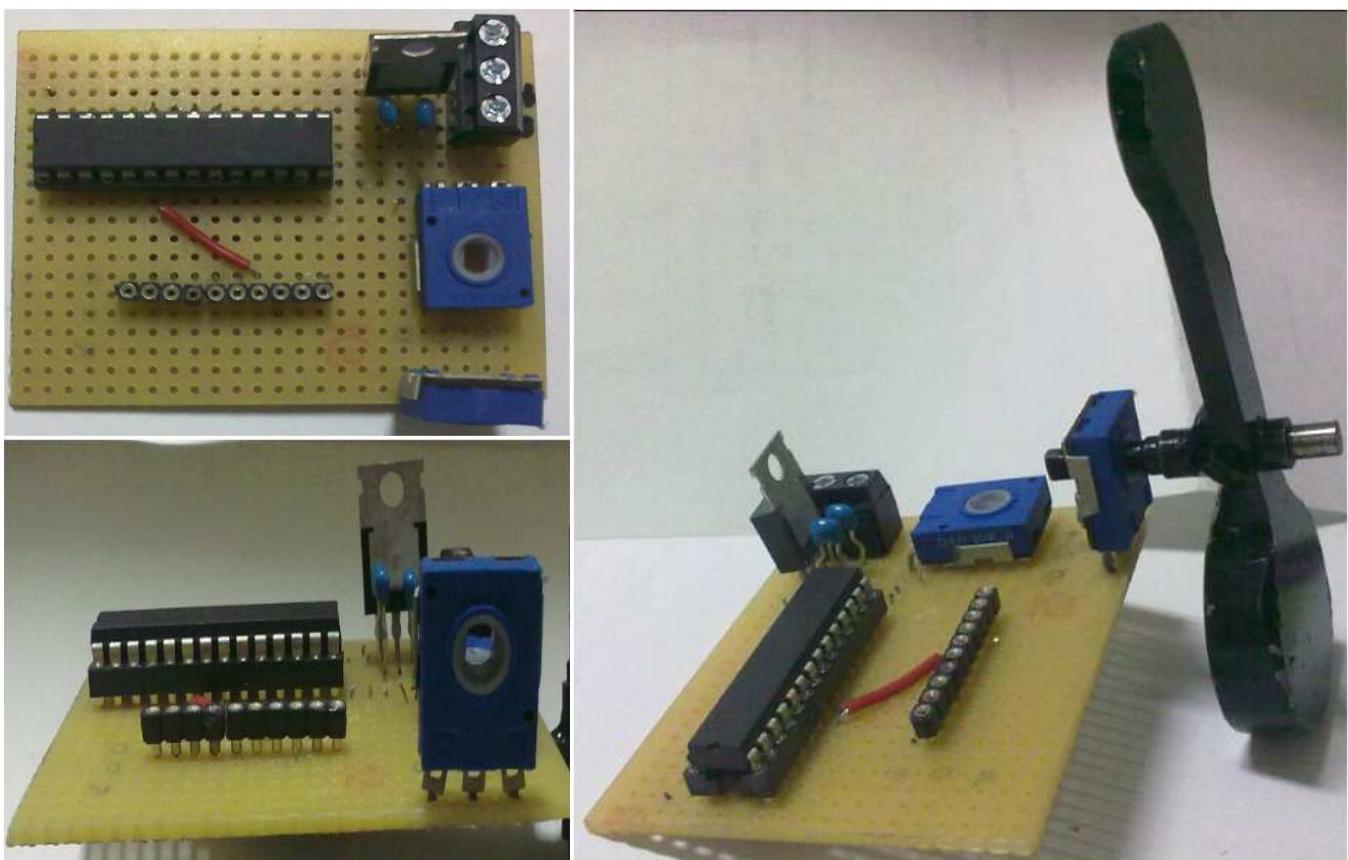

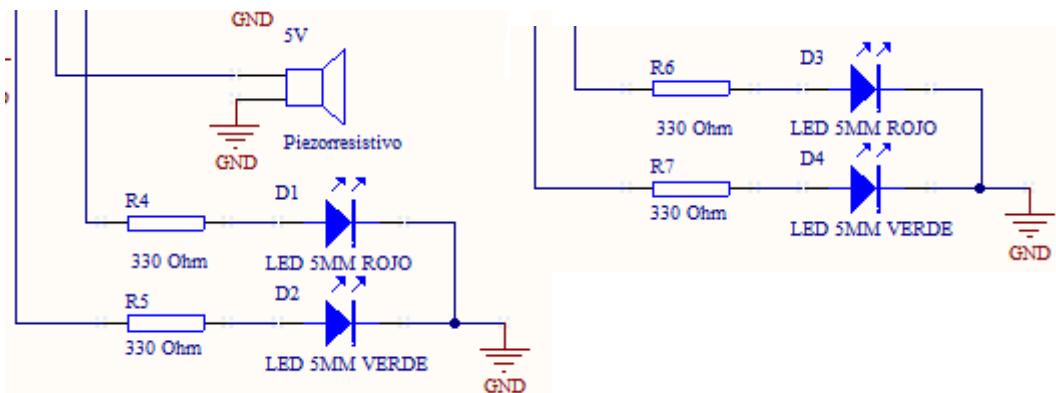

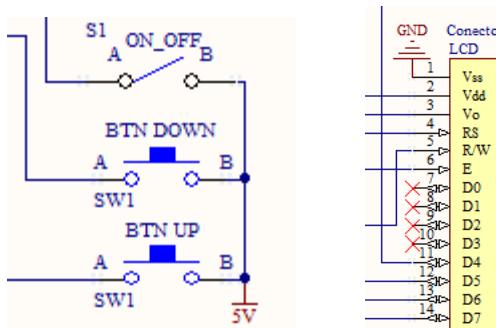

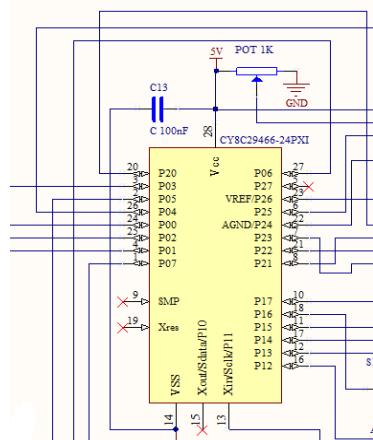

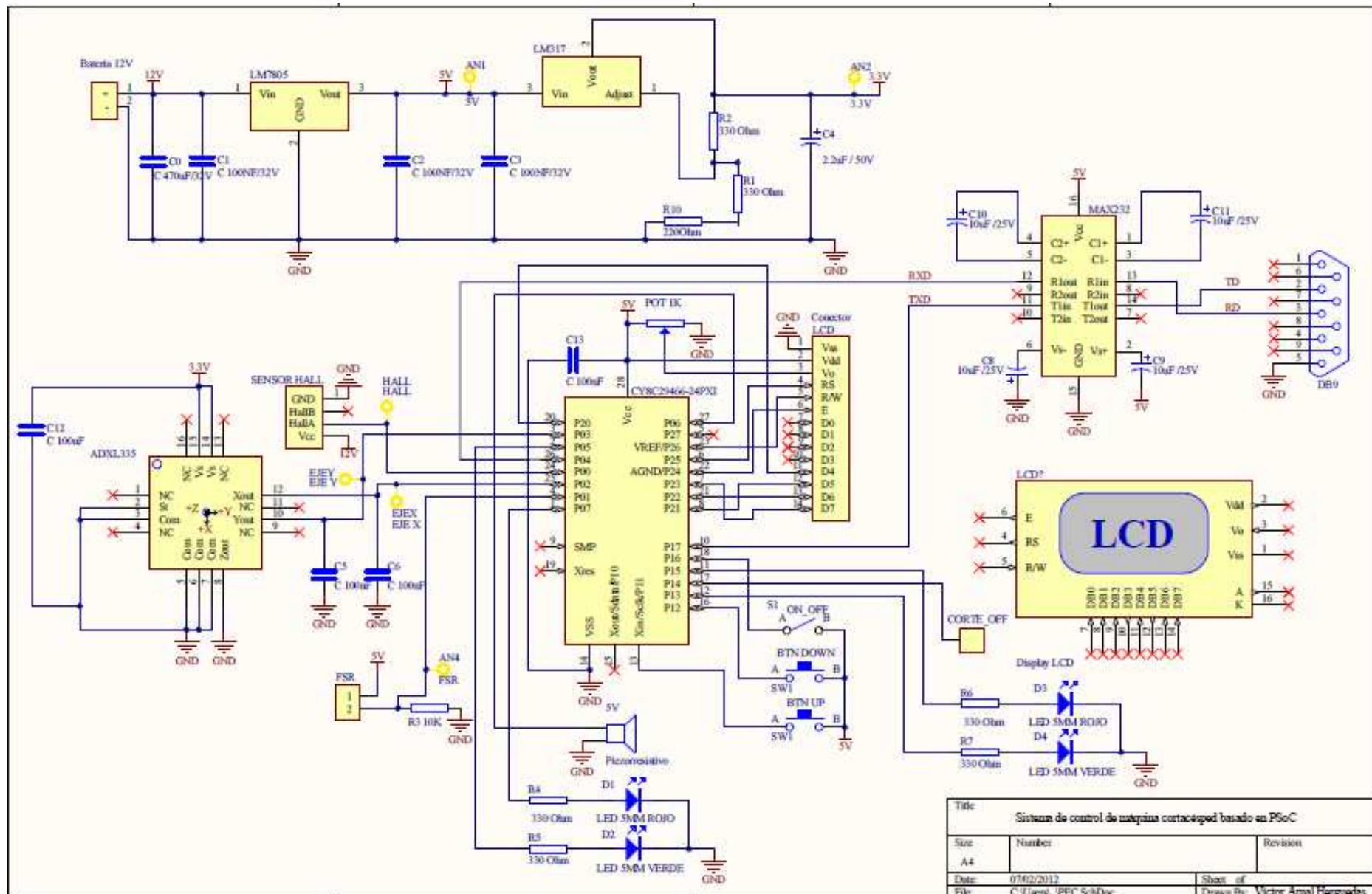

| 4.4 Prototipo de sistema conjunto .....                                 | 121        |

| A. Hardware del sistema .....                                           | 121        |

| B. Diagrama de bloques del sistema de control .....                     | 122        |

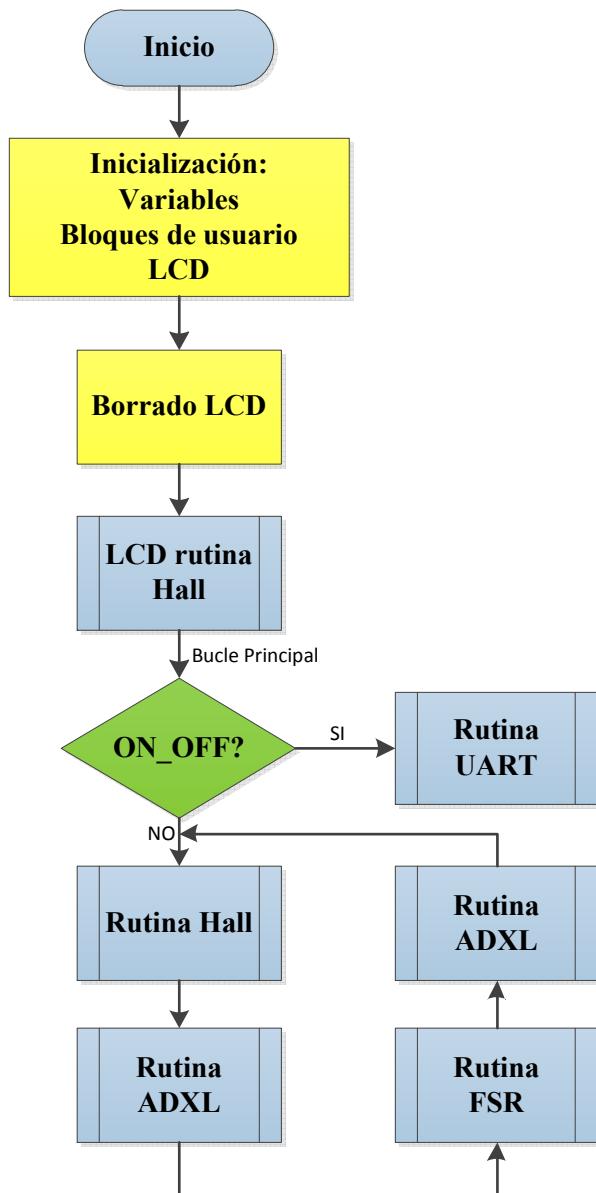

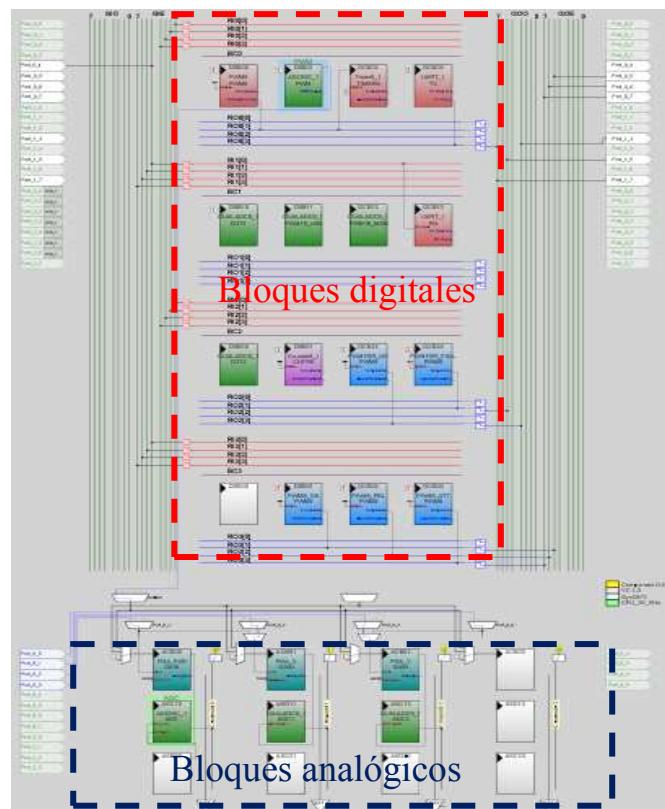

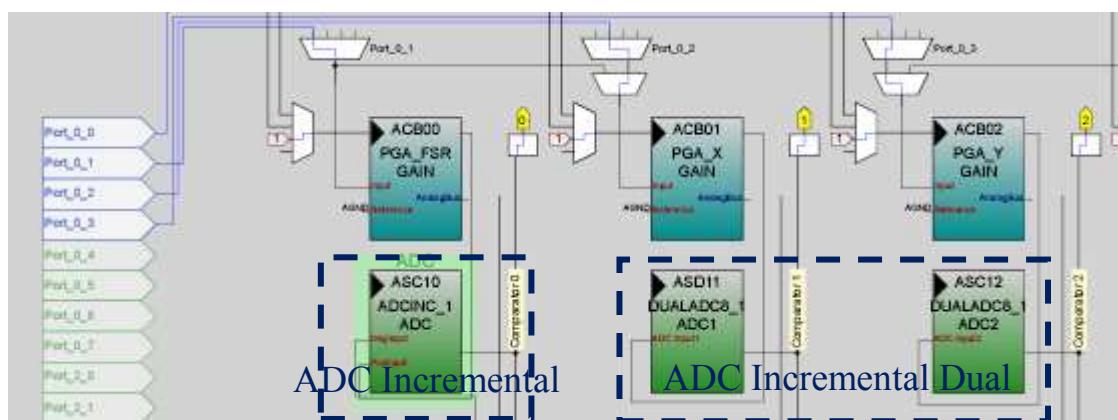

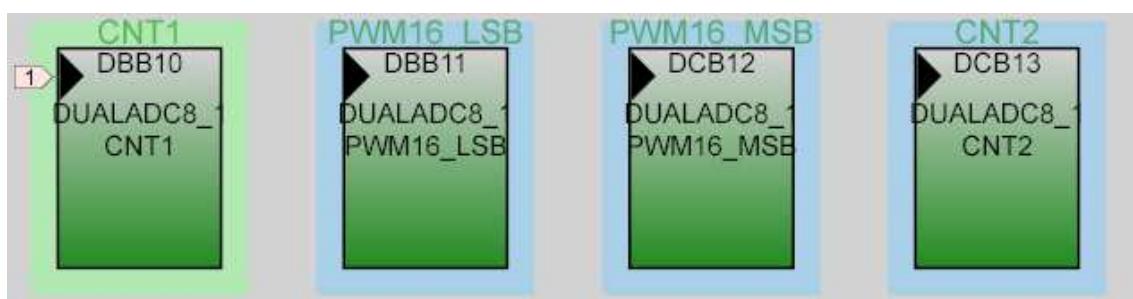

| C. Software del sistema.....                                            | 123        |

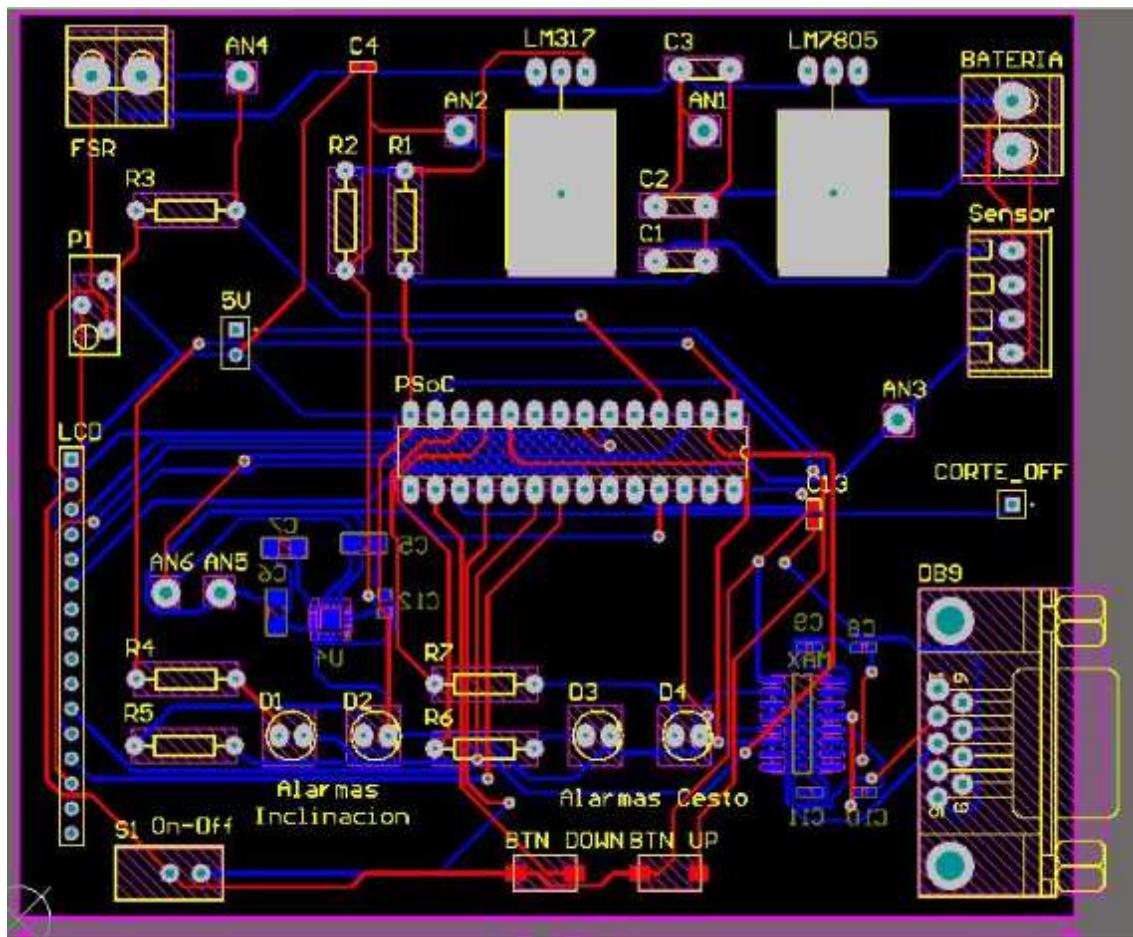

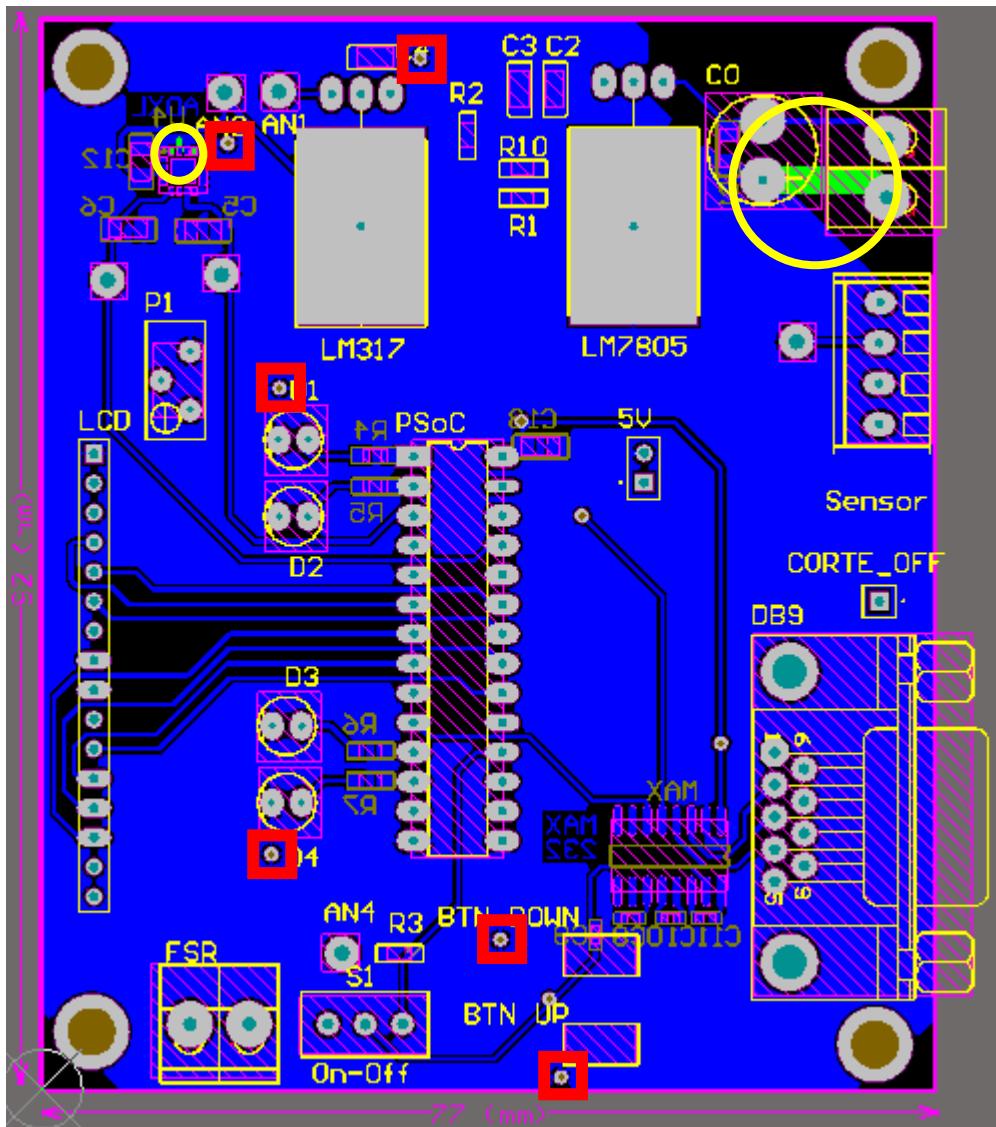

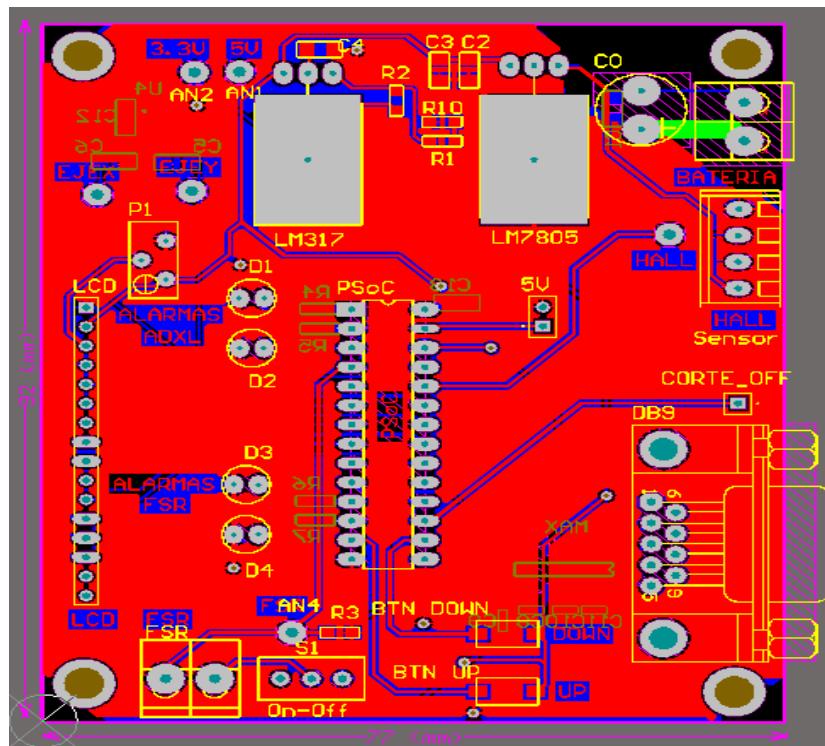

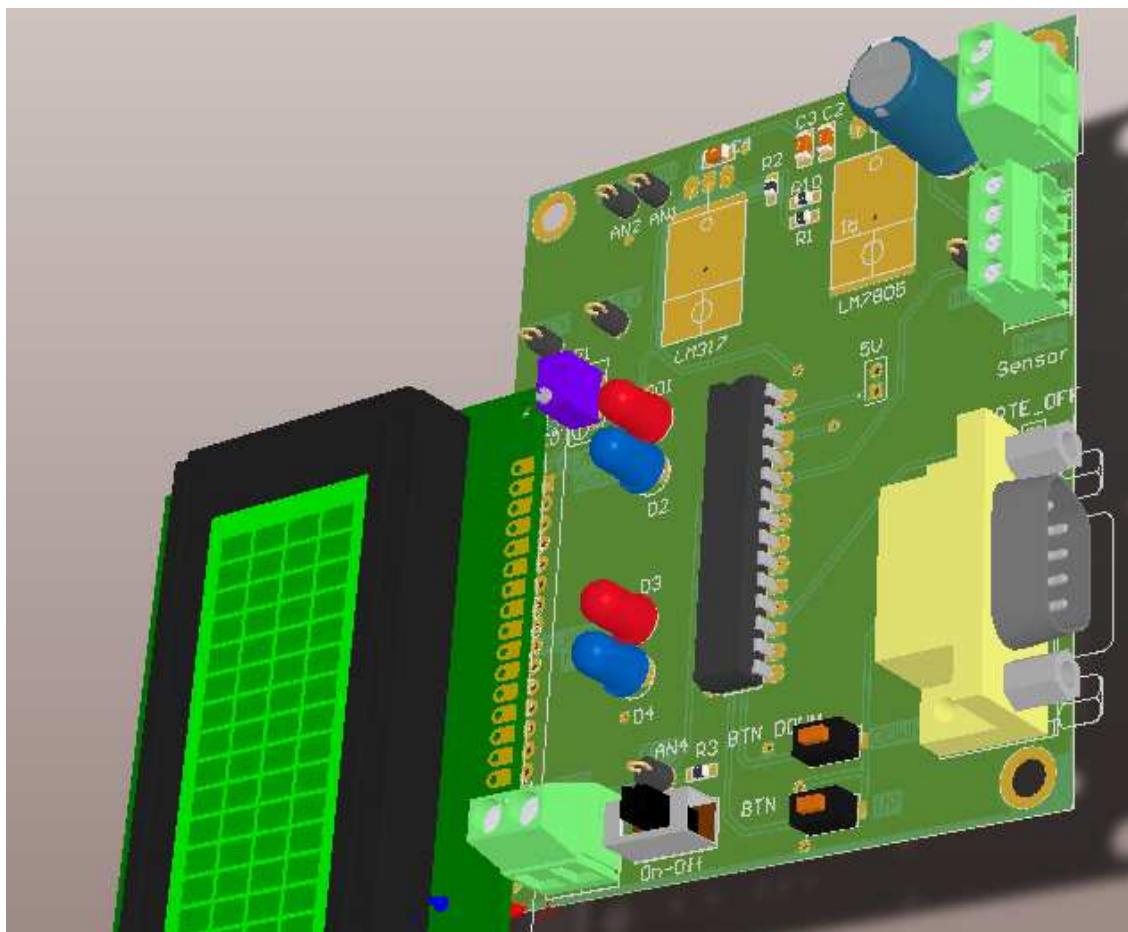

| 4.5 Diseño en Protel de prototipo final .....                           | 133        |

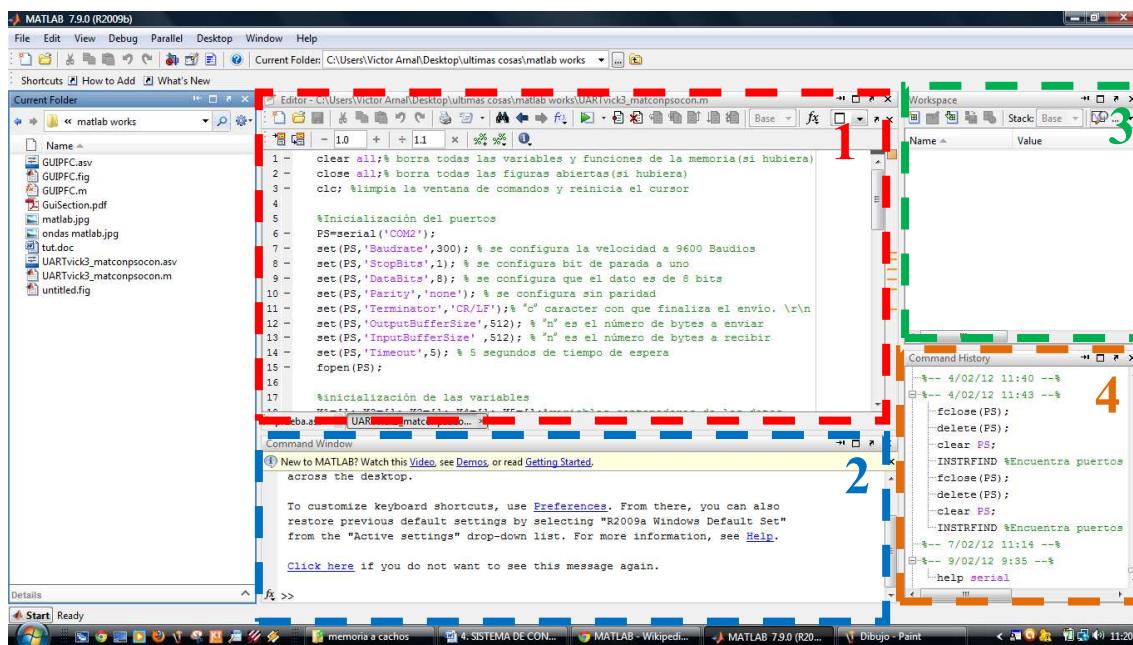

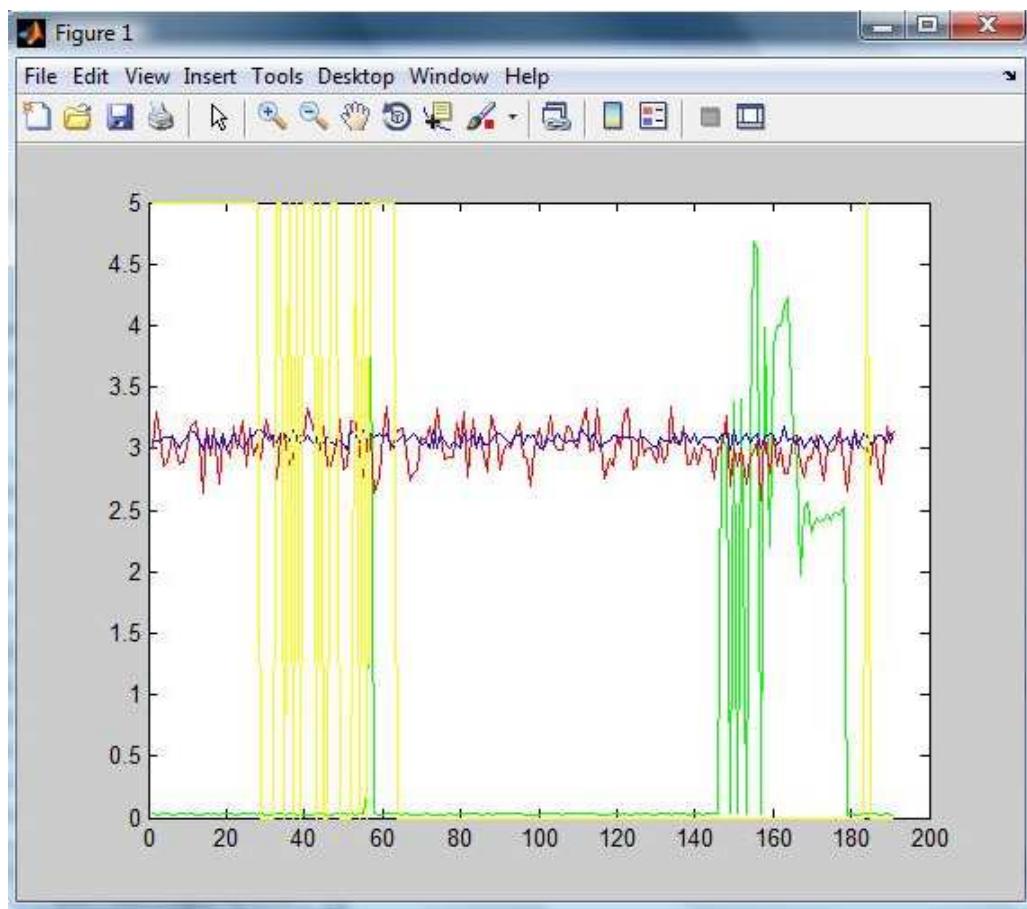

| 4.6 Aplicación software en Matlab .....                                 | 145        |

| <b>5. CONCLUSIONES.....</b>                                             | <b>150</b> |

| 5.1 Resultados obtenido .....                                           | 150        |

| 5.2 Mejoras y ampliaciones propuestas.....                              | 150        |

| 5.3 Cronograma.....                                                     | 151        |

| 5.4 Conclusiones personales .....                                       | 152        |

| <b>6. BIBLIOGRAFIA.....</b>                                             | <b>153</b> |

| 6.1 Bibliografía .....                                                  | 153        |

| 6.2 Páginas de internet consultadas.....                                | 153        |

| 6.3 Agradecimientos .....                                               | 153        |

## **1. INTRODUCCIÓN**

El proyecto fin de carrera “*Sistema de control de máquina cortacésped basado en PSoC*” tratará de mostrar al lector las características y posibilidades que ofrecen los “*embedded systems*” a través de una amplia explicación del PSoC CY8C29466-24PXi, tanto del software como del hardware, y mediante la creación de un sistema de control estándar para controlar ciertos aspectos de una máquina cortacésped. En este capítulo se va a contextualizar el proyecto, se explicarán los motivos del desarrollo del mismo y su alcance.

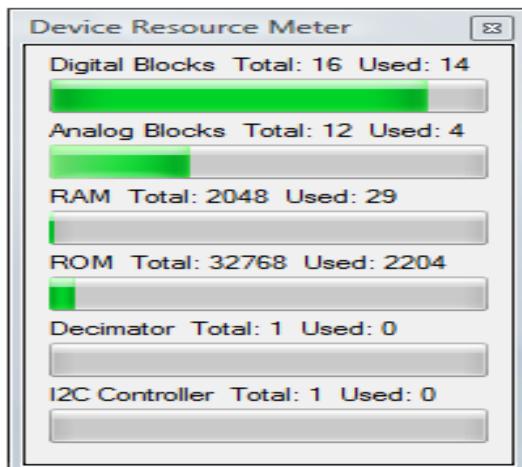

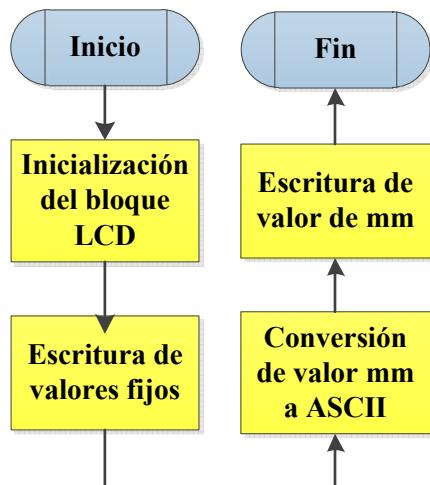

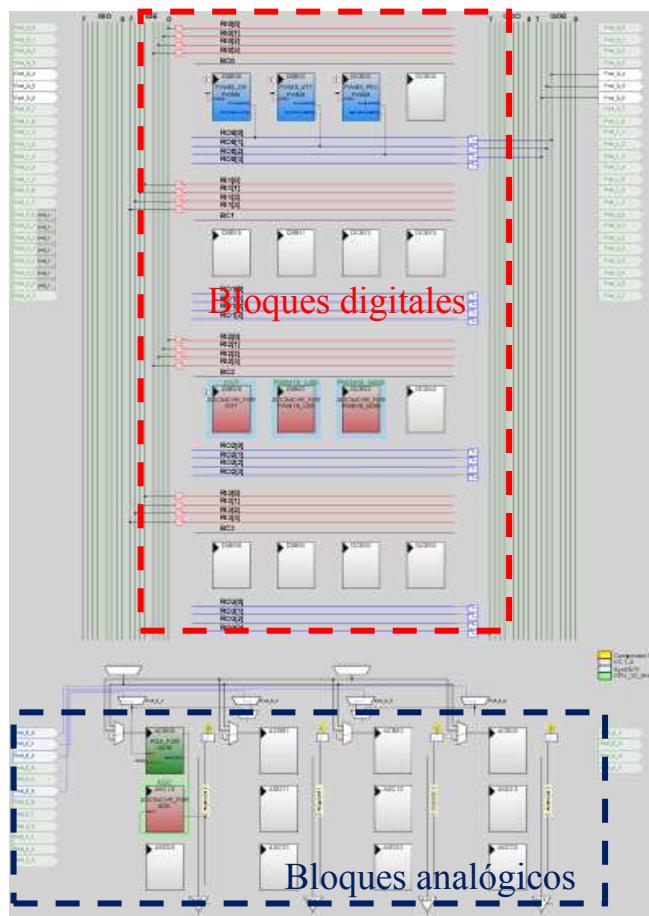

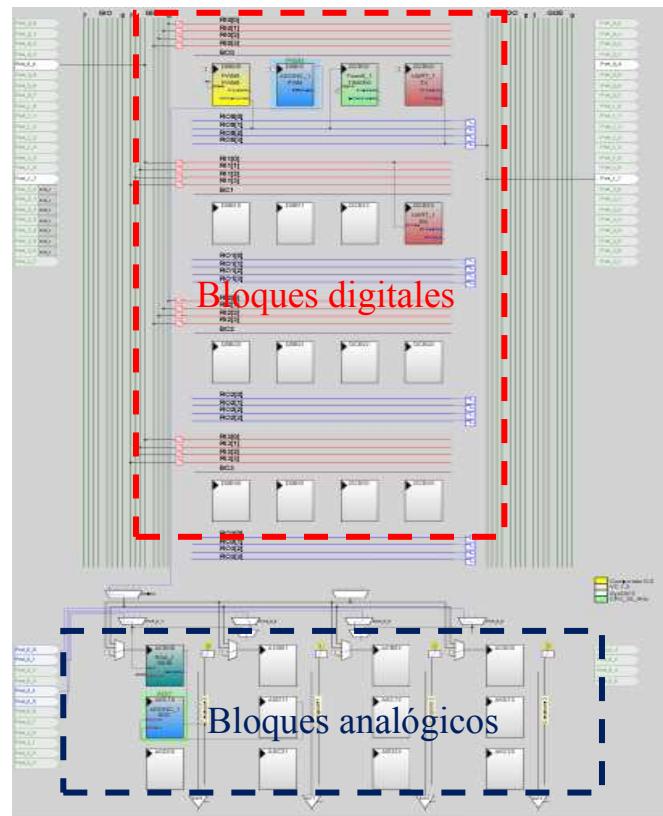

Los “*embedded systems*” o sistemas empotrados se basan en la tecnología de microcontroladores PSoC (Programmable System on Chip) de Cypress. El PSoC CY8C29466 de Cypress es un microcontrolador de 8 bits muy versátil ya que dispone de recursos analógicos (amplificadores operacionales, sensor de temperatura, conversor AD y DA, filtros,...) y digitales (temporizadores, contadores, moduladores de ancho de pulso (PWM), comunicación serie, generadores de números pseudo-aleatorios,...) completamente configurables en el mismo encapsulado. La arquitectura del microcontrolador, ofrece un máximo de 16 bloques digitales y un máximo de 12 bloques analógicos. Cada bloque tiene una serie de registros que determinan su funcionalidad y su conectividad con otros bloques, multiplexores, buses o puertos E/S.

El proyecto está confeccionado por 6 capítulos, que he intentado desarrollar de manera lineal para su fácil comprensión incluso para los lectores con bajos conocimientos en electrónica, que los cuales se indican a continuación:

- 1. Introducción:** En este bloque se introduce al lector en los contenidos del proyecto final de carrera y se muestra la declaración de los objetivos a alcanzar en el desarrollo del mismo.

- 2. Revisión histórica de las máquinas cortacésped y situación actual:** Se puede ver un pequeño seguimiento de la evolución de las máquinas cortacésped a lo largo de la historia, así como una reseña de la empresa en la que realice los estudios previos a la creación del sistema de control final.

- 3. PSoC: Programmable System on Chip:** En este capítulo se muestran todas las características tanto hardware como software del microcontrolador utilizado para la realización del proyecto, el PSoC de Cypress, perteneciente a la familia de los “*embedded systems*”.

- 4. Sistema de control estándar para máquinas cortacésped:** Una vez conocido el microcontrolador utilizado, descrito en el capítulo 3, se muestran por separado cada una de las aplicaciones del mismo en una máquina cortacésped y posteriormente el diseño conjunto del sistema final.

- 5. Conclusiones:** Como su nombre indica, en este capítulo se encuentan las conclusiones obtenidas a lo largo de la confección de esta proyecto final de carrera.

- 6. Bibliografía y agradecimientos:** En este último capítulo, el lector podrá observar la bibliografía consultada.

## **1.1 Motivación y objetivos**

La posibilidad de realizar unas prácticas en una empresa extranjera, para la que podía desarrollar un sistema de control que pudiera mejorar algunos aspectos de los productos que desarrollaban suponía un gran desafío. Tras hablar con los ingenieros de la empresa, llegamos a la conclusión que la creación de un sistema de control electrónico para suplir las carencias tanto de algunos actuadores existentes en las máquinas como la adquisición de nuevos datos de interés para el usuario final del producto, mejoraría enormemente la seguridad y la funcionalidad de sus máquinas cortacésped.

Por tanto, y debido a lo expuesto, los objetivos generales de este proyecto fin de carrera son:

- 1- Identificación del tipo de sensores y actuadores incorporados en las máquinas cortacésped y la posibilidad de mejorar los mismos mediante un sistema de control electrónico.

- 2- Conocimiento personal de una nueva herramienta de trabajo para el desarrollo de sistemas electrónicos, el microcontrolador PSoC, así como la mejora en el ámbito de la programación en lenguaje C.

- 3- Desarrollo de un sistema de control estándar basado en el microcontrolador de Cypress para máquinas cortacésped

- 4- En el ámbito personal, conocer el funcionamiento de trabajo de una empresa en lo relacionado con el diseño y el desarrollo de nuevos sistemas de control, así como el aprendizaje de una lengua extranjera nueva, el italiano.

## **1.2 Descripción y alcance del proyecto**

El objetivo principal de este proyecto final de carrera aquí expuesto ha sido el desarrollo de un sistema de control estándar para máquinas cortacésped que permita el control de una determinada serie de sensores y, consecuentemente, de variables de interés para el usuario final de la máquina. Se ha pretendido realizar un sistema de control lo suficientemente versátil que pueda ser incorporado a cualquiera de los modelos producidos por la empresa.

Previo comienzo del diseño del dicho sistema, debía introducirme en el manejo del microcontrolador que iba a utilizar, el PSoC CY8C29466-24PXI, ya que no lo había utilizado previamente y requería de una preparación previa. A partir de un kit de evaluación que adquirí (sus contenidos y utilidades serán desarrollados en el punto 3.2 de esta memoria) los conocimientos necesarios para utilizar cada uno de los bloques tanto digitales como analógicos de este microcontrolador, así como la inicialización de los mismos y las instrucciones en código C para su correcto funcionamiento. Una vez conocido el manejo del microcontrolador y desarrollado un sistema de control basado en el mismo, tuve que aprender a manejar las siguientes aplicaciones: Matlab para el desarrollo de una aplicación que representara gráficamente las señales obtenidas por el sistema creado con el PSoC y posteriormente, Altium Designer 2009 para la realización de un prototipo en una placa de circuito impreso.

Como ya he comentado, el objetivo final conseguido permitirá controlar, en tiempo real, una serie de variables de utilidad para el usuario de una máquina cortacésped y además, contar con la posibilidad de utilizar el sistema en cualquier máquina cortacésped.

## 2. REVISIÓN HISTÓRICA DE MÁQUINAS CORTACÉSPED Y SITUACIÓN ACTUAL

### *2.1 Introducción*

Como su nombre indica, un cortacésped o cortadora de césped es una máquina, manual o motorizada, usada para cortar el césped de forma que se obtenga una alfombra de hierba de altura uniforme. Estas máquinas evolucionaron de forma paralela a los motores de gasolina, ya que cuando estos últimos fueron los suficientemente pequeños y potentes supuso una revolución para ellas. En los siguientes apartados realizaré una pequeña revisión de la evolución en la historia de estas máquinas.

### *2.2 Historia de las máquinas cortacésped*

La primera cortadora de césped fue inventada por Edwin Budding, en el año 1827, en Inglaterra, siendo patentada en 1830. Esta segadora o cortacésped fue diseñada principalmente para cortar el césped en campos deportivos y grandes jardines, se inventó como una alternativa mejor a la guadaña. Aún así le costó diez años innovarla y conseguir que la segadora pudiera utilizarse mediante el uso de animales.

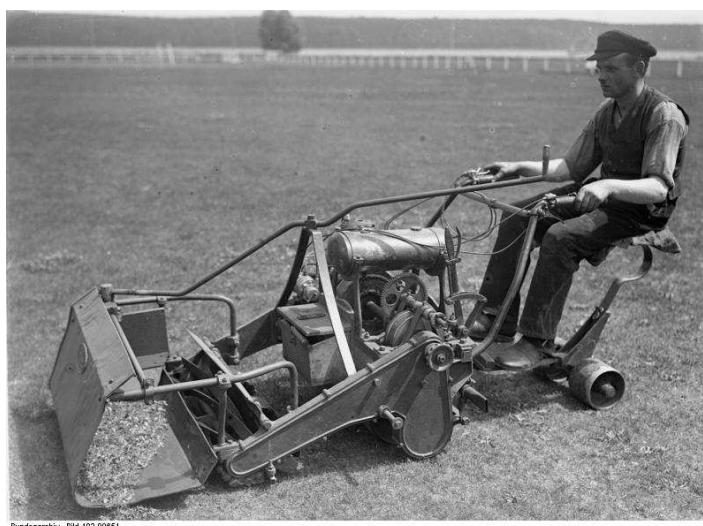

Fig. 2.1. Primera máquina cortacésped empujada por animales

En un acuerdo entre John Edwin Ferrabee y Edwin Budding el 18 de mayo de 1830, Ferrabee pagó los costes del desarrollo y obtuvo las cartas de las patentes y adquirió los derechos para fabricar, vender y conceder licencias a otros fabricantes en la producción de las cortadoras de césped. Thomas Green produjo la primera cortadora de césped en el año 1859, y en la década de 1860 comenzó la fabricación de las cortadoras de césped.

En 1862, la compañía de Farrabee fabricaba ocho modelos diferentes, cuya diferencia entre ellas era el tamaño de los rodillos que usaban. En 1870, Elwood McGuire de EE.UU., diseño una cortadora de césped que funcionaba empujada por ser humano, muy ligera lo que conllevo a un éxito comercial. Más tarde, en 1899, John Burr patentó una segadora con mejoras en el rotor y las paletas, con la colocación de un cambio en la rueda, para mejorar su rendimiento.

Fig. 2.2. Primera máquina cortacésped empujada por el hombre

JP Ingeniería de Leicester, se fundó después de la Primera Guerra Mundial, produjo una serie de cortacéspedes muy populares. En este tiempo, el operador se montaba detrás de los animales que tiraban de las máquinas de gran tamaño, estas fueron las primeras segadoras de este estilo. El aumento de la popularidad de los deportes que se practicaban sobre césped ayudó a que la propagación de máquina corta césped.

Las cortadoras de césped se convirtieron en una alternativa más eficiente a la guadaña y al pastoreo de animales. En 1893, James Sumner, de Lancashire patentó la primera cortadora de césped a vapor, utilizaba como combustible gasolina o queroseno. Despues de numerosos avances, las máquinas fueron vendidas por Stott Fertilizer e Insecticide Company de Manchester.

Los cortacéspedes rotativos no se desarrollaron hasta que los motores fueron lo suficientemente pequeños y sobre todo potentes como para ejecutar las hojas a una alta velocidad, muchas personas experimentaron con las cuchillas rotativas a finales de 1920 y principios de 1930, y Power Specialties Ltd. presentó un cortacésped de gasolina.

Fig. 2.3. Primera máquina cortacésped propulsada por un motor de gasolina

A partir de entonces, las máquinas cortacésped fueron mejorando a la vez que lo hacían los motores de gasolina. Igualmente, la evolución en otros campos como en la automovilística, siderurgia, electrónica, etc. hizo que la máquina evolucionara hasta las máquinas cortacésped que existen en la actualidad.

Fig. 2.4. Máquina cortacésped actual

### 2.3 *Grillo S.p.A.*

Fig. 2.5. Logo de la empresa Grillo SpA

Grillo SpA es una empresa italiana nacida en 1953 dedicada a la producción y venta de máquinas agrícolas y de jardín. Está situada en la ciudad de Cesena, en la región de Forlì-Cesena (FC). Una pequeña reseña histórica de la empresa es la siguiente:

En 1953 nació el primer auténtico motocultor "GRILLO": era una máquina que podía hacer óptimamente muchos trabajos. La idea ganadora fue de separar el vehículo autopropulsado del accesorio. Con las azadas montadas se cavaba, con el arado se araba, con el remolque se transportaba, con la bomba se rociaba etc. En 1955 se inició la primera producción de serie: 15 máquinas en un año.

Hoy en día se venden decenas de miles de máquinas con estas características alrededor del mundo. Estos inicios, en los años siguientes, permitieron la creación de otros interesantes modelos como desbrozadoras, motoazadas y carretillas motorizadas.

GRILLO proyecta y fabrica máquinas para la agricultura profesional y el mantenimiento de grandes áreas verdes, así como de los jardines y huertos domésticos. Sus máquinas nacen de estudios de ingeniería aplicados a la utilización diaria, con el objetivo de crear nuevas soluciones técnicas capaces de facilitar el trabajo del hombre.

Para proyectar y producir, disponen de un eficiente equipo de técnicos y diseñadores. La producción industrial se realiza mediante la utilización de herramientas de alto nivel tecnológico tales como corte con láser, robots, línea de montaje parcialmente automatizada, etc. GRILLO produce 20.000 máquinas al año y en una gama de más de 50 modelos diferentes, con sus 200 empleados.

Fig. 2.6. Sede central de Grillo SpA en Cesena

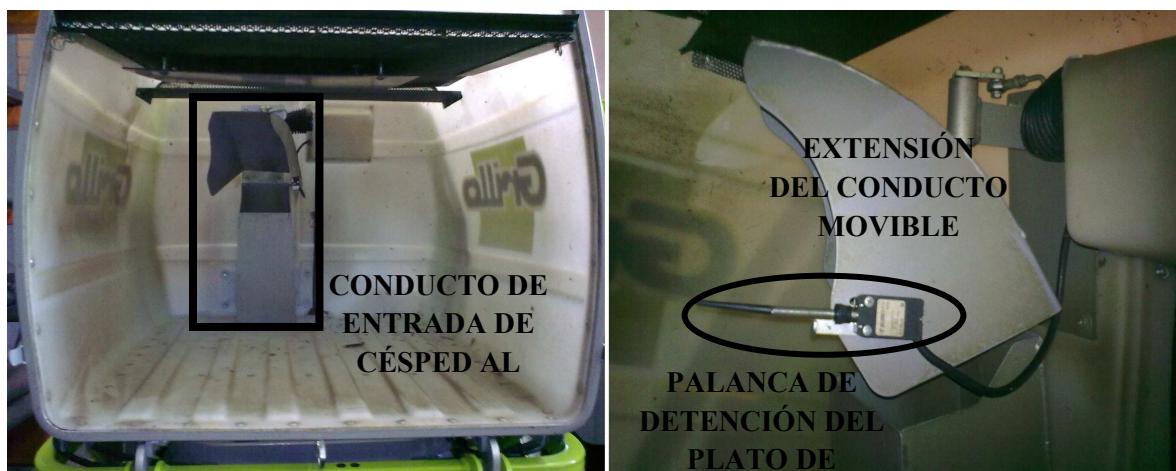

Fue en esta empresa donde realice un stage entre noviembre de 2010 y agosto de 2011, donde diseñé los primeros prototipos sobre los que después basaría este proyecto final de carrera. Cuando llegué allí, pregunté a los ingenieros que tipo de sensores podían ser incorporados a las máquinas o que variables era interesante capturar y procesar para mejorar la seguridad o el uso de la máquina para el usuario. Mientras que alguno de los actuadores que incorporaban actualmente las máquinas no funcionaban como a los ingenieros les gustaría, otros sistemas estaban siendo estudiados pero no habían comenzado su desarrollo.

Entonces, me puse de acuerdo con ellos para conocer qué tipo de cambios querían realizar en los actuadores existentes y qué sistemas nuevos querían incorporar. Ellos ya habían adquirido algunos sensores para incorporarlos a las máquinas, pero carecían de un sistema para controlarlos. Para los sistemas nuevos que consideraban interesantes, yo me encargué de buscar unos sensores adecuados.

Uno de los grandes problemas con los que me encontré, fue el medio en el que los sistemas debían funcionar. Al tratarse de máquinas cortacésped, debía escoger sensores robustos que resistieran situaciones adversas como suciedad, polvo e incluso agua. Además de idear un sistema que satisficiera las necesidades de los ingenieros, debía encontrar el sensor adecuado y en algunos casos, fabricar una carcasa o medio de protección de los sensores para evitar que sufrieran daños. En cualquier caso, los ingenieros de la empresa siempre me ofrecieron ideas y soporte frente a las dificultades que encontraba y en las que me ofrecer una solución.

## **2.4 Electrónica en máquinas cortacésped**

En los últimos tiempos, la electrónica ha aparecido prácticamente en todos los campos. En el campo de las máquinas cortacésped, además de introducir sistemas de control de variables de interés para el usuario en los modelos actuales, se han creado sistemas autónomos para realizar estas tareas de forma programada y automática. Los robots cortadores son unos cortacéspedes automáticos guiados por un alambre que define el área a cortar.

El robot utiliza este cable para buscar el límite de la zona a recortar y en algunos casos para localizar a un muelle de carga. Este tipo de cortadoras de césped robóticas son capaces de mantener hasta 5 hectáreas (20.000 m<sup>2</sup>) de césped. Son cada vez más sofisticadas y contienen cada vez más sensores haciendo estas máquinas prácticamente autónomas.

A partir de un cable perimetral colocado sobre la zona de corte, este robot es capaz de recrear un mapa de la zona de trabajo y de forma programada por el propietario, realizar el corte del césped. Estas máquinas incorporan un microprocesador que guardará datos de la región de corte además de recoger los datos de los sensores montados sobre la máquina y actuar cuando las condiciones sean las propicias para realizar su trabajo. Estas máquinas totalmente eléctricas, cuentan con una estación de carga a la que son capaces de regresar cuando su batería es baja reduciendo al mínimo su interacción con las personas.

Fig. 2.7. Robot cortacésped y detalle del display que incorpora

## **2.5 Conclusiones finales**

Como en todos los campos, la electrónica cada vez está más presente en las máquinas cortacésped. La inclusión de sistemas electrónicos en las mismas requiere de un estudio previo que determine el entorno en el que la máquina va a trabajar, a que situaciones puede ser sometida y otros aspectos que llevarán al diseñador a utilizar unos sensores u otros. En mi caso, he concluido que el estudio del entorno en el que la máquina desarrollará su trabajo es realmente importante, ya que determinará el uso de un tipo determinado de sensor y las precauciones y medidas de seguridad que se deberán tomar para evitar daños en el sistema electrónico.

Igualmente, hay una gran diferencia entre el diseño creado en el laboratorio y el diseño final que se montará sobre la máquina porque siempre aparecen variables o situaciones como vibraciones, ruidos, etc. que en el diseño no tienes en cuenta y que posteriormente debes modificar para evitarlos.

### **3. SISTEMA DE CONTROL BASADO EN PSoC**

Antes de comenzar el diseño de cualquier sistema electrónico es importante tener en cuenta los posibles componentes que serán utilizados en el mismo y las posibilidades que ofrece cada uno de ellos. Como elemento principal de un sistema electrónico, el microprocesador o microcontrolador que incorporará, deberá garantizar la capacidad de satisfacer todas las necesidades que pueda requerir dicho sistema.

Además, la interfaz de trabajo de este instrumento también ayudará al diseñador a decantarse por la elección de un microcontrolador u otro pero antes de decidirse entre uno u otro, el diseñador deberá conocer las necesidades de su sistema y la capacidad del microcontrolador para satisfacer todas ellas. Aspectos a tener en cuenta a la hora de realizar la decisión de la utilización de uno u otro microcontrolador pueden ser la capacidad de integración del mismo, la facilidad de programación, la interfaz de usuario que este ofrece o el coste del mismo.

Por tanto, tomando en cuenta los aspectos mencionados realizaré una comparación entre dos microcontroladores: el microcontrolador de Freescale MC9S08QG8 y el microcontrolador de Cypress PSoCCY8C9466-2PXi.

#### ***3.1 Propuesta de sistema de control***

Como ya se ha comentado previamente, el objetivo de este proyecto final de carrera consiste en la creación de un sistema de control de algunas variables de interés para el usuario de una máquina cortacésped. En el punto 4 de esta memoria, se puede encontrar una minuciosa explicación de todos los aspectos concernientes al control de estas variables que a grandes rasgos consisten en el control de tres sensores y en la habilitación de una comunicación serie con el PC a través del puerto serie.

Para realizar el control de dichos sensores así como del puerto serie era necesaria la elección de un microcontrolador que tuviera la capacidad tanto de procesar los datos arrojados por estos así como de ofrecer una respuesta a los datos ofrecidos por estos. En la asignatura de microprocesadores e instrumentación electrónica tuve la oportunidad de conocer el funcionamiento de los microcontroladores.

El  $\mu$ C utilizado en la misma fue el MC9S08QG8 de Freescale que ofrecía una visión global del funcionamiento de los mismos y que me permitiría posteriormente la posibilidad de controlar otros  $\mu$ C diferentes.

Ya que el  $\mu$ C utilizado en el sistema final de control es el PSoC CY8C29466 de Cypress mostraré algunas de las características de los mismos así como sus interfaces de trabajo para justificar el uso del mismo. También tuve en cuenta la posibilidad de adquirir un STARTER KIT para poder conocer las capacidades de cada uno de estos  $\mu$ C antes de incorporarlos al sistema final de control.

Un STARTER KIT consiste en una pequeña placa que incorpora un  $\mu$ C el cual permite explotar todas las propiedades del mismo, permitiendo al usuario tener una idea global de las posibilidades que ofrece. Suele incorporar además un software y un hardware de control para poder programar al  $\mu$ C posibilitando así la creación de infinidad de pruebas.

A continuación mostrare algunas de las propiedades de cada uno de los dos  $\mu$ C mencionados y las características que me llevaron a decantarme por uno de ellos.

### 3.1.1 Microcontroladores: MC9S08

El MC9S08QG8 es un microcontrolador de 8 bits de la familia FREESCALE que integra el CPU HCS08 de 20MHz. Este µC integra 8KB de memoria FLASH, 512B de RAM, un oscilador interno, hasta 14 pines de E/S y bloques de comunicación (SCI, SPI e I2C), temporización, conversión AD, etc. y se presenta en un encapsulado DIP de 16 bits.

El usuario dispondrá de hasta 14 GPIO's (General Purpose Input/Output, E/S de propósito general) con las que podrá desarrollar infinidad de sistemas. Es uno de los aspectos importantes a tener en cuenta, ya que la cantidad de GPIO's disponibles determinará la capacidad de integración del número de variables externas controlables por el mismo. Cuenta con un interfaz de desarrollo de programación de los mismos, el Code Warrior, que incluye diversos módulos como un editor/compilador de lenguaje ensamblador y C, simulador y depurador. También dispone de un STARTER KIT que comentare a continuación.

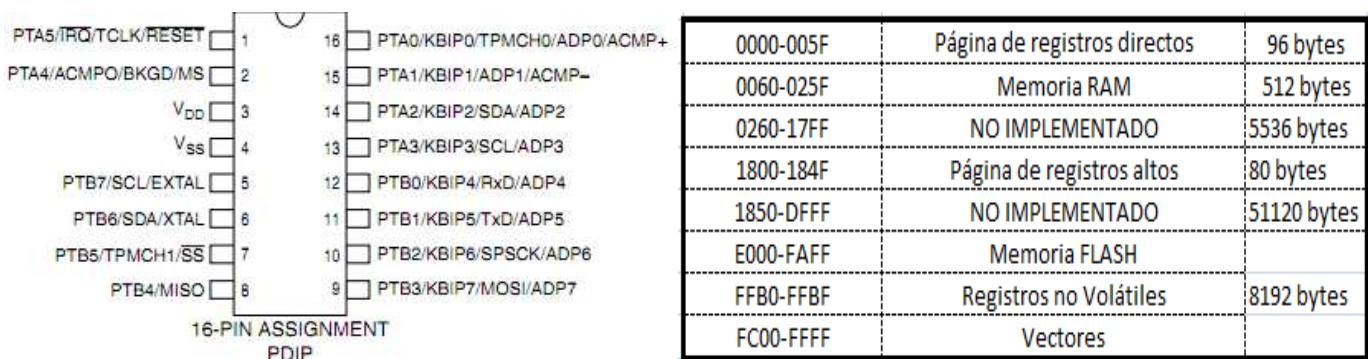

En la siguiente figura se muestra el patillaje del S08 con un encapsulado DIP 16 y su mapa de memoria correspondiente:

Diagrama que muestra el patillaje del MC9S08QG8 en encapsulado DIP 16 y su mapa de memoria correspondiente. El patillaje (16-PIN ASSIGNMENT PDIP) muestra la asignación de pines de 1 a 16. Los pines 1 a 8 están dedicados a puertos PTA y PTB, respectivamente. Los pines 9 a 16 están dedicados a la memoria y a la interfaz de comunicación. El mapa de memoria (Memory Map) enumera las direcciones y sus correspondientes funciones:

| Dirección | Función                      | Tamaño      |

|-----------|------------------------------|-------------|

| 0000-005F | Página de registros directos | 96 bytes    |

| 0060-025F | Memoria RAM                  | 512 bytes   |

| 0260-17FF | NO IMPLEMENTADO              | 5536 bytes  |

| 1800-184F | Página de registros altos    | 80 bytes    |

| 1850-DFFF | NO IMPLEMENTADO              | 51120 bytes |

| E000-FAFF | Memoria FLASH                |             |

| FFB0-FFBF | Registros no Volátiles       | 8192 bytes  |

| FC00-FFFF | Vectores                     |             |

Fig. 3.1 Asignación de pines del S08QG8 y mapa de memoria

Como se puede observar, cada patilla puede adoptar diversas configuraciones. Cuenta con dos puertos, PTA y PTB, de propósito general que cuentan con 6 y 8 bits respectivamente mostrados en la asignación de pines como PTAx y PTBx, siendo x el número de bit en el puerto. También se puede observar que la parte baja del byte de estos puertos puede adoptar la configuración KBIPx, cuyas siglas significan *Keyboard Interrupt Pin* o Pin de interrupción de teclado, que permitirá al usuario crear interrupciones a través de la configuración de estos.

Ya he comentado, que el S08 cuenta con un conversor AD de 10 bits y 8 canales integrado, al cual accederemos a través de la configuración tanto de los registros asociados así como de los pines señalados con las siglas ADP (pines 9 a 16, ambos incluidos) y también, podemos utilizar un comparador analógico configurando los pines nombrados con ACMP+ y ACMP-. Además de los conversor AD y del comparador analógico, el S08 cuenta con varios protocolos de comunicación serie. Configurando correctamente los registros y los pines asociados podremos realizar protocolos I2C a través de los pines SCL y SDA (pin 13 y pin 14), SCI a través de los pines TxD y RxD (pin 11 y pin 12), SPI mediante los pines SS, MISO, MOSI y SPSCK (en los pines 7, 8, 9 y 10).

En los siguientes puntos mostrare algunas de las características tanto del starter kit como del software de Freescale, el Code Warrior.

- STARTER KIT DEMO9S08QG8

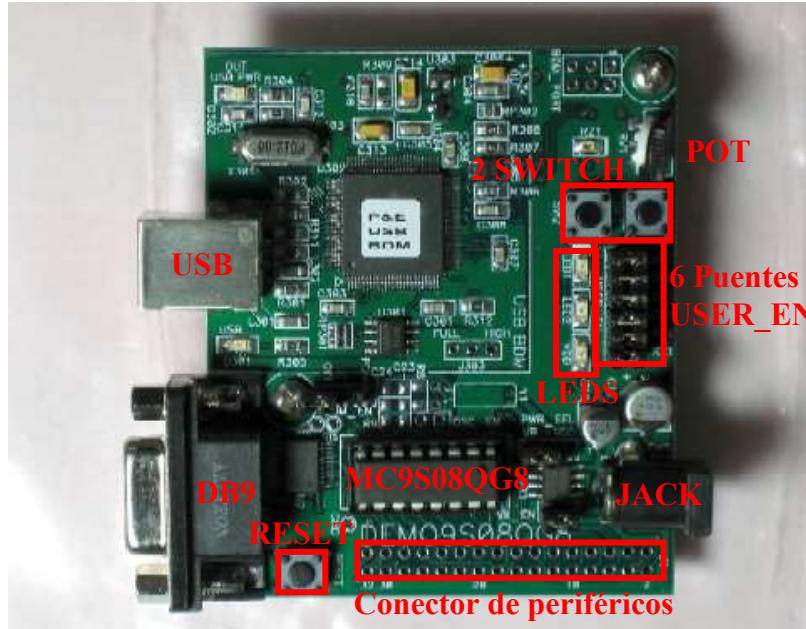

Fig. 3.2 Starter kit DEMO9S08QG8 de Freescale

La DEMO9S08QG8 es una tarjeta basada en el  $\mu$ C de Freescale. Esta tarjeta se utilizará a través del interfaz gráfico comentado, el Code Warrior, que permitirá al usuario editar y compilar programas así como su grabación en la memoria Flash del S08 que está integrado en la placa y además la opción de ejecutar dichos programas para comprobar su funcionamiento. Esta tarjeta incluirá, entre otras, las siguientes características:

1. El microcontrolador MC9S08QG8 con su encapsulado DIP16, alimentado a 3.3V y a 4 MHz.

2. Interfaz USB BDM de Motorola, que es la zona marcada por un cuadrado blanco en la placa Demo.

3. Un puerto USB desde el que se alimentará a la placa. También se puede alimentar con una fuente de 9V a través del regulador a 3.3V que incorpora.

4. Algunos periféricos: 3 interruptores (uno de ellos con la función de RESET), 3 diodos LED (uno de ellos conectado a Vcc), un potenciómetro, un fototransistor, un conector Jack y un conector DB9 para comunicación serie.

Además incluye un conector al que podremos conectar periféricos externos dependiendo de nuestras necesidades. Para poder utilizar esta placa en el ordenador, es necesario contar con el software Code Warrior de Freescale que describiré a continuación.

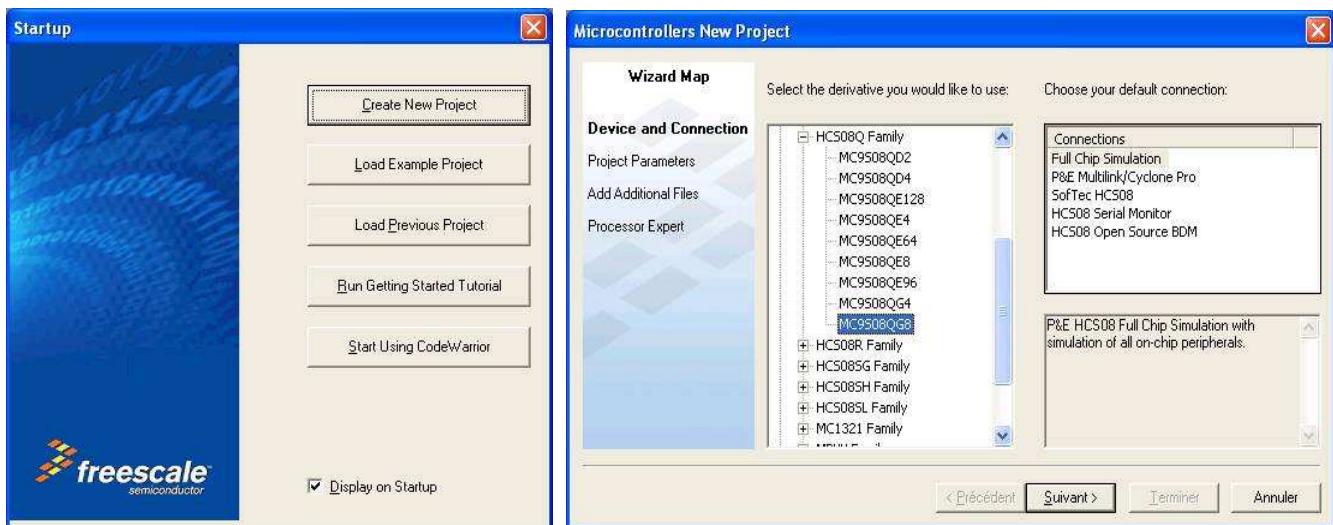

- CODE WARRIOR

Este entorno de desarrollo creado por Freescale permite realizar sistemas basados en la familia de  $\mu$ C HC(S)08. Este software incluye editor, ensamblador, compilador en C, simulador y depurador de hardware. Supone una ventaja la posibilidad de poder crear proyectos en varios lenguajes de programación. Para iniciar la creación de un proyecto se deben de seguir una serie de pautas. Una vez instalada la placa DEMO en el ordenador, se puede ejecutar el programa:

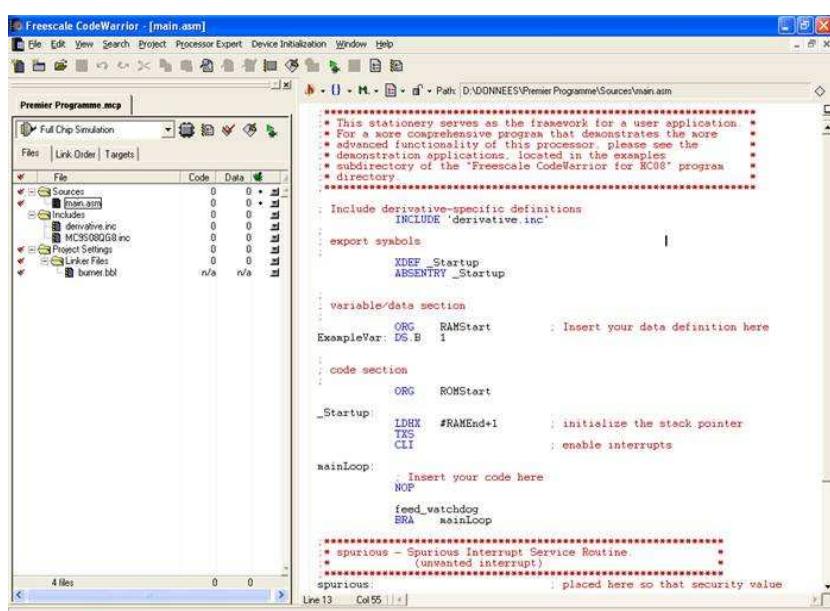

Fig. 3.3 Ventanas del programa Code Warrior de Freescale

Al crear un nuevo proyecto, deberemos elegir de la lista el  $\mu$ C con el que se va a trabajar y seguidamente el tipo de configuración que se desea. Normalmente, la configuración elegida será “Full Chip Simulation” que permitirá realizar simulaciones con todos los periféricos. Después se deberá elegir el código de programación que se utilizará en la confección del programa y una vez creado el proyecto la ventana de explotación donde se podrá confeccionar el código será la siguiente:

Fig. 3.4 Interfaz de trabajo del programa Code Warrior

En la derecha de la pantalla, se podrá confeccionar el código ensamblador o código C que posteriormente será grabado en el S08 y también se podrán modificar los registros de los diferentes periféricos de éste para realizar diversas tareas.

El acceso a dichos registros se puede realizar a través del menú desplegable que aparece en la izquierda de la pantalla, donde están todos los archivos relacionados con el proyecto que se está realizando. Una vez confeccionado el código, se puede compilar en busca de errores y posteriormente grabarlo en el S08 para comprobar su funcionamiento.

La necesidad de un mayor número de GPIO's para controlar todos los sensores que adquirieran variables de interés y su posterior procesamiento acompañado de una interfaz gráfica mucho más novedosa y configurable, me llevó a tomar la decisión de utilizar el PSoC CY8C29466 que al ser una herramienta mucho más moderna y potente permite desarrollar sistemas totalmente configurados por el usuario, con una capacidad de hasta 24 GPIO's configurables.

En los siguientes apartados mostraré todas las características y propiedades del microcontrolador de Cypress así como de su interfaz de usuario, el PSoC Designer IDE.

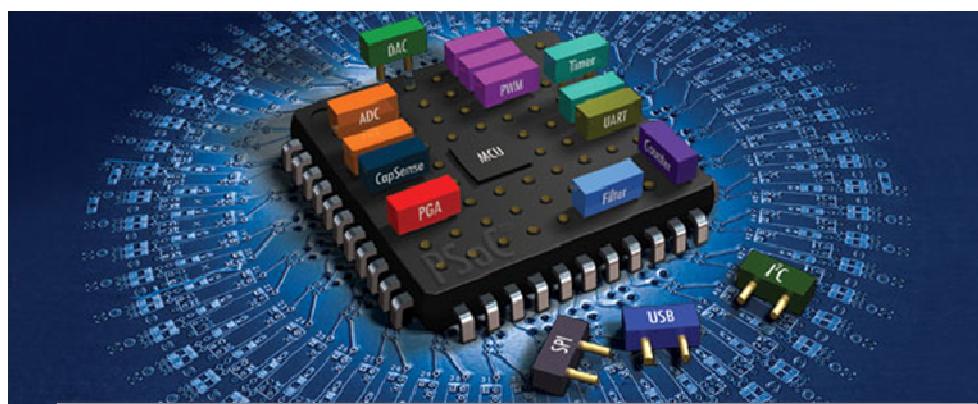

### **3.2 PSoC CY8C29466-24PXi**

El PSoC modelo CY8C29466-24PXi es el microcontrolador que he escogido para realizar mi sistema de control por su gran facilidad de configuración, tanto del software como del hardware. Incluido en la familia de los “embedded systems” (del inglés, sistemas empotrados), permiten reducir sustancialmente el tamaño de cualquier diseño electrónico gracias a su alto número de bloques configurables (Conversores A/D, D/A, amplificadores de ganancia programables, PWM, UART, etc.) permitiendo obtener un producto final con un alto nivel de prestaciones en un espacio realmente reducido.

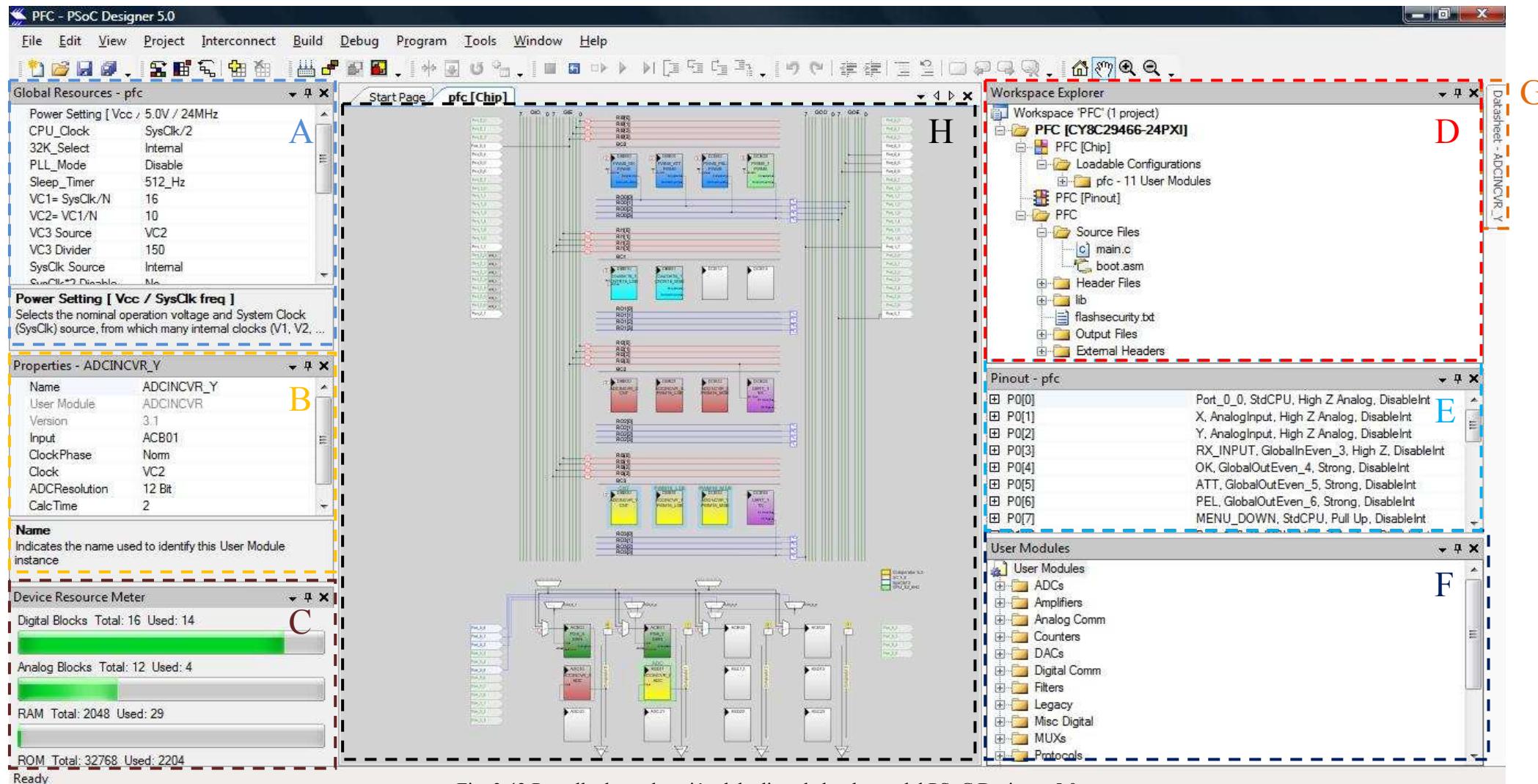

La programación del mismo se realiza a través de un software creado por Cypress, el PSoC Designer, que permite realizar la configuración tanto del SW como del HW del PSoC con una interfaz gráfica sencilla e intuitiva que ofrece un amplio abanico de opciones, dando la oportunidad al usuario de realizar un sistema de acuerdo a sus necesidades gracias a la alta personalización de cada uno de los bloques configurables mencionados, y de los que posteriormente, realizaré un análisis a fondo.

Además, permite al usuario realizar su proyecto en 2 lenguajes de programación (C o ensamblador) facilitando aún más su tarea.

Fig. 3.5 Detalle del PSoC CY8C29466-24PXi

Fig. 3.6 Imagen ilustrativa de los innumerables bloques que incluye el PSoC

A continuación comentaré todos los aspectos reseñables de este microcontrolador, valores típicos, características eléctricas, configuraciones posibles, software de programación, así como un detallado análisis de la configuración de algunos de los bloques más importantes y de igual manera, los utilizados por mí para la realización del proyecto.

### 3.2.1 Introducción/Generalidades

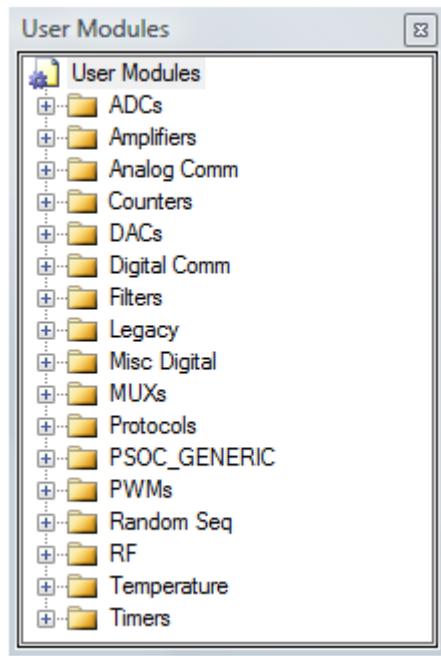

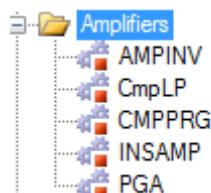

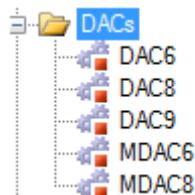

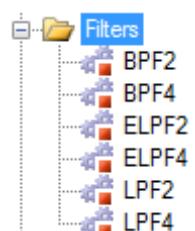

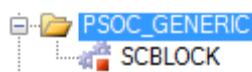

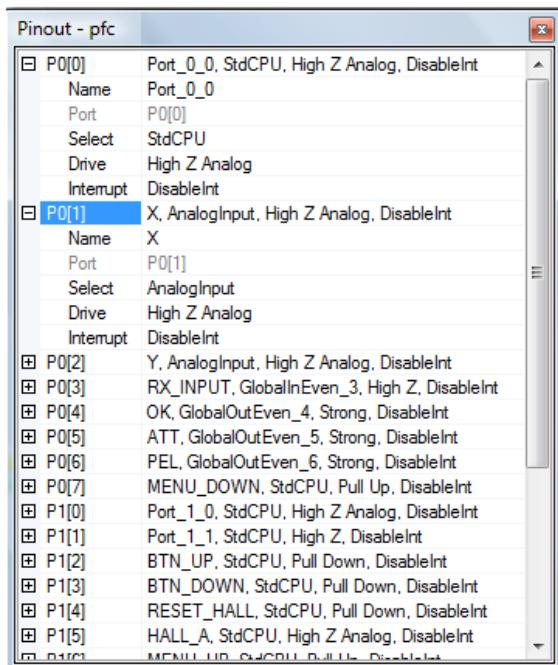

El PSoC CY8C29466-24PXi de Cypress es un microcontrolador de 8 bits con una alta capacidad de configuración, tanto de software como de hardware. Dentro del mismo podemos encontrar infinidad de bloques de usuario, analógicos y digitales, incluso de comunicación. Estos son:

Fig. 3.7 Muestra de todos los Módulos de usuario con los que cuenta el PSoC

- A. Bloques analógicos: Cada uno de los mencionados a continuación, son los bloques genéricos de carácter analógico, incluyendo cada uno diversidad de configuraciones posibles. La enumeración de los bloques de usuario se rige por la aparición en el software de Cypress.

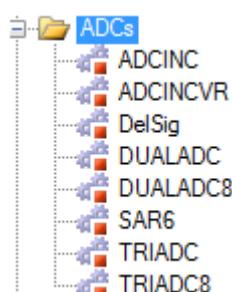

- Conversores A/D

Dentro de los Conversores A/D, podemos encontrarlos incrementales, incrementales con número de bits configurables, Delta Sigma, de doble y triple entrada de 8 bits, de doble y triple entrada con numero de bits configurables y por último, uno de aproximaciones sucesivas.

- Amplificadores

Los más comunes que podemos encontrar dentro de los amplificadores son los de ganancia programable, los inversores y los de instrumentación, los cuales posibilitan una amplia gama de ganancias. También es posible encontrar amplificadores configurados para funcionar como comparadores de baja potencia y como comparadores programables.

- Conversores D/A

Los Conversores D/A genéricos disponibles son de 6, 8 y 9 bits. También es posible utilizar DACS que multiplican la salida analógica mediante transformaciones de los bits de entrada digitales.

- Filtros

En el bloque de filtros, encontramos entre otros filtros de paso de banda y filtros paso bajo. Ambos tipos con la posibilidad de elegirlos de 2 o 4 polos.

- Bloques genéricos del PSoC

Dentro de este apartado podemos encontrar un bloque con una alta capacidad de configuración. Se trata de un condensador controlado por interruptores (Switched Capacitor BLOCK)

- Sensor de Temperatura

Por último, tenemos un bloque para la medición de la temperatura de la memoria Flash.

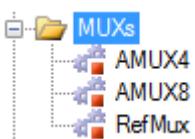

- Multiplexores

Estos multiplexores analógicos permiten seleccionar al usuario la entrada analógica que entrará en uno de los bloques CT (Continous Time), normalmente amplificadores. Es posible elegir entre 4 y 8 entradas.

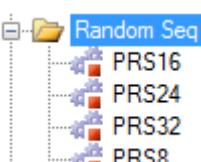

- B. Bloques Digitales: Los bloques digitales que podemos encontrar incluyen contadores, moduladores de ancho de pulso (PWM), multiplexores, etc. A continuación se muestra una enumeración de los mismos:

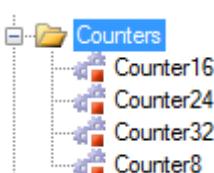

- Contadores

Los contadores que podemos encontrar son de 8, 16, 24 o 32 bits y tienen una fácil configuración tanto software (interrupciones para lectura, reset de conteo, etc.) como hardware ( ck de conteo, nº de bits...).

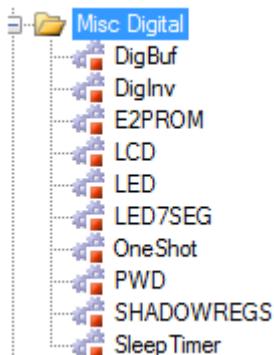

- **Misclánea Digital**

En este bloque encontramos una gran diversidad de funcionalidades muy útiles que facilitan mucho la labor del programador. Un claro ejemplo es el módulo del LCD que permite una sencilla escritura en el mismo con un simple par de instrucciones evitando así la típica rutina para inicializarlo.

También podemos encontrar módulos como el E2PROM que permite leer/escribir datos en memoria no volátil, el módulo de control de pantallas de 7segmentos de hasta 8 dígitos, un Sleep timer(para dejar el micro en suspensión), un módulo para configurar los GPIO's en los que conectaremos un diodo LED,

Así como otros bloques interesantes: Un buffer digital( un amplificador en modo seguidor), un inversor lógico, un generador de 1 pulso en respuesta a una señal entrada especificada (One Shot), un discriminador de ancho de pulso (PWD) y los SHADOW registers (que permiten utilizar de manera simultánea un puerto para varias tareas sin que se vean afectadas cada una de ellas por separado).

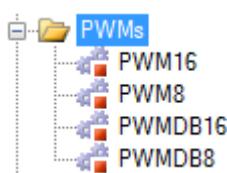

- **Moduladores de ancho de pulso (PWM)**

Este bloque permite integrar en el PSoC un PWM y su configuración dependiendo de las necesidades del programador. Así, este puede ser de 8 o 16 bits y puede tener 8 bits de generador de banda muerta (Dead Band Generator). Es posible configurar el ck del PWM permitiendo obtener cualquier tipo de señal

- **Generador de secuencias pseudo aleatorias (PSR)**

Este bloque proporciona una secuencia de números aleatorios que te permite establecer el algoritmo que regirá esta secuencia de números. Un bloque bastante útil para realizar, por ejemplo, juegos de azar (un dado, una carta, etc.)

- **Temporizadores (Timers)**

Los timers, parecidos a los contadores, pero conceptualmente diferentes pueden escogerse con diferente número de bits, siendo estos 8, 16, 24 o 32 bits y al igual que los contadores se pueden configurar totalmente (Sw y Hw).

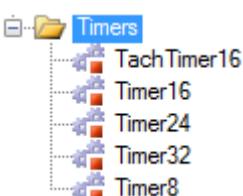

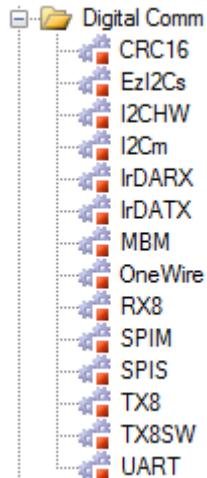

C. Bloques de comunicación: Es necesario realizar un apartado para enumerar las posibilidades que tiene el PSoC para comunicarse con otros dispositivos. Estos protocolos de comunicación son tanto digitales como analógicos y son los siguientes:

- Comunicación analógica

El DTMF (Dual Tone Multiple Frequency) es un generador de señales configurado como un conversor D/A de 6 bits, que envía información en forma de tonos analógicos a una frecuencia determinada por el usuario.

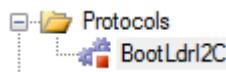

- Comunicación digital

- Protocolo BootLoader I<sup>2</sup>C

Este bloque de usuario permite realizar una configuración inicial al PSoC mediante el protocolo de comunicación I<sup>2</sup>C

- Módulos

Como se puede observar, existe una gran variedad de módulos de usuario de comunicación digital. Entre los protocolos más conocidos podemos destacar:

UART (Universal Asynchronous Receiver Transmitter), I<sup>2</sup>C (Inter-Integrated Circuits) , SPI (Serial Peripheral Interface) y OneWire(un cable) los cuales permiten realizar la comunicación entre el PSoC(en el papel de maestro) y un número n de dispositivos (esclavos) con solo dos hilos, que variará su función dependiendo del protocolo.

Otros bloques de comunicación digital que podemos utilizar son los protocolos de CRC (Cyclical Redundancy Check), recepción IR, MBM (Mail Box Manager) y receptor serie de 8 bits(para RS-232, UART separada en módulos TX y RX independientes).

A la vista del alto número de bloques que incluye el PSoC, es fácil tener una visión global de todas las posibilidades que ofrece este microcontrolador, el cual permite reducir el número de componentes electrónicos periféricos externos de cualquier diseño, el tiempo de diseño y, en consecuencia, el coste del proyecto.

En los próximos apartados, procederé a ampliar toda la información sobre el PSoC citada hasta ahora.

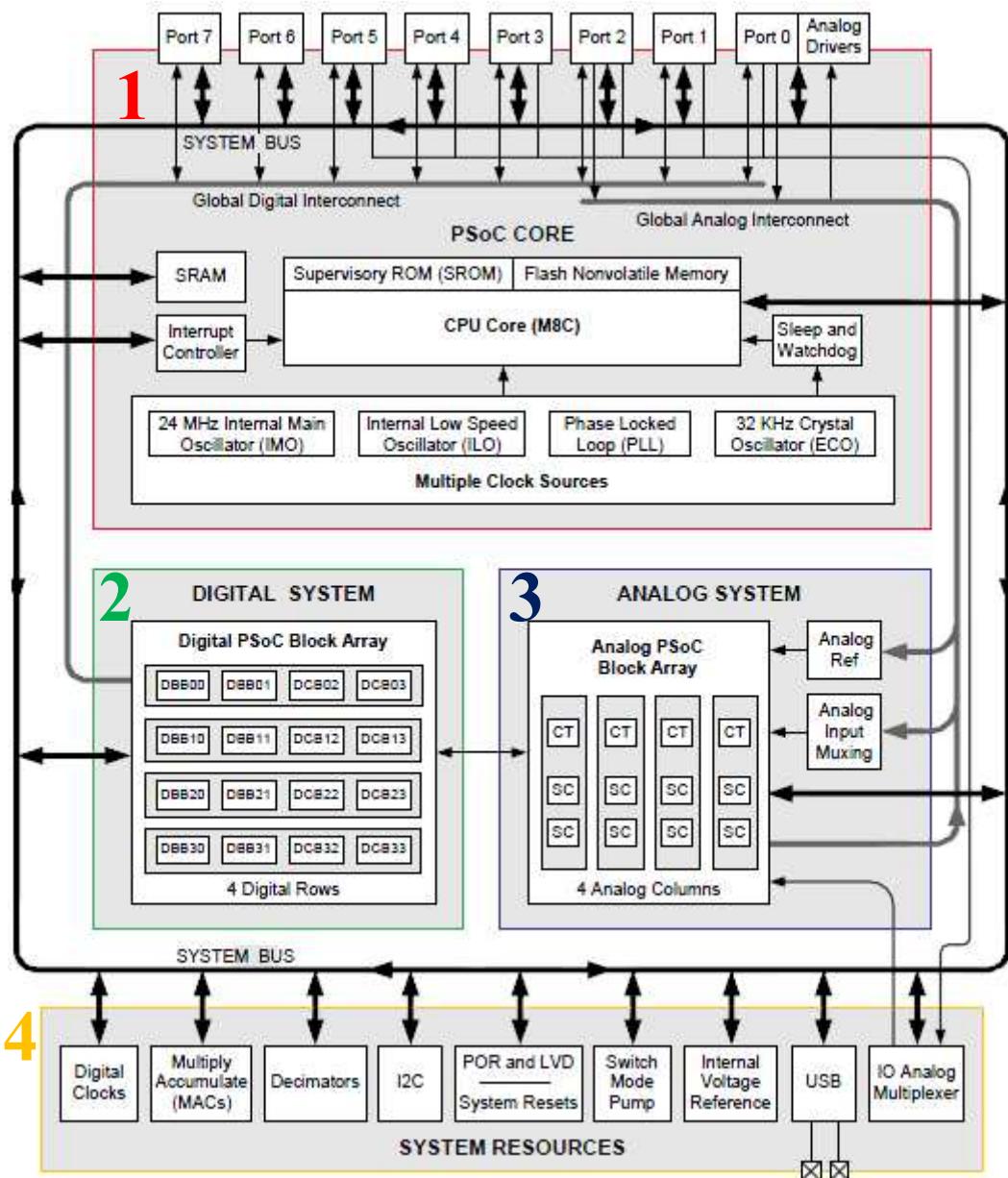

### 3.2.2 Arquitectura

La imagen que se muestra a continuación, disponible en el TRM (Technical Reference Manual) de Cypress, dispone la situación de todas las partes (numeradas) que componen la arquitectura interna del PSoC CY8C29x66:

Fig. 3.8 Arquitectura interna del PSoC CY8C29x66

Las 4 partes en que se puede descomponer la estructura interna del PSoC son:

1. PSoC Core (Núcleo del PSoC)

2. Digital System (Sistema Digital)

3. Analog System (Sistema Analógico)

4. System Resources (Recursos del sistema)

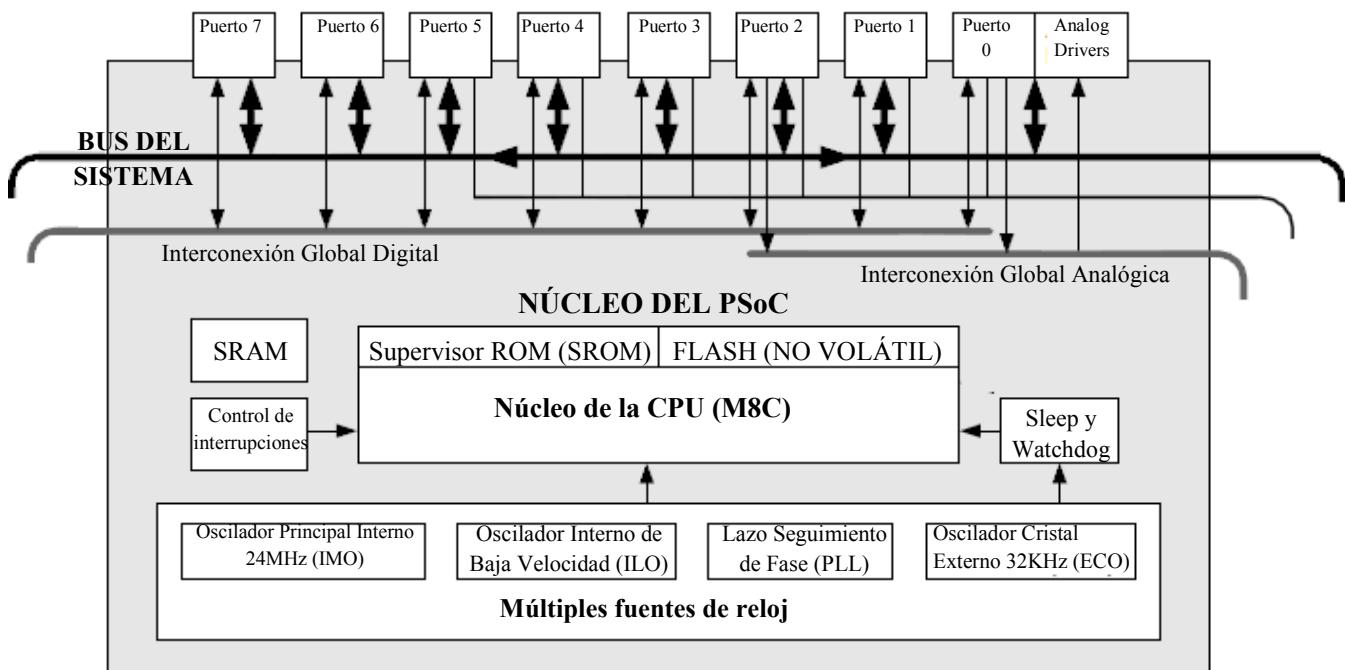

### 3.2.2.1 PSoC Core (Núcleo del PSoC)

Fig. 3.9 Núcleo del PSoC

El componente principal del núcleo del PSoC es un potente microcontrolador de 8 bits que ofrece 4 MIPS (millones de instrucciones por segundo) a 24 MHz, la velocidad de su oscilador interno principal, que mediante flexibles generadores (en PSoC Designer, a través de VC1, VC2 y VC3) permiten obtener múltiples fuentes de reloj para casi cualquier requerimiento.

Fig. 3.10 Detalle de conexión del cristal externo de 32 KHz (ECO)

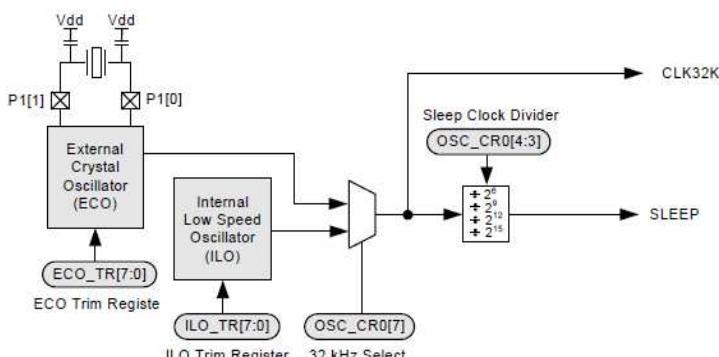

Además de este oscilador de 24 MHz, llamado IMO (Internal Main Oscillator), dispone de otras fuentes de reloj como el ILO (Internal Low Speed Oscillator), con una frecuencia de 32KHz, utilizado para despertar al sistema tras un estado en modo Sleep o para realizar resets con el Watchdog, aunque también puede utilizarse como fuente para bloques digitales.

Otra fuente de tiempo de la que puede disponer el núcleo es la llamada ECO (External Crystal Oscillator), que permite añadir un cristal de 32KHz externo, que generaría las demás fuentes de tiempo con una pequeña configuración del software (el cristal proporcionaría la referencia al IMO en el modo PLL).

La otra fuente que dispone se conoce como PLL (Phase-Locked Loop) que se encarga de proporcionar una frecuencia de oscilación de 24 MHz cuando se utiliza un cristal de 32KHz externo.

En lo referente a memoria, el núcleo posee 32 KB de memoria FLASH, no volátil, para el almacenamiento del programa y 2 KB de SRAM para almacenamiento de datos. Como se puede ver en el esquema, el llamado supervisor ROM (SROM), que contiene el código usado para realizar el boot (configuración inicial) del PSoC y las operaciones de la Flash.

Al igual que la mayoría de microcontroladores, el PSoC dispone de 5 registros que utiliza durante su funcionamiento. Dichos registros tienen 8 bits (el PC tiene 16) y son los siguientes: Acumulador (Accumulator), Índice (indeX), Contador de programa (ProgramCounter), Puntero de pila (StackPointer) y el indicador de estados (flags).

A través del bus del sistema, el núcleo se comunica con los otros bloques del integrado y con el exterior. Para captar las señales externas, el núcleo cuenta con un número variable de puertos E/S dependiendo del modelo del PSoC. En este caso, el 29466 cuenta con 3 puertos de 8 entradas/salidas de propósito general llamadas GPIOs (General Purpose Input Output). Estos puertos interconectan el bloque analógico y el bloque digital con el núcleo, lo que hace posible la interpretación de cualquier naturaleza de señal recibida en cualquiera de sus 24 entradas.

Cada una de estas 24 entradas/salidas, GPIO's, son totalmente configurables por software dependiendo de la función que desempeñe y de la naturaleza de la señal, analógica o digital. Los modos de configuración son los siguientes: high Z, high Z analog, open drain high, open drain low, pull up, pull down, strong y strong slow.

Cada uno de los modos descritos será descrito más a fondo en el apartado 3.2.6.

Por defecto, las GPIO están configuradas con alta impedancia analógica y por norma general se configurarán, como strong si tiene función de salida y como high z si su función es de entrada. Además, es de gran utilidad utilizar las resistencias de "pull up" y "pull down" internas de cada uno de las GPIO, ya que estos circuitos son cuando se escribe un '1' o un '0', respectivamente. En el apartado de entradas/salidas se describe cada uno de estos modos de una forma más concreta.

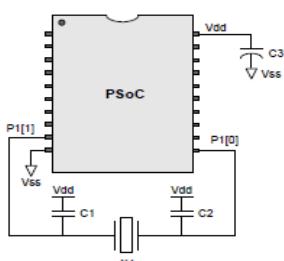

### 3.2.2.2 Sistema Analógico

Fig. 3.11 Esquema de bloques del sistema analógico del PSoC

Como se puede ver en el esquema, en lo referente a entradas y salidas, este bloque tiene una comunicación bidireccional tanto con el bus del sistema (Núcleo del PSoC, del que recibe las señales de reloj digitales), así como con el sistema digital. La comunicación de estos bloques con los puertos de E/S (GPIO's) se realiza a través de una red de multiplexores que se detallará a continuación.

El sistema analógico es una de las piezas claves del PSoC, ya que se encarga de la recepción así como del procesamiento y posterior manipulación de las señales analógicas.

Dependiendo del modelo de PSoC, este puede contener de 1 a 4 columnas de bloques analógicos. En el caso que nos concierne, el 29466 está formado por un array de cuatro columnas con tres bloques analógicos cada una. Estos tres bloques, están montados sobre amplificadores operacionales de bajo offset y bajo ruido y mediante un registro el PSoC determina la tipología de señal analógica dentro de los mismos. Estos bloques se llaman, CT (de tiempo continuo) y SC (condensadores conmutados, del inglés, Switched Capacitors). Dependiendo de la aplicación o de la naturaleza de la señal, se utilizará uno u otro.

Dada dicha configuración, el usuario tiene un gran elenco de posibilidades a la hora de crear su proyecto embebido, ya que dependiendo de sus necesidades de hardware, este utilizará una clase u otra de recursos.

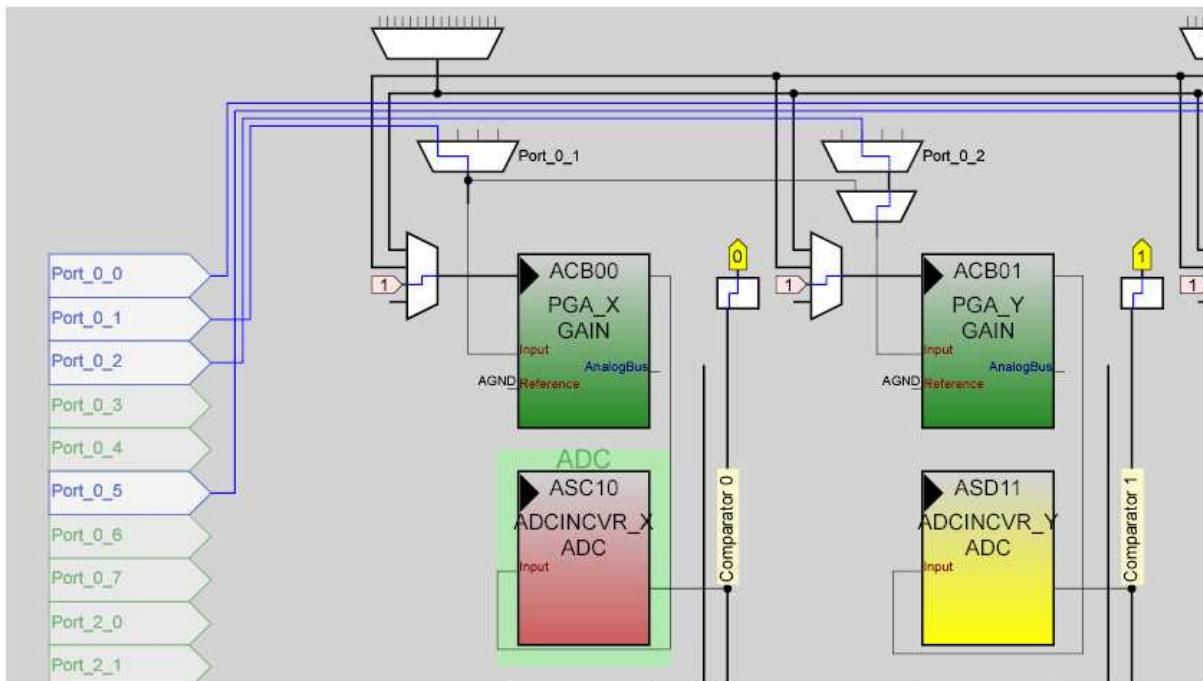

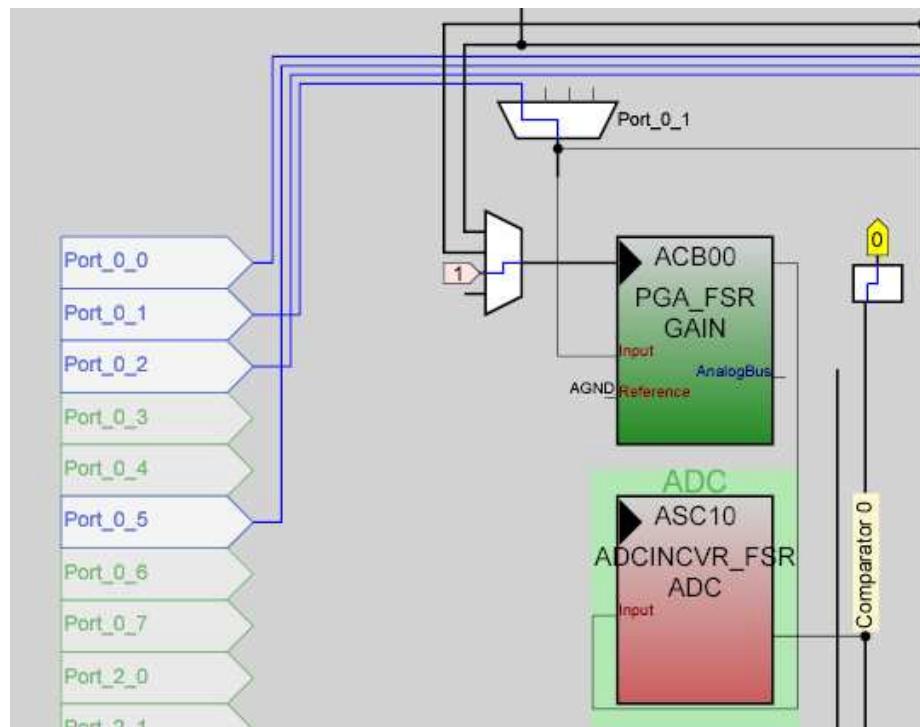

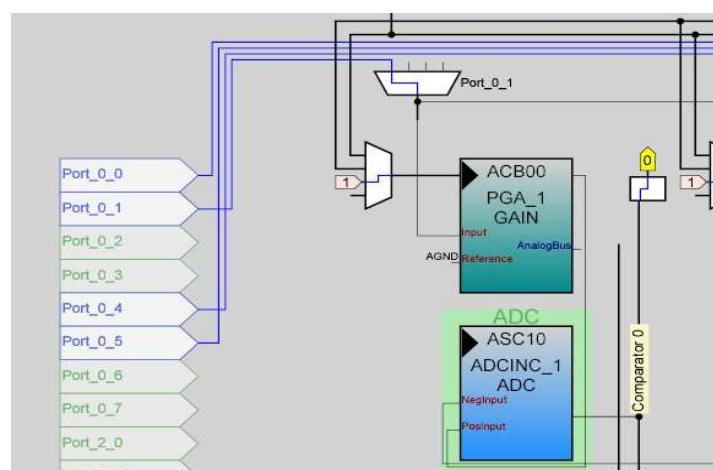

### 3.2.2.2.1 Interfaz, array y comunicación del sistema analógico

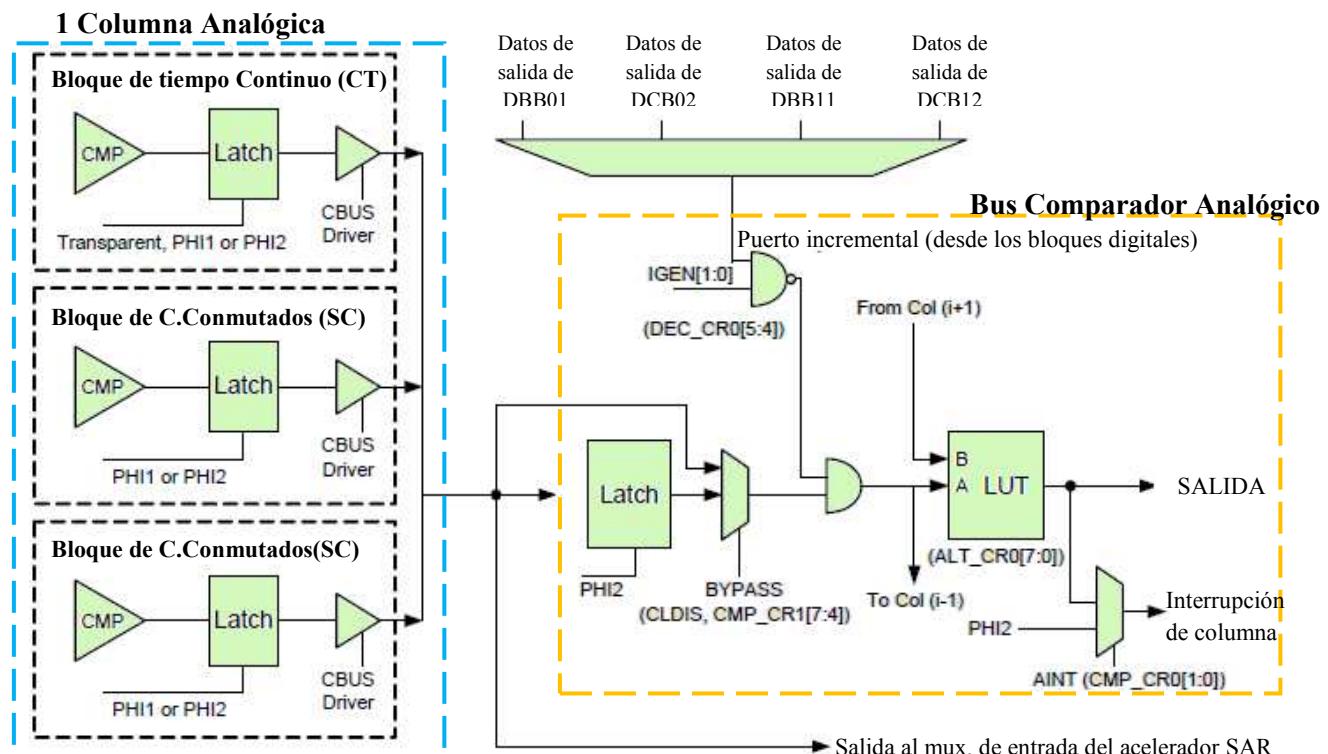

Como ya se ha comentado, el CY8C29466 cuenta con un sistema analógico en el que los bloques analógicos están organizados en columnas formando un array de cuatro columnas. Cada una de estas columnas contiene un bus comparador y 3 bloques analógicos asociados: un bloque de tiempo continuo (CT) y dos bloques de condensadores conmutados (SC) tipo C y tipo D. En la siguiente imagen se muestra el diagrama de bloques de una de ellas:

Fig.3.12 Diagrama de bloques de una columna analógica con su bus comparador asociado

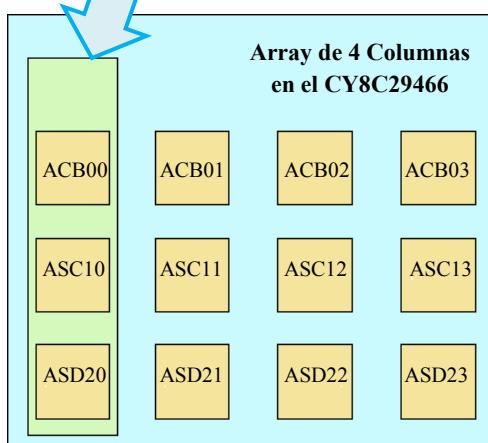

Fig.3.13 Configuración del array del CY8C29466

Como se muestra en la imagen, cada uno de los bloques de la columna analógica contiene un registro de retención (latch) que mantendrá el dato hasta que esté disponible, para después enviarlo al bus comparador analógico. Este bloque comparador, que también cuenta con un registro de retención con la misma función que el anterior, conducirá las señales a los bloques digitales como datos de entrada. También servirá como entrada al decimador y como entrada a interrupciones. A través del bloque LUT, *look up table*, se podrán modificar o combinar las salidas del bus comparador analógico con otros buses a partir de 2 entradas A y B proporcionando 16 posibilidades de funciones lógicas para dichas entradas. En la siguiente imagen podemos ver la configuración del CY8C29466, que cuenta con 4 columnas analógicas. El detalle del cuadro verde muestra la columna que ha sido expandida en la imagen anterior incluyendo el comparador de bus. A continuación mostraré la red de configuración de entrada analógica.

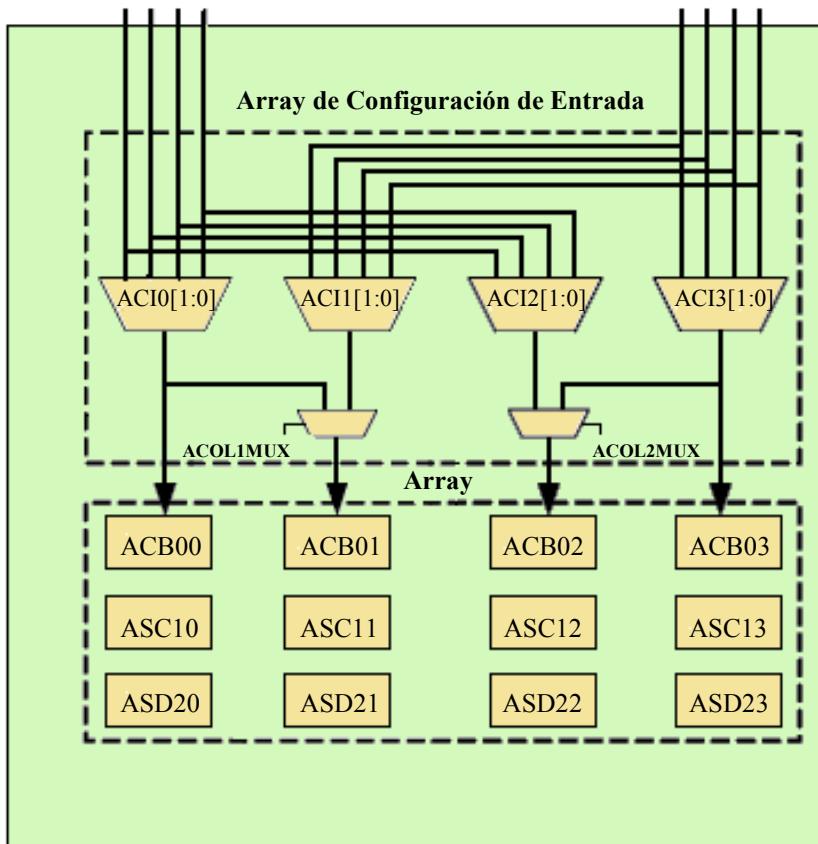

Fig. 3.14 Configuración del array del CY8C29466

El array de 4 columnas del PSoC a través de una red de multiplexores permite la unión entre los bloques analógicos y los pines exteriores del encapsulado de 28 pines. Como se puede ver, las columnas de las esquinas son alimentados por un multiplexor de 4 entradas mientras que las columnas centrales pueden ser alimentados por uno o dos multiplexores.

A través de los dos multiplexores centrales de 2 entradas, se podrá seleccionar a través de una patilla de control, la señal que recibirán las columnas centrales. Las patillas de control de dichos multiplexores reciben las señales llamadas ACOL1MUX y ACOL2MUX. Estos multiplexores son interruptores CMOS con una resistencia típica del rango de  $2\text{K}\Omega$ . Para realizar la conexión de los multiplexores con los pines existen cuatro drivers analógicos para llevar a la salida valores analógicos

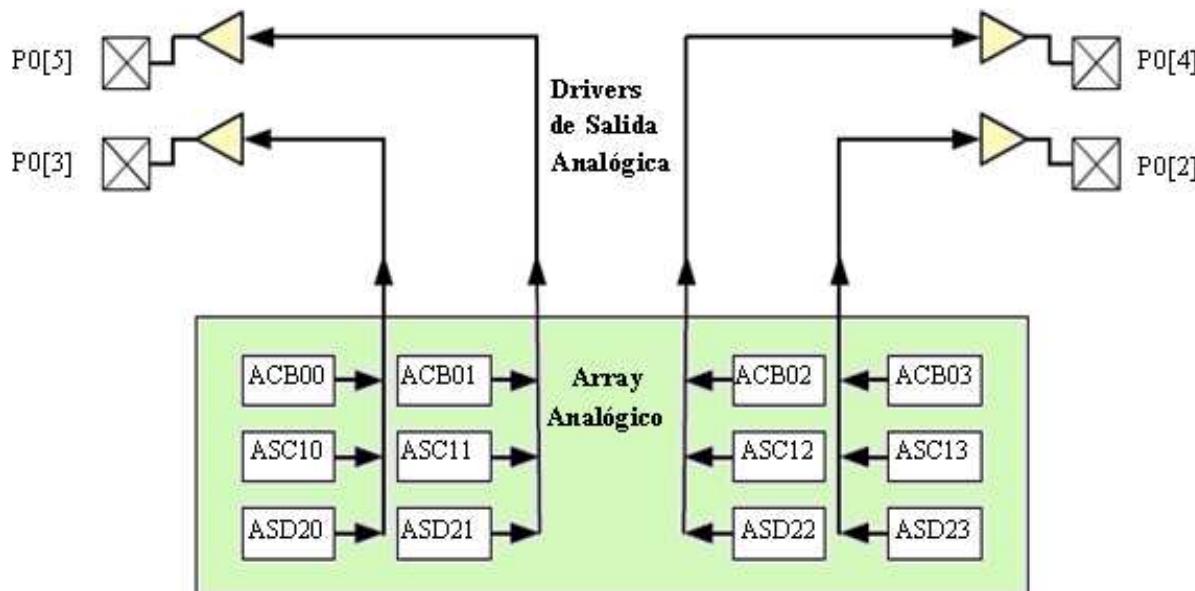

para llevar a la salida valores analógicos en los pines P0[2], P0[3], P0[4] y P0[5]. Cabe decir, que en otros modelos que cuentan con una o dos columnas, las patillas y pines de salida son diferentes. A continuación se muestra un detalle de la conexión de los arrays analógicos con los pines asociados a la salida de señales analógicas.

Fig.3.15 Conexión del array analógico con los pines del CY8C29466

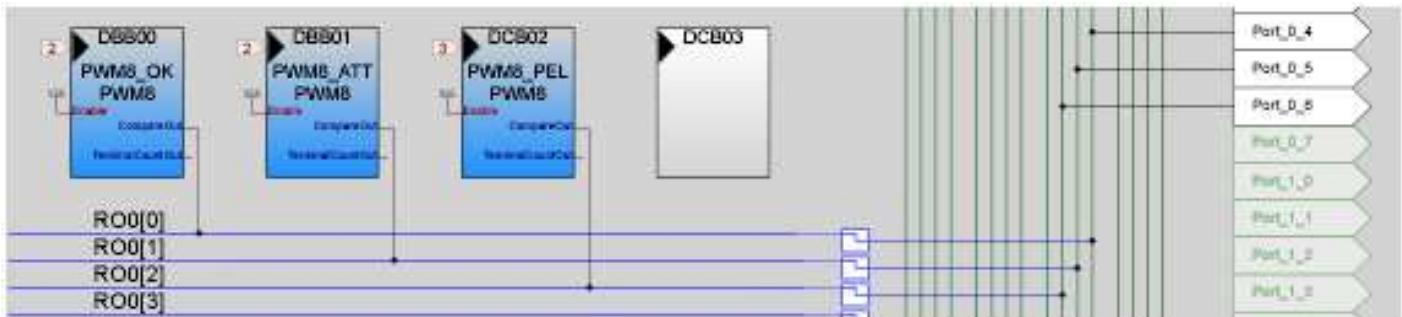

### 3.2.2.3 Sistema Digital

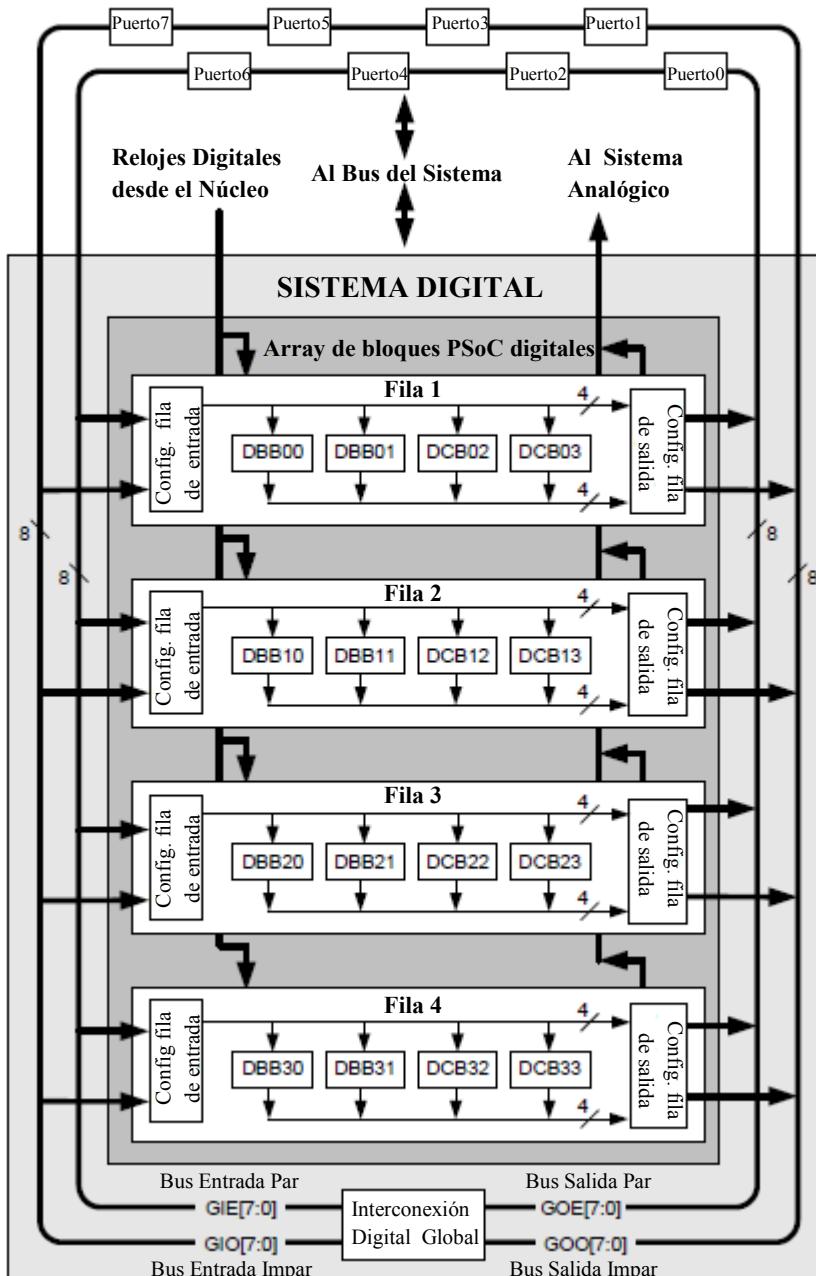

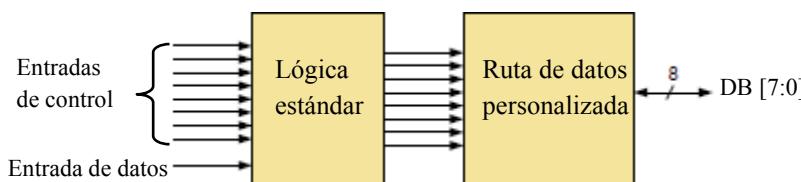

Fig. 3.16 Esquema de bloques del sistema digital del PSoC

Output Even) que permiten la salida de señales desde el núcleo del PSoC a los pines de los puertos.

Dichos bloques digitales pueden conectarse con cualquier GPIO a través de los puertos descritos y éstos tienen la capacidad de conectar cualquier señal con cualquier pin dependiendo de las necesidades del usuario. Por otro lado, existe la posibilidad de utilizar la capacidad de los buses para multiplexar las señales, así como de realizar operaciones lógicas sencillamente.

En la siguiente página se puede observar las conexiones internas que comunican el array de bloques digitales con sus respectivos pines, la cual recibe el nombre de interconexión digital global. Como se puede observar los pines y los puertos están separados dependiendo de si son pares e impares (even y odd). También se pueden observar las conexiones de los relojes digitales.

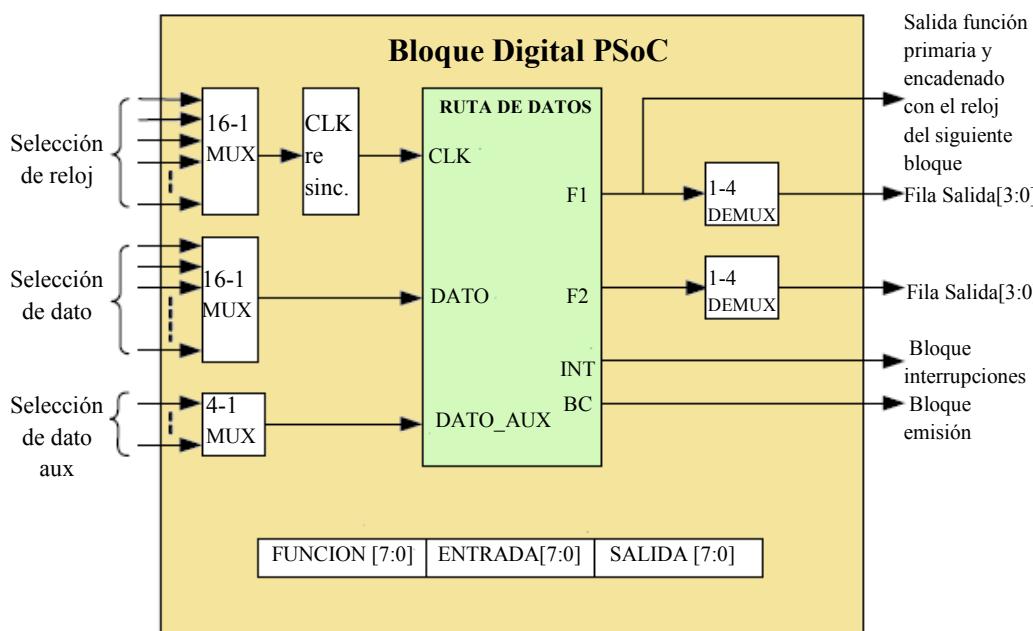

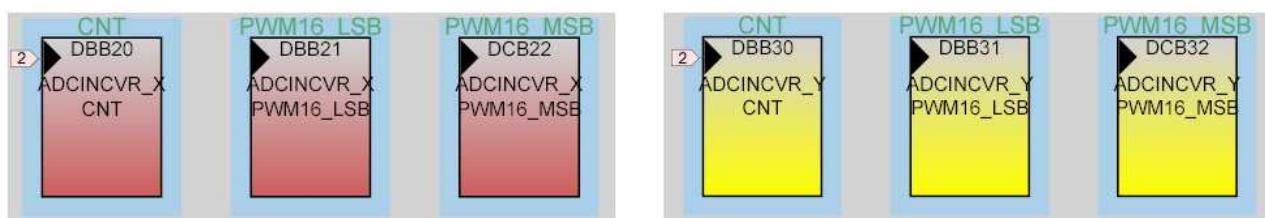

El sistema digital se encarga de realizar todas las operaciones de manipulación y tratamiento de datos digitales (contadores, PWM's, temporizadores, etc.) así como de protocolos de comunicación (SPI, I2C, etc.).

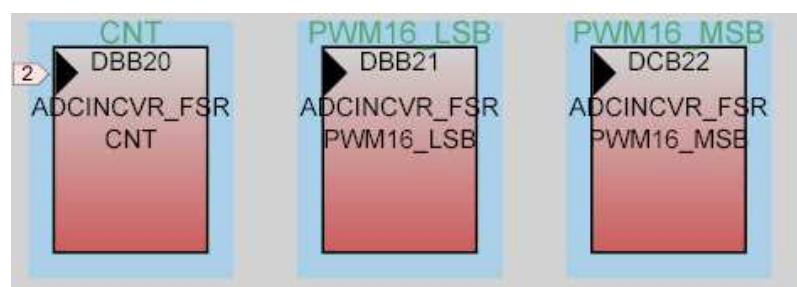

Al igual que el sistema analógico, dependiendo del modelo de PSoC el número de filas en este caso, es variable. En el caso del 29466, el sistema digital cuenta con 4 filas y 4 bloques digitales por fila, con un número total de 16 bloques digitales totalmente configurables. Cada uno de estos bloques es de 8 bits y tienen una alta capacidad de integración, gracias a una excelente comunicación bidireccional entre todos ellos, teniendo la posibilidad de unir bloques para alcanzar un bloque con hasta un máximo de 32bits.

Tanto la entrada como la salida a cada una de las filas de bloques que se han descrito, se pueden configurar: el usuario puede elegir el bus por el que quedarán conectados las entradas y las salidas a los bloques con los pines pares o impares de los puertos. Esta conexión se realiza mediante la Interconexión Digital Global (GDI), que consiste en 4 buses de 8 bits, 2 de entrada (Global Input Odd (impar) y Global Input Even (par)) que permiten la llegada de señales desde los pines del puerto hasta en núcleo del PSoC y 2 de salida (Global Output Odd y Global

### 3.2.2.3.1 Interfaz, array y comunicación del sistema digital

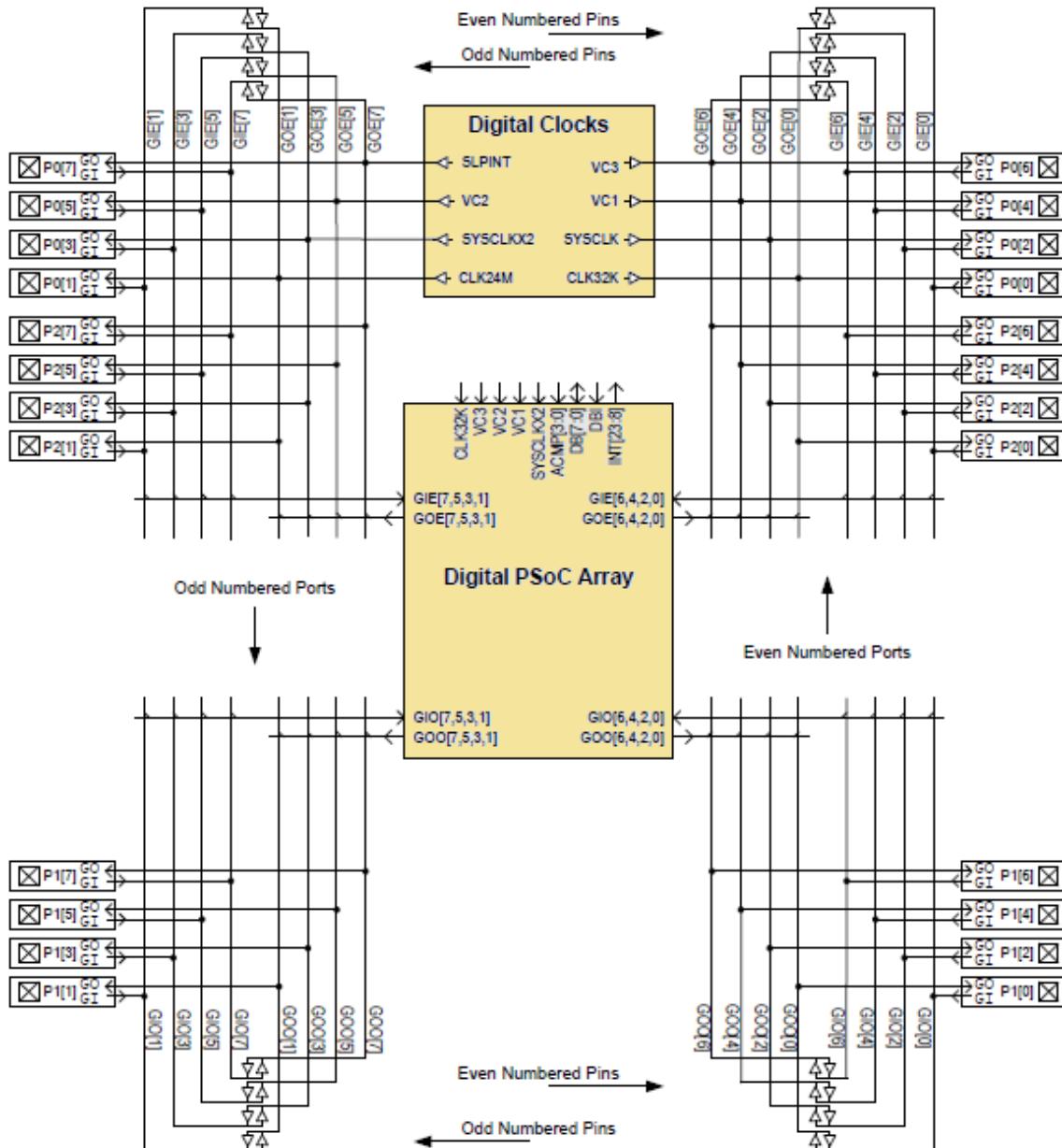

Fig. 3.17 Interconexión Digital Global del CY8C29466

Como se puede ver en el diagrama de conexiones, el PSoC que he utilizado cuenta con 3 puertos de 8 bits de los cuales, dos están conectados a buses globales pares y el restante a un bus global impar. Ahora nos centraremos en el array digital del PSoC y sus componentes internos.

El array está formado por cuatro bloques organizados en filas, estando estas totalmente comunicadas entre sí, permitiendo una configuración total de las funciones desempeñadas por las mismas y siempre a través del usuario.

La interconexión del array digital realiza la conexión entre la interconexión digital global y la interconexión digital de filas que variará según el modelo de PSoC. La imagen que se muestra en la siguiente página muestra el interior del array digital en la que se muestran todas las conexiones entre las cuatro filas de bloques digitales.

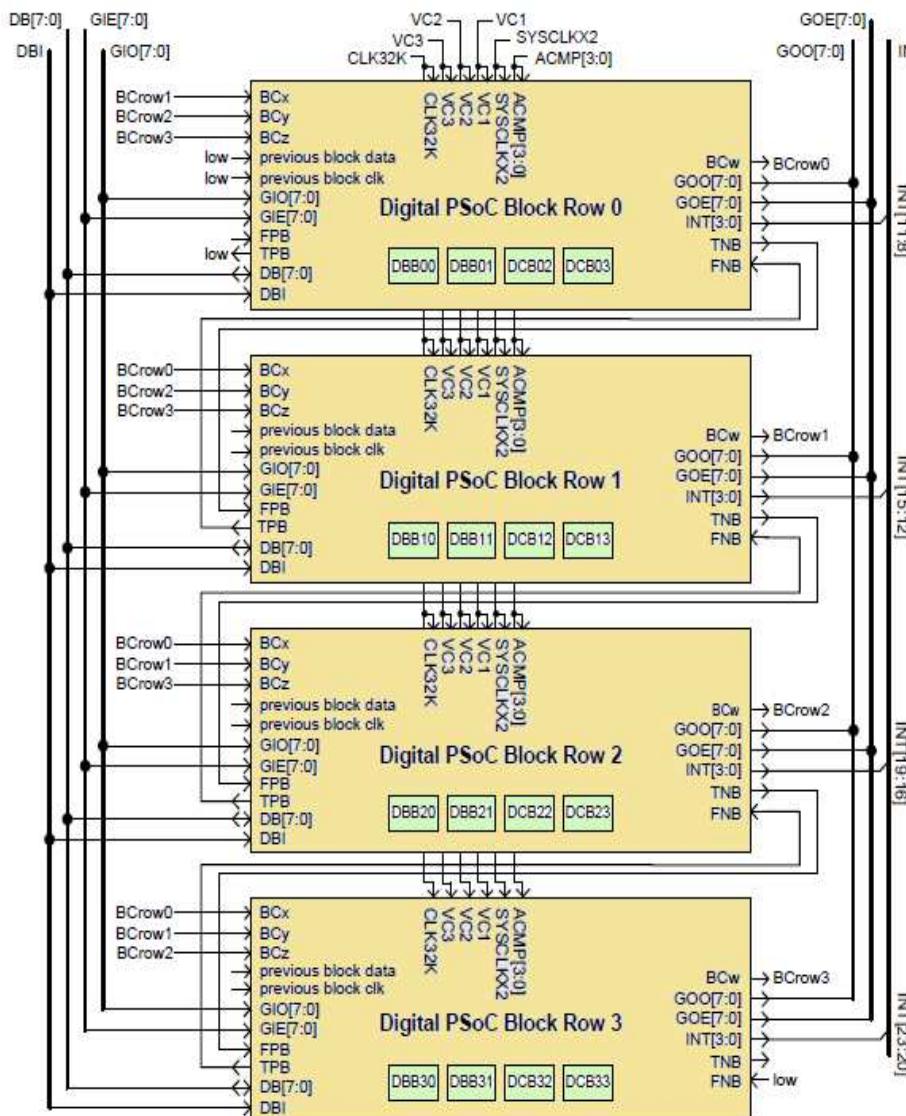

Fig. 3.18 Array de Interconexión Digital del CY8C29466

digital o de manera externa. Si es utilizada de manera externa, será utilizada por otra de las filas del array.

- Las filas de los array forman **cadenas** de bloques de una longitud igual al número de filas multiplicadas por cuatro. Como se puede ver en la imagen, y a excepción del primer bloque de la primera fila y el último de la última fila que no están conectados, todas las filas están interconectadas entre sí.

Profundizando más en el sistema digital y su sistema de interconexión, nos centraremos ahora en uno de los bloques de filas del array digital mostrando su contenido y su correspondiente conexión entre sus componentes internos. La imagen de la siguiente página muestra uno de estos bloques.

Cada una de las cuatro filas de bloques digitales está totalmente interconectada con las demás y con el exterior, recibiendo además las señales de reloj provenientes del núcleo. Es importante destacar que todas las filas tienen idénticas conexiones a las entradas y salidas globales. Para diferenciarlas, y darle a cada fila una dirección única las conexiones se realizan de la siguiente forma:

- Cada fila y los bloques que contienen tienen una **dirección única**.

- Cada uno de dichos bloques tienen un **vector único de interrupción**, teniendo siempre mayor prioridad los bloques que se encuentran en las filas superiores con respecto a las inferiores.

- Cada fila tiene una **red de emisión** particular que puede ser utilizada internamente por un bloque

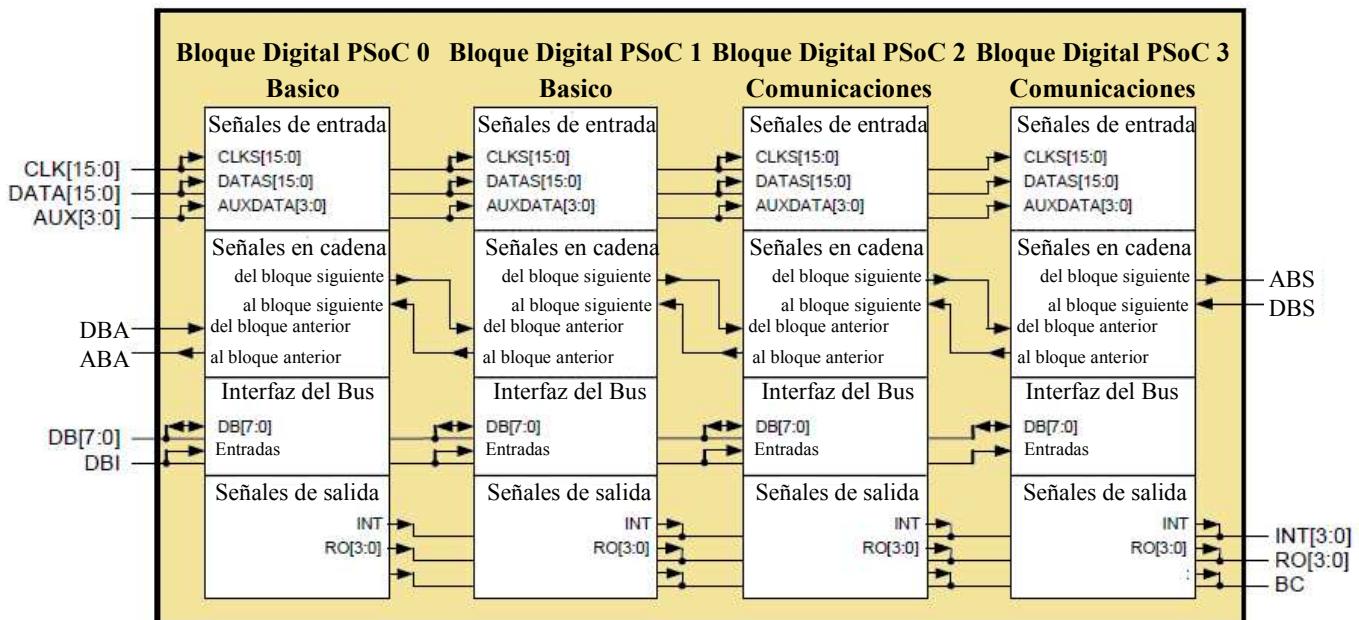

Fig. 3.19 Interconexión Digital de una fila del array del CY8C29466

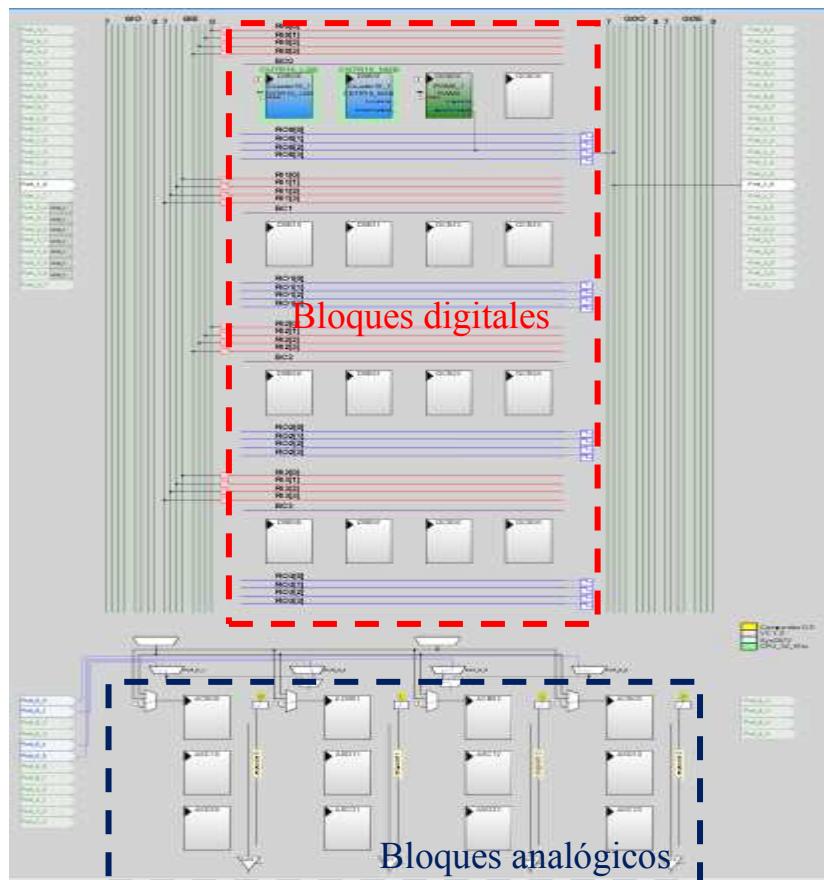

Como se puede ver, cada uno de las filas del array digital, contiene cuatro bloques digitales. Dos de estos bloques serán básicos o DBB (Digital Basic Block) y los otros dos serán de comunicación o DCB (Digital Communication Block). Cada uno de estos cuatro bloques se compone de cuatro “subapartados” ya que cada uno cumple una función determinada. Por un lado, tenemos los bloques que reciben/envían las señales a procesar/procesadas.

Si bien el “bloque” de señales de entrada recibe la señal de reloj, la señal del dato a procesar y un dato auxiliar, el “bloque” de señales de salida enviará al exterior las señales procesadas por el bloque correspondiente. También podemos encontrar otros dos “subapartados” que se encargan de interconectar la fila con las demás y con el bus del sistema. Uno de ellos, se encargará de unir los cuatro bloques digitales de la fila entre si y con los bloques digitales de las demás filas. El otro, se encargará de unir cada uno de los bloques de la fila con el bus del sistema. Para finalizar, mostraré el interior de un bloque digital. Cada uno de

los bloques digitales simples del PSoC podrá ser configurado para desempeñar una de las siguientes cinco funciones: temporizador, contador, modulador de anchura de pulso(PWM), creador de secuencias pseudo aleatorias (PRS) o comprobador de redundancia cíclica(CRC). Los bloques digitales de comunicación incluirán además dos funciones adicionales: maestro o esclavo de comunicación SPI y comunicación UART que será explicada posteriormente.

Fig. 3.20 Bloque digital del CY8C29466

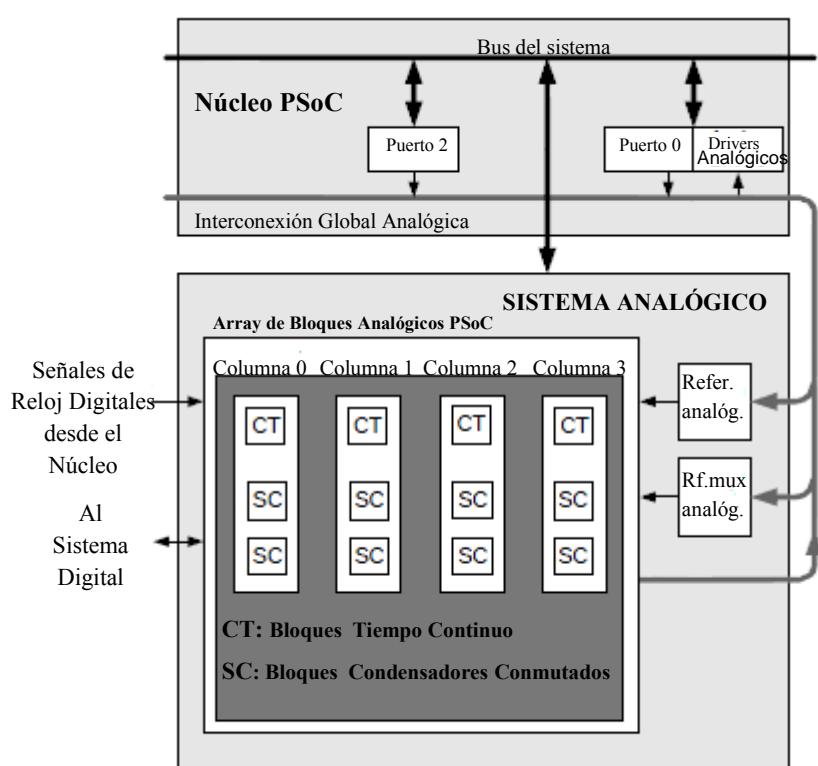

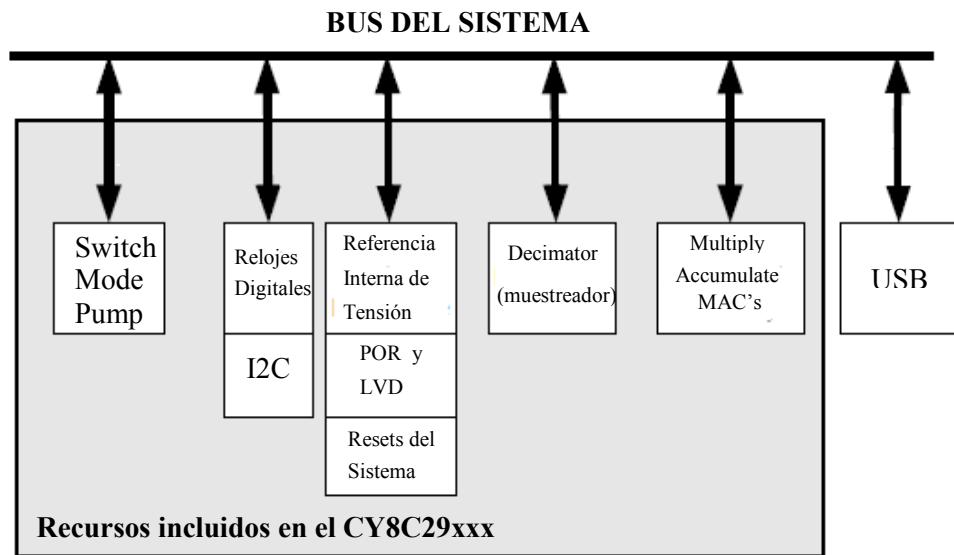

### 3.2.2.4 System Resources (Recursos del sistema)

Fig. 3.21 Recursos del sistema del CY8C29xxx

El PSoC CY8C29466-24PFI cuenta en su arquitectura una serie de funcionalidades, hardware y software, que amplían aun más las capacidades de éste. Esto en la mayoría de los casos, mejora sustancialmente la experiencia del usuario ya que, por ejemplo, le permite reducir todavía más las dimensiones del hardware o simplificar decisiones de diseño mediante software. Dichos recursos (y sus principales utilidades) son los siguientes:

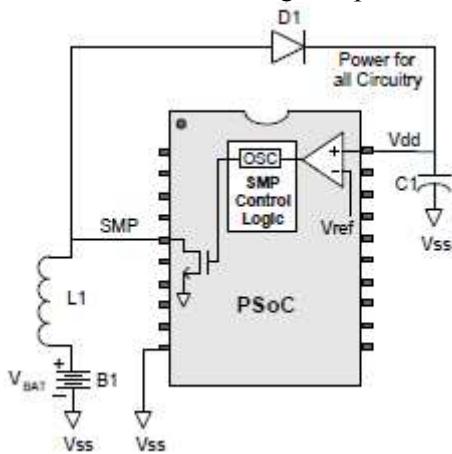

- **Switch Mode Pump (SMP):** Mediante una simple acomodación de hardware externa al PSoC, este circuito integrado permite obtener tensiones de alimentación constantes a partir de una batería.

Fig. 3.22 Hardware necesario para la utilización del SMP

En la fig. 3.22, podemos ver la configuración típica para su correcto funcionamiento: se coloca una bobina (la cual se elegirá con un valor adecuado correspondiente al valor que queremos que suministre a la carga en serie) entre la batería, y la patilla correspondiente al SMP incluyendo un diodo, que se recomienda Schottky (gracias a su rápida velocidad de conmutación y su baja caída de tensión inversa), hacia la patilla de alimentación. Un condensador se debe colocar entre la alimentación y la masa, el cual determinara el rizado y el tiempo de mantenimiento de la tensión de salida.

Este recurso, que es bastante útil cuando se quiere conseguir una alimentación constante del sistema, está relacionado con el Power on Reset (Energía en el re-arranque) y con el Sleep Mode (Modo “dormido”).

- **I<sup>2</sup>C (Inter Integrated Circuit):** Sus siglas provenientes del inglés significan Circuitos Inter-Integrados, y es un bus de comunicación muy utilizado y extendido en la industria por su simplicidad de operación. Requiere de tres hilos para operar correctamente, uno de datos, otro de reloj y otro de referencia(GND) y el PSoC permite una total configuración como maestro / esclavo o receptor / transmisor , utilizando únicamente dos GPIO's. El PSoC interactúa con el bloque mediante los registros de E/S y el usuario realizará mediante software la configuración y utilización del mismo (interrupciones, rutinas, etc.).

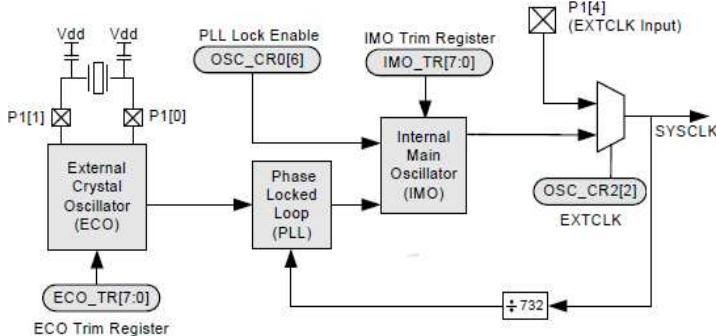

- Relojos Digitales:** A partir de dos relojes internos, el IMO y el ILO (siglas en inglés de Internal Main Oscillator (Oscilador interno principal) y Internal Low Speed Oscillator (Oscilador interno de baja velocidad), respectivamente) el PSoC obtiene todas las fuentes de reloj.

Fig.3.23 Diagrama de operación del IMO

El IMO es un oscilador, que por defecto funcionará a 24MHz y que a partir del cual, se basan la mayoría de las señales de reloj de los circuitos del PSoC. También puede funcionar en modo PLL (del inglés, Phase Locked Loop, Bucle de seguimiento de fase) llevándolo a una referencia de 32KHz de precisión aproximadamente (que se consigue realizando una división de los 24MHz por 732, como se puede ver en el diagrama). Esta operación se

puede realizar fácilmente actuando mediante software sobre los registros de configuración del IMO. Existe además la posibilidad de incorporar un oscilador de cristal externo ECO (del inglés, External Crystal Oscillator) que vendría a remplazar al oscilador interno y que realizaría la misma función del mismo, esto es, servir de base de tiempos para todos los circuitos del PSoC.

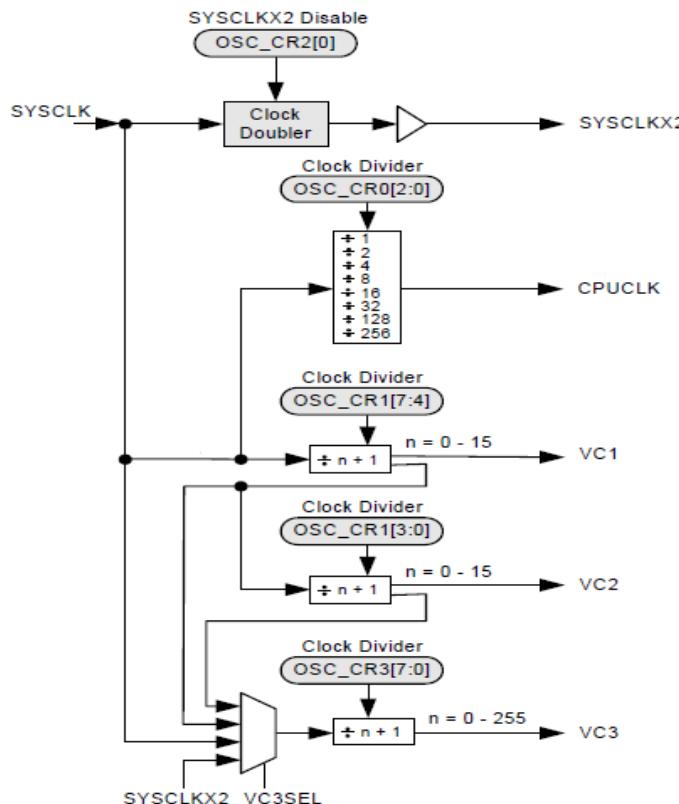

A partir del IMO, o del cristal externo, se obtendrá la red interna de bases de tiempo, la cual recibe el nombre de SYSCLK o reloj del sistema. Esta señal se diversificara en numerosas señales, que describiré brevemente, como se puede ver en el siguiente diagrama de flujo:

Fig.3.24 Diagrama de la red interna de bases de tiempos SYSCLK

A partir de la red de tiempos SYSCLK obtendremos las siguientes señales:

- SYSCLKx2:** El reloj del sistema doblará su frecuencia de trabajo mediante un doblador de reloj.

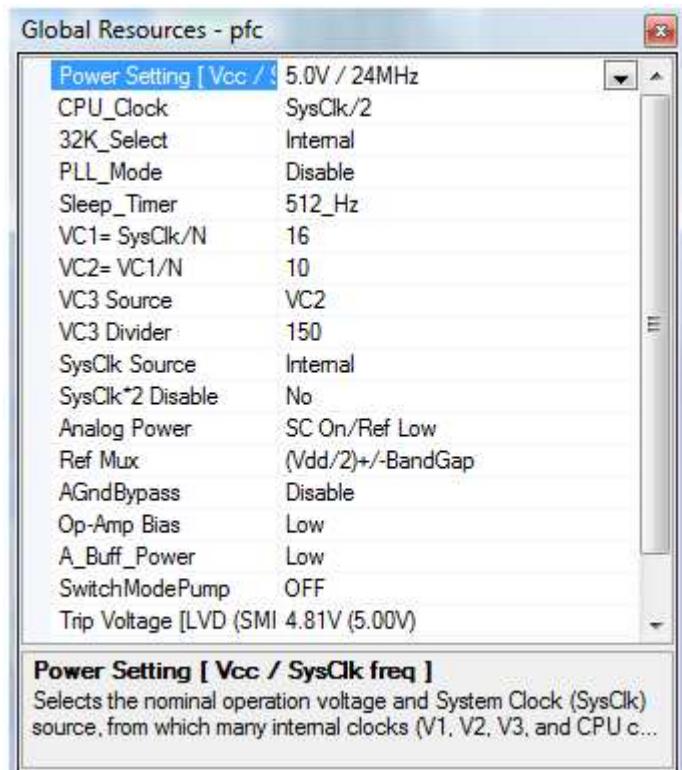

- CPUCLK:** La velocidad de trabajo de la CPU también vendrá derivada de SYSCLK donde el usuario elegirá el factor de división a aplicar entre 1, 2, 4, 8, 16, 32, 64, 128 y 256. Este valor es de frecuencia es fácilmente configurable mediante el software de Cypress (PSoC Designer) eligiendo el valor de un menú desplegable que posteriormente explicaré ampliamente en el apartado 3.3 Software de programación.

- VC1:** Las siglas en inglés significan Variable Clock 1, y es el primero de los 3 relojes variables con los que cuenta el usuario para obtener una gran diversidad de frecuencias de trabajo. Al igual que con CPUCLK, el usuario puede elegir fácilmente el factor de división mediante el software. En este caso el factor de división seleccionable varía entre 1 y 16.

mediante el software. En este caso el factor de división seleccionable varía entre 1 y 16.

- VC2: Deriva de la señal VC1. Igualmente su factor de división es seleccionable por el usuario entre 1 y 16.

- VC3: De igual manera que VC1 y VC2 es una frecuencia determinada por el usuario, con la diferencia de que este puede elegir la fuente de tiempos que recibirá el factor divisorio, pudiendo ser SYSCLK, VC1, VC2 o SYSCLKx2. En este caso el factor divisorio seleccionable oscilará entre 1 y 256

Fig.3.25 Diagrama de operación del ILO

El ILO es un oscilador con una frecuencia nominal de 32 KHz que el PSoC utiliza para las interrupciones de modo Sleep y Wake up y para las operaciones con el perro guardian o Watchdog, siendo esta su función principal. Aunque el usuario también puede utilizar la señal como una fuente de reloj. El ILO, en ausencia de un cristal externo, funcionará constantemente y también puede funcionar como oscilador general del sistema. Entonces, el ILO generará otras 2 señales:

- CLK32K: Esta señal, dependiendo de la inclusión de cristal externo, la proporcionará el ILO o el cristal. Puede funcionar como fuente general de tiempos en detrimento del IMO, modificando un registro.

- SLEEP: A partir de la señal de 32 KHz (independientemente de su origen), el usuario puede elegir el intervalo de tiempo que adquirirá el sistema en caso de caer en suspensión, o modo SLEEP, pudiendo ajustarlo a 4 valores oscilando de 1.95ms a 1s.

La gran variedad de bases de tiempos digitales a obtenibles a partir de dos relojes internos, permiten al usuario realizar un proyecto embebido personalizando totalmente las fuentes de reloj de todos sus componentes, sin la necesidad de incluir cristales externos o hardware adicional.

Esto supone un gran ahorro tanto de componentes así como de tiempo y tamaño de diseño, facilitando enormemente la labor del programador/usuario.

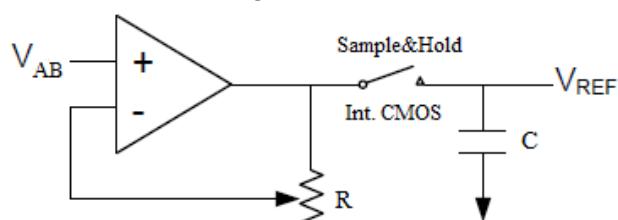

- **Referencia interna de tensión:** El PSoC cuenta con una referencia interna de que resulta de dos componentes, un generador de tensión de banda prohibida (bandgap) que genera 1.20V y del siguiente circuito: un amplificador que regula la ganancia de la tensión del generador a 1.30V. La conexión AO y C se realiza mediante un interruptor CMOS lo que permite al sistema utilizar la tensión de referencia Vref mientras el circuito de referencia es apagado. La tensión temperatura ambiente es de unos 1.30V. Además, de este bloque se obtiene una tensión proporcional a la temperatura para la medición de la misma.

Fig.3.26 Circuito generador de Vref

- **Power On Reset y Low Voltage Detect (POR y LVD):** Estos dos recursos del sistema sirven como protección del sistema en casos de bajo voltaje.

El POR realiza mediciones la tensión de alimentación Vdd y a la vez mantiene el sistema en reset hasta que la misma adquiere valores aceptables de operación, evitando de esta manera que el sistema arranque de forma inesperada o con valores insuficientes de tensión.

De igual manera, el LVD (del inglés Detección de Bajo Voltaje) realiza mediciones de Vdd pero a diferencia del POR, este proporciona una interrupción cuando dicha tensión baja por debajo de determinado valor. Puede resultar muy útil a la hora de realizar operaciones previas a la pérdida total de energía o para la ejecución de subrutinas en determinados valores críticos de Vdd.

- **Resets del sistema:** Existen diferentes formas de que un reset se produzca en el PSoC dependiendo de que lo desencadena. Estos son principalmente los siguientes:

1. *Reset en el arranque (Power on Reset):* Este reset suele darse cuando hay bajo suministro de tensión y puede ser ocasionado por múltiples fuentes.

2. *Reset externo:* Este reset lo producirá el usuario introduciendo un nivel alto en el pin XRES del PSoC, en el caso del CY82C9466 es el pin 19.

3. *Reset del Watchdog o perro guardián:* Es un reset opcional configurable por el usuario, para evitar normalmente bucles infinitos.

4. *Reset interno:* Puede darse durante la secuencia de arranque si el código SROM determina que la lectura de la Flash no es valida

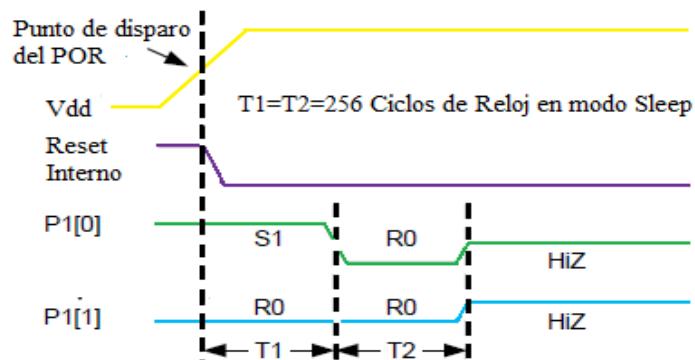

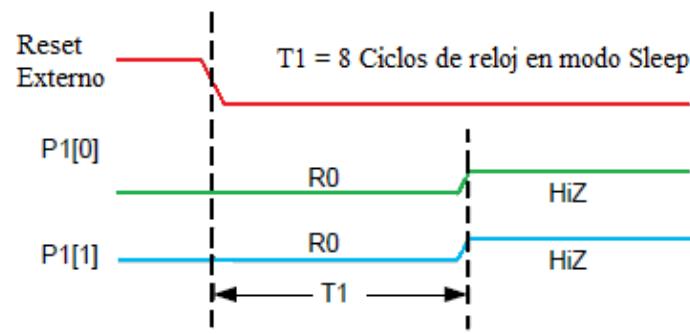

En el caso de que se produzca un reset en el arranque o un reset externo producirá la conmutación de los pines de prop. gral. (GPIO's), P1 [0] y P1 [1], de la siguiente forma:

En el caso del POR, el reset interno ocasiona, como podemos ver en el gráfico, un nivel alto a P1 [0] durante 256 ciclos de reloj en modo sleep (T1) y un nivel bajo a P1 [1]. Tras ese número de ciclos, P1 [0] también recibirá un nivel bajo y ambos puertos permanecerán así durante otros 256 ciclos. Tras ese periodo (T2) se producirá una transición mediante la cual ambos pines pasan a comportarse como alta impedancia y comenzará la operación normal de la CPU.

Si en cambio el reset es producido por un reset externo, esto es, cuando el usuario introduce un nivel alto en el pin XRES (19), ambos GPIO's toman un valor bajo y continuaran así durante 8 ciclos de reloj en modo Sleep. Tras ese periodo y tras una transición ambos pines tomaran un estado de alta impedancia y comenzara la operación normal de la CPU, como en el caso anteriormente descrito.

Fig. 3.27 Diagrama de funcionamiento del reset en el arranque y sus consecuencias sobre los GPIO's P1 [0] y P1 [1]

Fig. 3.28 Diagrama de funcionamiento del reset en el arranque y sus consecuencias sobre los GPIO's P1 [0] y P1 [1]

- **Decimator (Muestreador):** El PSoC cuenta con un pequeño hardware que asistirá en procesos de señales digitales. Puede ser de tipo 1 o tipo 2, pero en el caso que nos concierne, el CY8C29466, solo cuenta con el tipo 2. Este recurso del sistema puede ser usado principalmente para conversiones AD como por ejemplo la conversión delta sigma o la conversión AD incremental. En la siguiente imagen se puede ver la arquitectura del bloque:

Fig. 3.29 Arquitectura del muestreador tipo 2 incluido en el CY8C29466

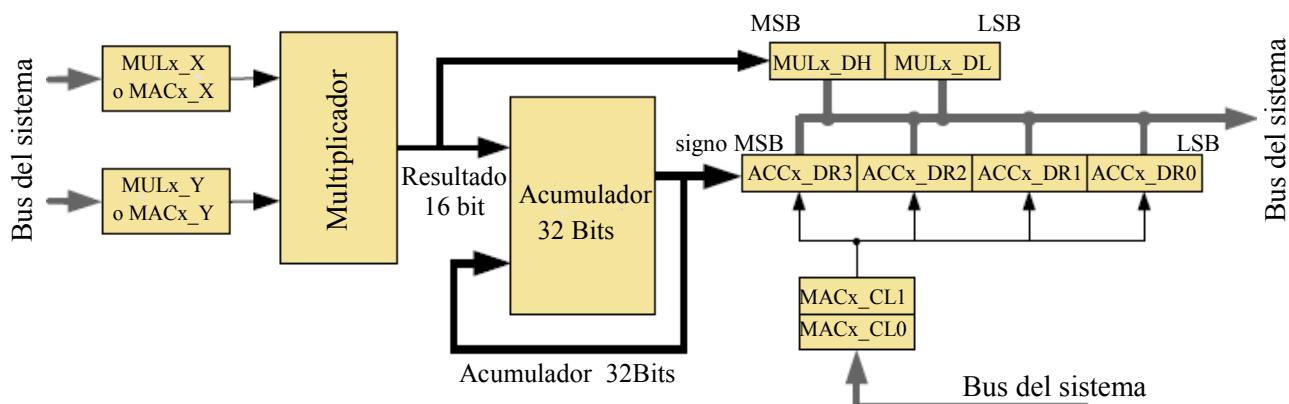

- **Multiply accumulate (MAC):** Este bloque del sistema corresponde con un multiplicador rápido de 8 bits con una acumulación de 32 bits. Como única interfaz, este recurso basado en registros es el bus del sistema, por lo que no se requieren fuentes de reloj especiales para que sea utilizado por bloques analógicos o digitales del PSoC. En el caso que nos concierne, el CY8C29466 cuenta con dos bloques MAC independientes entre sí. A continuación, detallo su diagrama de bloques y su funcionamiento:

Fig. 3.30 Diagrama de bloques del multiplicador rápido con acumulador de 32 bits del CY8C29466

El usuario podrá elegir entre una multiplicación simple o de una multiplicación con acumulación dependiendo de los registros utilizados en dicha operación. Para una multiplicación simple, como se puede observar en el diagrama, el MAC acepta dos valores de 8 bits (con o sin signo) llamados MULx\_X y MULx\_Y. El resultado de dicha multiplicación aparecerá instantáneamente en los registros MULx\_DH y MULx\_DL cuyo valor permanecerá tras un re-arranque o tras un reset ocasionado por el usuario.

En el caso de una multiplicación con acumulación, la operación comenzará en el momento en el que se escriba un valor en los registros MACx\_X y MACx\_Y, guardándose el resultado en los registros ACCx\_DR3, ACCx\_DR2, ACCx\_DR1 y ACCx\_DR0. En este caso, el valor de la multiplicación también se guardará en un acumulador como un valor de 32 bits con signo. En caso de querer borrar los registros que almacenan el resultado de multiplicaciones acumuladas, bastará con escribir en cualquiera de los registros MACx\_CL 1 o MACx\_CL 0.

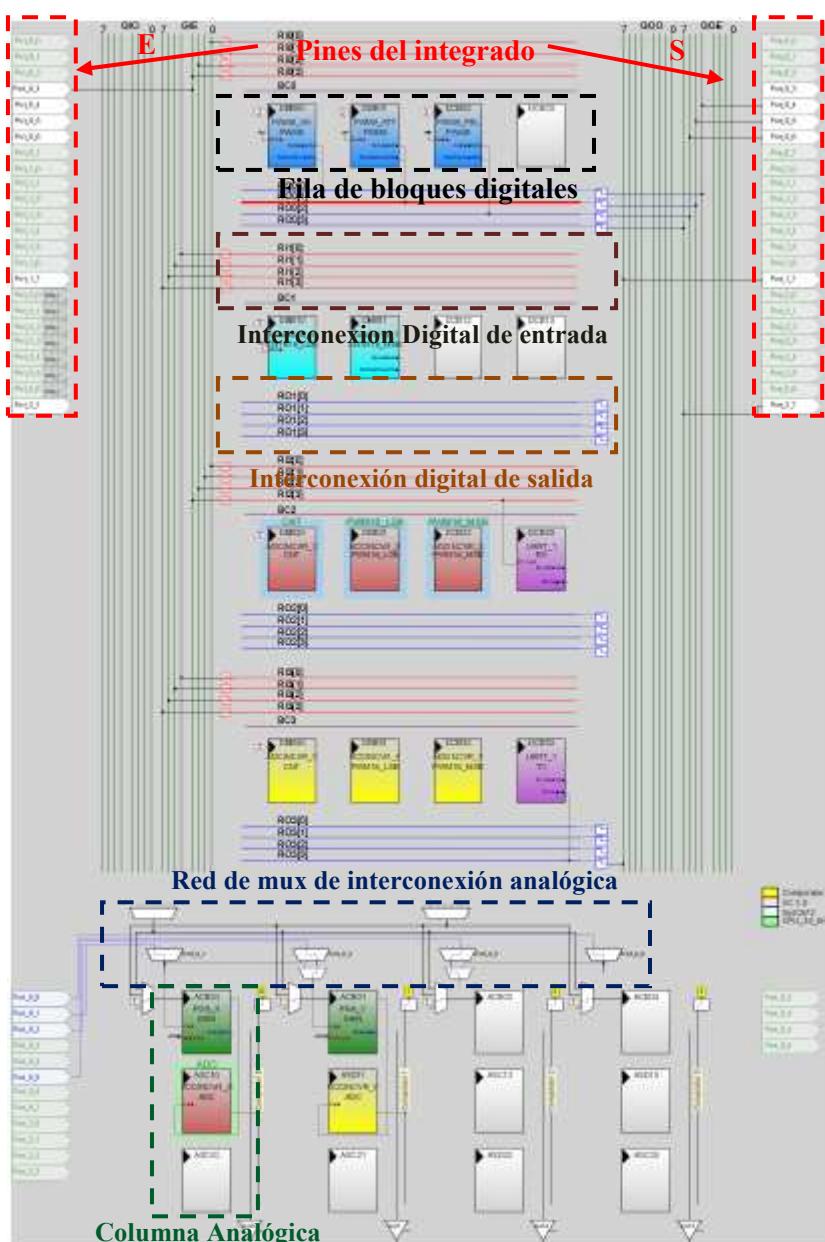

### 3.2.3 Entradas/Salidas - General Purpose Input Output(GPIO)

En lo concerniente a la comunicación, el PSoC cuenta con los GPIO, siglas en inglés de General Purpose Input Output (entradas/salidas de propósito general), que son los responsables de unir el núcleo del microprocesador con el exterior. Estos ofrecen una gran variedad de configuraciones para trabajar tanto con señales digitales como analógicas.

Cada puerto de entradas/salidas (nombrados como IO (input/output) a partir de ahora para mayor comodidad) contará con 8 bits y cada uno de estos puertos contará con 8 GPIO's idénticos teniendo cada uno de estos una identificación única. En nuestro caso, el CY8C29466 contará con 3 puertos llamados P[0], P[1] y P[2]. El diagrama de bloques de un GPIO es como el que se muestra a continuación:

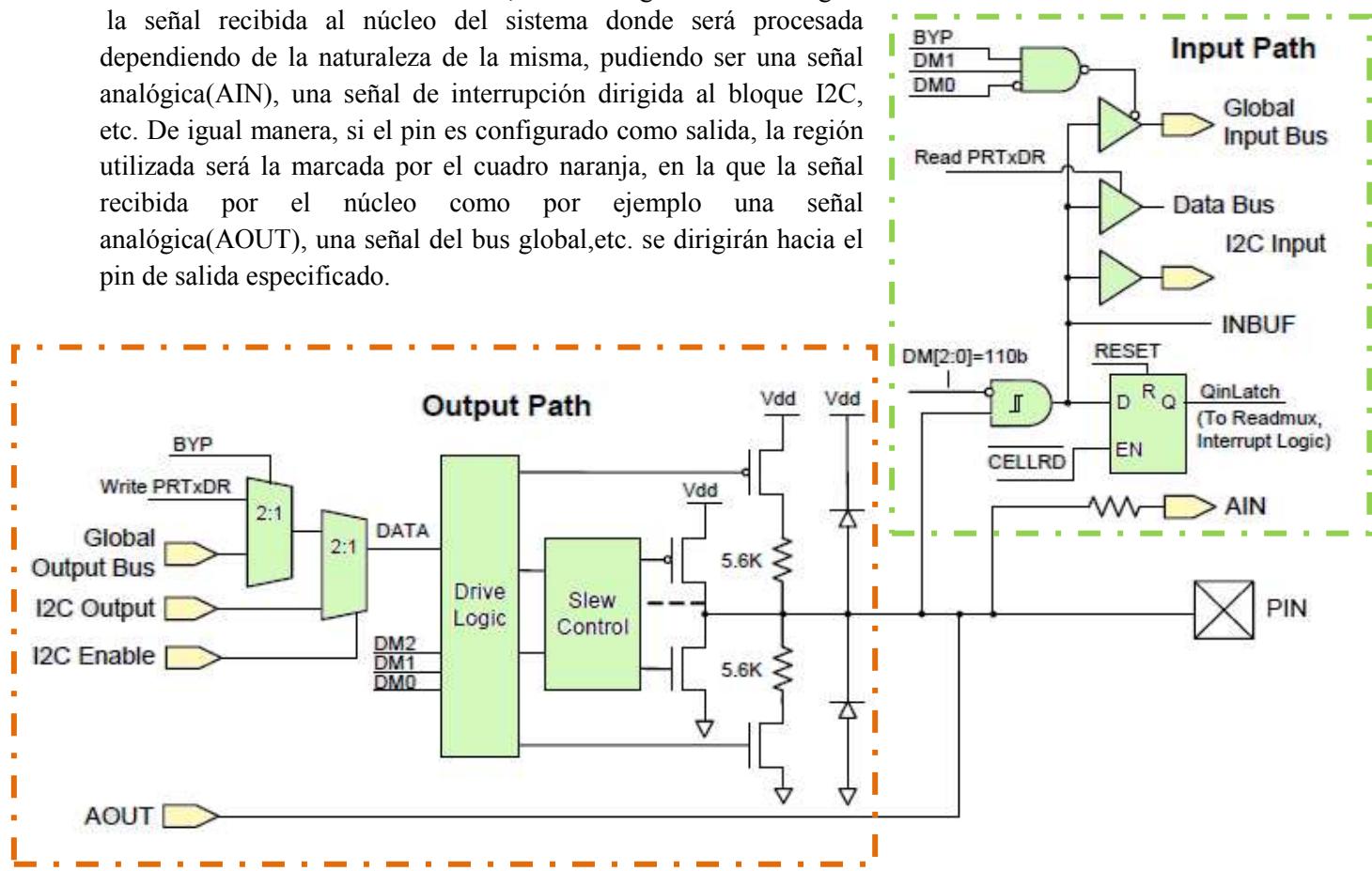

Dependiendo de la elección de una de las configuraciones arriba mencionadas, el GPIO hará uso de una u otra parte del circuito que contiene. Por un lado, si el pin es configurado como entrada, la región utilizada será la marcada con un cuadro verde, la cual dirigirá la señal dirigirán la señal recibida al núcleo del sistema donde será procesada dependiendo de la naturaleza de la misma, pudiendo ser una señal analógica(AIN), una señal de interrupción dirigida al bloque I2C, etc. De igual manera, si el pin es configurado como salida, la región utilizada será la marcada por el cuadro naranja, en la que la señal recibida por el núcleo como por ejemplo una señal analógica(AOUT), una señal del bus global,etc. se dirigirán hacia el pin de salida especificado.

Fig. 3.31 Diagrama de bloques de un GPIO

Cada uno de estos GPIO's podrá utilizarse de una forma diversa dependiendo de la función que vaya a desempeñar:

- IO Globales: entradas/salidas para bloques digitales del PSoC

- IO Analógicas: entradas/salidas para bloques analógicos del PSoC

- IO Digitales: entradas/salidas controladas por software

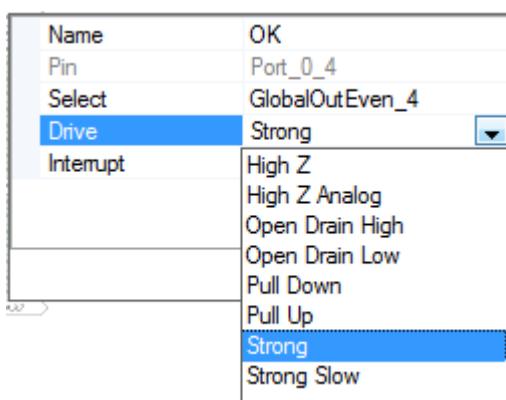

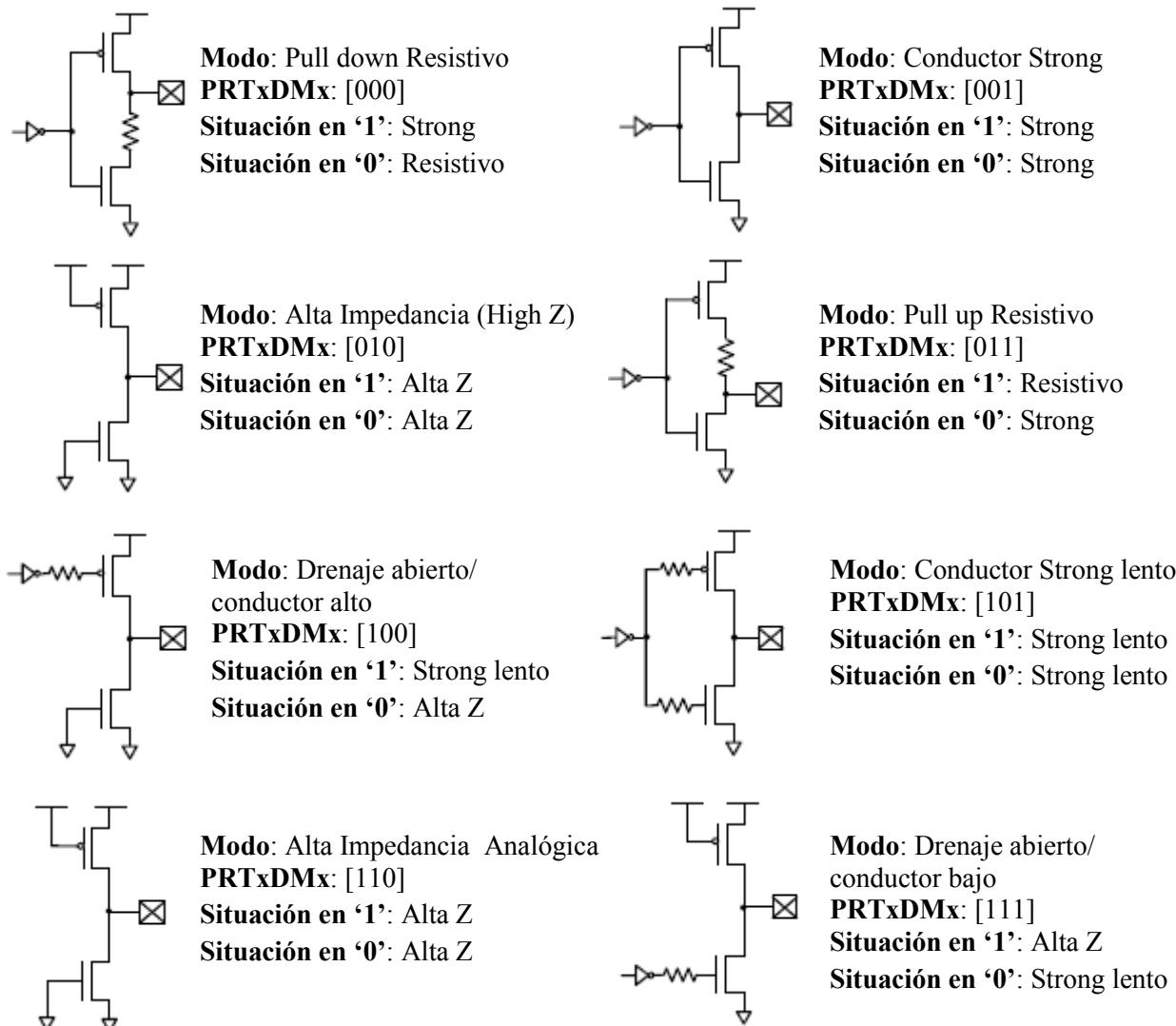

Además, cada GPIO adoptará mediante SW un modo de conducción de cada pin dependiendo de la naturaleza de la señal que vaya a pasar por el mismo. Esta operación se realiza fácilmente mediante el PSoC Designer y básicamente se basa en la modificación de un registro llamado PRTxDMx que se realizará de forma automática a través de su interfaz gráfica. Dichos modos de conducción, la configuración del registro PRTxDMx y la situación del pin en situación de ‘0’ y de ‘1’ se muestran a continuación:

Fig. 3.32 Menú desplegable de un GPIO en PSoC Designer IDE

A la izquierda se muestra una captura de pantalla del PSoC Designer, el software de Cypress para la configuración del mismo. Como se puede ver, es un menú desplegable de configuración de un GPIO, concretamente el puerto P0 [4]. En el tema que nos concierne, para elegir el modo de conducción no hace falta recurrir al registro PRTxDRx para modificar dicha modalidad, sino que se puede realizar fácilmente a través de este menú. En el apartado concerniente al SW de Cypress realizaré una explicación exhaustiva de todas las configuraciones posibles de cada GPIO.

### 3.2.3.1 E/S Globales

Los puertos GPIO se pueden configurar para ser usadas para interconectar señales a/desde los bloques digitales como entradas/salidas globales. Desactivada por defecto, requiere de la modificación de dos parámetros: el bit de selección de puerto global a través de PRTxGS del puerto que deseemos debe recibir un nivel alto.

Dependiendo de si queremos que sea una entrada o una salida deberemos modificar el modo de conducción. Para el caso de salida usaremos el de alta impedancia, y para el caso de salida cualquiera de los otros tipos que no sean de alta impedancia.

### 3.2.3.2 E/S Digital

Como ya he explicado en el apartado 3.2.4 Sistema digital, una de las principales operaciones de los GPIO's digitales es de enviar y recibir información desde el núcleo del PSoC hacia el exterior. Esto se lleva a cabo a través del registro de datos del puerto: PRTxDR.

De esta forma, el microprocesador del núcleo puede conocer el estado de un pin leyendo el estado del registro PRTxDR, transformando después el voltaje actual del pin en un valor lógico y devolviéndolo al microprocesador. Algunos ejemplos simples de instrucciones de lectura, escritura y modificación de este puerto son las operaciones lógicas NOT, OR, AND, y XOR.

Considerando la x de PRTxDR el numero de puerto que será sometido a modificación, es fácil cambiar el valor de un bit de un puerto. Por ejemplo, si queremos modificar cualquiera de los valores de un bit del puerto 1, bastará con lo siguiente:  $PRT1DR|=0x10$ . De esta manera, accederemos al byte del puerto 1, pudiendo modificar cualquiera de sus 8 bits (en hexadecimal). En este caso, se habrá modificado a '1' el bit 4 del puerto 1 mediante la operación OR.

### 3.2.3.3 E/S analógicas

Las señales de naturaleza analógica entrarán en el núcleo del PSoC a través de los pines del integrado por la patilla AOUT del bloque del GPIO como puede verse en la figura x.x. Normalmente para la recepción de señales analógicas, el modo elegido será de Alta Impedancia Analógica ya que este modo desactiva el inversor Schmitt. En lo referente a las salidas analógicas, están explicadas detalladamente en el apartado 3.2.3.

### 3.3 Hardware y Software de diseño/programación PSoC

Para realizar la programación tanto del software como del hardware del PSoC, Cypress cuenta con una herramienta útil y sencilla para el desarrollo de aplicaciones basadas en sistemas embebidos. Por un lado, para conocer las capacidades del PSoC conviene adquirir en un principio la herramienta de evaluación CY3210, hardware que permite conocer y testear las capacidades del PSoC y que a la vez ayuda al usuario a familiarizarse con el software de programación, el PSoC Designer. Ambas herramientas de desarrollo serán explicadas ampliamente en los siguientes apartados.

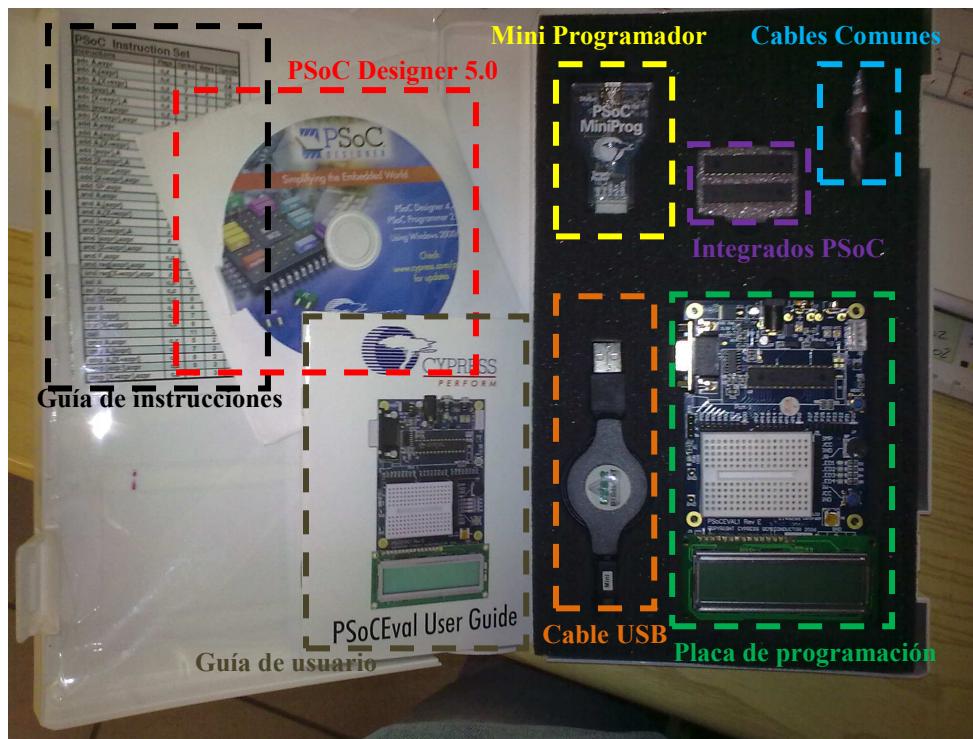

#### 3.3.1 CY3210-PSoC EVAL 1

El CY3210-PSoC EVAL 1 es una placa de evaluación que permite conocer las características y capacidades de los productos de Cypress. Antes de comenzar con la realización de mi proyecto, he debido conocer y aprender a utilizar la herramienta en la que se basaría mi sistema de control. El contenido de este kit de evaluación, que cuenta con todo lo necesario para empezar a desarrollar desde cero proyectos basados en PSoC, se enumera a continuación:

- Placa de evaluación PSoC

- Mini programador PSoC

- 2 integrados PSoC: CY8C29466-24PXI y CY8C27443-24PXI

- Cable USB A-miniB

- Cable común de cobre

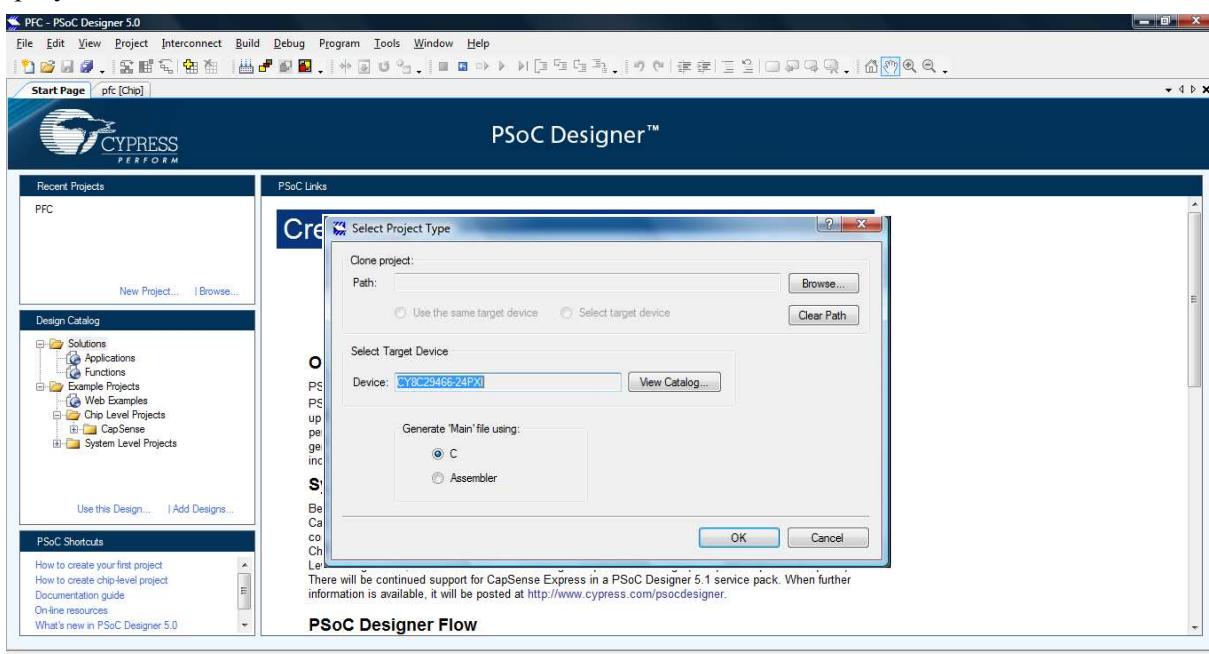

- Software de programación PSoC Designer 5.0

- Guía de usuario de la placa de evaluación

- Guía de instrucciones en ensamblador para el PSoC

Fig.3.33 Contenido del kit CY3210-PSoC EVAL 1 de Cypress

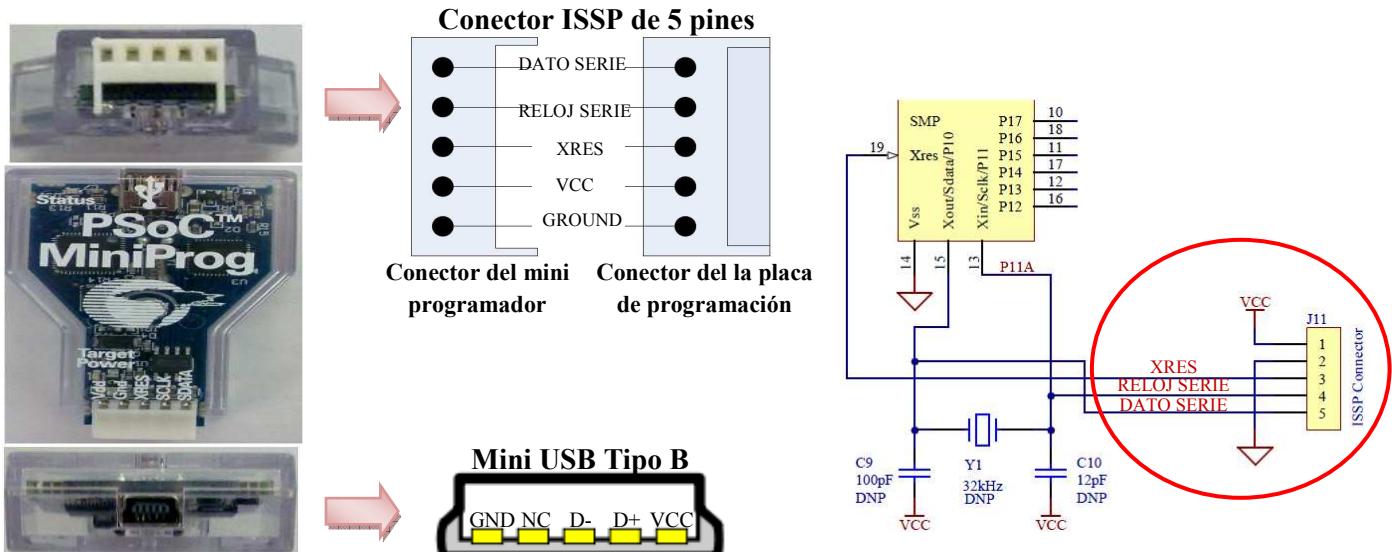

Lo fundamental de este kit es la placa de programación, el software PSoC Designer, los integrados PSoC y el mini programador los cuales explicaré más detalladamente. La placa de programación cuenta con todo tipo de utilidades para experimentar con el PSoC mientras que el mini programador nos será útil para, como su nombre indica, programar el integrado PSoC con el código desarrollado en el PSoC Designer, que será explicado en profundidad posteriormente.

Los otros componentes incluidos en el kit, como la guía de usuario y la guía de instrucciones, nos facilitaran los primeros pasos con esta herramienta. El cable USB servirá para conectar el programador al PC y los cables de cobre serán útiles para realizar conexiones simples en la placa de programación. A continuación se detalla el contenido de la placa de programación.

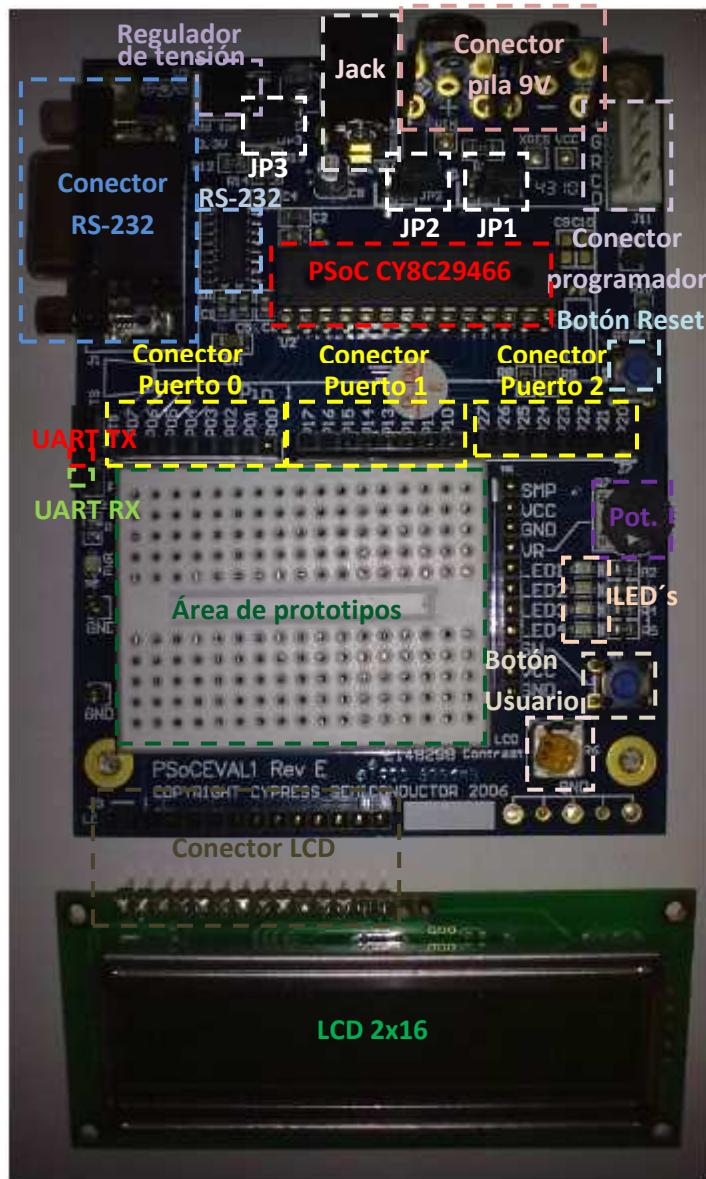

### 3.3.1.1 Placa de programación y mini programador

Fig. 3.34 Placa de programación del kit CY-3210

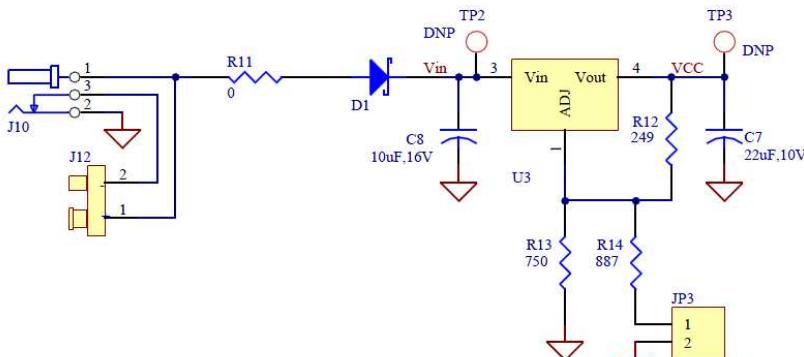

Fig. 3.35. Esquemático del sistema de alimentación del CY-3210 PSoC EVAL1

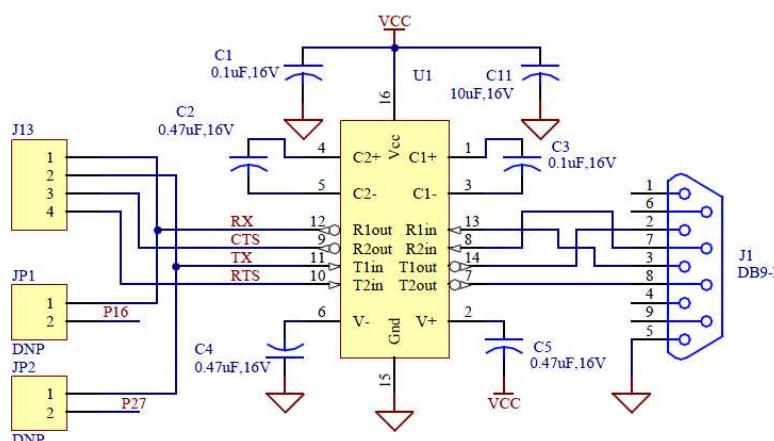

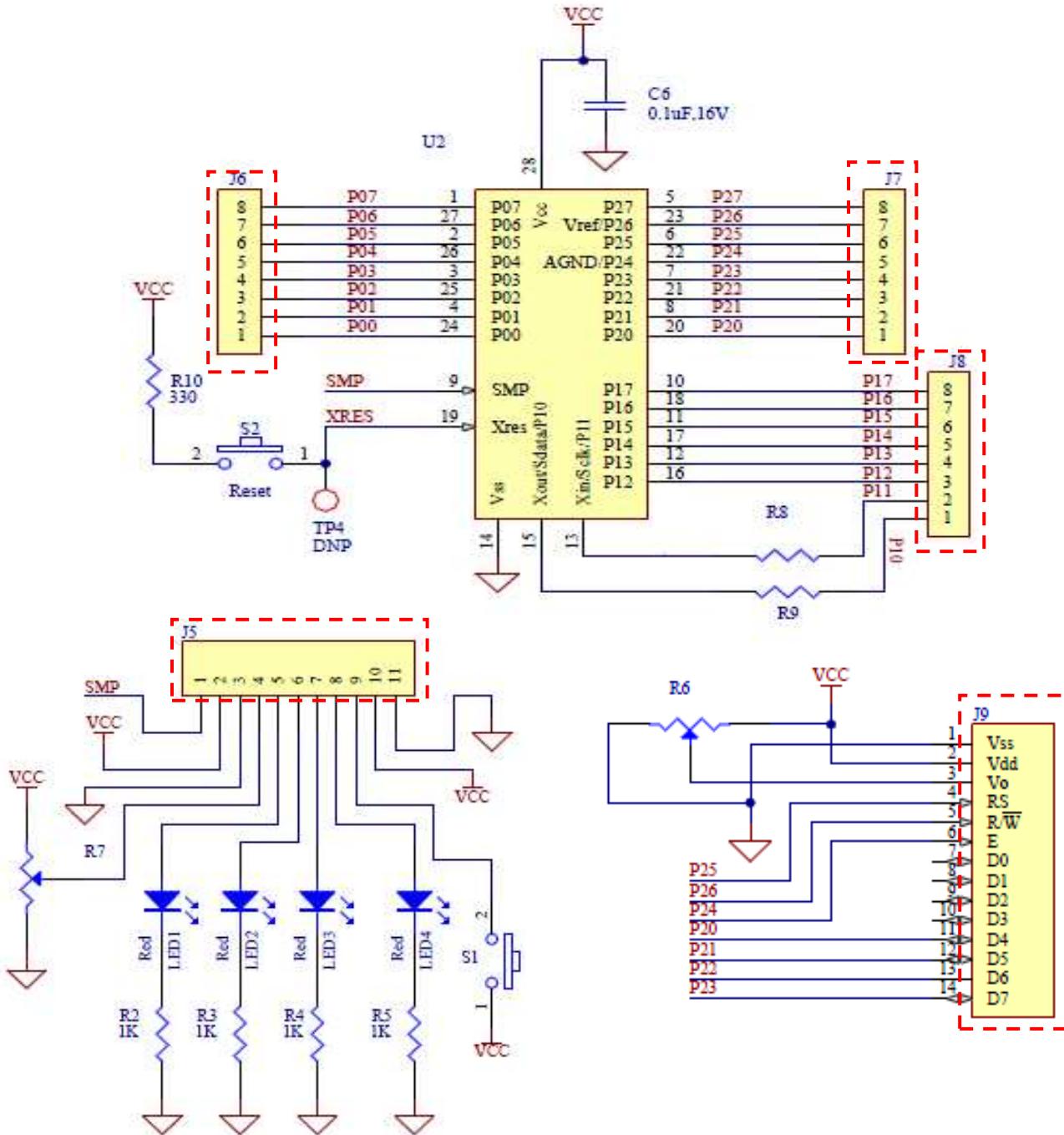

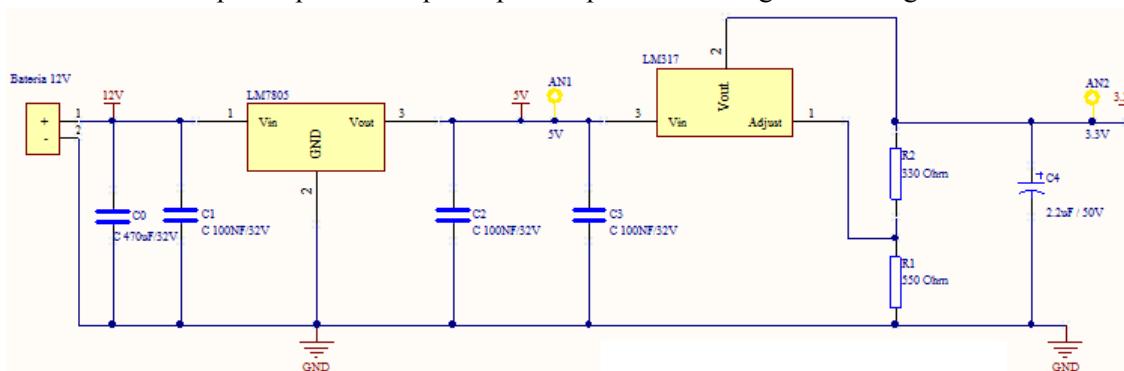

La placa de programación permite experimentar con el dispositivo PSoC como parte del aprendizaje previo a la creación de un proyecto basado en el mismo. Esta se puede dividir en cinco subpartes dependiendo de la función que representa cada una de ellas en el conjunto de la misma. Estas partes son las siguientes: Sistema de alimentación, interfaz de programación, interfaz del RS-232, área de prototipos y área de visualización. Cada una de estas partes realiza una función fundamental para el desarrollo de aplicaciones en la placa de programación y cada una de estas partes están formadas por los siguientes componentes:

- Sistema de alimentación (zona superior central): Cuenta con un sistema de alimentación realmente versátil ya que cuenta con varias posibilidades. Lo más común es alimentar la placa con los 5V que le proporciona el mini programador mediante USB o bien mediante una pila de 9V gracias al zócalo que incorpora.

Además existe la posibilidad de alimentarla mediante un transformador de 9V a 12V DC conectado al Jack que incorpora. Mediante el regulador de tensión incorporado, se convertirá la tensión de alimentación (si procede) en 3.3V /5V dependiendo de las necesidades del proyecto a realizar.

Por otro lado, no es posible usar más de una fuente de alimentación al mismo tiempo o si es menor a 7V o superior a 12V.

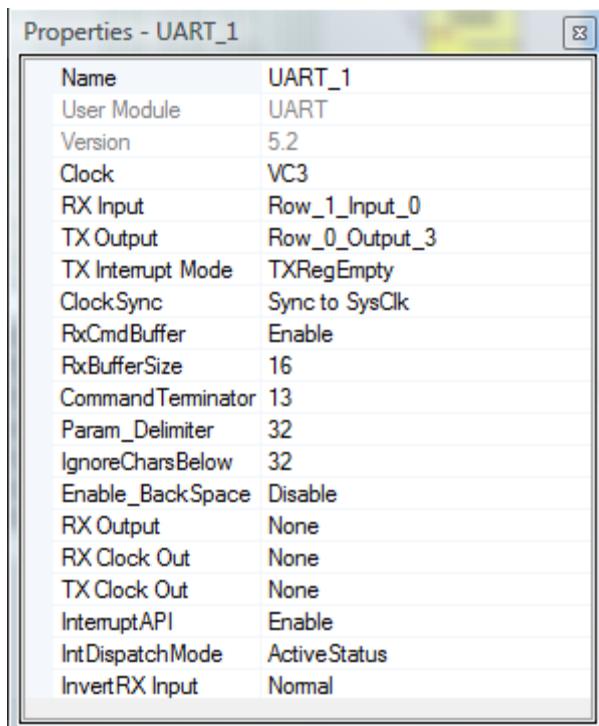

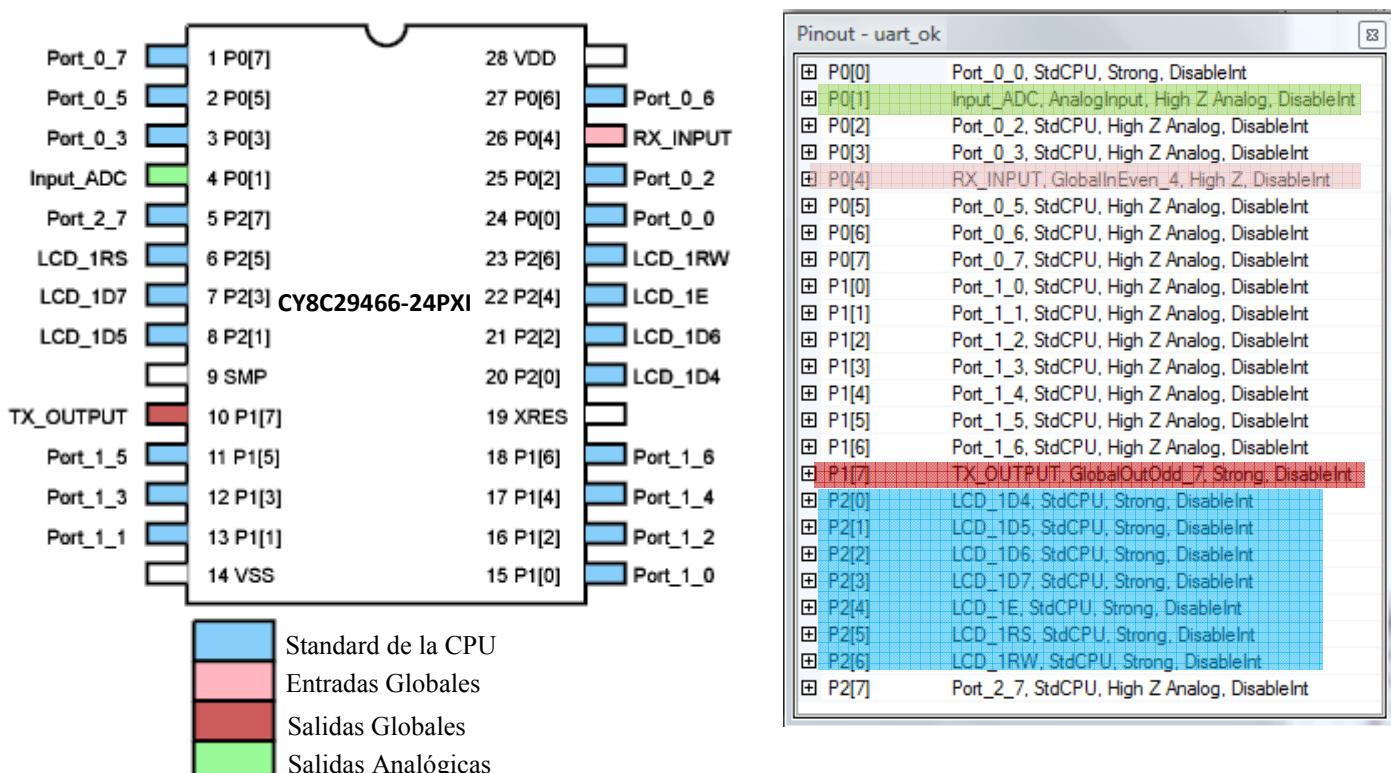

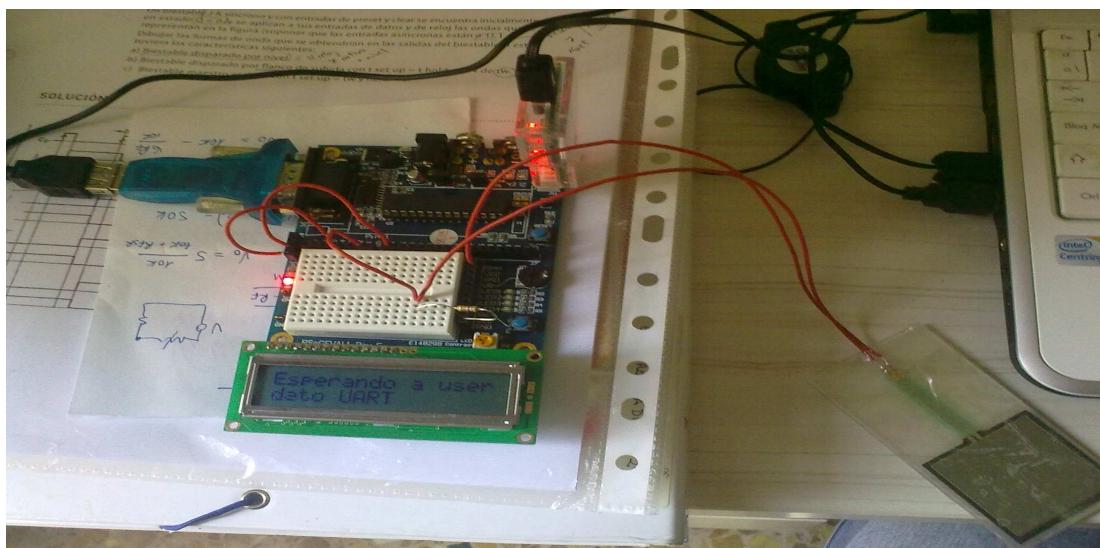

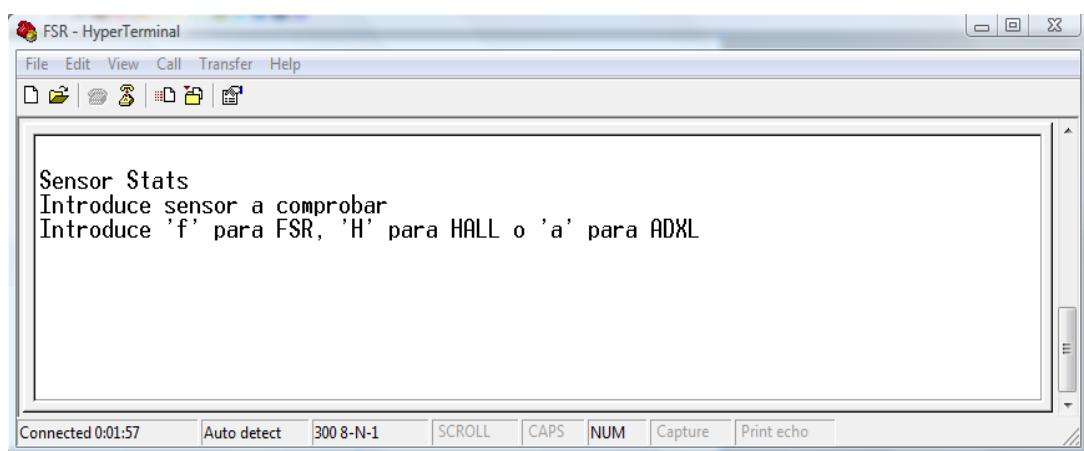

También cuenta con 3 jumpers para habilitar/deshabilitar funciones: el jumper 1 y 2 tienen relación con el interfaz del RS-232 y se explicara su función a continuación mientras que el jumper 3, como se puede ver en el esquemático de la derecha, determinará el funcionamiento del regulador de tensión a 3.3V (conectado) o 5V (desconectado).