# A Robust 10-Gb/s Duobinary Transceiver in 0.13-μm SOI CMOS for Short-Haul Optical Networks

Javier Aguirre <sup>10</sup>, David Bol <sup>10</sup>, *Member, IEEE*, Denis Flandre <sup>10</sup>, *Senior Member, IEEE*, Carlos Sánchez-Azqueta, and Santiago Celma

Abstract—Duobinary modulation is a robust and attractive coding format for high-speed serial data transmission because it allows an excellent tradeoff between speed, noise and power. However, conventional architectures reported in the literature performing the necessary precodification in a duobinary transceiver suffer from a severe vulnerability to glitches that limits their performances at high data rates. This study presents a new precoder scheme that overcomes this limitation with a very small design, area and power consumption, and a time-domain analysis that confirms the advantages of the proposed solution. The proposed precoder has been implemented in a full duobinary transceiver fabricated in a 0.13- $\mu$ m partially depleted-silicon on insulator CMOS technology that works at 10 Gb/s. The fabricated precoder consumes 13.8 mW and the decoder consumes 23.2 mW from a single supply of 1.2 V. Experimental results are provided for a simulated channel of 50-m plastic optical fiber.

Index Terms—Analog signal processing, duobinary modulation, graded index POF (GI-POF), high-speed communications, multilevel modulation, SOI-CMOS.

#### I. INTRODUCTION

ATA traffic in industrial environments increases at a dizzying pace. Applications of serial communications, such as ambient parameter monitoring, chip-to-chip interconnections or industrial Ethernet networks, among many others, are a constant challenge for optimizing the performance and the reliability of the communication link [1]–[3]. This is why the use of techniques to exploit the channel bandwidth such as equalization [4] or signal modulation [5] is required. In this scenario, a very in-

Manuscript received December 13, 2016; revised February 24, 2017, March 24, 2017, April 20, 2017, and May 4, 2017; accepted May 15, 2017. Date of publication June 16, 2017; date of current version December 8, 2017. This work was supported by MICINN-FEDER under Grant TEC2014-52840-R, and FPU fellowship program to J. Aguirre (FPU12/03869). (Corresponding author: Javier Aguirre.)

J. Aguirre, C. Sánchez-Azqueta, and S. Celma are with the Group of Electronic Design (GDE), Aragón Institute of Engineering Research (I3A), Universidad de Zaragoza, Zaragoza 50009, Spain (e-mail: jag@unizar.es; csanaz@unizar.es; scelma@unizar.es).

D. Bol and D. Flandre are with the ICTEAM Institute - ECS Group, Université catholique de Louvain, 1348, Louvain-la-Neuve, Belgium (e-mail: david.bol@uclouvain.be; Denis.Flandre@uclouvain.be).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TIE.2017.2716870

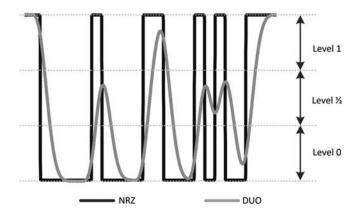

Fig. 1. Transient response of a signal before (NRZ) and after (DUO) passing through a band-limited channel.

TABLE I

DUOBINARY SIGNAL GENERATION PROCESS

| $\overline{NRZ(t-T_b)}$ | NRZ(t) | DUO(t) |  |  |

|-------------------------|--------|--------|--|--|

| 0                       | 0      | 0      |  |  |

| 1                       | 1      | 1      |  |  |

| 0                       | 1      | 1/     |  |  |

| 1                       | 0      | 1/2    |  |  |

teresting option is the use of amplitude modulation, where three schemes are the most widespread: non return to zero (NRZ), *n*-level pulse amplitude modulation and duobinary.

It is commonly agreed that, among them, duobinary modulation offers the best tradeoff between the three most important figures of merit of a modulation scheme: data rate, signal to noise ratio (SNR) and power consumption [5], [6]. Both duobinary and 4-PAM achieve double data rate compared to NRZ. However, 4-PAM is affected by a higher SNR degradation, producing many more errors than duobinary at high data rates. Moreover, the circuitry needed to perform duobinary modulation consumes less power than that of 4-PAM [6].

The key in duobinary modulation is to take advantage of the intersymbol interference (ISI) caused by the limited bandwidth of the channel, assuming that all the received symbols suffer from it. When an NRZ signal is sent through a band-limited channel, so that its spectrum covers frequencies beyond the channel bandwidth, ISI distorts the signal linearly [7]. If

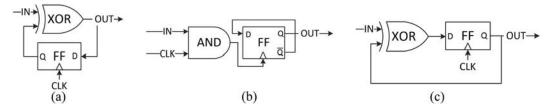

Fig. 2. Block diagram of (a) conventional XOR-based precoder, (b) AND-based precoder, and (c) proposed modified XOR-based precoder.

Fig. 3. Waveforms of the most relevant signals in the duobinary XOR-based precodification process. From top to bottom: input NRZ data stream, clock signal, conventional output taken in the XOR gate, and proposed output in the FF.

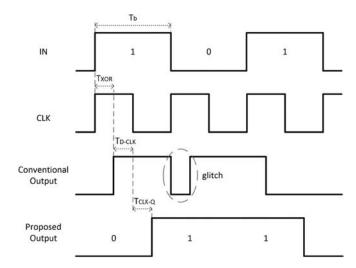

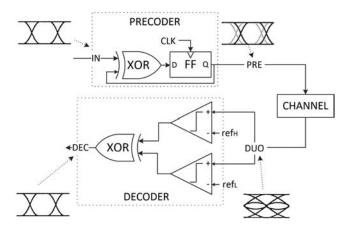

Fig. 4. Block diagram of the proposed duobinary transceiver.

this output signal, whose eye diagram is completely closed, is treated as an NRZ signal, it will be impossible to recover. On the contrary, assuming that the signal has ISI so that the value of the nth bit of the output depends on the value of both nth and (n-1)th bits of the input, the output can be processed as a three-level signal, as depicted in the waveforms of Fig. 1. Table I indicates how the three levels of the duobinary signal (DUO) are created in a band-limited channel, as a function of the NRZ input bits.

A feasible duobinary transceiver needs two blocks for a correct operation: a precoder in the transmitter and a decoder

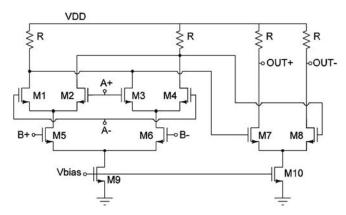

Fig. 5. Schematic of the proposed SCL XOR gate.

in the receiver [6]–[11]. In the literature, several precoder architectures are reported. On one hand, XOR-based precoders are only implemented at system level [8] due to its glitch vulnerability in circuit implementations. On the other hand, AND-based precoders have intrinsically limited speed [9], [10]. Moreover, other papers report complex methods for precoding the signal before a serializer, which enhances the data rate at the cost of design complexity, power, and area consumption [6], [11].

This study proposes a new solution, which is based on the XOR-based structure but does not generate glitches and achieves excellent energy efficiency with small area consumption, improving the reported schemes.

Based on the results of this study, a duobinary transceiver has been implemented in a 0.13- $\mu$ m 1.2-V partially depleted (PD) silicon on insulator (SOI) CMOS technology. It achieves 10 Gb/s, allowing the use of graded index POF (GI-POF) channels for multigigabit applications with large core diameter (up to 1 mm).

It is worth mentioning that PD-SOI is a very interesting technology for high-speed analog electronics [12]. The silicon wafer contains a layer of silicon oxide of a few hundreds of nanometer that isolates the active elements from the rest of the silicon substrate. This insulation avoids the leakage current typical of bulk Si technologies, which is the cause of several reliability problems, especially in the elevated temperature range. In addition, SOI technology avoids the creation of parasitic NPN and PNP transistors formed by adjacent regions in the substrate, eliminating latch-up failures. The buried oxide layer also yields advantages in terms of radiation hardness against single events, but more importantly for the present application: parasitic capacitances and HF crosstalk through

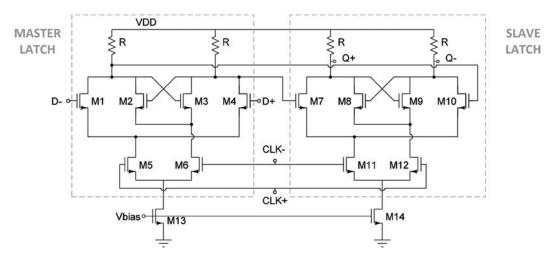

Fig. 6. Schematic of the proposed SCL Flip Flop.

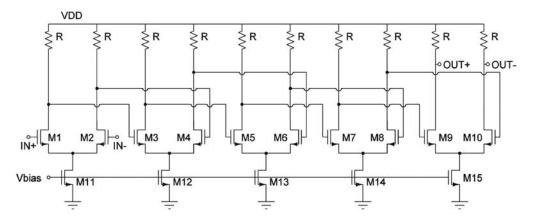

Fig. 7. Schematic of the proposed SCL voltage comparator.

the substrate. Consequently, it is commonly recognized that PD-SOI can bring a reduction of power or an improvement of frequency performance by about 30% over bulk CMOS technology at the same transistor size [13].

This paper is organized as follows. Section II presents the improved precoder technique. Section III describes the main blocks of the proposed architecture. Section IV details the most relevant results. Finally, Section V summarizes the conclusions.

#### II. DUOBINARY PRECODIFICATION

There are two conventional structures to implement a duobinary precoder in a serialized signal: XOR-based and AND-based precoders. The first one is formed by an XOR gate with a feedback loop through a flip-flop (FF), Fig. 2(a). Its major drawback is that it needs a very precise adjustment of the delay time of the cells to ensure a correct operation. Otherwise, the output produces glitches, which ruins the final result. The second structure is formed by an AND gate and a divide-by-2 frequency divider, Fig. 2(b). It avoids the global feedback loop, which removes the restrictions in the time domain. However, it presents a drawback, which is that the AND gate must be able to work at double data rate than the rest of the cells, since

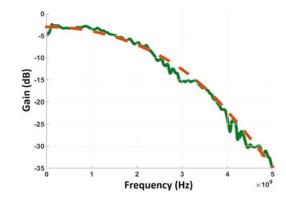

Fig. 8. Modified frequency response of a 50-m 1-mm GI-POF link (solid line) and ninth-order low-pass Bessel filter (dashed line).

one of its inputs is the clock signal, limiting the maximum data rate of this type of precoders. This study proposes the use of the XOR-based architecture but considering that the output of the system is not the output of the XOR gate, but the output of the FF, as shown in Fig. 2(c). This simple and reliable solution, which has not been reported in the literature, solves the issue of the glitches that is found in the conventional structures and relaxes the constraints in the time domain.

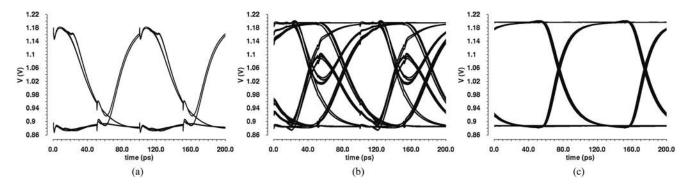

Fig. 9. Simulated eye diagrams of output signals for: (a) AND gate in an AND-based precoder, (b) conventional XOR-based precoder, and (c) proposed XOR-based precoder.

TABLE II

PROCESS CORNER ANALYSES RESULTS AT 27 °C

|     |                   | Min. | Typ. | Max. |

|-----|-------------------|------|------|------|

| PRE | Eye aperture (mV) | 238  | 294  | 353  |

|     | Jitter (ps)       | 3.9  | 4.2  | 6.7  |

| DEC | Eye aperture (mV) | 248  | 306  | 365  |

|     | Jitter (ps)       | 21.4 | 27.2 | 37.1 |

TABLE III

TEMPERATURE SIMULATION RESULTS

|     |                   | −40 °C | 27 °C | 85 °C |

|-----|-------------------|--------|-------|-------|

| PRE | Eye aperture (mV) | 274    | 294   | 322   |

|     | Jitter (ps)       | 5.0    | 4.2   | 4.9   |

| DEC | Eye aperture (mV) | 270    | 306   | 352   |

|     | Jitter (ps)       | 28.3   | 27.2  | 30.4  |

The next paragraphs present an analysis of the design constraints of the conventional XOR-based precoder and how they can be hugely relaxed by means of the modified XOR-based precoder proposed in this paper. We define  $T_{\rm XOR}$  as the delay in the XOR gate and  $T_{D-Q}$  as the delay in the FF, which in turn can be divided into two components:  $T_{D-{\rm CLK}}$  is the time that passes since the input D experiences a change until the clock flags the sample instant; and  $T_{{\rm CLK}-Q}$  is the delay between the sample instant and the toggle in the output

$$T_{D-Q} = T_{D-\text{CLK}} + T_{\text{CLK}-Q}. \tag{1}$$

In the conventional structure [see Fig. 2(a)], a necessary condition must be perfectly achieved: the sum of the delay times of the whole feedback loop must be 1-bit period  $T_b$

$$T_{XOR} + T_{D-Q} = T_b. (2)$$

If (2) is not satisfied, the output signal contains glitches that ruin the final result. The duration of the glitches,  $T_g$ , is the difference between the bit period and the loop delay

$$T_{g} = |T_{b} - T_{XOR} - T_{D-Q}|.$$

(3)

On the contrary, in the proposed structure [see Fig. 2(c)], the FF samples the signal once for every bit, so the glitches

Fig. 10. (a) Screenshot of the full floorplan and (b) photograph of the fabricated die and the precoder on-wafer test setup with GSGSG probes.

Fig. 11. Block diagram of the experimental setup.

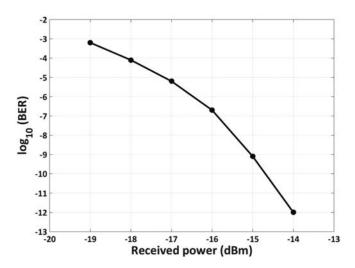

Fig. 12. Bit error rate versus received 10 Gb/s 2<sup>31</sup>–1 PRBS input signal.

disappear. To achieve a correct operation, the conditions that must be satisfied are

$$T_{XOR} + T_{D-Q} < 2T_b \tag{4}$$

$$T_{\text{XOR}} + T_{\text{CLK}-O} \le T_b.$$

(5)

While in the conventional structure the delay times have to be perfectly adjusted, in the proposed structure it is enough to minimize them and, even so, the requirements of the circuits are more flexible than in the conventional case. Fig. 3 illustrates how the conventional XOR-based precoder produces glitches when the loop delay is not perfectly adjusted and how the solution proposed in this paper overcomes this limitation.

# III. CIRCUIT DESIGN

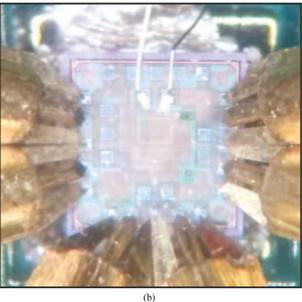

To demonstrate the correct operation of the proposed precoder, a full duobinary transceiver including a precoder and a decoder has been designed and fabricated. Fig. 4 shows the block diagram of the proposed duobinary transceiver. All the cells have been implemented in the H9SOI-FEM 0.13-μm CMOS technology from STMicroelectronics. Source coupled logic (SCL) cells have been chosen because they can operate at a data rate 30% higher than standard CMOS logic cells for the same technology [10]. SCL cells are built concatenating differential pairs, in such a way that every pair of transistors must be always excited by a differential signal. Typical values for such pairs are

W/L =  $10 \,\mu\text{m}/0.13 \,\mu\text{m}$  for the transistors,  $500 \,\Omega$  for the resistors and current sources of 1.5 mA, achieving cells with a bandwidth of 16 GHz and a potential fan-out of 10. All transistors have their body connected to source to avoid floating-body effects in PD-SOI technology.

# A. Precoder

The precoder has been implemented by means of the structure proposed in the previous section, with an XOR gate and a FF. Its block diagram is shown in the precoder box in Fig. 4. The input data signal and the output of the FF enter an XOR gate, whose output goes to the input of the FF, which is driven by the clock signal. The schematic of the proposed SCL XOR gate is shown in Fig. 5. The data signal IN goes to the input A, whereas signal PRE is connected to input B. Transistors M1–M6 perform the logic operation and the output differential pair M7–M8 increases the bandwidth of the cell. Transistors M9–M10 carry out the source current that biases the cell. The FF has been implemented with two D-latches in master-slave configuration, and its schematic is shown in Fig. 6. Each latch, M1–M6 and M7-M12, is formed by two differential pairs, one of which is cross-coupled.

#### B. Decoder

The function of the decoder in a duobinary transceiver is the recovery of the original data sequence from the three-level duobinary signal that comes from the channel. In this study, the decoder has been implemented with a topology formed by a window comparator and an XOR gate. The block diagram is shown in the decoder box of Fig. 4. Both voltage comparators used to implement the window comparator are formed by five differential amplifiers connected in cascade, as can be seen in Fig. 7, achieving the required slew-rate of 25.9 V/ns. The noninverting input of both comparators is connected at the signal DUO, which is the channel output signal. On the other hand, the inverting inputs, ref<sub>H</sub> and ref<sub>L</sub>, are connected to voltage references. The level of ref<sub>H</sub> must be set between the corresponding logic levels 1 and 1/2 of the DUO signal, whereas the level of ref<sub>L</sub> must be established between the 0 and ½ logic levels. The XOR gate structure is the same as that of the precoder, whose schematic is shown in Fig. 5.

#### C. Channel

Since a duobinary signal is defined as the mean value of the nth and the (n-1)th bits of the input, a channel in the z-domain can be expressed as  $1+z^{-1}$  [9]. A feasible way of implementing this function is a low-pass Bessel filter with an order between fifth and ninth and a bandwidth between  $0.2/T_b$  and  $0.3/T_b$  [14]. Despite the fact that not all channels present optimum characteristics to be used with duobinary modulation, the features of the channel can be adapted with the corresponding transceiver front-end (including pre-emphasis, equalizer, etc.) to satisfy these requirements. The test setup of this work includes a ninth-order low-pass Bessel filter with 2.2-GHz bandwidth. This configuration has been chosen because it is similar to the

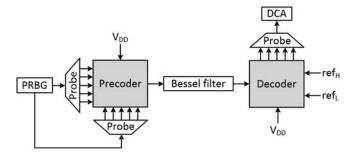

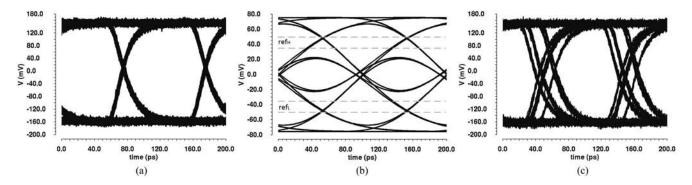

Fig. 13. Experimental eye diagrams of different stages through the transceiver with the proposed precoder: (a) precoder output, (b) channel output, and (c) decoder output.

GI-POF link reported in [15], but the bandwidth has been enhanced up to 2.2 GHz in order to be able to test the transceiver up to 10 Gb/s. Fig. 8 shows the transfer functions of the implemented Bessel filter and the measured modified GI-POF link.

### IV. RESULTS

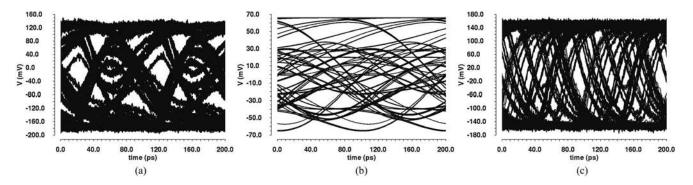

First of all, we are going to demonstrate that the proposed precoder is the most reliable solution among the three precoder architectures described in Section II when the data rate is as high as 10 Gb/s. For that purpose, a set of transistor-level simulations has been carried out. Fig. 9(a) shows the signal of an AND-based precoder at the AND output when it operates at 10 Gb/s. Since the clock signal changes twice a bit period, the AND output should be able to do the same, what makes this system more likely to produce errors in the following frequency divider.

Fig. 9(b) and (c) show the operation of the XOR-based precoder architecture. Fig. 9(b) is the eye diagram taking the conventional output, whereas Fig. 9(c) shows the signal eye diagram at the proposed output. As it can be seen, the output signal of the conventional precoder is full of glitches that ruin the result. However, the proposed solution filters all those glitches, presenting an eye diagram completely open. The transceiver has been found functional for all the corner analyses available in the technology, with a variation of 20% in the vertical aperture of the eye diagrams, due to the variation suffered by the current sources of the cells. The decoder jitter suffers a high variation since it is dominated by the asynchronous comparisons carried out by the voltage comparators. The main results of the process corner analyses and temperature simulations in the range from -40 °C to 85 °C are presented in Tables II and III, respectively.

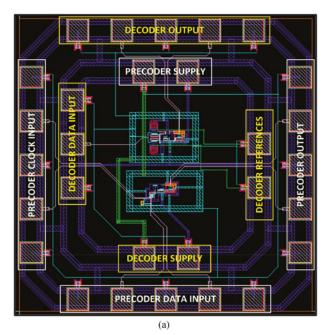

Finally, the experimental results of the fabricated prototype are presented. Fig. 10(a) shows a screenshot of the floorplan. It has been designed to contain both the precoder and the decoder in the same die of 1 mm<sup>2</sup>. Fig. 10(b) shows the photograph of the fabricated die while the precoder is tested in a probe station. The two microwires on the top are soldered to a printed circuit board that biases the ICs, whereas the three differential probes on the left, right, and bottom carry the input and output signals. The low-pass Bessel filter has been implemented with passive elements matched to 50  $\Omega$  at both the input and the

output and it is placed between the output of the precoder and the input of the decoder. The prototypes have been tested for 10 Gb/s with a pseudorandom bit sequence of  $2^{31}-1$  bits using a pseudo-random bit generator Picosecond 12050 and a digital communications analyzer (DCA) Agilent Infiniium DCA-J 86100C, with the experimental setup depicted in Fig. 11. During the test of the full transceiver, two dies have been used, one for the precoder and a different one for the decoder. DC signals and connections with the filter have been made with microwires soldered to the dies, whereas probes have been used for the precoder inputs and the decoder outputs. Fig. 12 shows the bit error ratio (BER) performance of the decoder, which has been estimated from the Q factor of the eye diagrams, and presents a value of  $10^{-12}$  for a received power of -14 dBm.

Fig. 13 shows the eye diagrams through the transceiver at 10 Gb/s decoupled of their dc components: Fig. 13(a) shows the precoder output, presenting an RMS jitter of 4.7 ps and a vertical aperture of 278 mV. Fig. 13(b) shows the decoder input, which is a duobinary signal. Finally, the decoded signal is represented in Fig. 13(c). For an optimal performance of the decoder, the voltage references of the comparators are fixed with temperature compensated voltage references. Fig. 13(b) contains two regions delimited by dashed horizontal lines, 15-mV width each, in which ref<sub>H</sub> and ref<sub>L</sub> have to be set. The RMS jitter in this eye diagram is 28 ps and the vertical aperture 245 mV. For comparison, Fig. 14 shows the eye diagrams through the transceiver using the conventional XOR-based precoder. The precoder output is completely damaged by glitches, so the same happens with the following stages.

Table IV compares the performance of this transceiver with other reported CMOS duobinary precoders and transceivers. The features of both precoder (TX) and decoder (RX) have been separated in order to highlight the advantages of the proposed precoder architecture. Since [6] and [11] report duobinary precoders, they lack the receiver part. The energy efficiency, in J/bit, is defined as the ratio between the power and the data rate. The experimental uncertainty in the calculation of the energy efficiencies is below 2%. It is worth highlighting that, in this study, the energy efficiency of the precoder is improved to 1.38 pJ/bit with small area consumption, thanks to the power saving advantages of PD-SOI CMOS technology and the new precoder architecture featuring low design and area overheads.

Fig. 14. Experimental eye diagrams of different stages through the transceiver with the XOR-based conventional precoder: (a) precoder output, (b) channel output, and (c) decoder output.

# TABLE IV SUMMARY OF RESULTS

|                                                                      | [6]                      |                                         | [9]                    |                                      | [10]                      |                                           | [11]                   |                                                  | This work                   |                                                        |  |

|----------------------------------------------------------------------|--------------------------|-----------------------------------------|------------------------|--------------------------------------|---------------------------|-------------------------------------------|------------------------|--------------------------------------------------|-----------------------------|--------------------------------------------------------|--|

| Technology Data rate (Gbps) Precoder architecture Supply voltage (V) | 4                        | 90 nm CMOS<br>20<br>Pre-serializer<br>1 |                        | 90 nm CMOS<br>20<br>AND-based<br>1.5 |                           | 0.18 μm CMOS<br>3.125<br>AND-based<br>1.8 |                        | 0.18 $\mu$ m CMOS<br>10<br>Pre-serializer<br>1.8 |                             | 0.13 μm PD-SOI CMOS<br>10<br>Modified XOR-based<br>1.2 |  |

| Power (mW)<br>Energy efficiency (pJ/bit)<br>Area (mm²)               | TX<br>122<br>6.1<br>0.17 | RX<br>N/A*<br>N/A*<br>N/A*              | TX<br>120<br>6<br>0.21 | RX<br>75<br>12.5<br>0.11             | TX<br>10.1<br>3.2<br>N/A* | RX<br>17.8<br>5.7<br>N/A*                 | TX<br>20<br>2<br>0.035 | RX<br>N/A*<br>N/A*<br>N/A*                       | TX<br>13.8<br>1.38<br>0.006 | RX<br>23.2<br>2.32<br>0.016                            |  |

<sup>\*</sup>N/A: Not available.

#### V. CONCLUSION

This study presents a duobinary transceiver fabricated in 0.13- $\mu$ m PD-SOI CMOS technology. This transceiver uses a new precoder architecture, which overcomes the disadvantages of the other architectures reported in the literature, avoiding the appearance of glitches and achieving robust operation. The proposed transceiver reaches 10 Gb/s, enabling its use in multigigabit applications such as short-reach GI-POF channels. Simulation results already revealed the advantages in terms of glitch robustness of the proposed scheme against the conventional one. Finally, an experimental characterization made with several prototypes is presented that demonstrates robust operation of the proposed duobinary transceiver at 10 Gbps consuming 37 mW from 1.2 V single supply, 13.8 mW corresponded to the precoder and 23.2 mW to the decoder. The full transceiver exhibits a competitive energy efficiency of only 3.7 pJ/bit. A bit error ratio of  $10^{-12}$  for -14 dBm received power has been obtained by using an electrical equivalent model for 1-mm 50-m GI-POF channel.

# REFERENCES

- J. A. Maestro and P. Reviriego, "Energy efficiency in industrial ethernet: The case of powerlink," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2896–2903, Aug. 2010.

- [2] Y. Dong and K. W. Martin, "Gigabit communications over plastic optical fiber," *IEEE Solid State Circuits Mag.*, vol. 3, no. 1, pp. 60–69, Winter 2011.

- [3] M. Kamiya, H. Ikeda, and S. Shinohara, "Wavelength-division-multiplexed analog transmission through plastic optical fiber for use in factory communications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 2, pp. 507–510, Apr. 2002.

- [4] C. Gimeno et al., "Continuous-time linear equalizer for multigigabit transmission through SI-POF in factory area networks," *IEEE Trans. Ind. Electron.*, vol. 62, no. 10, pp. 6530–6532, Oct. 2015.

- [5] D. Zeolla, A. Nespola, and R. Gaudino, "Comparison of different modulation formats for 1-Gb/s SI-POF transmission systems," *IEEE Photon. Technol. Lett.*, vol. 23, no. 14, pp. 950–952, Jul. 15, 2011.

- [6] B. Min, K. Lee, and S. Palermo, "A 20 Gb/s triple-mode (PAM-2, PAM-4 and duobinary) transmitter," *Microelectron. J.*, vol. 43, pp. 687–696, 2012.

- [7] J. G. Proakis, *Digital Communications*, 5th ed. New York, NY, USA: McGraw-Hill, 2008.

- [8] R. R. Mahmud, M. A. G. Khan, and S. M. A. Razzak, "Design of a Duobinary encoder and decoder circuits for communication systems," in *Proc. Int. Conf. Elect. Comput. Eng.*, Dhaka, Bangladesh, 2010, pp. 49–52.

- [9] J. Lee, M. S. Chen, and H. D. Wang, "Design and comparison of three 20-Gb/s backplane transceivers for duobinary, PAM4, and NRZ data," *IEEE J. Solid-State Circuits*, vol. 43, no. 9, pp. 2120–2133, Sep. 2008.

- [10] J. Aguirre, C. Sánchez-Azqueta, E. Guerrero, C. Gimeno, and S. Celma, "Precoder and decoder for duobinary modulation over equalized 50-m SI-POF," in *Proc. 12th Conf. Ph.D. Res. Microelectron. Electron.*, 2016, pp. 1–4.

- [11] M. Sharad, V. S. R. P, and P. Mandal, "A new double data rate (DDR) dual-mode duobinary transmitter architecture," in *Proc. 24th Int. Conf. VLSI Des.*, Chennai, India, 2011, pp. 12–17.

- [12] B. Kazemi Esfeh et al., "Assessment of 28 nm UTBB FD-SOI technology platform for RF applications: Figures of merit and effect of parasitic elements," Solid-State Electron., vol. 117, pp. 130–137, 2016.

- [13] D. Flandre, J.-P. Raskin, and D. Vanhoenacker-Janvier, "SOI CMOS transistors for RF and microwave applications," *Int. J. High-Speed Electron. Syst.*, vol. 11, no. 4, pp. 1159–1248, 2001.

- [14] A. Rahman, M. Broman, and M. Howieson, "Optimum low pass filter bandwidth for generating duobinary signal for 40 Gb/s systems," Thin Film Technology Corporation, North Mankato, MN, USA, pp. 1–5, 2009.

- [15] D. Visani et al., "Beyond 1 Gbit/s transmission over 1 mm diameter plastic optical fiber employing DMT for in-home communication systems," J. Lightw. Technol., vol. 29, no. 4, pp. 622–628, Feb. 15, 2011.

Javier Aguirre was born in Pamplona, Spain. He received the B.Sc. and the M.Sc. degrees in physics in 2011 and 2012, respectively, from the University of Zaragoza, Zaragoza, Spain, where he is currently working toward the Ph.D. degree in physics in the Group of Electronic Design, Aragon Institute for Engineering Research (GDE-I3A). In 2015, he was a visiting Ph.D. student at the UCL, Louvain-la-Neuve, Belgium.

His research interests include noise rejection techniques, sensor interfaces, high-frequency

communication circuits, and mixed-signal integrated circuits.

**David Bol** (S'07–M'09) received the M.Sc. degree in electromechanical engineering and the Ph.D. degree in engineering science from the Université catholique de Louvain, Louvain-la-Neuve, Belgium, in 2004 and 2008, respectively. In 2005, he was a visiting Ph.D. Student at the CNM, Sevilla, Spain, and in 2009, a Postdoctoral Researcher at intoPIX, Louvain-la-Neuve, Belgium.

In 2010, he was a Visiting Postdoc Researcher at the UC Berkeley Lab for Manufac-

turing and Sustainability, Berkeley, CA, USA. In 2015, he participated to the creation of e-peas semiconductors, Liège, Belgium. He is currently leading with Prof. Denis Flandre the Electronic Circuits and Systems research group focused on ultra-low-power circuits and systems, technology/circuit interaction, mixed-signal SoC design, variability mitigation, nano-CMOS technologies and green semiconductor manufacturing. He has authored more than 70 papers and conference contributions and holds three patents.

Dr. Bol (co-)received three Best Paper/ Poster/Design Awards in IEEE conferences (ICCD 2008, SOI Conf. 2008, FTFC 2014).

**Denis Flandre** (SM'03) received the M.Sc. and Ph.D degrees in electrical engineering from Université catholique de Louvain (UCL) in 1986 and 1990, respectively.

Since 2001, he has been a Full-Time Professor at UCL. He has authored more than 900 technical papers or conference contributions. He is coinventor of 12 patents. He has lectured many short courses on SOI technology, devices and circuits. He is involved in R&D on SOI MOS devices, digital and analog circuits, as well as

sensors and MEMS, for high-speed, low-voltage low-power, microwave, biomedical, radiation-hardened and high-temperature electronics and microsystems.

Dr. Flandre is the Co-Founder of CISSOID (SOI and high-reliability IC products), and scientific advisor of INCIZE (Semiconductor characterization and modeling for digital, analog/RF and harsh environment design) and e-peas (Energy harvesting and processing solutions for IoT applications). He has been a member of several EU Networks of Excellence on High-Temperature Electronics, SOI technology, Nano-electronics and Micro-nano-technology, and of the SOI Industry Consortium.

Carlos Sánchez-Azqueta was born in Zaragoza, Spain. He received the B.Sc., M.Sc., and Ph.D. degrees from the University of Zaragoza, Zaragoza, Spain, in 2006, 2010, and 2012, respectively, all in physics, and the Dipl.-Ing. degree in electronic engineering from the Complutense University of Madrid, Madrid, Spain in 2009.

He is currently a Member of the Group of Electronic Design, Aragón Institute of Engineering Research, University of Zaragoza.

His research interests include mixed-signal integrated circuits, high-frequency analog communication circuits, phase-locked loops, and clock and data recovery circuits.

Santiago Celma was born in Zaragoza, Spain. He received the B.Sc., M.Sc., and Ph.D. degrees in physics from the University of Zaragoza, Zaragoza, Spain, in 1987, 1989, and 1993, respectively.

He is currently a Full Professor in the Group of Electronic Design, Aragon Institute of Engineering Research, University of Zaragoza. He has coauthored more than 100 technical papers and 300 international conference contributions. He is coauthor of four technical books and the holder

of four patents. He appears as a Principal Investigator in more than 30 national and international research projects. His research interests include circuit theory, mixed-signal integrated circuits, high-frequency communication circuits, wireless sensor networks, and cryptography for secure communications.