## Trabajo Fin de Máster

Evaluación de SLAMBench en un sistema completamente heterogéneo: CPU, GPU y FPGA

Evaluation of SLAMBench on a truly heterogeneous system: CPU, GPU and FPGA

Autor/es

Marcos Canales Mayo

Director/es

Darío Suárez Gracia y Rubén Gran Tejero

Escuela de Ingeniería y Arquitectura

2018

MARCOS CANALES MAYO

EVALUACIÓN DE SLAMBENCH EN UN SISTEMA

COMPLETAMENTE HETEROGRÉNEO: CPU, GPU Y

FPGA

# EVALUACIÓN DE SLAMBENCH EN UN SISTEMA COMPLETAMENTE HETEROGÉNEO: CPU, GPU Y FPGA

MARCOS CANALES MAYO

Máster en Ingeniería Informática

Supervisado por

Darío Suárez Gracia y Rubén Gran Tejero

Grupo de Arquitectura de Computadores

Departamento de Ingeniería e Informática de Sistemas

Escuela de Ingeniería y Arquitectura

Universidad de Zaragoza

Marcos Canales Mayo: *Evaluación de SLAMBench en un sistema completamente heterogéneo: CPU, GPU y FPGA*, Máster en Ingeniería Informática, © Mayo 2017

## DECLARACIÓN DE AUTORÍA Y ORIGINALIDAD

(Este documento debe acompañar al Trabajo Fin de Grado (TFG)/Trabajo Fin de Máster (TFM) cuando sea depositado para su evaluación).

D./Dª. Marcos Canales Mayo,

con nº de DNI 73161591-V en aplicación de lo dispuesto en el art. 14 (Derechos de autor) del Acuerdo de 11 de septiembre de 2014, del Consejo de Gobierno, por el que se aprueba el Reglamento de los TFG y TFM de la Universidad de Zaragoza,

Declaro que el presente Trabajo de Fin de (Grado/Máster) Máster, (Título del Trabajo)

Evaluación de SLAMBench en un sistema completamente heterogéneo:

CPU, GPU y FPGA

es de mi autoría y es original, no habiéndose utilizado fuente sin ser citada debidamente.

Zaragoza, 21 de Septiembre de 2018

Fdo: Marcos Canales Mayo

## ABSTRACT

---

Existe una tendencia en los últimos años hacia usar los sistemas heterogéneos para implementar aplicaciones con requerimientos muy estrictos de rendimiento o consumo de energía, que los sistemas homogéneos no son capaces de satisfacer. En este proyecto se presenta un estudio sobre KinectFusion, una carga de trabajo significativa de visión por computador, ejecutado en un sistema 3-heterogéneo, compuesto por CPU, GPU y FPGA. Mediante el uso del benchmark SLAMBench se evalúa el impacto que tienen diversos tipos de optimizaciones sobre la implementación original de KinectFusion y enfocadas a la FPGA, pues es el dispositivo que en teoría ofrece mejor relación rendimiento/consumo energético.

En general, los resultados demuestran que el principal cuello de botella en la FPGA es la transferencia de los buffers de entrada y salida debido a las limitaciones del *hardware*. Sin embargo, aunque la GPU alcanza 3,5 veces más ancho de banda, la FPGA es un dispositivo capaz de dar un rendimiento competitivo y podría usarse como acelerador en un sistema más equilibrado. Esto es gracias a las diversas técnicas de optimización que se pueden aplicar y con las que se han conseguido, para el caso estudiado, un *speedup* de 16,54 con respecto a la implementación original. Las optimizaciones que mayor impacto han tenido están relacionadas con el alineamiento y patrón de acceso a memoria. Por el contrario, la técnica más importante que no ha dado resultados es el uso de representación en coma fija, ya que los requerimientos de precisión y el *overhead* producido por las conversiones hunden el rendimiento de la aplicación.

Este trabajo sienta las bases para una futura investigación más detallada sobre el papel que podría jugar una FPGA en entornos heterogéneos y, en concreto, sobre su posible rol en un algoritmo complejo como KFusion.

## ÍNDICE GENERAL

---

|          |                                                          |           |

|----------|----------------------------------------------------------|-----------|

| <b>1</b> | <b>INTRODUCCIÓN</b>                                      | <b>1</b>  |

| 1.1      | Objetivo . . . . .                                       | 4         |

| 1.2      | Alcance . . . . .                                        | 4         |

| 1.3      | Estructura del documento . . . . .                       | 4         |

| <b>2</b> | <b>SISTEMAS HETEROGÉNEOS: ESTADO DEL ARTE</b>            | <b>7</b>  |

| 2.1      | Heterogeneidad . . . . .                                 | 7         |

| 2.2      | Hardware . . . . .                                       | 8         |

| 2.2.1    | GPU . . . . .                                            | 9         |

| 2.2.2    | FPGA . . . . .                                           | 10        |

| 2.3      | Software . . . . .                                       | 10        |

| 2.3.1    | OpenCL . . . . .                                         | 11        |

| 2.3.2    | Altera Offline Compiler . . . . .                        | 11        |

| <b>3</b> | <b>TRABAJOS RELACIONADOS</b>                             | <b>13</b> |

| <b>4</b> | <b>SLAMBENCH</b>                                         | <b>15</b> |

| 4.1      | KinectFusion . . . . .                                   | 15        |

| 4.2      | Benchmark . . . . .                                      | 16        |

| <b>5</b> | <b>HERRAMIENTAS Y METODOLOGÍA DE TRABAJO</b>             | <b>19</b> |

| 5.1      | Plataformas disponibles . . . . .                        | 19        |

| 5.2      | Flujo de trabajo con la FPGA . . . . .                   | 20        |

| <b>6</b> | <b>TÉCNICAS EXPLORADAS PARA OPTIMIZAR KERNELS</b>        | <b>23</b> |

| 6.1      | Caracterización de KFusion . . . . .                     | 23        |

| 6.2      | Técnicas exploradas . . . . .                            | 26        |

| 6.2.1    | Memoria privada, local y global . . . . .                | 26        |

| 6.2.2    | Parámetros <i>attribute</i> . . . . .                    | 27        |

| 6.2.3    | <i>Loop unrolling</i> y <i>loop pipelining</i> . . . . . | 28        |

| 6.2.4    | Patrón de acceso a memoria . . . . .                     | 29        |

| 6.2.5    | Memoria alineada . . . . .                               | 30        |

| 6.2.6    | Buffers de lectura/escritura . . . . .                   | 31        |

| 6.2.7    | Funciones <i>built-in</i> . . . . .                      | 31        |

| 6.2.8    | División en múltiples kernels . . . . .                  | 32        |

| 6.2.9    | Opciones de compilación . . . . .                        | 33        |

| 6.2.10   | Barriers . . . . .                                       | 34        |

| 6.2.11   | Half float . . . . .                                     | 34        |

| 6.2.12   | Representación en coma fija . . . . .                    | 35        |

| 6.2.13   | Múltiples binarios AOCX . . . . .                        | 35        |

| 6.3      | Resultados . . . . .                                     | 36        |

| <b>7</b> | <b>CONCLUSIONES Y TRABAJO FUTURO</b>                     | <b>43</b> |

| <b>A</b> | <b>APPENDIX</b>                                          | <b>45</b> |

| A.1      | OpenCL sample application . . . . .                      | 45        |

| A.2      | Filtro bilateral . . . . .                               | 47        |

| A.3      | Informe generado por el AOC . . . . .                    | 47        |

|      |                                                                                      |           |

|------|--------------------------------------------------------------------------------------|-----------|

| A.4  | Uso de recursos de la FPGA en la implementación original . . . . .                   | 48        |

| A.5  | Kernel original de reduce . . . . .                                                  | 51        |

| A.6  | Comparación de anchos de banda de los dispositivos . . . . .                         | 54        |

| A.7  | Funciones built-in . . . . .                                                         | 55        |

| A.8  | Pérdida de precisión en las versiones de coma fija . . . . .                         | 56        |

| A.9  | Balanceo de carga . . . . .                                                          | 57        |

| A.10 | Tiempo desglosado de las etapas de <i>track</i> y <i>reduce</i> en la FPGA . . . . . | 58        |

| A.11 | Esfuerzos . . . . .                                                                  | 59        |

|      | <b>BIBLIOGRAFÍA</b>                                                                  | <b>63</b> |

## ÍNDICE DE FIGURAS

---

|           |                                                                                                                                                                                                                                      |    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

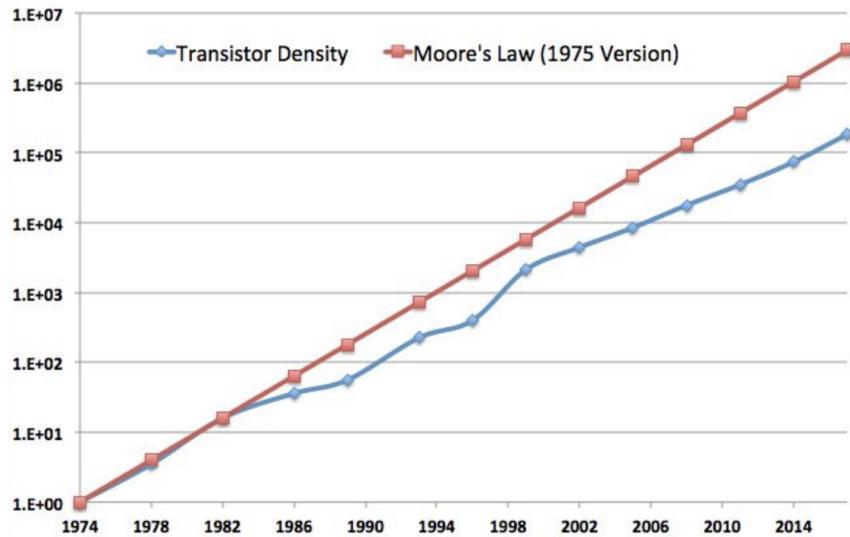

| Figura 1  | Deceleración de la densidad de transistores respecto a la ley de Moore - A New Golden Age for Computer Architecture [12] . . . . .                                                                                                   | 2  |

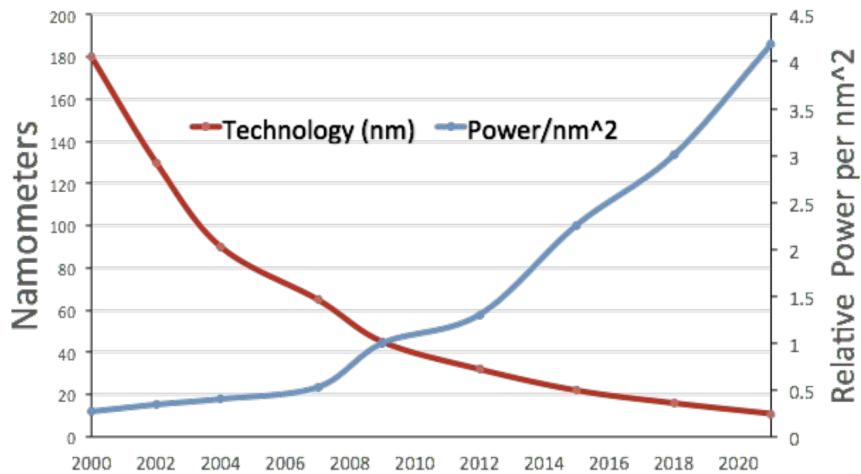

| Figura 2  | Evolución de la densidad de potencia vs. tecnología - A New Golden Age for Computer Architecture [12] . . . . .                                                                                                                      | 2  |

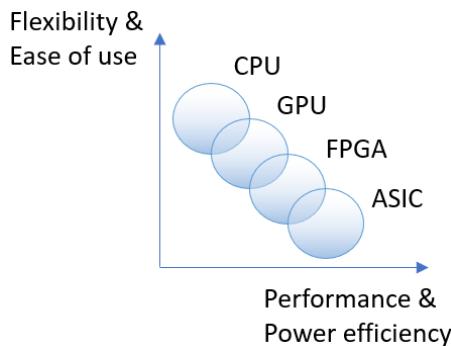

| Figura 3  | Flexibilidad y facilidad de uso frente a rendimiento y eficiencia energética según el tipo de dispositivo . . . . .                                                                                                                  | 3  |

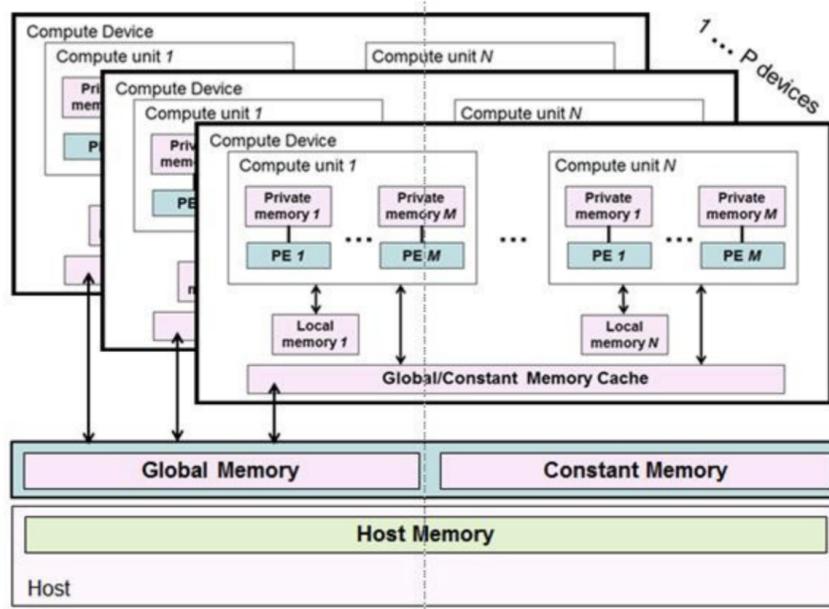

| Figura 4  | Modelo <i>host-device</i> - OpenCL 2.2 Specification [7]                                                                                                                                                                             | 8  |

| Figura 5  | Comparación de paralelismos SIMD vs <i>Pipeline</i> - OpenCL on FPGAs for GPU Programmers                                                                                                                                            | 9  |

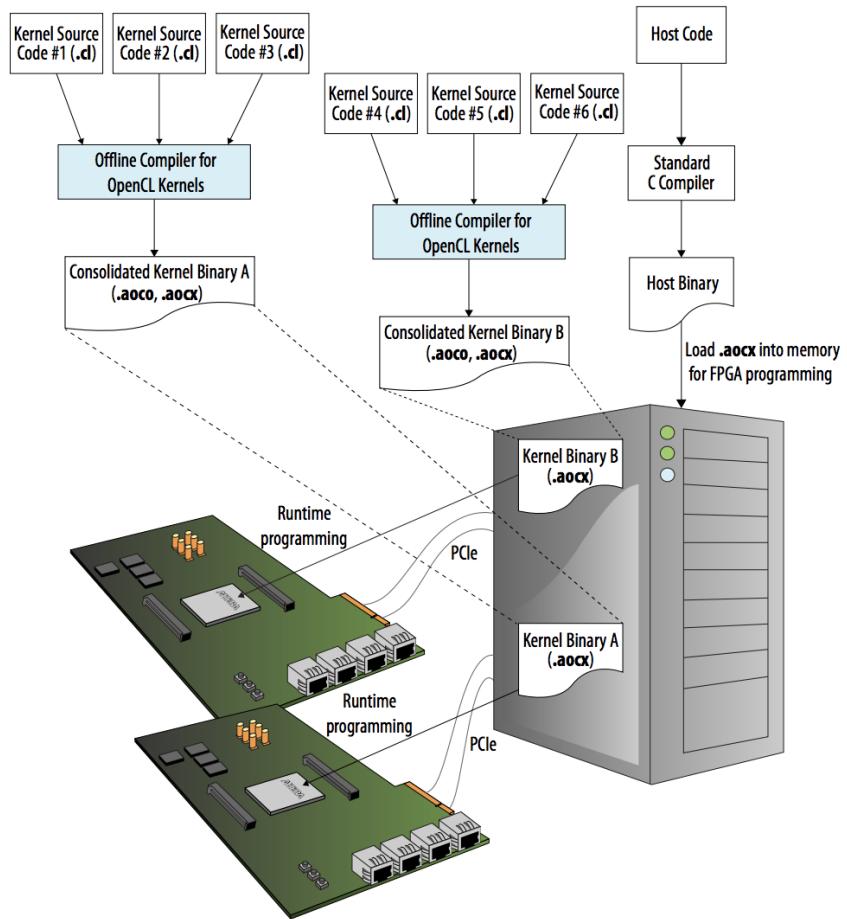

| Figura 6  | OpenCL FPGA Programming flow - Intel FPGA SDK for OpenCL Pro Edition Programming Guide [10] . . . . .                                                                                                                                | 12 |

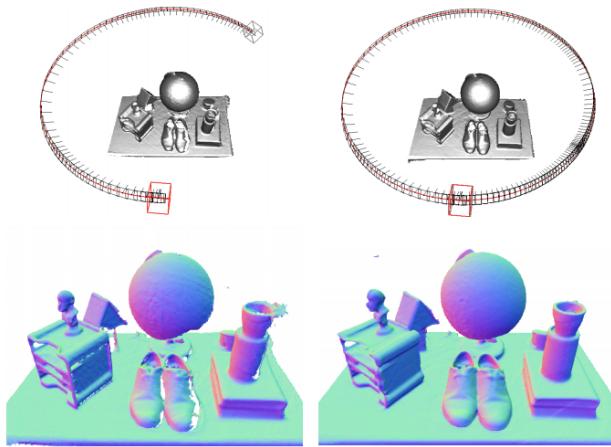

| Figura 7  | Trayectoria y volumen calculados por KFusion a lo largo del tiempo - KinectFusion: Real-Time Dense Surface Mapping and Tracking [18] . . .                                                                                           | 16 |

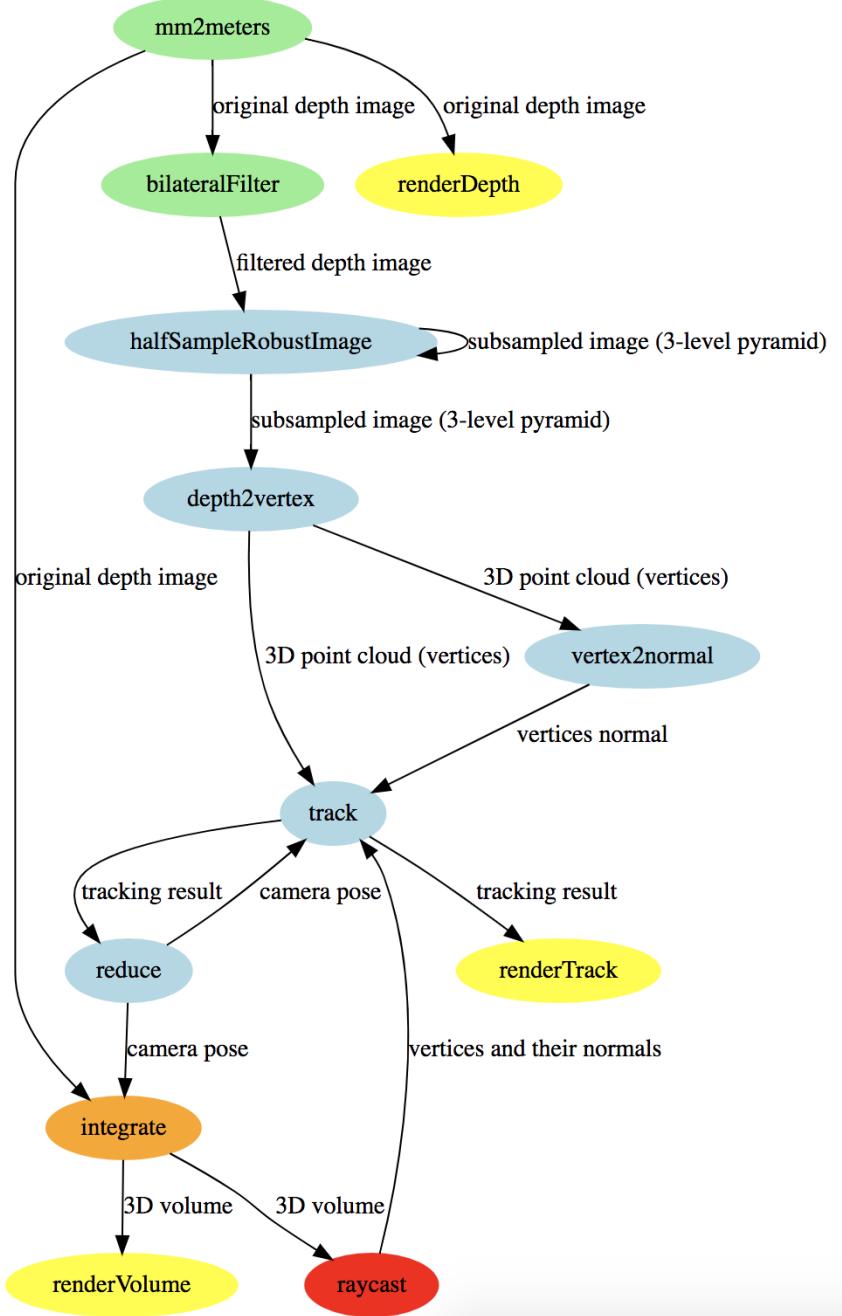

| Figura 8  | Etapas en que se divide KFusion . . . . .                                                                                                                                                                                            | 17 |

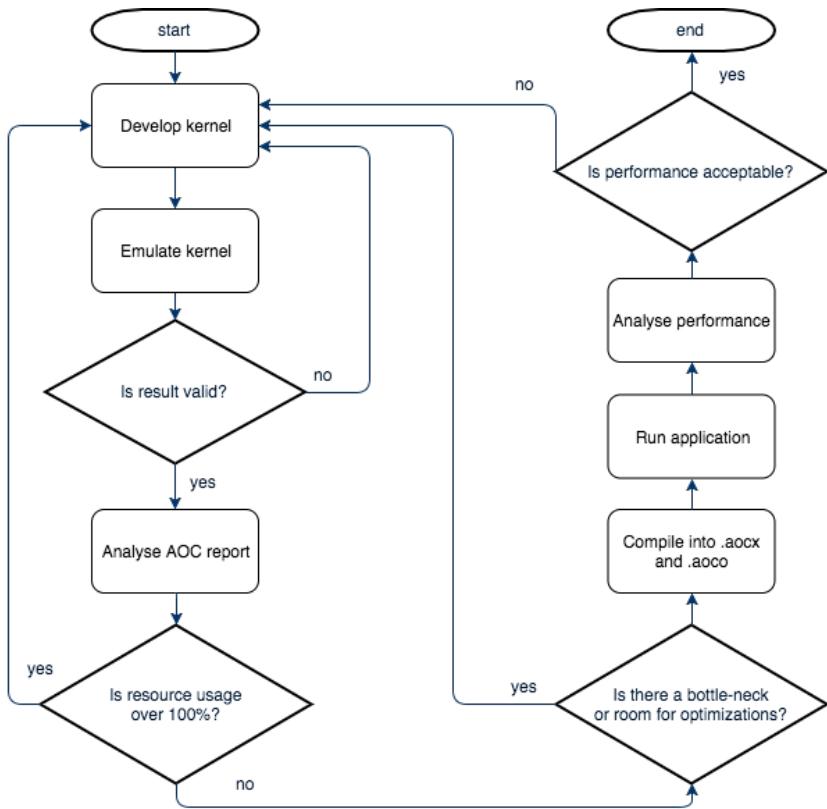

| Figura 9  | Flujo de trabajo con la FPGA . . . . .                                                                                                                                                                                               | 21 |

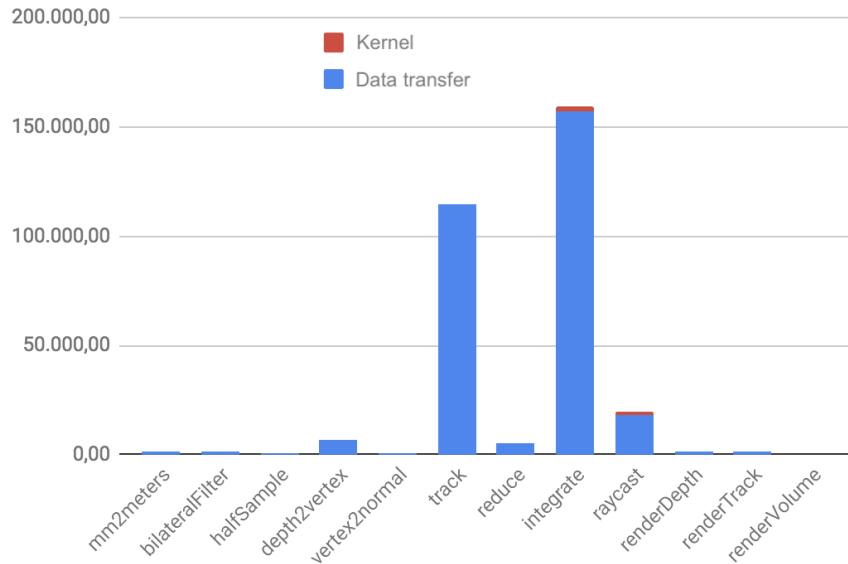

| Figura 10 | Tiempos (ms) de la versión original del código de cada kernel OpenCL en la FPGA de Socarrat                                                                                                                                          | 24 |

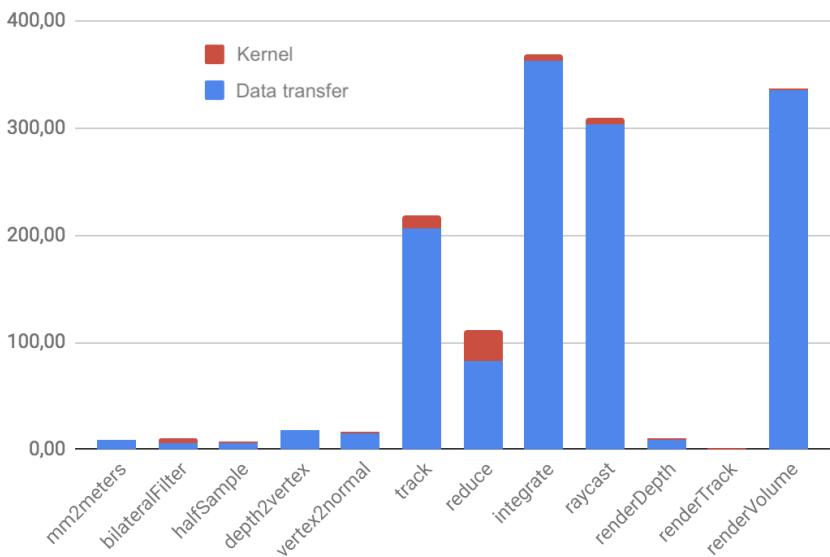

| Figura 11 | Tiempos (ms) de la versión original del código de cada kernel OpenCL en la GPU de Socarrat                                                                                                                                           | 25 |

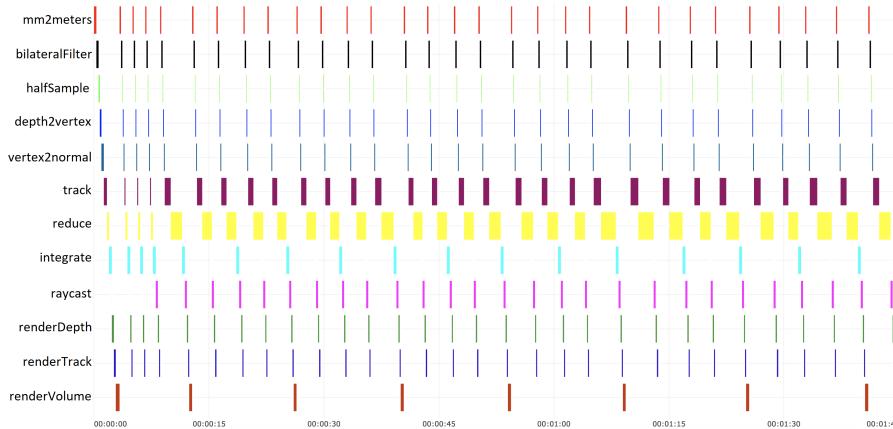

| Figura 12 | Duración de cada etapa ejecutando todo el <i>pipeline</i> de la versión original de OpenCL en la GPU . . . . .                                                                                                                       | 27 |

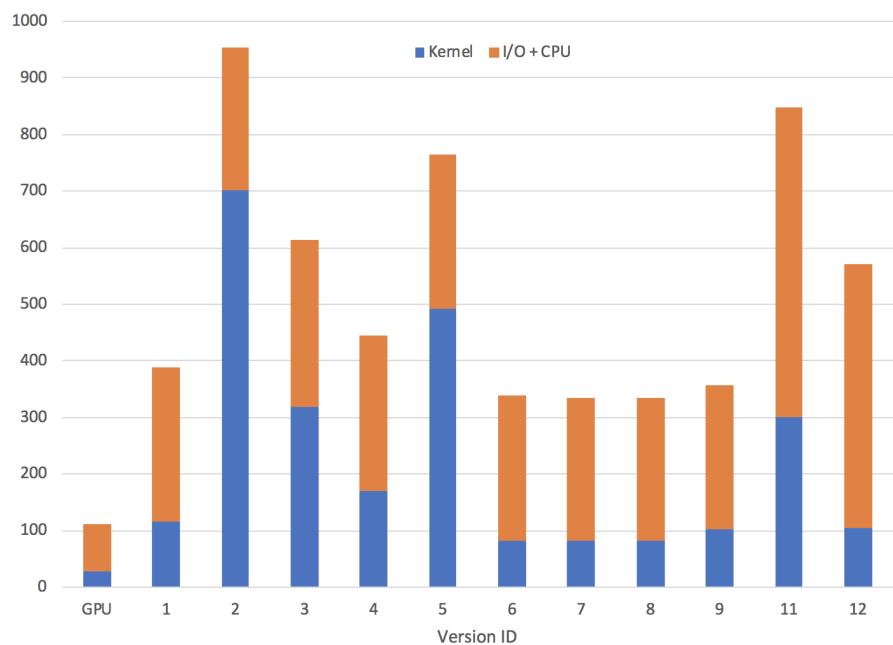

| Figura 13 | Tiempo (ms) de kernels + IO + CPU para cada una de las versiones con optimizaciones, de la 1 a la 12 corresponden a versiones para la FPGA                                                                                           | 38 |

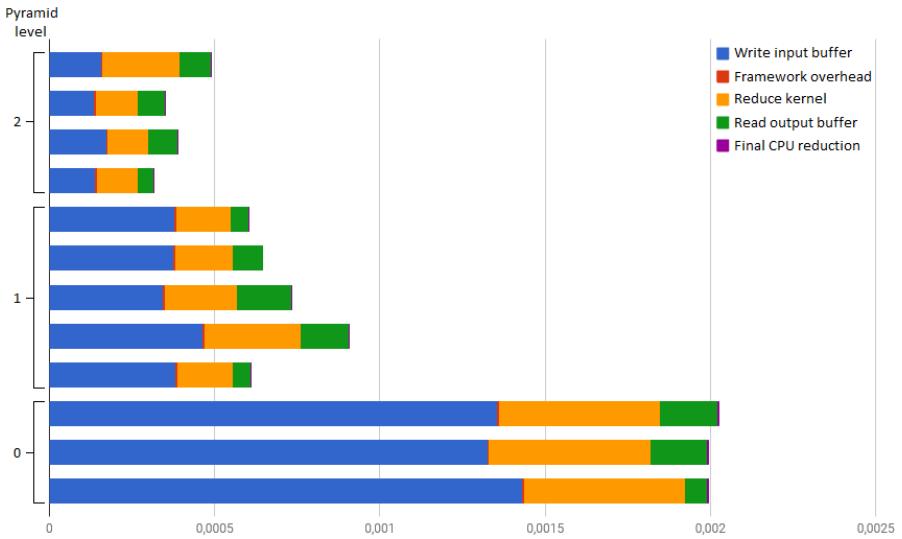

| Figura 14 | Distribución del tiempo (ms) consumido por la mejor versión de <i>reduce</i> en la FPGA de Socarrat                                                                                                                                  | 40 |

| Figura 15 | Filtro bilateral aplicado sobre los Minaretes y el lago Minarete en el desierto Ansel Adams del Bosque Nacional Inyo, Sierra Nevada, Condado de Madera, California - KinectFusion: Real-Time Dense Surface Mapping and Tracking [25] | 48 |

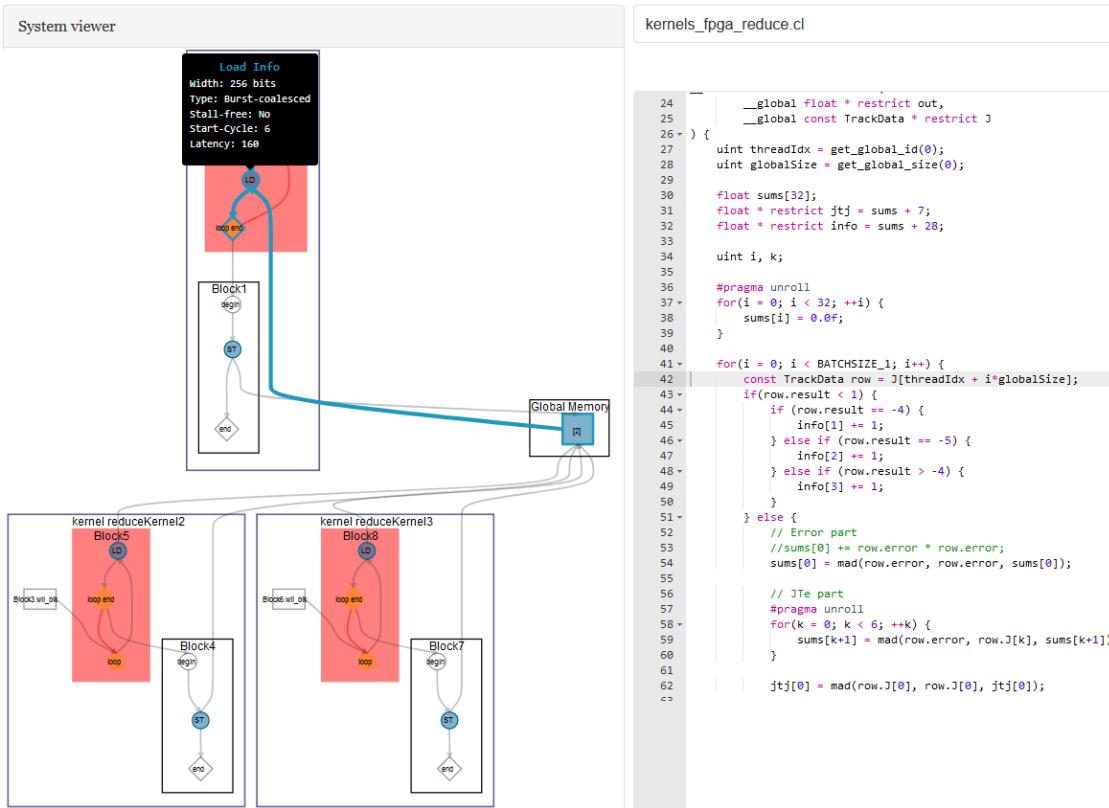

| Figura 16 | Informe de AOC con una vista del diseño creado por la FPGA . . . . .                                                                                                                                                                 | 49 |

|           |                                                                                                                                                                                          |    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 17 | Informe de AOC con información detallada sobre cantidad y tipo de recursos utilizados por cada instrucción del kernel . . . . .                                                          | 49 |

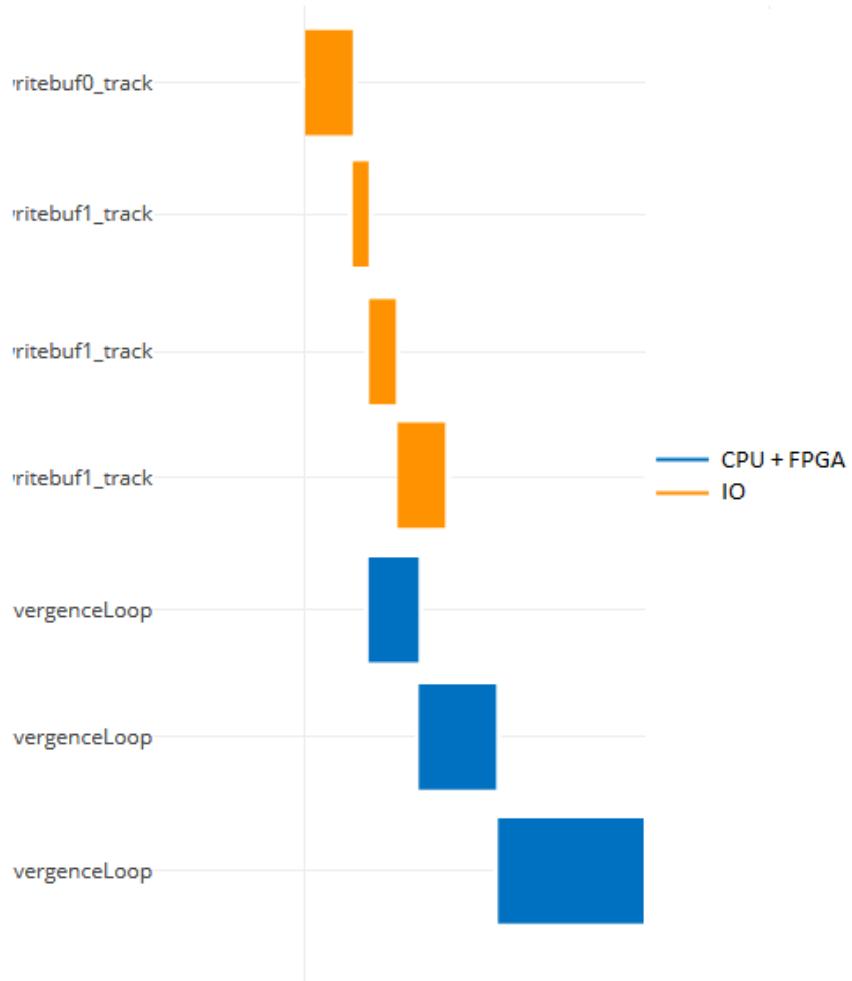

| Figura 18 | Tiempo desglosado de las etapas de <i>track</i> y <i>reduce</i> en la FPGA . . . . .                                                                                                     | 59 |

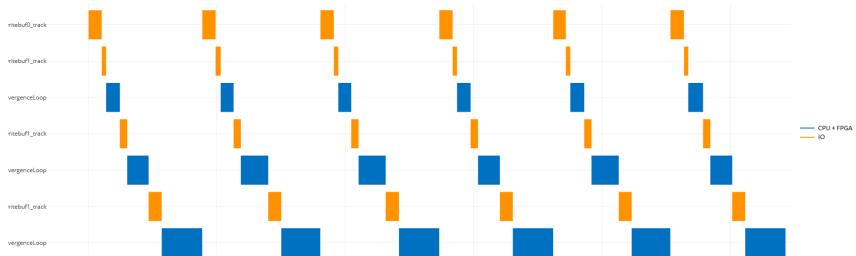

| Figura 19 | Tiempo desglosado de las etapas de <i>track</i> y <i>reduce</i> con solape entre <i>writebuf1_track</i> de un nivel de la pirámide y <i>convergenceLoop</i> del siguiente . . . . .      | 60 |

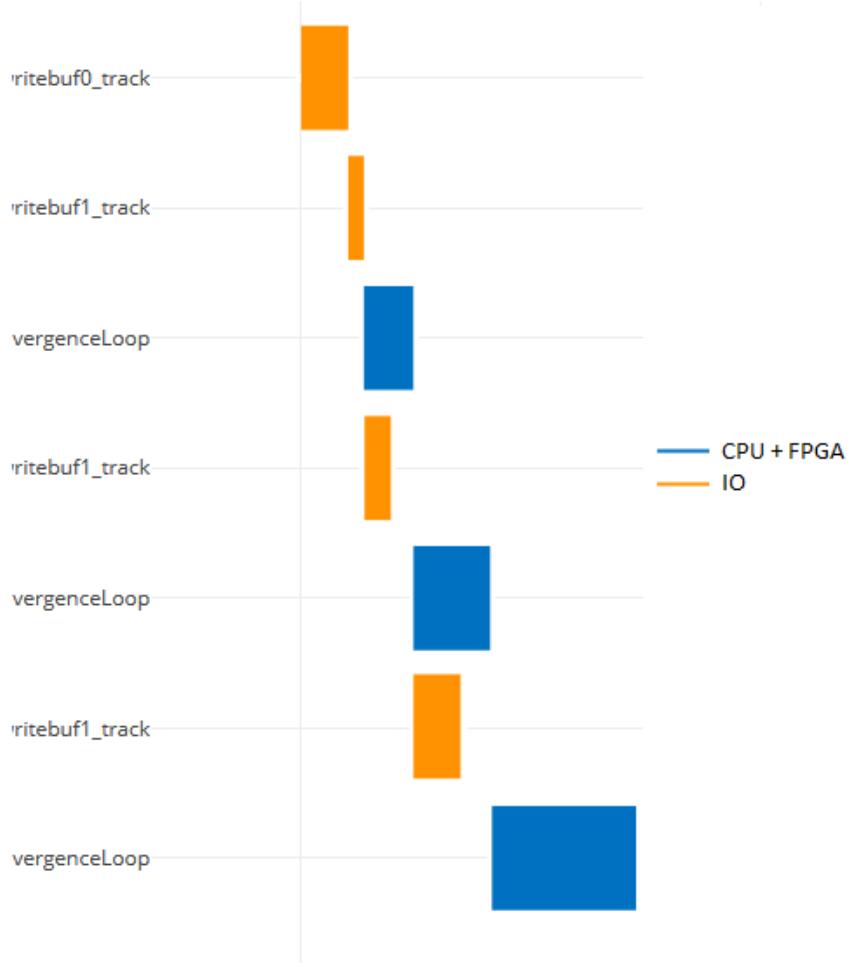

| Figura 20 | Tiempo desglosado de las etapas de <i>track</i> y <i>reduce</i> con solape entre <i>writebuf1_track</i> y <i>convergenceLoop</i> , independientemente del nivel de la pirámide . . . . . | 61 |

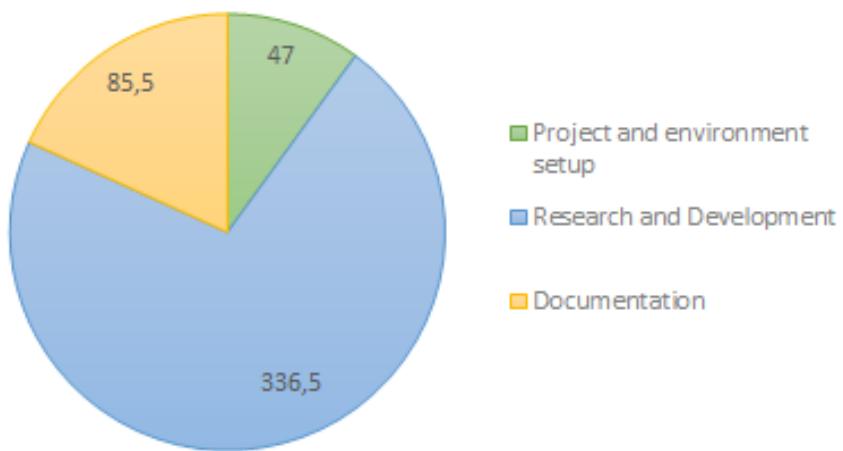

| Figura 21 | Esfuerzos invertidos (en horas) en cada tarea a lo largo de este trabajo . . . . .                                                                                                       | 62 |

## ÍNDICE DE TABLAS

---

|         |                                                                                                                                                        |    |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tabla 1 | Plataformas disponibles durante el proyecto . . . . .                                                                                                  | 19 |

| Tabla 2 | Tiempo (ms) de ejecución de kernel en la versión original de OpenCL . . . . .                                                                          | 24 |

| Tabla 3 | Tiempo total (ms) en la versión original de OpenCL                                                                                                     | 25 |

| Tabla 4 | Resumen del impacto en el tiempo de ejecución (ms) de todas las optimizaciones en la FPGA . . . . .                                                    | 37 |

| Tabla 5 | Porcentaje de uso de recursos en la FPGA de Socarrat de la versión original . . . . .                                                                  | 50 |

| Tabla 6 | Porcentaje de uso de recursos en la FPGA de DE1SoC de la versión original . . . . .                                                                    | 51 |

| Tabla 7 | Tamaños de buffers (MB), tiempos de IO (s) y anchos de banda (MB/s) del kernel de <i>reduce</i> para todos los dispositivos de la plataforma . . . . . | 55 |

## LISTINGS

---

|                                               |    |

|-----------------------------------------------|----|

| src/OpenCL_sample_host.c . . . . .            | 45 |

| src/OpenCL_sample_device.c . . . . .          | 47 |

| src/OpenCL_original_reduce_kernel.c . . . . . | 52 |

| src/OpenCL_sample_built-in_opt.c . . . . .    | 56 |

## INTRODUCCIÓN

---

La evolución en la capacidad de cómputo de los procesadores de propósito general ha sido exponencial desde los años 60. Desde entonces el tamaño de los transistores se ha ido reduciendo progresivamente. Tal y como determinó Moore [15], este hecho hacía posible doblar la cantidad de transistores que contenían los *chips* en cada una de estas “iteraciones” de dos años - observación denominada ley de Moore. A su vez, ésto permitía reducir el voltaje y corriente necesario para que los transistores puedan funcionar correctamente. En línea con esto, se podía incrementar la frecuencia de reloj del *chip* (es decir, aumentar el número de instrucciones ejecutadas por unidad de tiempo) manteniendo constante la densidad de potencia (i.e. potencia disipada por unidad de superficie) entre iteraciones. Estas son las reglas de escalado que explicó Dennard con mayor detalle en su trabajo [4].

Sin embargo, desde aproximadamente el año 2005 [13], debido a ciertas limitaciones tecnológicas ya no es posible reducir en la misma medida el tamaño de los transistores, así como el voltaje y corriente que se les aplica. Esto ha provocado una deceleración en la densidad de transistores respecto a la ley de Moore, mostrado en la Figura 1. Además, el fin del escalado de Dennard conlleva que la densidad de potencia aumente desde entonces, como se puede ver en la Figura 2. Esto significa que aumentar la frecuencia de reloj (en el paso de una generación de procesadores a otra) implicaría generar más calor que los sistemas de refrigeración no serían capaces de soportar. Es por ello que, para solventar este problema, emergió el modelo del procesador *multicore*, es decir, disponer de varios procesadores a una frecuencia moderada con hilos de ejecución paralelos. Esto sustituye al modelo tradicional en el que se dispone de un único procesador a alta frecuencia.

No obstante, los avances en múltiples campos, como la visión por computador, han conducido al desarrollo de algoritmos complejos con altos requerimientos en capacidad de cómputo. En ocasiones, estos algoritmos son implementados en sistemas empotrados con limitaciones en cuanto al consumo de energía. Es el caso de las aplicaciones SLAM (*Simultaneous Localization And Mapping*), mediante las cuales un sistema autónomo es capaz de crear un mapa 3D de su entorno al mismo tiempo que se desplaza a través de él.

En este contexto, una aplicación SLAM debe cumplir con diversos requisitos:

- Ser precisa en los cálculos realizados para construir el mapa 3D.

Figura 1: Deceleración de la densidad de transistores respecto a la ley de Moore - A New Golden Age for Computer Architecture [12]

Figura 2: Evolución de la densidad de potencia vs. tecnología - A New Golden Age for Computer Architecture [12]

Figura 3: Flexibilidad y facilidad de uso frente a rendimiento y eficiencia energética según el tipo de dispositivo

- Garantizar un rendimiento mínimo, dadas las restricciones temporales.

- Tener un bajo consumo, debido a las limitaciones de las baterías que se usan en estos sistemas autónomos.

En muchos casos, los procesadores *multicore* (de propósito general) no satisfacen los estrictos requerimientos de este tipo de aplicaciones. La conclusión de Hennessy y Patterson a este respecto [12] es que, para afrontar este problema, es necesario usar los transistores de manera más eficiente, construyendo dispositivos especializados en vez de dispositivos de propósito general, a cambio de perder flexibilidad. Tal y como ilustra la Figura 3, por lo general cuanto más especializado sea el dispositivo mejor rendimiento y consumo energético tendrá a costa de perder flexibilidad y facilidad de uso, si bien es cierto que existen raras ocasiones en las que esto no se cumple.

A raíz de esta necesidad nace el concepto de sistemas heterogéneos, es decir, compuestos por diversos tipos de dispositivos de procesamiento especializados cada uno de ellos en realizar tareas concretas. Por ejemplo, Google diseñó en 2017 las *Tensor Processing Units* (TPUs), un acelerador específico para realizar funciones comunes en redes neuronales (inteligencia artificial), en concreto un *Application Specific Integrated Circuit*<sup>1</sup> (ASIC). Estos dispositivos son usados en sus propios servicios como Google Translator o el buscador de Google, además de ponerlos a disposición en sus servicios *Cloud* para el uso por cualquier persona. Esto es debido a que, como demuestran Sato [21] y Jouppi [14], tienen una relación rendimiento/consumo mucho mayor que las CPUs y GPUs más modernas, en ocasiones incluso más de dos órdenes de magnitud mayor.

<sup>1</sup> circuito integrado para cumplir una función específica sin poder ser reprogramado

## 1.1 OBJETIVO

A raíz del reto de programar para sistemas heterogéneos y caracterizarlos nace SLAMBench [17], un benchmark para el popular algoritmo SLAM denominado KinectFusion (abreviado KFusion) [18], ideado por Microsoft. SLAMBench permite medir tanto la precisión como el rendimiento de KFusion. El *benchmark* proporciona una implementación de KFusion para diversos tipos de sistemas, como por ejemplo para sistemas heterogéneos. Esto es de utilidad a la hora de evaluar y optimizar KFusion, con el fin de cumplir con los requerimientos mencionados con anterioridad.

Este trabajo se enfoca concretamente en analizar y comprender el comportamiento de una carga de trabajo significativa, como SLAMBench, en sistemas heterogéneos con dispositivos de tipo FPGA (*Field-programmable gate array*). Uno de los objetivos principales es estudiar la viabilidad de este tipo de dispositivos en comparación con otros (descritos más adelante), dado que tienen mayor potencial en términos de eficiencia energética. Adicionalmente, se estudiará cualquier posible modificación que pueda hacerse sobre la implementación original con el fin de mejorar sus resultados en sistemas heterogéneos, sin alterar el comportamiento del algoritmo en sí.

## 1.2 ALCANCE

El alcance de este proyecto comprende los siguientes puntos:

- Comprender qué hace KFusion e identificar los posibles *hotspots*.

- Estudiar el comportamiento y la viabilidad de SLAMBench en un sistema 3-heterogéneo (i.e. tres tipos de dispositivos), poniendo especial atención en dispositivos de tipo FPGA. Esta configuración contrasta con el Estado del Arte en sistemas heterogéneos, donde prácticamente siempre se utilizan únicamente dos dispositivos.

- Estudiar el impacto de posibles optimizaciones sobre los *hotspots* en base a los criterios previamente descritos, implementarlos y analizar sus resultados.

## 1.3 ESTRUCTURA DEL DOCUMENTO

A partir de este punto, el documento se estructura en los siguientes capítulos:

2. **Sistemas heterogéneos: Estado del Arte**, para detallar el concepto de heterogeneidad en este contexto y, desde esta perspec-

tiva, dar a conocer el estado de los sistemas heterogéneos al comienzo de este proyecto.

3. **Trabajos relacionados** que sirvan de referencia para la temática de este proyecto. Esto incluye describir a grandes rasgos estos trabajos, así como clarificar todo aquello que sea de utilidad de cara a mejorar cualquier aspecto este proyecto.

4. **SLAMBench**: capítulo que describe los aspectos más importantes del *benchmark* con el que se trabaja durante todo el proyecto.

5. **Herramientas y metodología de trabajo**: describir las herramientas usadas a largo de este proyecto (*hardware* y *software*) para facilitar la comprensión de los resultados y la reproducibilidad de los experimentos. Así pues, también se detallan los procedimientos seguidos a la hora de realizar ciertas tareas de interés.

6. **Técnicas exploradas para optimizar kernels**: estudio de las diversas mejoras implementadas para acelerar KFusion especialmente sobre una FPGA. Esto incluye el análisis de la versión original de KFusion, así como el desarrollo y análisis de los resultados de estas optimizaciones.

7. **Conclusiones y Trabajo futuro**: utilidad de este trabajo de investigación, principalmente poniendo el foco en describir a grandes rasgos lo que aporta a lo ya existente en la literatura. Aspectos de interés que no se han llevado a cabo pero que serían de utilidad para alcanzar los objetivos planteados.

8. **Apéndices**: detalles referenciados a lo largo del documento.

## 2.1 HETEROGENEIDAD

Los sistemas heterogéneos se distinguen por estar formados por diversos dispositivos (*devices*) de distintas características (organización, arquitectura, frecuencia de reloj, rendimiento, ancho de banda, consumo energético...) con fines distintos. Además, se caracterizan por seguir el modelo *host-device*, en el que coexisten estos dispositivos funcionan como unidades de cómputo a disposición de un anfitrión (*host*), que hace de "coordinador". Esto es, el *host* es quien decide en qué momento y qué tareas manda a los *devices*. Como se puede observar en la Figura 4, existe una memoria global que comparten todos los dispositivos de la plataforma, es decir, *host* y dispositivos (*compute devices*). Cada dispositivo se divide en unidades de cómputo (*compute units*), que a su vez se divide en elementos de procesamiento (*processing elements*, PE). Además, hay zonas de memoria, denominada memoria local, que sólo son visibles para los elementos de procesamiento de una misma unidad de cómputo. Adicionalmente, cada elemento de procesamiento dispone de una memoria privada. Por último, como se puede apreciar en la imagen, también existen zonas de memoria constante usada exclusivamente y optimizada para lecturas.

Ejecutar un algoritmo complejo en un sistema de estas características explotando adecuadamente todos los dispositivos es un problema difícil. De hecho, se puede abordar siguiendo diversas estrategias, como por ejemplo minimizando el tiempo que los dispositivos están ociosos. Otra alternativa es dividir el problema en etapas y ejecutar cada una en aquel dispositivo que mejor se adapta a sus necesidades, simulando un *pipeline*. Son muchos los factores que influyen en determinar cuál es la mejor estrategia y cómo implementarla, ya que cada dispositivo tiene distintas características.

Como se ha mencionado con anterioridad, algunas aplicaciones de campos como la visión por computador o la robótica tienen requerimientos muy exigentes en cuanto a rendimiento y/o consumo. Este problema suele resolverse utilizando sistemas heterogéneos que disponen de un procesador de propósito general (denominado *Central Processing Unit*, CPU) junto a otro procesador que funciona a modo de acelerador. Este acelerador suele ser una GPU o una FPGA. No obstante, dada la complejidad que adquieren ciertos algoritmos como KFusion y la diversidad de estructuras de datos y patrones de paralelismo de los que hacen uso, algunos de estos sistemas heterogéneos no son capaces de satisfacer los requerimientos de estas aplicaciones.

Figura 4: Modelo *host-device* - Opencl 2.2 Specification [7]

Esto es debido a que es bastante difícil adecuar la totalidad del algoritmo a un sistema 2-heterogéneo (i.e. que tiene a su disposición 2 dispositivos distintos, normalmente CPU-GPU o CPU-FPGA). Este es el principal problema que se intenta atajar en este trabajo, poniendo el foco especialmente en intentar sacar partido de la FPGA y llevando a cabo una implementación de KFusion en un sistema 3-heterogéneo compuesto de una CPU, una GPU y una FPGA.

## 2.2 HARDWARE

En esta sección se describe el modelo de ejecución de los dos principales aceleradores que se usan en sistemas heterogéneos: GPU y FPGA. La Figura 5 muestra un ejemplo para ambos dispositivos en el que se manda ejecutar 6 veces un *kernel* (un trabajo o función) que tiene 5 etapas. En el eje X se muestra la evolución en el tiempo, en este caso medido en ciclos de reloj del dispositivo. En cada casilla, se muestra como número el identificador de ejecución del *kernel*, mientras que la letra representa la etapa en la que se encuentra dicha ejecución. Como se puede observar, la GPU es capaz de ejecutar de forma paralela 3 ejecuciones del mismo *kernel*, que avanzan de manera simultánea en cada ciclo de reloj. Una vez han finalizado, comienzan las siguientes 3 ejecuciones del *kernel*, de nuevo, de manera paralela. En cambio, tal y como se puede observar, la FPGA funciona como un procesador segmentado, en el cual todas las instrucciones avanzan cada ciclo hacia la etapa siguiente. Este concepto es importante, dado que, igual que en las CPUs, una instrucción puede quedarse en una

|                                              |        |        |        |        |        |        |        |        |        |        |

|----------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| SIMD<br>Parallelism<br><br><b>(GPU)</b>      | 1<br>A | 1<br>B | 1<br>C | 1<br>D | 1<br>E | 4<br>A | 4<br>B | 4<br>C | 4<br>D | 4<br>E |

|                                              | 2<br>A | 2<br>B | 2<br>C | 2<br>D | 2<br>E | 5<br>A | 5<br>B | 5<br>C | 5<br>D | 5<br>E |

|                                              | 3<br>A | 3<br>B | 3<br>C | 3<br>D | 3<br>E | 6<br>A | 6<br>B | 6<br>C | 6<br>D | 6<br>E |

| <b>Clock Cycle</b>                           | 1      | 2      | 3      | 4      | 5      | 6      | 7      | 8      | 9      | 10     |

| Pipeline<br>Parallelism<br><br><b>(FPGA)</b> | 1<br>A | 2<br>A | 3<br>A | 4<br>A | 5<br>A | 6<br>A |        |        |        |        |

|                                              |        | 1<br>B | 2<br>B | 3<br>B | 4<br>B | 5<br>B | 6<br>B |        |        |        |

|                                              |        |        | 1<br>C | 2<br>C | 3<br>C | 4<br>C | 5<br>C | 6<br>C |        |        |

|                                              |        |        |        | 1<br>D | 2<br>D | 3<br>D | 4<br>D | 5<br>D | 6<br>D |        |

|                                              |        |        |        |        | 1<br>E | 2<br>E | 3<br>E | 4<br>E | 5<br>E | 6<br>E |

|                                              |        |        |        |        |        |        |        |        |        |        |

Figura 5: Comparación de paralelismos SIMD vs Pipeline - OpenCL on FPGAs for GPU Programmers

etapa durante varios ciclos, bloqueando el resto de instrucciones que la siguen en el *pipeline*.

### 2.2.1 GPU

Las *Graphics Processing Unit* (GPU) son aceleradores dedicados principalmente, aunque no únicamente, al procesamiento de gráficos y cálculos en coma flotante. Se caracterizan por contener un número grande de núcleos que ejecutan instrucciones de forma paralela. Debido a esta característica, son dispositivos ideales para ejecutar aplicaciones “embarazosamente paralelas” (o *embarrassingly parallel* por su traducción del inglés), es decir, aquellas en las que la carga de trabajo sea fácilmente separable en multitud de “subtrabajos” y que éstos sean poco dependientes o independientes entre sí.

Para comprender mejor la arquitectura de una GPU, formulemos el modo de calcular su *throughput*<sup>1</sup>. Con el fin de simplificar, vamos a obviar situaciones como esperas por operaciones de memoria, *barriers*<sup>2</sup>, etc. Así pues, podríamos concluir con la siguiente fórmula:

Throughput = BytesPerWorkItem \* Frequency

- **Throughput**: rendimiento medido en *bytes* por segundo.

- **BytesPerWorkItem**: trabajo en *bytes* que es capaz de producir un “trabajador”.

<sup>1</sup> rendimiento o cantidad de trabajo capaz de resolver por unidad de tiempo

<sup>2</sup> punto de sincronización que obliga a esperar a que todos los *threads* hayan llegado este punto

- **Frequency:** frecuencia de reloj de la FPGA en hertzios (ciclos por segundo).

### 2.2.2 *FPGA*

Las *Field-Programmable Gate Array* (FPGA) son dispositivos que contienen circuitos lógicos reprogramables. El paralelismo de este tipo de dispositivos es diferente, ya que se caracterizan por tener una estructura de *pipeline* como se puede ver en la Figura 5, similar a la arquitectura segmentada de una CPU.

En el caso ideal, el *throughput* de una FPGA podría medirse de la siguiente manera:

Throughput =

$$\text{BytesPerWorkItem} * (\text{Frequency} / \text{max(InitiationInterval)})$$

El **initiation interval** es el número de ciclos que tarda una iteración de un bucle en ejecutarse (cada bucle puede tener un initiation interval distinto). En la ecuación se tiene en cuenta el máximo *initiation interval* ya que es el perteneciente al bucle que retrasará las instrucciones que se encuentren en etapas anteriores del *pipeline*.

En el ámbito de la programación para FPGAs, existen los *Hardware Description Languages* (HDL), lenguajes como *VHDL* o *Verilog* que permiten programar FPGAs a bajo nivel, definiendo la estructura de los circuitos digitales y de sus señales. Aunque esto ofrece la oportunidad de afinar una aplicación con alto grado de detalle, también hay que considerar el tiempo de desarrollo, que puede aumentar de forma notable en función de la complejidad de la aplicación.

No obstante, gracias al proceso de HLS (*High Level Synthesis*), es posible generar automáticamente un diseño en código HDL para la FPGA a partir de un comportamiento programado en un lenguaje de más alto nivel como C, C++ o OpenCL. Esto facilita el desarrollo para FPGAs y abre la puerta a una mayor comunidad de desarrolladores, puesto que los HDLs tienen una curva de aprendizaje muy pronunciada.

## 2.3 SOFTWARE

En este apartado se justifica y describe el *software* con el que sea posible explotar las capacidades del *hardware* disponible. En este sentido y dado el alcance del proyecto, la opción idónea es OpenCL, principalmente debido a que es necesario una interfaz o lenguaje compatible con todos los dispositivos de los que se compone la plataforma heterogénea.

### 2.3.1 OpenCL

OpenCL es un *framework* que ofrece una interfaz (*Application Programming Interface, API*) basada en el lenguaje de programación C99, para programar aplicaciones que hagan uso de diversos dispositivos en una plataforma heterogénea. La mayor ventaja es que define un lenguaje común de alto nivel para varios tipos de dispositivos. Esto significa que es posible programar en OpenCL para CPU, GPU y FPGA a la vez, siempre que los fabricantes (*vendors*) de estos dispositivos provean de un *driver* de OpenCL para hacer uso de ellos. Desde este punto de vista, un caso opuesto a OpenCL es CUDA, una API también basada en C99, pero con la que únicamente es posible usar GPUs de NVIDIA.

Programar para FPGAs con OpenCL también es una ventaja en términos de tiempo de desarrollo, frente a usar directamente un HDL, ya que existen herramientas que aplican el proceso HLS mencionado anteriormente: analizan este lenguaje de alto nivel y generan el diseño *hardware* correspondiente.

En el apéndice A.1 se muestra un ejemplo de una aplicación que usa OpenCL, acompañada de comentarios para facilitar su comprensión.

### 2.3.2 Altera Offline Compiler

El compilador offline de Altera (AOC por sus siglas en inglés) es una herramienta necesaria para poder utilizar OpenCL con FPGAs de Altera, de la empresa Intel. El propósito de esta herramienta es realizar el proceso de HLS para FPGAs de este fabricante, es decir, en base al código OpenCL que se necesita ejecutar en el *device*, generar un diseño e implementación en la FPGA en términos de puertas lógicas. Esta implementación se almacena en un fichero binario que en tiempo de ejecución se carga en la FPGA.

Generar el fichero binario es una tarea que requiere un tiempo considerable para el compilador, que depende de la complejidad del código y de la capacidad en recursos de la FPGA. Para el caso que nos ocupa y dependiendo del código OpenCL compilado, el AOC puede tardar entre 45 minutos y 1 hora y media en analizar el código, crear un diseño y generar la implementación para las FPGAs usadas en este trabajo. No obstante, esta herramienta trae consigo utilidades que permiten emular el comportamiento del código OpenCL en las FPGAs. Esto facilita la tarea de desarrollo, ya que es posible **validar** el comportamiento y resultado de la aplicación sin necesidad de compilar. También es capaz de generar informes sobre el código OpenCL, sin necesidad de compilar. Estos informes sirven para analizar en detalle cómo funcionará cada porción del código OpenCL en la FPGA, con el fin de mejorar si es posible la implementación.

Figura 6: OpenCL FPGA Programming flow - Intel FPGA SDK for OpenCL Pro Edition Programming Guide [10]

La Figura 6 ilustra cómo se trabaja con OpenCL y el AOC para usar FPGAs de Altera. Los distintos ficheros OpenCL, que contienen todos los *kernel*s que van a ejecutar los dispositivos, sirven de entrada para el AOC y su proceso de HLS. Aunque en la imagen no se puede observar, durante el proceso de compilación se generan ficheros que contienen código en un HDL con un diseño a nivel de *hardware*. Finalmente se generan un fichero binario con extensión .aocx y otro .aoco que sirven para reprogramar la FPGA en tiempo de ejecución con este diseño. Por su parte, el código C/C++ del anfitrión, haciendo uso de librerías de OpenCL, carga estos binarios durante la ejecución del programa y hace uso de las FPGAs.

TRABAJOS RELACIONADOS

---

En este capítulo se presentan trabajos importantes de ejecución desde lenguajes de alto nivel en GPU y FPGAs, con el fin de dar a conocer el contexto de los sistemas heterogéneos en general y del uso de estos dispositivos en particular. Además, en capítulos posteriores también se harán referencias a trabajos que están más íntimamente relacionados con este proyecto.

Tal y como describe Muslim [16], las GPUs ofrecen alto rendimiento en operaciones de coma flotante y gran ancho de banda en transacciones de memoria. Por el contrario, las FPGAs se caracterizan, entre otras cosas resumidas por Muslim [16] y Demirsoy [2], por ofrecer una buena relación entre el rendimiento y consumo de energía. OpenCL y el compilador *offline* de Altera son las herramientas principales usadas hoy en día por la comunidad de desarrolladores con el objetivo de alcanzar un buen ratio rendimiento/consumo en este tipo de dispositivos. Existen múltiples optimizaciones (Singh [5]) que pueden aplicarse a diversidad de aplicaciones con el fin de maximizar este ratio. Además, como ilustra Denisenko [3], la creación de un lenguaje de alto nivel como es OpenCL abre la puerta a mayor número de desarrolladores, ya que no es necesario tener un conocimiento detallado tanto del hardware como de las herramientas y flujo de trabajo tradicionales con FPGAs. Al mismo tiempo, incrementa la productividad del desarrollador al utilizar un entorno de desarrollo más familiar. Asimismo, otro de los beneficios de OpenCL es que el código es *cross-platform*<sup>1</sup>. No obstante, a la hora de implementar una aplicación en OpenCL, el desarrollador ha de ser consciente del tipo de dispositivo subyacente, ya que una porción de código OpenCL que da buenos resultados en una GPU no tiene por qué funcionar bien en una FPGA.

Hay muchos ejemplos del éxito de ciertas aplicaciones en FPGAs a CPUs y GPUs. Es el caso de la implementación de *Stencil*<sup>2</sup> llevada a cabo por Jia [11], en la que consigue una mejora de dos órdenes de magnitud en el rendimiento respecto a la versión original del algoritmo. Además, es capaz de caracterizar el sistema de memoria de la FPGA, observando su comportamiento al hacer uso de la memoria local, de las capacidades de vectorización, etc. Otro ejemplo de *Stencil* es el realizado por Waidyasoorya [24], en el que se compara su rendimiento frente a GPUs y CPUs en el ámbito de aplicaciones como el método de Jacobi, la ecuación de Laplace o el método de las Diferen-

---

<sup>1</sup> el mismo código puede usarse en diferentes plataformas o entornos

<sup>2</sup> patrón de cálculo geométrico mediante el cual se computa iterativamente el valor de un punto dados los puntos adyacentes

cias Finitas en el Dominio del Tiempo (todos usan *Stencil*). También se describen los factores que de alguna manera acotan el rendimiento en cada uno de los casos, como puede ser el límite de recursos de la FPGA o el bajo ancho de banda de acceso a memoria.

El trabajo de Tang [22] enseña los resultados de una implementación de K-means que realiza una parte del algoritmo en la CPU y otra en la FPGA, de tal manera que se maximiza el rendimiento global. Adicionalmente, compara el rendimiento y consumo de la FPGA frente a una CPU y una GPU. Sin embargo, es necesario tener en cuenta que en este caso la FPGA dispone de tecnología mucho más moderna que los otros dos dispositivos, por lo que la comparativa podría estar de alguna forma sesgada en beneficio de la FPGA.

Pu [19] hace lo mismo con el algoritmo *K-Nearest neighbors* (KNN), aunque en este caso existe equilibrio entre los tres dispositivos. De nuevo, se describen las distintas optimizaciones que han llevado a la mejor versión de KNN para la FPGA. Termina mostrando los resultados en los que se aprecia que el rendimiento de la GPU es el mayor de todos y, en concreto, tres veces mayor que el la FPGA. Sin embargo, la FPGA a su vez consigue un rendimiento por consumo 3 veces mayor que el de la GPU.

Por último, Verma [23] presenta un caso de estudio similar con el benchmark *OpenDwarfs*. Uno de los puntos interesantes que trata son algunas de las limitaciones que tiene el compilador de Altera ([1]) a la hora de aplicar heurísticas y estimar el uso de recursos, ya que esto no siempre genera la mejor configuración hardware para la FPGA. Por lo tanto, es conveniente que el desarrollador sea consciente de estas limitaciones y sepa actuar en consecuencia para dar información adicional al compilador y evitar estas situaciones.

Todos estos trabajos vienen a demostrar que las FPGAs pueden competir con las GPUs, que es el tipo de dispositivo que tradicionalmente ha abarcado gran parte del mercado de los aceleradores.

# 4

## SLAMBENCH

---

Los trabajos en el campo de visión por computador suelen poner de manifiesto problemas a la hora de resolver de poner en práctica de manera eficiente algoritmos como KFusion [18]. Además, se puede observar que el foco de los autores en este sentido es siempre desarrollar una implementación adecuada para GPUs. Sin embargo, como se ha mencionado con anterioridad, es posible que existan otros aceleradores (las FPGAs en el caso que nos ocupa) que resuelvan de mejor manera las necesidades computacionales o de consumo en ciertas situaciones. Con el propósito de medir estas necesidades y aprovechar distintas formas de paralelismo en diversos tipos de dispositivos (con OpenCL, CUDA, OpenMP, ...) surge el benchmark SLAMBench [17]. Este benchmark está preparado para ejecutarse con el *dataset* ICL-NUIM [8] como entrada de datos, ampliamente utilizado en benchmarks de aplicaciones SLAM.

El trabajo realizado por Sergio Iannace [9], basado en SLAMBench e íntimamente relacionado con este proyecto, presenta determinadas optimizaciones sobre las etapas de KFusion, usando OpenCL para en FPGAs. En este contexto, justifica que puede ser idóneo hacer uso de FPGAs en ciertas situaciones, frente al uso tradicional de GPUs. Esto sirve como fundamento para el comienzo de este proyecto y es una de las principales referencias durante el desarrollo del mismo.

### 4.1 KINECTFUSION

KFusion es un algoritmo que, a partir de los *frames* o imágenes tomadas sucesivamente por una cámara, calcula la trayectoria de esta cámara en el espacio y construye un volumen 3D. El algoritmo produce un resultado como el que aparecen en la Figura 7. En la fila superior se puede observar la evolución de la trayectoria de la cámara conforme se mueve en torno a un punto, mientras que en la fila inferior se aprecia el volumen 3D obtenido a partir de las imágenes. La primera columna corresponde al resultado de procesar dos tercios de la vuelta alrededor del punto. En la última columna se muestran los resultados correspondientes a una vuelta entera.

La implementación de KFusion proporcionada en SLAMBench se divide en las etapas mostradas en la Figura 8 (ejecutadas para cada imagen). Cada círculo corresponde a un kernel y su color indica la etapa a la que pertenece. Las flechas y sus etiquetas indican una dependencia entre kernels, siendo el origen de la flecha el productor y

Figura 7: Trayectoria y volumen calculados por KFusion a lo largo del tiempo - KinectFusion: Real-Time Dense Surface Mapping and Tracking [18]

el destinatario el consumidor. En resumen, estas son las etapas en las que se divide:

1. **Preprocesado de la imagen tomada** (color verde): se aplica un filtro bilateral para mejorar la detección de puntos de interés en etapas posteriores. El funcionamiento de este filtro se explica en el Apéndice A.2.

2. **Tracking** (color azul): detección de puntos característicos (esquinas, bordes...) y estimación de la nueva pose de la cámara. Esto es posible gracias a la correspondencia que es capaz de establecer entre puntos de una imagen y puntos de las anteriores imágenes. Sin aplicar el filtro bilateral esta etapa perdería precisión.

3. **Integrate** (color naranja): integración de los puntos característicos en la nube o volumen de puntos 3D. Este volumen es la estructura 3D que se va construyendo mientras se van tomando las imágenes.

4. **Raycast** (color rojo): traza rayos a los puntos para conocer si la superficie es visible o no.

5. **Rendering** (color amarillo): renderiza el volumen obtenido.

#### 4.2 BENCHMARK

SLAMBench es un benchmark que ofrece la posibilidad de evaluar el comportamiento de KFusion en diversas implementaciones:

- Secuencial en C++: utilizando un hilo de ejecución de la CPU.

Figura 8: Etapas en que las se divide KFusion

- OpenMP: aprovechando las capacidades *multicore* de la CPU.

- CUDA: usando únicamente GPUs de NVidia.

- OpenCL: usando únicamente un acelerador cualquiera compatible con OpenCL.

Uno de los objetivos principales de este proyecto es analizar e implementar en la FPGA aquellas partes del algoritmo KFusion que puedan ajustarse a las características de la FPGA, sin perder los beneficios que proporcionan tanto la CPU como la GPU. Esta es una de las razones por las que se escoge OpenCL como *framework* de trabajo en este proyecto, y que se detalla en el capítulo correspondiente.

## HERRAMIENTAS Y METODOLOGÍA DE TRABAJO

### 5.1 PLATAFORMAS DISPONIBLES

Con el fin de facilitar la comprensión de los tiempos obtenidos durante los experimentos y facilitar su reproducibilidad, en la Tabla 1 se presentan las características más relevantes de las plataformas de las que se disponen en la Tabla 1. Cabe destacar que la plataforma Socarrat es una estación de trabajo con una GPU y una FPGA discretas, mientras que la plataforma DE1-SoC integra una CPU y una FPGA en el mismo *chip*.

Tabla 1: Plataformas disponibles durante el proyecto

| Plataforma      | CPU         |                          |                           |                      |

|-----------------|-------------|--------------------------|---------------------------|----------------------|

|                 | GHz         | Núcleos                  | Threads                   | Memoria <sup>1</sup> |

| <b>Socarrat</b> | 4,2         | 4                        | 8                         | 64 GB                |

| <b>DE1-SoC</b>  | 2           | 2                        | 2                         | 1 GB                 |

| GPU             |             |                          |                           |                      |

|                 | GHz         | Núcleos                  | Conector                  | Memoria <sup>2</sup> |

|                 | 1           | 3072                     | PCIe 3.0 x16 <sup>3</sup> | 12 GB                |

| <b>DE1-SoC</b>  | N/A         | N/A                      | N/A                       | N/A                  |

| FPGA            |             |                          |                           |                      |

|                 | On/Out Chip | Conector                 | Memoria <sup>2</sup>      |                      |

|                 | Out of chip | PCIe 3.0 x8 <sup>4</sup> | 4 GB                      |                      |

| <b>DE1-SoC</b>  | On of chip  | N/A                      | 64 MB                     |                      |

<sup>1</sup> memoria global de la plataforma

<sup>2</sup> memoria integrada en el dispositivo

<sup>3</sup> velocidad máxima de 15,76 GB/s

<sup>4</sup> velocidad máxima de hasta 7,88 GB/s

Teniendo estas características en cuenta y que sería interesante experimentar con un sistema 3-heterogéneo, la principal plataforma de trabajo y donde se realizarán la mayoría de experimentos es **Socarrat**. Sin embargo, se ha de tener en cuenta que trabajar con ésta tiene los siguientes inconvenientes:

- Es compartida entre varios investigadores, por lo que los experimentos pueden ocasionalmente estar “contaminados”. No obs-

tante, para evitar esto, antes de realizar cualquier experimento se observará si el sistema está siendo usado por otra persona. Además, se realizará un número de ejecuciones determinado para cada experimento, siendo el resultado válido la media de todos ellos. También se pondrá especial atención al coeficiente de variación, que servirá como medida de la validez de los experimentos.

- No es un sistema del todo equilibrado, ya que, tal y como se verá en capítulos posteriores, la FPGA está muy por detrás en capacidad de cómputo.

La totalidad de los experimentos presentados en este trabajo corresponden a ejecuciones con la versión 17.0 del AOC y del *runtime* de OpenCL de Altera, excepto para la plataforma DE1SoC que sólo dispone de la versión 16.0 del *runtime*. Los tiempos resultantes mostrados en este documento están en milisegundos, a no ser que se mencione lo contrario. En todos los experimentos se utiliza el *dataset* ICL-NUIM 2 como entrada de datos. Dado que la ejecución con el *dataset* entero puede tardar varias horas (contiene 882 *frames*), todas las medidas corresponden a la media de 20 ejecuciones con los primeros 30 *frames* del *dataset* como entrada, que consideramos representativos. Además, las medidas mostradas para cada kernel corresponden a la ejecución de únicamente ese kernel en el dispositivo determinado, mientras que el resto de kernels son ejecutados en el *host*. La razón detrás de esto es que así se puede ver cuánto se tarda en la transferencia de datos de entrada y salida entre *host* y *device* para cada kernel, ya que es algo que también hay que valorar para una implementación en un sistema heterogéneo, donde no todos los kernels se ejecutan en el mismo dispositivo. Si se ejecutaran todos los kernels en, por ejemplo, la GPU, únicamente habría transferencia de datos al inicio (envío de los datos de entrada desde el *host* a la GPU) y al final del algoritmo (envío de los resultados desde la GPU al *host*).

## 5.2 FLUJO DE TRABAJO CON LA FPGA

Gracias a las guías de mejores prácticas que proporciona Intel [1], se han tenido en cuenta la gran mayoría de herramientas proporcionadas para desarrollar la versión óptima de un kernel. A partir de estas guías, se ha definido el proceso mostrado en el diagrama de flujo de la Figura 9, cuyos pasos son los siguientes:

1. Implementación del kernel.

2. Emulación del kernel para comprobar la validez de la implementación en cuanto a resultados.

3. Análisis del *informe* generado (ver Apéndice A.3). Si es posible mejorar el kernel entonces se vuelve al primer paso.

Figura 9: Flujo de trabajo con la FPGA

4. Generación de los ficheros binarios .aocx y .aoco.

5. Ejecución de la aplicación.

6. Análisis de las medidas obtenidas. Si no son aceptables se vuelve al primer paso con una implementación alternativa.

La mayor diferencia respecto al flujo de trabajo propuesto por Intel, es que en este caso no se hace uso del *profiler* del *Software Development Kit* (SDK) de Altera. Esta herramienta proporciona información muy detallada, por ejemplo sobre latencia de accesos a memoria, cuánto le cuesta a la FPGA ejecutar cada línea de código, etc. En definitiva, la herramienta se encarga de recolectar todos los datos con alto grado de detalle y finalmente obtener estadísticas relevantes sobre el comportamiento del dispositivo en tiempo de ejecución. La gran desventaja y principal razón por la que se prescinde de esta herramienta es que el tiempo de ejecución del programa se ve sensiblemente afectado, pues la permanente comunicación entre *host* y FPGA lo ralentiza notablemente. Es por ello que, en vez de usar esta herramienta, se ha modificado el *framework* de SLAMBench para crear un *profiler* propio y simple utilizando funciones de librerías estándar de C y de la librería de OpenCL. Así pues, se pueden obtener métricas similares con apenas impacto en el tiempo de ejecución.

# 6

## TÉCNICAS EXPLORADAS PARA OPTIMIZAR KERNELS

---

En este capítulo se explican las distintas técnicas exploradas para optimizar kernels y se analizan sus resultados en comparación con la implementación original. Aclarar que, como se verá en el apartado final, las técnicas se han aplicado de manera incremental, es decir, cada vez que se prueba una nueva técnica se “crea” una versión del código con esa y todas las anteriores que han mejorado el rendimiento de la aplicación. De esta forma la última versión tendrá todas las técnicas que han funcionado satisfactoriamente. Todas las optimizaciones que se han llevado a cabo y que se presentan en este capítulo están disponibles en un repositorio público [20].

### 6.1 CARACTERIZACIÓN DE KFUSION

Con el fin de comprender el funcionamiento de cada uno de los kernels de KFusion en términos de rendimiento y consumo de recursos se ha ejecutado la versión original de OpenCL del *benchmark*. Así pues, los resultados presentados en la Tabla 2 corresponden a los tiempos de ejecución de cada kernel en cada dispositivo. Asimismo, en la Tabla 3 se muestran el resultado de la suma del tiempo de transferencia de datos (*input/output*, IO) y del tiempo de ejecución del kernel en el dispositivo. En la Figura 10, se puede comparar para cada kernel la cantidad de tiempo que tarda la FPGA de Socarrat en transferir datos y ejecutar el propio kernel. La Figura 11 muestra los mismos datos para la GPU de Socarrat. Teniendo en cuenta estas dos gráficas, la diferencia entre el tiempo de IO y el de los propios kernels es notable en ambos FPGA y GPU.

Figura 10: Tiempos (ms) de la versión original del código de cada kernel OpenCL en la FPGA de Socarrat

Tabla 2: Tiempo (ms) de ejecución de kernel en la versión original de OpenCL

| Etapa     | Kernel          | Socarrat |                 |      | DE1-SoC |                 |

|-----------|-----------------|----------|-----------------|------|---------|-----------------|

|           |                 | CPU      | FPGA            | GPU  | CPU     | FPGA            |

| prepro    | mm2meters       | 8,3      | 9               | 0,3  | 75,5    | 19              |

|           | bilateralFilter | 715,2    | 201,4           | 4,8  | 13131   | 414             |

| track     | halfSample      | 2,7      | 12,9            | 0,5  | 25      | 77,7            |

|           | depth2vertex    | 13,4     | 15,3            | 1    | 196,7   | 36,8            |

|           | vertex2normal   | 21,1     | 23,9            | 1,6  | 444,5   | 172,9           |

|           | track           | 238,9    | 74,5            | 11,7 | 4955,5  | 426,6           |

|           | reduce          | 73       | 98,7            | 28,4 | 1411,9  | NA <sup>1</sup> |

| integrate | integrate       | 1115,6   | 1.728           | 6    | 19044   | 2734            |

| raycast   | raycast         | 3157     | 1689,4          | 6,9  | 24030,1 | NA <sup>1</sup> |

| render    | renderDepth     | 10,8     | 11,8            | 0,4  | 205,8   | 22,3            |

|           | renderTrack     | 4,8      | 14,6            | 0,5  | 229,9   | 43,3            |

|           | renderVolume    | 938,6    | NA <sup>1</sup> | 2    | 9003,1  | NA <sup>1</sup> |

<sup>1</sup> la FPGA no dispone de suficientes recursos para implementar el kernel

Figura 11: Tiempos (ms) de la versión original del código de cada kernel OpenCL en la GPU de Socarrat

Tabla 3: Tiempo total (ms) en la versión original de OpenCL

| Etapa     | Kernel          | Socarrat |                 |       | DE1-SoC |                 |

|-----------|-----------------|----------|-----------------|-------|---------|-----------------|

|           |                 | CPU      | FPGA            | GPU   | CPU     | FPGA            |

| prepro    | mm2meters       | 8,3      | 1332,9          | 8,8   | 75,5    | 364,4           |

|           | bilateralFilter | 715,2    | 1468,7          | 11,1  | 13131   | 657,4           |

| track     | halfSample      | 2,7      | 452             | 6,6   | 25      | 228,2           |

|           | depth2vertex    | 13,4     | 6381,3          | 18,69 | 196,7   | 149,2           |

|           | vertex2normal   | 21,1     | 345,7           | 16,04 | 444,5   | 665,9           |

|           | track           | 238,9    | 114910,8        | 219   | 4955,5  | 24767,4         |

|           | reduce          | 73       | 5521,5          | 111,5 | 1411,9  | NA <sup>1</sup> |

| integrate | integrate       | 1115,6   | 159111,2        | 368,6 | 19044   | 55826,4         |

| raycast   | raycast         | 3157     | 19830,6         | 309,8 | 24030,1 | NA <sup>1</sup> |

| render    | renderDepth     | 10,8     | 1279,1          | 9,7   | 205,8   | 270,7           |

|           | renderTrack     | 4,8      | 1694            | 0,6   | 229,9   | 987,8           |

|           | renderVolume    | 938,6    | NA <sup>1</sup> | 337,4 | 9003,1  | NA <sup>1</sup> |

<sup>1</sup> la FPGA no dispone de suficientes recursos para implementar el kernel

Cabe destacar que la GPU es el dispositivo más rápido en todos los kernels en términos de ejecución, llegando a ser dos órdenes de magnitud más rápida que la CPU y la FPGA en los kernels de *integrate* y *raycast*, que son los más lentos en estos dos dispositivos. No obstante,

si se suma el tiempo de IO la CPU es más rápida en los kernels de *mm2meters*, *halfSample*, *depth2vertex* y *reduce*. Esto es debido a que los cálculos no son lo suficientemente intensivos como para que merezca la pena que la GPU los resuelva, ya que el tiempo de IO entre *host* y GPU termina ocultando el tiempo de ejecución del kernel. Aún así, la suma de estos kernels apenas suponen un 6 % del tiempo de ejecución en la GPU, por lo que no merece la pena poner el foco en ellos, ya que cualquier optimización que se les aplique tendría un impacto muy pequeño en el tiempo global.

En general, se puede apreciar que los kernels que más tiempo consumen tanto en cálculo como en IO son *track*, *reduce*, *integrate* y *raycast*. Excepto *reduce* (ver código original en el Apéndice A.5), todos ellos tienen un alto “grado” de divergencia, es decir, existen multitud de caminos que los *threads* pueden tomar, debido mayormente a las cláusulas *if-else*. Si un *thread* toma un camino distinto al siguiente y ambos tardan tiempos distintos en sus caminos, llegará un momento en el que uno de ellos esté esperando al otro para converger (ver implementación del kernel de *integrate* como ejemplo). Este comportamiento es difícilmente evitable y es una de las principales razones por las que este proyecto se enfocará en optimizar el kernel de *reduce* para la FPGA. Además, en la Figura 12, donde se muestra para 30 frames la duración de cada etapa ejecutando todo el *pipeline* en la GPU, se puede observar que este kernel es el más costoso en cuanto a tiempo de ejecución (supone más del 40 % del tiempo de ejecución total del algoritmo). Finalmente, dado que implementa el patrón *reduce* (necesita muchos datos de entrada pero produce muy pocos de salida), es uno de los *kernels* que menos transferencia de datos necesita. Esto es importante, pues el tiempo de transferencia de datos supone una penalización importante a la hora de enviar tareas a los dispositivos y la FPGA en este kernel alcanza un ancho de banda total 3,5 veces menor que la GPU (ver Apéndice A.6). Es por ello que este kernel es el candidato ideal para ser optimizado.

Adicionalmente, en el Apéndice A.4 se explican los principales tipos de recursos de los que disponen las FPGAs y el porcentaje de uso de estos recursos en la versión original en ambas FPGAs.

## 6.2 TÉCNICAS EXPLORADAS

### 6.2.1 Memoria privada, local y global

En el modelo *host-device* de OpenCL existen tres tipos de memoria:

- **Global:** visible por el *host* y todos los dispositivos. Suele ser grande pero lejana, por lo que el acceso a esta memoria es costoso.

Figura 12: Duración de cada etapa ejecutando todo el *pipeline* de la versión original de OpenCL en la GPU

- **Local:** dentro del kernel, visible por todos los *work items* que pertenezcan a un mismo *work group*. Es más pequeña que la global, pero tiene menor latencia de acceso.

- **Privada:** dentro del kernel, visible sólo por un *work item*. Normalmente se sitúa en los registros del dispositivo, lo que significa que está a una distancia física muy corta (baja latencia), aunque son más limitados en cantidad. Esta es la memoria que se usa por defecto al declarar variables en el kernel.

Teniendo en cuenta estas características, es conveniente minimizar siempre los accesos a memoria global y usar siempre que sea posible la memoria privada. La memoria local podría usarse como cache de un grupo de *work items*. Un ejemplo de uso es la propia implementación original del kernel de *reduce* (ver Apéndice A.5). En esta implementación, cada *work item* resuelve un problema parcial y deja su resultado en memoria local. Finalmente, uno de los *work items* hace una reducción sobre todos estos cálculos parciales para obtener la solución al problema global.

Para definir una variable como memoria global o local es necesario añadir el modificador `_global` o `_local` al declarar la variable, como se mostrará en los ejemplos de las siguientes técnicas.

### 6.2.2 Parámetros attribute

En OpenCL es posible añadir al código directivas que proporcionen cierta información al compilador a la hora de asignar recursos a un kernel. Estas directivas son denominadas “atributos”. Algunos de los atributos que se han aplicado en la medida de lo posible son los siguientes:

- **REQD\_WORK\_GROUP\_SIZE:** Indica exactamente cuántos *work items* van a ser invocados para ejecutar un determinado kernel.

- **MAX\_WORK\_GROUP\_SIZE**: Indica cuántos *work items* como máximo van a ser invocados para ejecutar un determinado kernel.

- **NUM SIMD WORK ITEMS**: Con esto se aprovecha la capacidad de vectorización del dispositivo (*Single Instruction Multiple Data*, SIMD). Por ejemplo, si este atributo tiene valor “4” y los accesos a memoria por parte de los *work items* son consecutivos, entonces el compilador será capaz de vectorizar el acceso a memoria de manera que ejecutará una instrucción para cargar los datos correspondientes a 4 *work items*.

La siguiente porción de código muestra un ejemplo de uso de esta técnica:

```

__attribute__((reqd_work_group_size(64,1,1)))

__attribute__((num_simd_work_items(4)))

__kernel void vectsum(

__global const float * restrict a,

__global const float * restrict b,

__global float * restrict c

) {

size_t threadId = get_global_id(0);

c[threadId] = a[threadId] + b[threadId];

}

```

Esto indicará al compilador que realice operaciones vectoriales con un tamaño de 4 *floats*. Además, el compilador sabe que siempre se lanzarán 64 *work items* para este kernel. No obstante, en los experimentos realizados el uso de recursos de la FPGA no varía en función de estos parámetros, además de que no han resultado en una mejora sobre el rendimiento de la aplicación, por lo que es posible que el compilador haya ignorado estos atributos en el caso que nos ocupa.

### 6.2.3 Loop unrolling y loop pipelining

*Loop unrolling* consiste en, como su nombre indica, desenrollar iteraciones de un bucle, esto es, clonar el cuerpo del bucle tantas veces como indique el grado de desenrollado y ajustar el índice del bucle. Una de las ventajas de esto es que se reduce la lógica de control tantas veces como el grado de desenrollado. Suele combinarse con *loop pipelining*, de manera que si un bucle sigue el patrón LOAD-COMPUTE-STORE, al desenrollarlo 2 veces quedará como LOAD-LOAD-COMPUTE-COMPUTE-STORE-STORE. Así se consigue mayor rendimiento, ya que las latencias de memoria quedan ocultas. Es tarea del desarrollador definir el desenrollado de un bucle y es el AOC el que se encarga de crear la estructura de *pipeline* si es posible. Para desenrollar un bucle, han de cumplirse las siguientes condiciones:

- No debe haber dependencias entre iteraciones.

- El número de iteraciones debe ser conocido en tiempo de compilación.

- El dispositivo debe disponer de los recursos necesarios para clonar el cuerpo del bucle.

Un ejemplo de uso de *loop unrolling* es la siguiente porción de código:

```

#pragma unroll 4

for(int i=0; i<8; i++) {

sum += a[i]*b[i];

}

```

Esto sería traducido por el compilador a un código equivalente al siguiente:

```

for(int i=0; i<2; i+=4) {

sum += a[i]*b[i];

sum += a[i+1]*b[i+1];

sum += a[i+2]*b[i+2];

sum += a[i+3]*b[i+3];

}

```

Además, siguiendo el ejemplo anterior, si el compilador crea una estructura de *pipeline* entonces el resultado puede guardarse en el propio *pipeline* hasta el final del bucle, sin necesidad de entregar los datos a memoria en cada ciclo. Esto significa que los resultados de *sum* se acumularán en el *pipeline* hasta que termine la iteración, momento en el que se entregarán a la memoria global.

Como es de esperar, el uso de recursos aumentará en función del grado de desenrollado de los bucles. En el caso del kernel de *reduce*, el uso total de recursos en la versión original en la FPGA de Socarrat es de 33 %. Sin embargo, si se desenrollaran todos los bucles que cumplen las condiciones anteriormente mencionadas, este dato aumenta al 39 %. Aún así la mejora es inapreciable, probablemente debido a que estos bucles no tienen casi impacto en el tiempo de ejecución de este kernel.

#### 6.2.4 Patrón de acceso a memoria

Los patrones de acceso a memoria también son importantes a la hora de realizar optimizaciones. Tener un patrón de acceso aleatorio podría hundir el rendimiento de un aplicación, ya que no se aprovechan los mecanismos de *cache*. Por ello, siempre es ideal tener un patrón de acceso a posiciones de memoria consecutivas, que aproveche la localidad espacial o temporal de los datos para facilitar su reuso.

En este contexto surge el concepto de memoria coalescente. Cuando se realiza una operación de lectura de un dato, la memoria no

entrega únicamente ese, sino que entrega un bloque de datos consecutivos entre los que se encuentra el pedido. Es por ello que, si *work items* consecutivos piden datos que están contiguos en memoria, el rendimiento de la aplicación mejorará notablemente, ya que siempre se aprovecharán todos los datos que la memoria entrega. Además, se pueden combinar múltiples instrucciones de memoria en una única instrucción vectorial (SIMD).

A continuación se muestra un ejemplo de un acceso a memoria aleatorio frente a uno consecutivo:

```

// Unknown random memory access

for (int i=0; i<32; i++) {

int idx = a[i] + b[i];

c[idx] = c[idx]*d[idx];

}

// Consecutive memory access which can be coalesced

for (int i=0; i<32; i++) {

c[i] = a[i] * b[i];

}

```

El mejor patrón de acceso a memoria probado ha mostrado un *speedup* en el tiempo de ejecución del kernel de 1,22 en relación a la implementación original, principalmente a causa del acceso a memoria de forma coalescente mediante el cual siempre se aprovecha todo el bloque de datos leído de memoria. Por otro lado, en el tiempo de IO se ha conseguido un *speedup* de 1,08, gracias a que se ha reducido el tamaño del buffer de salida del kernel, aunque el tamaño del buffer de entrada sigue siendo considerablemente mayor. Esto es lógico, debido al propio patrón *reduce*.

#### 6.2.5 Memoria alineada

Las llamadas al sistema como *malloc* o *calloc*, no reservan memoria de forma alineada, lo que supone una penalización en el tiempo de IO en el caso de las FPGAs de Altera debido a restricciones de su *runtime*. Es por ello que en estos casos, el *runtime* muestra mensajes como éste: *\*\* WARNING: [aclo] NOT using DMA to transfer 2457600 bytes from device to host because of lack of alignment\*\* host ptr (0x7fadcc1a6d010) and/or dev offset (0x4e5800) is not aligned to 64 bytes*

Para evitar esto es posible reservar memoria de forma alineada con la llamada *posix\_memalign* en el código del *host* tal y como se muestra en el siguiente ejemplo:

```

// Unaligned:

// myHostBuffer = (float*) malloc(32 * sizeof(float));

// Aligned to 64 bytes:

posix_memalign((void **) &myHostBuffer, 64, 32 * sizeof(float));

```

Únicamente haciendo este cambio sobre para los buffers del kernel de *reduce* el tiempo de IO se redujo un 95 % para la FPGA, aunque para la GPU esta técnica no tiene ningún efecto.

### 6.2.6 Buffers de lectura/escritura

La API de OpenCL permite indicar si un buffer va a ser utilizado como sólo lectura, escritura o ambos. Esto proporciona información al compilador del host y al *driver* del device sobre cómo va a ser utilizado ese buffer y por lo tanto podría ser capaz de hacer ciertas optimizaciones. Por ejemplo:

- Si un buffer está marcado como “sólo lectura” el dispositivo podría situarlo en una zona de memoria constante, ya que tiene un acceso de lectura mucho más rápido que la memoria RAM.

- Si un buffer es “sólo escritura”, el *driver* del dispositivo podría decidir implementar un modelo de memoria *write-around*, es decir, todas las operaciones de memoria van a memoria principal sin pasar por *cache*. De esta forma, las operaciones sobre este buffer no ocuparán entradas en la *cache*, que podrá disponer de más espacio para otros buffers sobre los que sí se ejecuten operaciones de lectura.

A continuación se muestra un breve ejemplo de uso:

```

// Host code when creating the OpenCL buffer:

myHostOpenCLWriteOnlyBuffer = clCreateBuffer(context,

CL_MEM_WRITE_ONLY, 32 * sizeof(float), NULL, NULL);

myHostOpenCLReadOnlyBuffer = clCreateBuffer(context,

CL_MEM_READ_ONLY, 32 * sizeof(float), NULL, NULL);

// Device code when defining the function parameters:

__kernel void myDeviceKernel (

__global __write_only float * myDeviceWriteOnlyBuffer,

__global __read_only const float * myDeviceReadOnlyBuffer

) {

// ...

}

```

No obstante, depende del *driver* del dispositivo tener en cuenta estos *flags* para realizar las optimizaciones oportunas. De hecho, estas técnicas no han supuesto ninguna mejora en el rendimiento o en el uso de recursos de la FPGA.

### 6.2.7 Funciones built-in

La especificación de OpenCL incluye un conjunto de instrucciones para ejecutar funciones que son frecuentemente utilizadas, de tal manera que el fabricante pueda proporcionar una implementación óptima para su plataforma. Es por ello que es recomendable utilizar siempre que sea posible las funciones *built-in* correspondientes, en lugar de hacer una implementación propia. A continuación se listan algunas de estas funciones (ver Apéndice A.7 para una explicación más detallada acompañada de un ejemplo de uso):

- **mad**: calcula el valor aproximado de  $a \times b + c$ .

- **ceil**: redondea hacia arriba un número flotante.

- **sin**: computa el seno de un número.

- **fmod**: devuelve el módulo de un número.

La siguiente porción de código muestra un ejemplo de uso de la función *mad*:

```

__kernel void myDeviceKernel (

__global float * a,

__global float * b,

__global float * c

) {

size_t threadId = get_global_id(0);

// Using normal arithmetics

// a[threadId] += b[threadId] * c[threadId];

// Using built-in functions

a[threadId] = mad(b[threadId], c[threadId], a[threadId]);

}

```

Sin embargo, para las funciones usadas en los experimentos se ha comprobado que el AOC no realiza ninguna optimización específica para el dispositivo, por lo que no se ha observado que la precisión de la aplicación o el rendimiento varíen usándose esta técnica.

#### 6.2.8 División en múltiples kernels

Durante la fase de *tracking* se aplica un submuestreo, obteniendo la misma imagen en tres tamaños distintos: 320x240, 160x120 y 80x60. Esta representación de la imagen se denomina “pirámide de tres niveles”. En el caso del kernel de *reduce*, siempre es lanzado con tres cantidades de *work item* distintas (una para cada nivel de la pirámide), por lo que dividirlo en tres kernels podría ayudar al compilador a realizar una mejor asignación de recursos. Esto es debido a que, para cada uno de los kernels, el número de *work items* que van a ejecutarlo es conocido en tiempo de compilación, así como el número de iteraciones de todos los bucles.

```

// Size is unknown for the compiler, but we know the application

// always passes three sizes

__kernel void myDeviceKernel (

__global float * a,

__global float * b,

__global float * c,

int size

) {

for (int i=0; i<size; i++) {

// ...

}

}

```

```

}

// Known size for all kernels, hence better resources assignment

// and possibility to unroll and pipeline the loop

__kernel void myDeviceKernel1 (

__global float * a,

__global float * b,

__global float * c

) {

for (int i=0; i<320*240; i++) {

// ...

}

}

__kernel void myDeviceKernel2 (

__global float * a,

__global float * b,

__global float * c

) {

for (int i=0; i<160*120; i++) {

// ...

}

}

__kernel void myDeviceKernel3 (

__global float * a,

__global float * b,

__global float * c

) {

for (int i=0; i<80*60; i++) {

// ...

}

}

```

Gracias a esta técnica, se ha obtenido un *speedup* de 2,07 en el tiempo de ejecución del kernel, a cambio de usar un 19 % más de recursos de la FPGA.

### 6.2.9 Opciones de compilación

La especificación de OpenCL indica que ciertas opciones de compilación que pueden pasarse en tiempo de ejecución a la instrucción *clBuildProgram* (es decir, a la hora de crear el objeto que contiene el programa de OpenCL). Un ejemplo de opción de compilación es la opción *-cl-fast-relaxed-math*, mediante la cual se indica que las operaciones en coma flotante pueden violar el estándar IEEE 754.

No obstante, es decisión del *vendor* tenerlas en cuenta o no. Por ejemplo, en el caso de la implementación OpenCL de NVIDIA (para sus GPUs) sí que se tiene en cuenta este parámetro, pues en este caso el programa OpenCL se crea en tiempo de ejecución. Sin embargo, la implementación OpenCL de Altera ignora estos parámetros, ya que el

programa OpenCL en su caso es un binario que se crea previamente a la ejecución del programa. En su lugar, Altera especifica que se puede pasar *-fp-relaxed* como parámetro al AOC a la hora de crear el binario.

Por la experiencia durante este proyecto usando este tipo de opciones, no ha sido posible verificar que éstas tienen un impacto en el rendimiento. Es posible que en los experimentos realizados haya quedado oculta una posible mejora por otros factores que tienen mayor impacto en el tiempo de ejecución de la aplicación.

#### 6.2.10 Barriers

Las barriers son un punto de sincronización entre múltiples *work items*. Esta instrucción provoca una espera hasta que todos los *work items* afectados por el barrier hayan llegado a ejecutar esta instrucción y sus operaciones de memoria se hayan completado. Existen dos tipos de barriers en OpenCL:

- **Local:** El punto de sincronización es a nivel de work group.

- **Global:** El punto de sincronización es a nivel global, de todos los *work items*.

Siempre que se pueda, es mejor evitar los barriers, ya que se desperdicia tiempo de cómputo por la espera provocada por la sincronización. Prescindir de los barriers de la implementación original de *reduce* implica modificar el patrón de acceso a memoria y la forma de reparto de trabajo entre los *work items*, por lo que el impacto de evitar los barriers se cuantifica en conjunto con las relacionadas con la memoria.

#### 6.2.11 Halffloat

Existen varios grados de precisión para números en coma flotante que cumplen el formato estándar IEEE 754. Los más habituales son:

- **Precisión doble:** ocupan 64 bits, de los cuales 1 indica el signo, 11 el exponente y 52 la mantisa.

- **Precisión simple:** ocupan 32 bits, de los cuales 1 indica el signo, 8 el exponente y 23 la mantisa.