# Characterization of HPC applications for ARM SIMD instructions

# Víctor Soria Pardos

DIRECTOR: ADRIÀ ARMEJACH (BSC-CNS)

Co-director: Darío Suárez (UNIZAR)

RESPONSIBLE: MIQUEL MORETÓ (DAC)

DEGREE IN INFORMATICS: COMPUTATION FACULTAT D'INFORMÀTICA DE BARCELONA (FIB)

# Abstract

Nowadays, most Intruction Set Architectures (ISA) include Single Instructions that process Multiple Data (SIMD) to speed up High Performance Computing (HPC) applications. The first part of this work aims to characterize HPC applications optimized using the NEON extension, which is the actual SIMD extension supported by ARMv8 processors. For this purpose, we have two high-end ARMv8 processors, ThunderX and ThunderX2, and two mainstream comercial ARMv8 compilers, GCC and Arm HPC Compiler. With this set up we have characterized a collection of benchmarks extracted from RAJAPerf, HACCKernels and HPCG benchmarks. The characterization includes experimental work in order to obtain speed-up, scalability, energy efficiency and power efficiency measurements for all benchmarks. Moreover, we have taken a look into the assembly code to identify what optimizations are used by each compiler that makes benchmarks run faster or slower.

The second part of this work focuses on the novel Scalable Vector Extension (SVE) specified in the ARMv8.2 ISA. This SIMD specification introduces a Vector-Length Agnostic programming model, which enables implementation choices for vector lengths that scale from 128 to 2048 bits. To this day, no real processor implements this new ISA, therefore we have used the Arm Instruction Emulator (ArmIE), an emulation tool developed by Arm, that allows the execution of SVE compiled binaries running in an ARMv8 processor. Our work analyzes how compilers that support SVE (GCC and Arm HPC Compiler) vectorize the benchmarks and what is the quality of the generated assembly code. We also propose some low level optimizations to improve code generation.

# Resum

Avui en dia, la majoria dels conjunts d'instruccions (ISA) inclouen instruccions que processen múltiples dades en una única instrucció. Aquestes instruccions s'utilitzen per accelerar aplicacions d'alt rendiment (HPC). La primera part d'aquest treball busca caracteritzar aplicacions HPC que han estat optimitzades utilitzant NEON, que és l'actual subconjunt d'instruccions vectorials suportat pels processadors basats en l'ISA ARMv8. Per aconseguir aquest objectiu tenim a la nostra disposició dos processadors de alta gamma basats en ARMv8, que són ThunderX i ThunderX2, i dos dels principals compiladors del mercat, GCC i Arm HPC Compiler. Amb aquests hem caracteritzat una col·lecció de benchmarks obtinguts del conjunt de benchmarks RAJAPerf i les aplicacions HACCKernels i HPCG. Aquesta caracterització inclou experiments per obtenir la millora de rendiment, l'escalabilitat, l'eficiència energètica i el consum de potència. A més, hem analitzat el codi assemblador per tal d'identificar quines optimitzacions s'han fet i quines caracteristiques fan que uns experiments siguin més ràpids que altres.

La segona part d'aquest treball es centra en la nova extensió vectorial escalable (SVE) de Arm, la qual està especificada en la ISA ARMv8.2. Aquesta especificació introdueix el model de programació independent de la longitud dels registres vectorials (VLA). Aquest model permet que els fabricants de processadors puguin triar diferents longituds de vectors 128 i 2048 bits par la implementació de las entre A dia d'avui, no existeix cap processador que micro-arquitectures. implementi aquest nou repertori d'instruccions, per tant hem estat forçats a utilitzar una eina de emulació (ArmIE) desenvolupada per Arm. Aquesta eina ens permet executar binaris compilats amb suport per SVE en processadors de la ISA ARMv8. En aquest treball s'analitza com els compiladors GCC y Arm HPC Compiler vectoritzen benchmarks, i a més es proposa una optimització de baix nivell per tal de millorar la generació de codi.

# Resumen

Hoy en día, la mayoría de repertorios de instrucciones (ISA) incluyen instrucciones que procesan multiples datos en una única instruccion. Éstas instrucciones se utilizan para acelerar aplicaciones de alto rendimiento (HPC). La primera parte de este trabajo busca caracterizar aplicaciones HPC que han sido optimizadas utilizando NEON, que es el actual subcojunto de instrucciones vectoriales soportado por los procesadores basados en la ISA ARMv8. Para alcanzar este objetivo tenemos a nuestra disposición dos procesadores tope de gama basados en ARMv8, que son ThunderX y ThunderX2, y dos de los principales compiladores del mercado, GCC y Arm HPC Compiler. Con ellos hemos caracterizado una colección de benchmarks extraidos del conjunto de benchmarks RAJAPerf y las aplicaciones HACCKernels y HPCG. Esta caracterización incluye una serie de experimentos que buscan calcular el speed-up, la escalabilidad, la eficiencia energética y de consumo de Además, hemos analizado el código ensamblador para potencia. identificar que optimiaciones se han llevado a cabo y qué caracteristicas hacen que unos experimentos sean más rápidos que otros.

La segunda parte de este trabajo se centra en la nueva extensión vectorial escalable (SVE) de Arm, la cual está especificada en la ISA ARMv8.2. Esta especificación introduce el modelo de programación independiente de la longitud de los registros vectoriales (VLA). La cual permite que los fabricantes de procesadores puedan elegir diferentes longitudes de vectores entre 128 y 2048 bits, para la implementación de sus microarquitecturas. A día de hoy, no existe ninguna máquina que implementa este nuevo repertorio de instrucciones, por lo tanto hemos tenido que usar una herramienta de emulación (ArmIE) desarrollada por Arm. Esta herramienta nos permite ejecutar binarios compilados con soporte para SVE en procesadores de la ISA ARMv8. Nuestro trabajo analiza cómo los compiladores GCC y Arm HPC Compiler vectorizan estos benchmarks y además propone ciertas optimizaciones de bajo nivel para mejorar la generación de código.

# Preface

Dear reader, the document you are reading right now is my final bachelor thesis that concludes my four years degree in informatics engineering at University of Zaragoza, which I have developed and defended at the Polytechnic University of Catalonia. This project has been developed with the colaboration of the Mont-Blanc 2020 project.

I would like to thank Adrià Armejach, Darío Suárez and Miquel Moretó, for their dedication and support. Without them this project would not have been possible. My gratitude also goes to my office partners for the support, answering all my questions. I would finally like to dedicate this work to my parents and friends, whom have encouraged me during this long path.

# Contents

| 1 | Cor | itext a | nd Scope of the Project                   | 1  |

|---|-----|---------|-------------------------------------------|----|

|   | 1.1 | Conte   | xt                                        | 1  |

|   | 1.2 | Proble  | em Formulation                            | 2  |

|   | 1.3 | Object  | tives                                     | 4  |

|   | 1.4 | Stakeh  | nolders                                   | 4  |

|   |     | 1.4.1   | Developer and Research Intern             | 4  |

|   |     | 1.4.2   | Director, Co-director and Ponent          | 4  |

|   |     | 1.4.3   | Scientific Community                      | 5  |

|   | 1.5 | State-o | of-the-art                                | 5  |

|   |     | 1.5.1   | ThunderX and ThunderX2                    | 5  |

|   |     | 1.5.2   | The Mont-Blanc European Project           | 5  |

|   |     | 1.5.3   | LLVM and GCC Comparisons                  | 6  |

|   |     | 1.5.4   | SVE Research                              | 7  |

|   | 1.6 | Scope   |                                           | 7  |

|   | 1.7 | Develo  | opment Practices and Validation           | 8  |

|   |     | 1.7.1   | Short Development Cycles                  | 8  |

|   |     | 1.7.2   | Tools for Development                     | 9  |

|   |     | 1.7.3   | Project Tracking                          | 9  |

|   |     | 1.7.4   | Final Evaluation                          | 9  |

| 2 | Pro | ject Pl | lanning                                   | 10 |

|   | 2.1 | Estima  | ated Project Duration                     | 10 |

|   | 2.2 | Projec  | t Tasks                                   | 10 |

|   |     | 2.2.1   | T1 Project Planning and Feasibility       | 10 |

|   |     | 2.2.2   | T2 System Set Up and Benchmark Analysis   | 11 |

|   |     | 2.2.3   | T3 Compilation and Experiment Development | 11 |

|   |     | 2.2.4   | T4 Performance and Code Analysis          | 12 |

|   |     | 2.2.5   | T5 SVE Compilation and Code Analysis      | 13 |

|   |     | 2.2.6   | T6 Final Stage                            | 13 |

|   | 2.3 | Task I  | Dependencies                              | 13 |

|   | 2.4 | Estimated Time                                 | 13 |

|---|-----|------------------------------------------------|----|

|   | 2.5 | Resources                                      | 14 |

|   |     | 2.5.1 Hardware Resources                       | 14 |

|   |     | 2.5.2 Software Resources                       | 14 |

|   |     | 2.5.3 Human Resources                          | 15 |

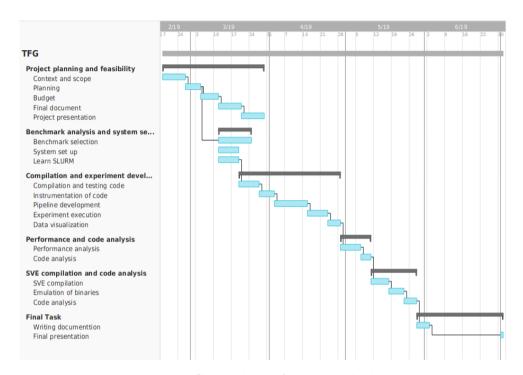

|   | 2.6 | Gantt chart                                    | 16 |

|   | 2.7 | Action Plan                                    | 16 |

|   |     | 2.7.1 Machine Failures                         | 17 |

|   |     | 2.7.2 Timetable                                | 17 |

|   |     | 2.7.3 Bad Documentation                        | 17 |

| 3 | Buc | dget and Sustainability                        | 18 |

|   | 3.1 | V v                                            | 18 |

|   |     | 3.1.1 Human Resources                          | 18 |

|   |     | 3.1.2 Software Resources                       | 18 |

|   |     | 3.1.3 Hardware Resources                       | 20 |

|   |     | 3.1.4 Indirect Costs                           | 20 |

|   |     | 3.1.5 Contingency and Unexpected Events        | 21 |

|   |     | 3.1.6 Total Budget                             | 21 |

|   | 3.2 | Budget Control                                 | 22 |

|   | 3.3 | Sustainability                                 | 23 |

|   |     | 3.3.1 Self-assessment of the Current Domain of |    |

|   |     | Sustainability Competence                      | 23 |

|   |     | 3.3.2 Environmental Sustainability             | 24 |

|   |     | 3.3.3 Economic Sustainability                  | 24 |

|   |     | 3.3.4 Social Sustainability                    | 25 |

| 4 | Met | thodology                                      | 26 |

|   | 4.1 | Benchmark Selection                            | 26 |

|   | 4.2 |                                                | 27 |

|   | 4.3 | Software Stack                                 | 29 |

|   |     | 4.3.1 Compilers                                | 29 |

|   |     | 4.3.2 Performance Libraries                    | 29 |

|   |     | 4.3.3 Hardware Counters                        | 29 |

|   |     | 4.3.4 Extrae and Paraver                       | 30 |

|   |     | 4.3.5 ArmIE                                    | 30 |

|   | 4.4 | Test Machines Architecture                        |

|---|-----|---------------------------------------------------|

|   |     | 4.4.1 ThunderX                                    |

|   |     | 4.4.2 ThunderX2                                   |

|   |     | 4.4.3 Skylake                                     |

|   | 4.5 | Workload and Environment                          |

|   |     | 4.5.1 Compilation                                 |

| 5 | Ber | achmark Vectorization 38                          |

|   | 5.1 | RAJAPerf                                          |

|   |     | 5.1.1 MULADDSUB                                   |

|   |     | 5.1.2 EOS                                         |

|   |     | 5.1.3 HYDRO                                       |

|   |     | 5.1.4 INT_PREDICT                                 |

|   |     | 5.1.5 COPY                                        |

|   |     | 5.1.6 VOL3D                                       |

|   |     | 5.1.7 FIR                                         |

|   |     | 5.1.8 JACOBI_1D                                   |

|   |     | 5.1.9 JACOBI_2D                                   |

|   |     | 5.1.10 GEMM                                       |

|   |     | 5.1.11 FLOYD_WARSHALL 45                          |

|   | 5.2 | HACCK                                             |

|   | 5.3 | HPCG                                              |

| 6 | Res | ults and Analysis 49                              |

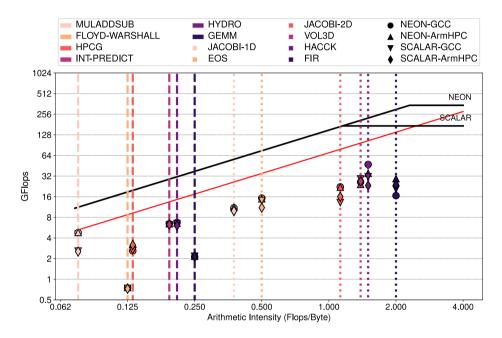

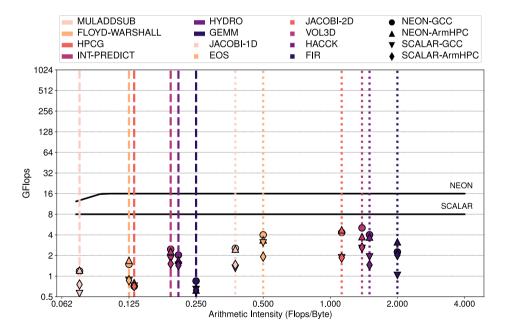

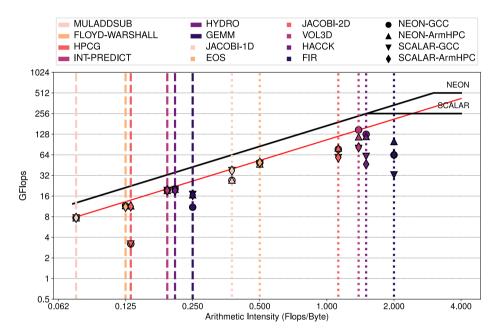

|   | 6.1 | Roofline Models                                   |

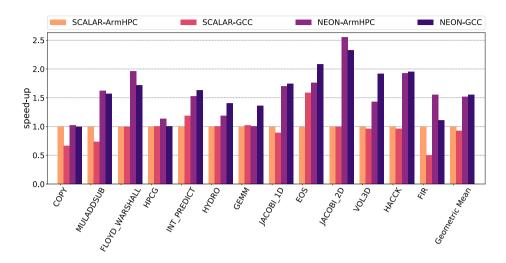

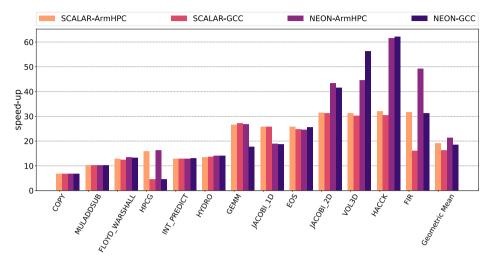

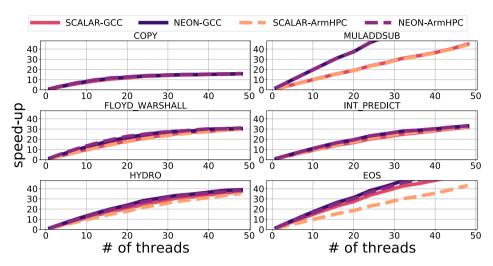

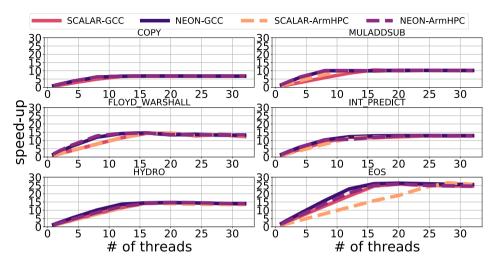

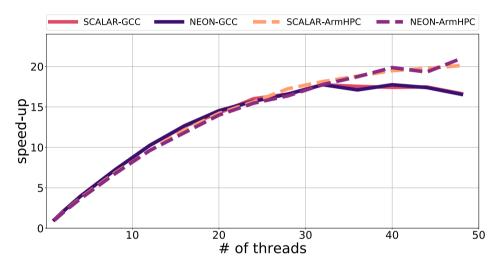

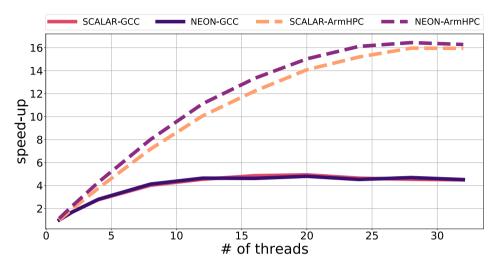

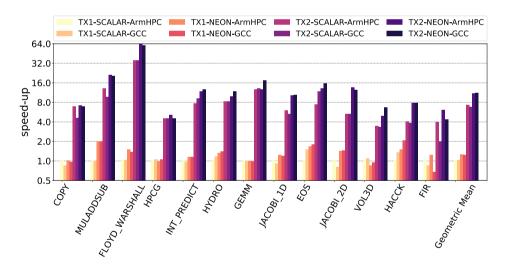

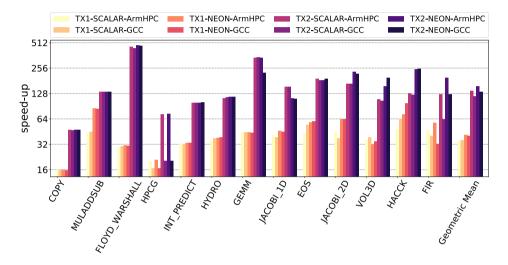

|   | 6.2 | Performance, Scalability and Bounds               |

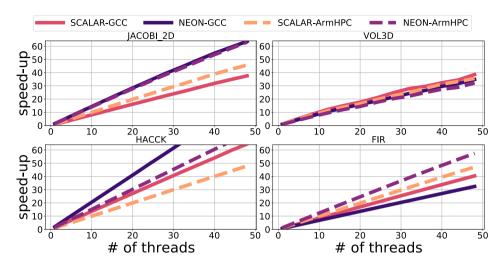

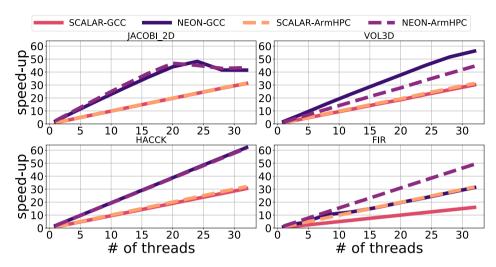

|   |     | 6.2.1 Low AI Benchmarks                           |

|   |     | 6.2.2 High AI Benchmarks                          |

|   |     | 6.2.3 JACOBI_1D                                   |

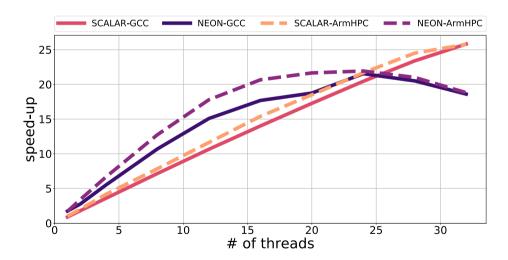

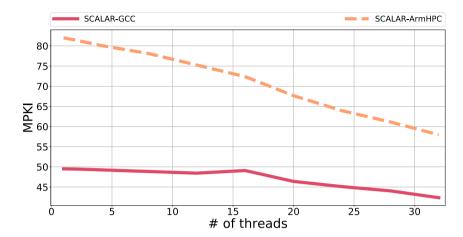

|   |     | 6.2.4 HPCG                                        |

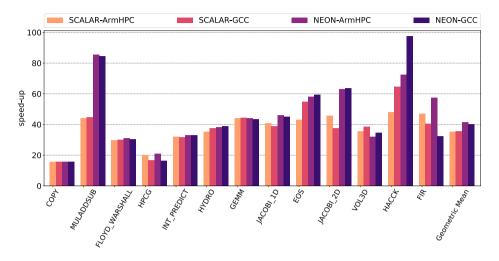

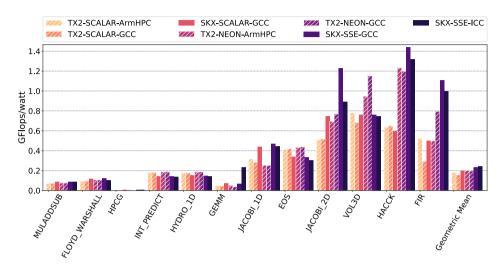

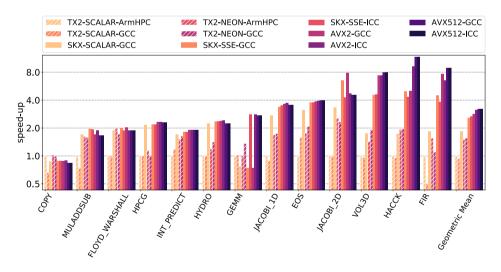

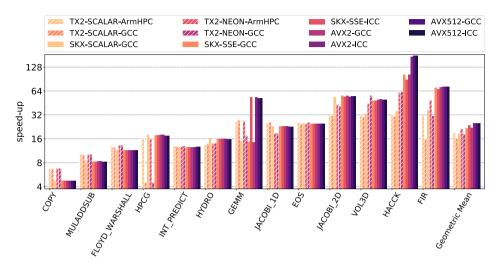

|   | 6.3 | Test Machines Performance Comparison 67           |

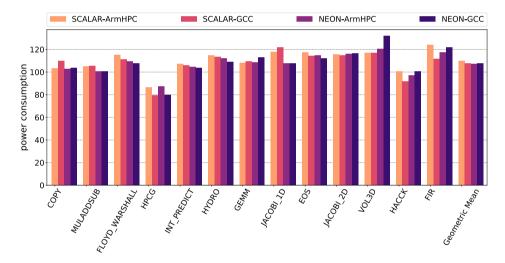

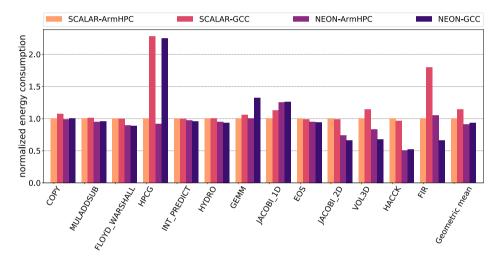

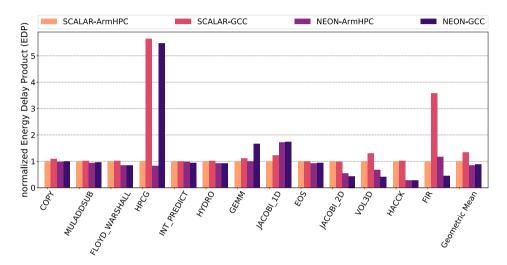

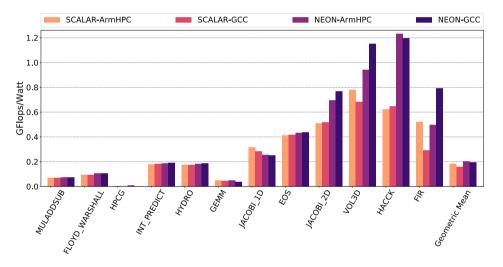

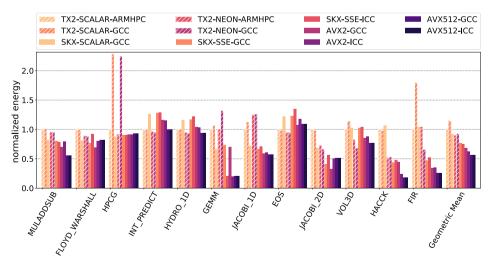

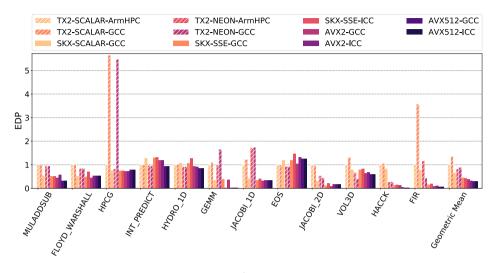

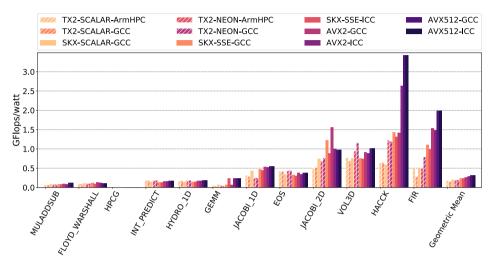

|   | 6.4 | Power and Energy Efficiency of ThunderX2 69       |

|   | 6.5 | Code Analysis                                     |

|   |     | 6.5.1 Loop Unrolling and Reduction of Data Access |

|   |     | Instructions                                      |

|   |     | 6.5.2 Keeping Constants Stored in Registers       |

|              |       | 0.5.3            | Library and Runtime Performance    | 78  |

|--------------|-------|------------------|------------------------------------|-----|

|              |       | 6.5.4            | VOL3D                              | 79  |

| 7            | SVI   | E <b>A</b> nal   | ysis                               | 82  |

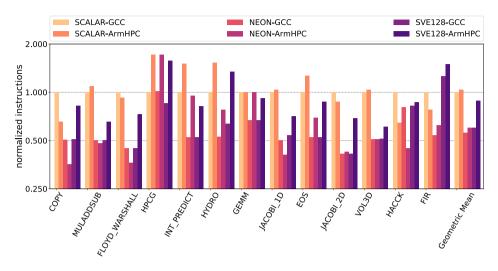

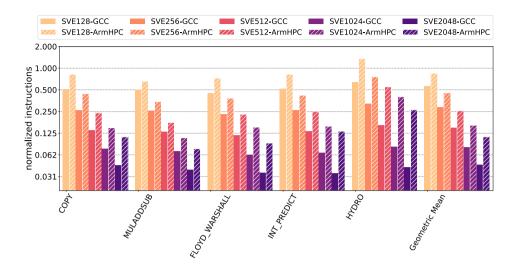

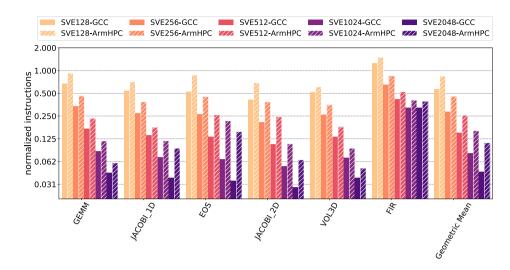

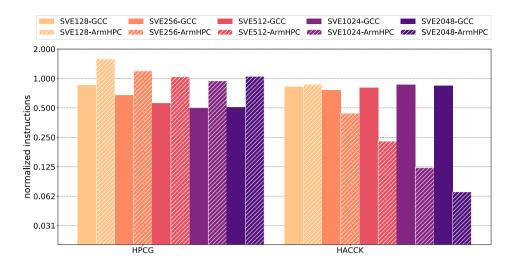

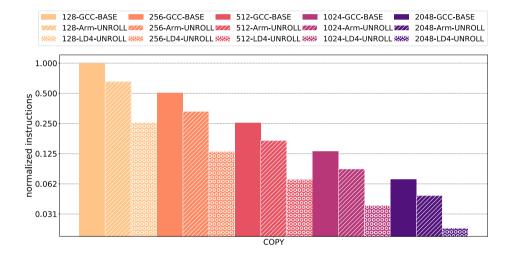

|              | 7.1   | Instru           | ction Reduction                    | 82  |

|              |       | 7.1.1            | Number of Instructions Executed    | 82  |

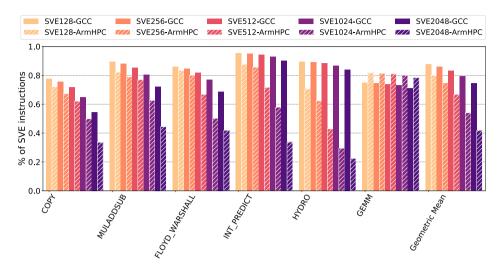

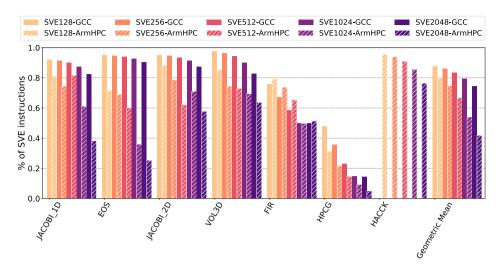

|              |       | 7.1.2            | Ratio of SVE Instructions          | 87  |

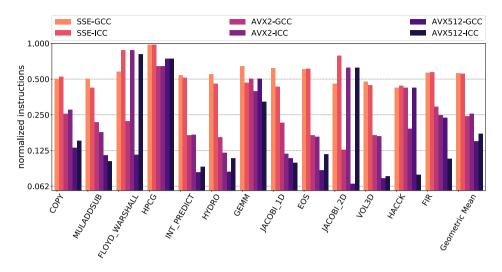

|              |       | 7.1.3            | Comparision Between SVE and x86_64 | 88  |

|              |       | 7.1.4            | Final Remarks                      | 90  |

|              | 7.2   | Code             | Analysis                           | 91  |

|              |       | 7.2.1            | Data Dependencies                  | 91  |

|              |       | 7.2.2            | Indices and Registers              | 93  |

|              |       | 7.2.3            | Instruction Selection              | 95  |

|              |       | 7.2.4            | FIR                                | 96  |

|              |       | 7.2.5            | Loop unrolling                     | 97  |

|              |       | 7.2.6            | Non-Temporal Vector Instructions   | 100 |

| 8            | Cor   | clusio           | ns                                 | 102 |

|              | 8.1   | Summ             | ary                                | 102 |

|              | 8.2   |                  | t Autoevaluation                   | 103 |

| A            | Wo    | rkloads          | 5                                  | 105 |

| В            | Sky   | lake F           | lags                               | 107 |

| $\mathbf{C}$ | Thu   | $\mathbf{nderX}$ | 2 and Skylake Comparision          | 111 |

|              | C.1   |                  | mance                              | 111 |

|              | C.2   |                  | y Efficiency                       | 112 |

|              | $C^3$ |                  | Efficiency                         | 11/ |

# Chapter 1

# Context and Scope of the Project

This chapter analyzes HPC research lines on Single Instruction, Multiple Data architectures focusing in ARM-based proposals. Then, it introduces problem formulation, project objectives and principal stakeholders. Finally, describes state-of-the-art proposals, project scope and development practices.

#### 1.1 Context

Nowadays, one of the most used methods of speeding up HPC (High Performance Computing) and machine learning applications, is through SIMD (Single Instruction, Multiple Data) [1]. These instructions increase data parallelism, since the same operation is executed on different data points at the same time. This approach dominated supercomputing during 80's, until they were surpassed by inexpensive MIMD approaches (Multiple Instructions, Multiple Data), where different processors compute different instructions to different data [2]. Modern supercomputers architectures are dominated by clusters of MIMD computers, each of them implementing SIMD.

A current trend in the server & HPC segments is the popularization of Arm's (Advanced RISC Machines) Instruction Set Architecture (ISA). The ARM ISA has become with the years the most used and the most produced in quantity terms [3]. One of the key factors for the adoption of ARM ISA is its power efficient RISC chips, which is a key factor in the mobile market segment. If we classify the ISAs according to their complexity, we usually distinguish between RISC and CISC. Reduced

Instruction Set Computing (RISC) is a family of processors architectures that have a small set of general purpose instructions, while on the other extreme of the design space, instructions in a Complex Instruction Set Computing (CISC) machine can execute several low level operations. In fact most current CISC processors internally execute RISC micro-operations.

On one hand, RISC cores are well known for addressing embedded systems and battery powered platforms where power efficiency is critical, due to their power efficient design they consume less for the same task. On the other hand CISC cores have been dominating supercomputing and server markets, because of high performance designs. However, with the years, these differences have been reducing and Arm has focused towards HPC and server systems introducing its SIMD extensions (NEON and SVE), while Intel has introduced its new mobile chips based on the Atom product like, for smartphones [4].

In this context, the Mont-Blanc project [6] was born to develop a supercomputer based on mobile market technology; in order to take advantage of the higher manufacturing volumes, faster design cycles and better economic factors [5]. To achieve this, Mont-Blanc focuses on ARM-based processors. An initial prototype was based on the Samsung Exynos 5 Dual processor, and in 2017 Mont-Blanc announced a new prototype based on Marvell's ThunderX2 CPUs [7].

#### 1.2 Problem Formulation

This project aims to characterize SIMD generated code of the two main ARM ISA compilers: GCC (GNU Compiler Collection) and the Arm HPC compiler. We cover two different SIMD extensions: NEON and the Scalable Vector Extension (SVE), for the ARM 64 bits architecture ARMv8.2-A.

The NEON extension was first introduced in the ARMv7-A specification. With a vector length of 128-bit, its instructions can perform two operations of double precision floating point or 4 operations of single precision floating point [11]. SVE was first introduced within ARMv8.2-A in 2016. This extension is a novel approach for SIMD instruction specifications. It allows developers to generate and optimize SIMD code and forget about the vector length. In other words the ISA is vector

length agnostic and enables SVE binaries to run on machines with different vector lengths without recompilation. Apart from the vector length agnostic paradigm, SVE supports gather and scatter instructions that allow SIMD instructions to operate on non contiguous data [12]. Nowadays, there is no machine that implements the SVE extension, and it is planned that Fujitsu will deploy the first in 2021.

To perform the characterization we use a set of HPC and Machine Learning benchmarks, namely: RAJAPerf loops [8], HACCK [9] and HPCG [10]. These benchmarks will be compiled and executed for using the OpenMP programming model. A benchmark is a program which the main goal is to quantify the performance of a computer and to be able to compare it with other computers. This is achieved by executing the same binary under the same conditions on different computers and analyzing the metrics obtained from these executions. Metrics help analysts quantify and characterize program's behaviour, e.g. GFlops and speed-up are two well known metrics that measure a program performance [25].

The selected benchmarks employ OpenMP to parallelize execution. OpenMP is a specification for a set of compiler directives, library routines, and environment variables that can be used to specify high-level parallelism in Fortran and C/C++ programs. OpenMP is used to parallelize benchmarks, via shared memory multiprocessing programming. It offers an easy way to parallelize code in order to scale application at the node level, and it is widely used in supercomputers.

Each benchmark will be executed mainly in the two prototype clusters from the Mont-Blanc project that are called ThunderX and ThunderX2. The two clusters are based on ARM 64 bit processor, that are manufactured by Cavium (Marvell Technology Group). One is based on a ThunderX model with 48 in-order cores and the other a ThunderX2 with 32 out-of-order cores. Both processors use a custom implementation of ARM 64 bit cores, focusing its features for enterprise server solutions and HPC workloads.

Eventually, we will make some experiments in a third machine based on Intel's Skylake architecture. These experiment will help us to contrast the results obtained in both Cavium machines.

# 1.3 Objectives

Once we have the statement of the problem, we can focus on the different objectives this project aims to achieve. These can be summarized as:

- 1. Implement and maintain a work space for experiments.

- 2. Develop an evaluation methodology and the necessary infrastructure to conduct experiments for the research work. This infrastructure can be used in future experiments and by other researches.

- 3. Measure performance and power consumption differences between GCC and ARM-HPC compilers, between SIMD and no SIMD assembly code and between ThunderX and ThunderX2 nodes in machine learning and HPC benchmarks.

- 4. Check correctness of assembly code generated by both compilers for the new vector extension SVE.

- 5. Analyze how each compiler optimizes the same code. And seek for specific compiler options that optimize concrete applications.

#### 1.4 Stakeholders

## 1.4.1 Developer and Research Intern

The developer will be responsible of all the technical part. From modifying the benchmarks code to be suitable for experiments to implement an automatized pipeline for the execution of the experiments. But the most important task for the researcher is to analyze and document the results.

## 1.4.2 Director, Co-director and Ponent

The director of this project is Adrià Armejach, he is senior researcher at Barcelona Supercomputer Center (BSC-CNS). The co-director of the project is Darío Suárez, assistant professor at Universidad de Zaragoza. And the responsible of the project is Miquel Moretó, Ramon y Cajal

research fellow at UPC and senior researcher at BSC. Their roles will be essential for the correct development of the project and their knowledge will be key for the analysis of the results.

#### 1.4.3 Scientific Community

The results published after this work can be used by the scientific community in future research. The direct beneficiary will be the BSC. The usage of novel technologies like SVE and the Arm HPC compiler is still in its early stages compared to other technologies, so the results of this project may help developers in the future.

#### 1.5 State-of-the-art

As mentioned before, the ARM ISA has seen a steep growth in popularity. This has lead academia to start researching ARM based solutions for HPC.

#### 1.5.1 ThunderX and ThunderX2

On 2014, Cavium announced ThunderX, its first 64 bit multi-core ARM server microprocessor. Relying on the ARMv8 ISA, this processor was able to integrate 48 in-order cores. On 2016, Cavium announced its new server generation, ThunderX2. As well as ThunderX, is a 64 bit multi-core ARM server microprocessor, but with a radical new architecture based on 32 out-of-order cores implementing the ARMv8.1 ISA. Both processors are suitable for vector architecture experiments since they support NEON and have high memory bandwidth. Moreover, both processors have been used on several academic articles [13] [14].

### 1.5.2 The Mont-Blanc European Project

Since 2011, the Mont-Blanc European project has encouraged its vision of an exascale supercomputer based on technology coming from the mobile market segment. The last Mont-Blanc prototype is called Dibona, which is based on ThunderX2 processors. The whole system is suited for HPC workloads, like simulation of geophysics, fusion, materials, particle physics, life sciences, combustion, aerodynamics, weather forecast,

computational fluid dynamics, biophysics, and a large etc. consequence of project researching, numerous reports have been published in the past years. During stage three of the Mont-Blanc project, the team chose a set of HPC applications for evaluating their performance in ARM-based architectures. The benchmarks were ported and tuned for ARM mini-cluster prototypes, that includes ThunderX processor [15]. After that, Dibona behaviour was studied using a heterogeneous set of benchmark compiled with a collection of commonly used compilers. These benchmark were chosen in order to reach the throughput and memory bandwidth peaks of Thunder X2. In those experiments the main objective instead of comparing possible ARM ISA compilers, was chose the best generated code that could achieve the highest performance. [16]. Another interesting report is [17], that compared GOMP (GCC OpenMP) implementation) and IOMP (intel and LLVM OpenMP implementation). Nevertheless, these experiments only focused in OpenMP instead of full compiler capabilities.

While all these works are profoundly related with HPC on ARM based machines, none of them analyzes differences between compiler generated assembly.

## 1.5.3 LLVM and GCC Comparisons

The Arm HPC compiler is based on LLVM tool chain technology. Since LLVM was released first on 2003 there has been many comparisons between both compilers. Almost all these comparisons are focused on the x86 architecture [18], and only few ones that take a look at ARM assembly are outdated [19]. On these papers GCC usually has a better performance over LLVM while on Mont-Blanc's papers LLVM outperforms GCC, specially when using optimized Arm Performance Libraries.

Arm has also published some posts in its blog, in which they shown some small cases of study. Nevertheless, this experiments come from Arm itself and they don't give enough detailed information [20].

1.6. SCOPE 7

#### 1.5.4 SVE Research

Until the first SVE implementation arrives, developers and the scientific community have only two main tools to port and tune applications for the new ISA. One based on simulation (gem5 [21]) and one based on emulation (ArmIE [22].) Simulations give detailed reports about execution performance, but require a high computational cost. On the contrary, emulators can run application's binaries in less time, but losing all possible information about execution time and performance. The major part of scientific research has focused on simulations in last years. These simulations are essential for the development of future chips, but emulators can obtain useful information, specially about compiler code generation and correctness.

## 1.6 Scope

The purpose of this section is to frame the contents of this project and to explain what is out of scope, either due to time limitations or divergence over the main objectives.

As said before, this project aims to characterize Arm's Single Instruction Multiple Data ISA extensions on HPC applications. There are two main extensions: NEON and SVE. The focus will be on the NEON extension, which can be evaluated using real machines. We will evaluate performance and power consumption. Since, there is no real hardware implementing SVE yet, its characterization would require the use of simulations tools with a steep learning curve, and a low level of maturity which does not fit with the time duration of this project. However, SVE will be analyzed using an emulator.

Initially, a set of HPC applications will be chosen. This benchmarks have to be suitable for vectorization and have different characteristics in order to cover a broad spectrum of HPC applications. For example, some of them could be compute intensive, that is when the CPU operations define the execution time, or memory intensive, where data movements represent a major part in execution time. The set of applications should take into account actual scientific problems, machine learning or genomics.

For NEON characterization, applications will be instrumented in order

to capture the execution time and hardware counters, that would give the performance information of its execution. Power measurement scripts will be written to catch energy consumption and calculate energy efficiency. All these tasks are a small part in the development of a fully automatized experiment pipeline. This necessity of such a high level of automatization is caused by long execution times and high number of experiments that restricts human intervention.

During the experiments, binaries will be evaluated on three machines, one based on ThunderX processors, other in ThunderX2 processors and the third in Skylake processors. These two latter machines are placed inside Dibona, which is a prototype developed within the Mont-Blanc project and employs ThunderX2 and Skylake processors. With data gathered from experiments, a two way analysis is done. On one side, assembly code generated is analyzed. On the other, performance metrics are calculated so binaries can be compared between each other. With the analysis, some conclusions should be obtained, like what compiler is doing a better job of auto-vectorization for HPC, or the most energy efficient processor and the associated reasoning.

For SVE analysis, a new version of every program is complied allowing SVE vectorization. The correctness of generated code is checked using the ArmIE emulator on the new binaries. Emulation only gives information about which instructions have been executed, but there is no useful information about execution time or cycles executed. As a consequence of performance information absence, both compilers will be compared on their ability to vectorize each loop and on the correctness of the code.

# 1.7 Development Practices and Validation

As said before, the short time available for finishing the project implies the use of agile and strict work methodologies.

## 1.7.1 Short Development Cycles

With the use of short cycle methodologies (small tasks defined each week) an accurate control of the project is granted. This methodology makes easy to check if the project is on track and reschedule tasks if necessary.

#### 1.7.2 Tools for Development

To analyze the execution of the benchmarks, specific tools like power measurement scripts, paraver [23] and extrae [24] will be used. All of them are based on hardware counters and were developed at BSC to help developers understand the behavior of parallel applications. Additionally, the progress of the project will be registered using BSC's gitlab infrastructure.

## 1.7.3 Project Tracking

A detailed tracking on project progress will be achieved by performing weekly meetings with project advisors. These meetings will be documented in their respective records and documentation.

#### 1.7.4 Final Evaluation

Once all the experiments and analysis have been done, we will obtain and redact what are the main differences between compilers. Then, the level of completeness of project is evaluated checking how many of the initial objectives are full filled.

# Chapter 2

# **Project Planning**

This chapter is a summary of the initial project management course done in March of 2019. It specifies project duration and individual tasks. Then, it explains project schedule and their associated resources. Finally, it describes an action plan for eventual deviations of project schedule.

# 2.1 Estimated Project Duration

The estimated project duration was approximately 4 months. The project started on February 18<sup>Th</sup>, 2019 and the deadline was expected to be on July 3<sup>rd</sup>, 2019. However, we extended it to July 17<sup>Th</sup> of 2019.

# 2.2 Project Tasks

In this section, we explain what are the main project tasks. We explain which steps must be done to accomplish each task.

## 2.2.1 T1 Project Planning and Feasibility

This task pertains to Project Management Course and includes the next four stages:

- I Project scope.

- II Project planning.

- III Project budget.

- IV Initial state of the art.

#### 2.2.2 T2 System Set Up and Benchmark Analysis

The main objective of this task is to make an analysis of possible benchmarks that are suitable for the project and set up the necessary software and tools needed to achieve project objectives.

Benchmarks are selected from Mont-Blanc 2020 project (MB2020) initial prospections. At the moment, this report is confidential until its final version is published. This report searches and analyzes a set of real life applications that exhibit the characteristic demands of Big Data and HPC applications. These programs stress all the segments targeted by MB2020. One of the principal characteristics of these applications its that allow exploring the vector ISA in terms of manual code vectorization, auto-vectorization, and the use of generic performance libraries. Therefore, the benchmarks used in this project are a subset of the MB2020 benchmarks

To develop the project, we need a modern version of GCC (version 8.2.0) and the ARM compiler for HPC (version 19.0) as well as their respective implementations of OpenMP installed, for compiling and executing the parallel versions of the benchmarks. Extrae and paraver are also needed in order to generate traces of the execution and visualize them. These traces are used to understand the behavior of the different benchmarks. All these tools are already installed in the test machines but the developer needs to test and learn how to use them for the project.

The test clusters use as operating system a Linux distribution adapted to ARM, so no learning phase is needed. The executions in the Mont-Blanc clusters are done through the SLURM queue system. SLURM (Simple Linux Utility for Resource Management) is an open-source resource manager designed for Linux clusters of all sizes. Learning how to use SLURM is needed for the project, because SLURM lets the user allocate exclusive access to resources, bind processes to cores, specify shell scripts to run before or after an execution, and automatize experiments.

#### 2.2.3 T3 Compilation and Experiment Development

Benchmark compilation is the central part of the project. Initially all benchmarks are compiled in six different versions: NEON-ArmHPC,

NEON-GCC, SCALAR-ArmHPC, SCALAR-GCC, SVE-ArmHPC and SVE-GCC. Prefix refers to type of vectorization: SCALAR is a non-vectorized binary, NEON uses NEON vectorization and SVE uses SVE vectorization. The suffix refers to compiler used for the compilation. After that step, assembly code must be checked in order to assert that is correct and vectorized.

The first step to perform the experiments is to instrument all benchmarks so we can measure execution time and hardware counter values of the regions of interest. These regions execute the most important part of the benchmark, the part that stresses the processor. At same time shell scripts are written in a way that they launch experiments and capture energy consumption automatically. Another parallel task, is programming a python scripts for data visualization and metrics calculation, that help during analysis.

#### 2.2.4 T4 Performance and Code Analysis

Next step consists in doing a deep analysis with all the information compiled from benchmarks executions. Benchmark bounds are identified and performance is compared between the two compilers and hardware prototypes, i.e. one benchmark may be limited by number of floating point operations done per second (FLOPS) and its vectorized version has an higher performance than scalar version. The best binary version is selected by comparing all binaries within the same workload. Performance differences between performing vectorization and not, are shown for each compiler.

Then, the power and energy consumption of both processors is measured in order to compute the energy and power efficiency. However, during the project development we could not measure this metrics in ThunderX, because the tool used for this purpose was broken. In the place of ThunderX, we finally measured Skylake.

Then assembly code is used to justify all these observations, checking for optimizations performed by the compiler. If each compiler selects a different set of instructions for the same task, they can be compared because both codes are executed on the same hardware.

#### 2.2.5 T5 SVE Compilation and Code Analysis

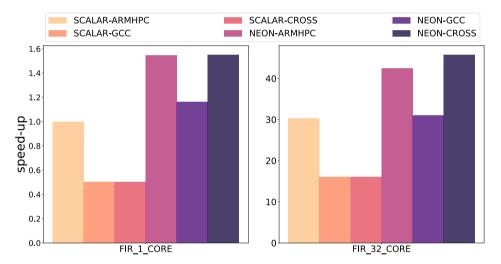

Last step consist in benchmarking all SVE binaries for the same experiments used in past steps. Then we review the assembly code of the binaries in order to find possible errors, unnecessary parts or possible optimizations. We compare how much vectorization is done by each compiler using SVE. Then we show how SVE vectorization reduces the number of instructions executed when increasing the vector length from 128 bits to 2048 bits, and what weight have these SVE instructions. We also compare SVE to Intel SIMD instructions set in order to compare how well SVE vectorize for different vector lengths.

#### 2.2.6 T6 Final Stage

The final stage consists on preparing the delivery of the project. This includes document all experiments, make the necessary graphs to illustrate the results, make an analysis over the results and draw conclusions. With these elements we build the memory of the bachelor thesis. Finally, we prepare the presentation for the thesis defense.

## 2.3 Task Dependencies

The first task to be done is project planning (T1). This task is key for the correct organization and development of the project. Tasks T2 and T5 depend on T1. Then Task T3 depends on T2 and T4 depends on T3. Finally, T6 depends on all of them. The final stage must be done once the project is finished.

## 2.4 Estimated Time

In this section we present a resume with the estimated cost in hours of each task and what has been its real duration.

| Stage                                  | Estimated dedication (hours) | Final dedication (hours) |

|----------------------------------------|------------------------------|--------------------------|

| Planning and feasibility               | 75                           | 62                       |

| Benchmark analysis and system set up   | 50                           | 67                       |

| Compilation and experiment development | 160                          | 177                      |

| Performance and code analysis          | 75                           | 83                       |

| SVE compilation and code analysis      | 110                          | 122                      |

| Final Stage                            | 80                           | 84                       |

| Total                                  | 550                          | 595                      |

Table 2.1: Estimated and dedicated hours per group of tasks.

#### 2.5 Resources

#### 2.5.1 Hardware Resources

- Laptop PC (with an Intel i7-8550U CPU @ 1.80GHz, 8 of RAM): used as work station.

- Thunder cluster: Cavium ThunderX with 128GB of RAM and 128GB of SSD. Each node has 2 sockets, each with 48 ARMv8 in-order cores.

- ThunderX2 cluster: Marvell ThunderX2 with 256GB of RAM and 3.3TB of disk. Each node has 2 sockets, each with 32 ARMv8.1 out-of-order cores.

- Skylake cluster: Intel Xeon Platinum 8176 Processor with 28 Skylake out-of-order cores.

#### 2.5.2 Software Resources

• GNU Compiler Collection (GCC), version 8.2.0: for compilation.

2.5. RESOURCES 15

- Arm compiler for HPC, version 19.0: for compilation.

- Arm Instruction Emulator, version 19.0: for emulation of SVE instructions.

- Arm Performance Libraries: for compilation of scientific applications.

- CMake: for automatization of compilation and linking.

- Perfmon2: for capturing hardware counters.

- Python: for data parsing.

- Extrae: for obtaining OpenMP and hardware counter traces

- Paraver: for visualizing extrae traces.

- Latexmk: for compiling project documentation.

- PDF viewer: for visualizing project final documentation.

- Matplotlib: for building graphs.

- ICC: for compilation.

- Libcount: for counting instructions with ArmIE.

#### 2.5.3 Human Resources

The development of this project involves Adrià Armejach, Darío Suárez and Miquel Moretó as advisors and Víctor Soria as main developer and research intern of the project.

### 2.6 Gantt chart

Figure 2.1: Gantt chart of project schedule

## 2.7 Action Plan

The Gantt chart listed above in Figure 2.1 depicts the initial project plan to achieve all the objectives, but in most projects, it is hard to follow planning as initially thought, and in this case we have had to delay the project duration. This was caused by an underestimation of the task duration, but in other cases can be due to unexpected problems. In these cases, the project team has to find a solution in order to minimize the negative impact over the original task scheduling.

This bachelor thesis must be delivered before the 24Th of June, 7 seven days before the presentation. However, this project was planned to finish

the  $3^{\rm rd}$  of June. Nevertheless, we have finished it the  $17^{\rm Th}$  of June. We have been able to delay the project, because we planned the delivery 21 days before the real deadline. This gave us some days to accommodate the deviations.

Following we explain the project deviations and the mitigation actions we have taken.

#### 2.7.1 Machine Failures

Normal servers, and specially prototypes, can have hardware errors. Also, machines may not be available for other reasons like high utilization on the server, network problems or maintenance works.

**Solution:** This problems can only be resolved by system administrators. In our case, we had to change the test machines in the phase of energy and power measurement, because the tools used for this purpose were broken. We changed ThunderX for Skylake, so we could compare ThunderX2 metrics with another architecture.

#### 2.7.2 Timetable

Because we have special conditions for the development of this project (programs licenses), the timetable was a critical part of the project.

**Solution:** To overcome it, a very rigid and realistic timetable was followed with weekly meetings with the project advisors to ensure the project was following the timetable.

#### 2.7.3 Bad Documentation

Working with machine prototypes usually leads to working with incomplete documentation.

**Solution:** We faced situations where we needed information that did not appear in the documentation. The developer have had to ask to experts or developers with knowledge on the problems for help.

# Chapter 3

# Budget and Sustainability

In this chapter the budget and sustainability of the project are explained. The first part contains a detailed description of software, hardware and human costs and an analysis of how the budget was affected by deviations. The second part evaluates the sustainability of the project.

## 3.1 Budget Estimation

In order to develop the project successfully, it requires a set of resources listed in the previous report, Section 2.5. In this section we estimate the costs of the human, hardware, software resources and the indirect costs. The amortization of each investment will be calculated using two factors; the first one is the useful life of the investment, and the second one is the amount of time is used in the project.

#### 3.1.1 Human Resources

This project is mainly carried by only one person that does all the experiment and documentation work. He counts with the help of three advisors that have guided him. Table 3.1 specifies the number of hours estimated and the final hours consumed for every role and the economic value of them.

#### 3.1.2 Software Resources

In this section, we list the costs of the software tools that were used during the development of the project. All tools are free for use for academic purposes or are open source.

| Role              | Price per hour(€) | Estimated<br>Hours | Cost (€) | Real<br>Hours | Cost (€) |

|-------------------|-------------------|--------------------|----------|---------------|----------|

| Analyst / Advisor | 20.00             | 32                 | 640.00   | 32            | 640.00   |

| Analyst / Intern  | 8.00              | 550                | 4400.00  | 595           | 4760.00  |

| Total             |                   |                    | 5040.00  |               | 5400.00  |

Table 3.1: Human resources budget.

| Product                      | Price (€) | Useful life | Amortization $(\in)$ |

|------------------------------|-----------|-------------|----------------------|

| GCC (8.2.0)                  | 0.00      | _           | 0.00                 |

| Arm compiler for HPC (19.0)* | 0.00      | _           | 0.00                 |

| Arm Instruction Emulator*    | 0.00      | _           | 0.00                 |

| Arm Performance Libraries*   | 0.00      | _           | 0.00                 |

| CMake                        | 0.00      | _           | 0.00                 |

| Perfmon2                     | 0.00      | _           | 0.00                 |

| Python                       | 0.00      | _           | 0.00                 |

| Extrae                       | 0.00      | _           | 0.00                 |

| Paraver                      | 0.00      | _           | 0.00                 |

| Latexmk                      | 0.00      | _           | 0.00                 |

| PDF viewer                   | 0.00      | _           | 0.00                 |

| SLURM                        | 0.00      | _           | 0.00                 |

| Matlplotlib                  | 0.00      | _           | 0.00                 |

| ICC*                         | 0.00      | _           | 0.00                 |

| Libcount                     | 0.00      | _           | 0.00                 |

| Total                        | 0.00      |             | 0.00                 |

<sup>\*</sup>Need licence but are free for academia

Table 3.2: Software budget.

#### 3.1.3 Hardware Resources

In this section, we list the costs of the hardware clusters that were used during the development of the project. All this hardware has been purchased before the beginning of the project, because is part of the Mont-Blanc project. These machines are not exclusive for this bachelor thesis, so the only cost this hardware has for the project is their amortization. Servers and personal computers have an estimated life of 5 years. Table 3.3 lists the amortization of each hardware resource. The total cost is  $1210,68 \in$ , but we split this value in two because at the time initial estimation was done Skylake cluster was not supposed to be used.

| Investment                     | Price (€) | Useful life | Amortization $(\in)$ |

|--------------------------------|-----------|-------------|----------------------|

| Dell Inspireon 13 7030         | 900.00    | 5 years     | 60.00                |

| Thunder cluster node*          | 3500.00   | 5 years     | 233.34               |

| Dibona ThunderX2 cluster node* | 6000.00   | 5 years     | 400.00               |

| Dibona Skylake cluster node*   | 7760.19   | 5 years     | 310.00               |

| Total                          | 18160.00  |             | 693.34 + 310.00      |

<sup>\*</sup>The cost of the Dibona clusters is an estimation because they are not publicly available

Table 3.3: Hardware budget.

#### 3.1.4 Indirect Costs

In addition to the costs related to the explicitly required resources specified up to this point, other costs that affect project budget must be considered. Even if they are not directly related with the tasks. These costs are derived from project execution, i.e the cost of electricity, internet access, office rent, etc. However, as the project was developed in its totality at the BSC-CNS installations, it is not possible to specify the real cost of the services. In its place we provide estimated data, see Table 3.4.

| Product     | Price per month(€) | Number of months | Cost (€) |

|-------------|--------------------|------------------|----------|

| Electricity | 75.00              | 4                | 300.00   |

| Internet    | 37,90              | 4                | 151.60   |

| Office rent | 90.00              | 4                | 360.00   |

| Transport   | 35.00              | 4                | 140.00   |

| Total       |                    |                  | 951.60   |

Table 3.4: Estimated indirect costs.

### 3.1.5 Contingency and Unexpected Events

Budget estimation as project planning can suffer possible deviations. Therefore, contingency was calculated as much as 15% of the total cost. This value permitted us to extend the project 14 days. At the end, we did not exceed the total budget, see Table 3.5

#### 3.1.6 Total Budget

Finally, by consolidating all tables above, the total budget is obtained. Taxes that apply to resources cost are included in the investment price.

| Туре                      | Estimated Cost $(\in)$ | $\begin{array}{cc} \operatorname{Real} & \operatorname{Cost} \\ (\in) & \end{array}$ |

|---------------------------|------------------------|--------------------------------------------------------------------------------------|

| Human resources           | 5040.00                | 5400.00                                                                              |

| Software resources        | 0.00                   | 0.00                                                                                 |

| Hardware resources        | 693.34                 | 1003.34                                                                              |

| Indirect costs            | 951.60                 | 951.60                                                                               |

| Total without contingency | 6684.94                |                                                                                      |

| Contingency (15%)         | + 802.20               |                                                                                      |

| Total                     | 7487.14                | 7354.94                                                                              |

Table 3.5: Total budget.

## 3.2 Budget Control

In this section we explain the control mechanism developed to prevent project deviations. One of the most frequent deviations in computer science projects is task duration. It is highly important to account the number of hours spent on every project task, and to have a comparison with the amount of estimated hours. Verification of project objectives is also a key part of project tracking.

A control mechanism for measuring and avoiding deviations is obtaining the difference between resources consumed and resources estimated for each task. This procedure has to take special care of tasks that have a high risk of deviation. The principal motivation for following such a strict tracking is that, the earlier a deviation is detected, the earlier could a corrective action be taken. Therefore, the deviation would have a lower impact on task scheduling. This tracking is assured to be executed because there is a weekly meeting between developer and advisors.

During project execution we did some more resources than the initially estimated, since we had to use extra hardware that was not planned. In the case of software programs there are a lot of open source alternatives that covered project needs. Human resources was the main resource deviation and the one who most budget increment supposed, that was the reason to include a contingency item in the budget.

The possible project deviations were measured with the following metrics:

#### • Efficiency deviations:

Cost of human resources deviation = (number of work hours estimated - number of work hours realized) \* estimated cost

Cost of product consumption deviation = (estimated consumption of product - real consumption of product) \* estimated product cost

#### • Total deviations:

Total deviation on human resources = estimated human resources cost - real human resources cost

Total fixed cost deviation = estimated total fixed costs - real total fixed costs

## 3.3 Sustainability

The sustainability of this project is discussed from three points of view: economic, social and environmental.

# 3.3.1 Self-assessment of the Current Domain of Sustainability Competence

After answering an interactive pool provided by UPC, I have obtained the following conclusions:

Throughout the survey, I realized that I have an intermediate level of knowledge about sustainability of a project. All knowledge I have about this topic comes from self learning and personal interests, because in my university of origin this competence does not exist. I think that I am able to analyze correctly the sustainability of a project in all three dimensions: economic, social and environmental. I can identify possible impact of an IT project. Moreover I can find new ideas and solutions in order to make these IT projects more sustainable in any of these three areas.

To me, economic and environmental aspects of IT projects are easy to cover since their impact can be easily measured and actions can be taken in consequence. For example, development teams can choose product materials taking into account how big are its associated costs or environmental footprints. However, to me social sustainability is harder to analyze. I do not know accessibility, ergonomics, on safety metrics; nor possible solutions or actions to modify project shortcomings on these aspects. Despite this lack of knowledge in these topics, I consider social impact of my research projects, so they can help people improve their quality of life.

On the other hand, during the survey I found some terms that I was not familiar with. For example, the existence of *deontological ethics* about sustainability for computer scientists. So I had to find information about this logic. In the future I want to know more about them so I can apply them to future projects.

#### 3.3.2 Environmental Sustainability

During the development this project it consumed only one environmental resource, electricity. Test clusters (ThunderX and Dibona ones) were running during all 4 months. In fact, they are running all year, because they are a shared resource for different scientific research groups. Dibona's ThunderX2 has a known power of 180 watts and ThunderX 120 watts. However, these metrics are not exact because the whole system consumes more power, and both processors have lower operation frequencies, because they are not always working at full load. Since the start of the project to its finish date, there have been 2520 hours. That supposes 756 kWh consumed by the clusters.

Besides these two clusters, a laptop was used for development tasks, but its energy consumption is negligible, it spent around 500 Wh. All this energy consumption could not be reduced because the laptop was used only when it was necessary and the cluster cannot be turned off.

Even though, the resulting conclusions extracted from this project can be used in future works, so wasted energy would be further amortized. When programmers know what compiler flags generate best power efficient code helps to waste less energy.

Therefore its environmental sustainability is awarded with an 8. Despite its high energy consumption during development, it could save energy in posterior applications, and has a low risk for the environment.

#### 3.3.3 Economic Sustainability

Project costs have been already detailed in section 3.1. There is no estimation for maintenance within budget summary, since the only project outcome is the results report. However, the project's useful life is expected to last for a while, because it may be useful for future research teams or developers.

Reducing project budget maintaining the project scope could have been only achieved by reducing the number of dedicated hours taken to develop it, but this would have required a more experienced developer who's salary would be higher. Both hardware and software resources are clearly justified in the planning section, so every euro spent in this resources could not be saved.

The cost of this project compared to other state-of-the-art and similar projects is more affordable, due to a shorter project duration, lower waste in human resources and lower use of software and hardware resources. This similar projects invest from  $17933 \in 0.23026 \in 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.23026 = 0.230$

This project is awarded an 8 in the economic sustainability area, since most of the software tools have no cost at all, there is no maintenance, and even though the Mont-Blanc clusters are expensive, they are not used exclusively for this research.

#### 3.3.4 Social Sustainability

At personal level, the accomplishment of the projected plan has supposed my firsts steps in research. As said many times before, this project will engross Academia publications and may contribute to have a better understanding of today's compilers. At the same time I have learned about how compilers generate assembly code and optimize it. This project also aimed to support the development of high performance computing models for Arm technology. This may help to perfect HPC applications like medical, engineering and scientific simulations.

Actually, there is a lot of literature published about GCC and Clang compilers (Arm HPC Compiler is based on Clang). But all this articles focus on Intel architectures, therefore there is not enough information of code generated by these two compilers on Arm architectures. HPC research, which was treated indirectly in this project, has a high impact in society because it helps scientist find solutions for social problems like air pollution, medical treatments or product development.

Hence, it is awarded a 7 in the social sustainability area, since it will benefit the scientific community and has the potential to improve people quality of life, not directly but indirectly.

# Chapter 4

# Methodology

This chapter describes the experiment infrastructure built and the methodology we follow. First, a description of the software stack used, followed by selection of benchmarks, an architectural description of the test machines, and finally the experimentation environment and metrics.

#### 4.1 Benchmark Selection

This section describes the selection process we have followed to choose the set of benchmarks we want to study. Then, the chosen benchmark suites are described. A benchmark suite is a collection of benchmarks that are grouped by its characteristics. As mentioned in section 2.2.2, we have picked up benchmark suites employed in the Mont-Blanc 2020 project. The project team has followed this criteria:

- I Benchmarks represent a computational pattern that consumes significant resources on today's massively-parallel HPC systems.

- II Benchmarks are foreseen to be long-term candidates for relevant HPC computations.

- III Benchmarks allow porting in terms of manual code vectorization, auto-vectorization, and by using generic performance libraries. Benchmarks are suitable to SVE porting.

- IV Benchmarks demand high memory bandwidth or represent relevant HPC computational patterns.

- V Benchmarks are written in C/C++ and use OpenMP.

4.2. METRICS 27

| Name of the suite | Type                  | Number of benchmarks |

|-------------------|-----------------------|----------------------|

| HACCK             | n-body methods        | 1                    |

| HPCG              | sparse linear algebra | 1                    |

| RAJAPerf          | set of HPC kernels    | 11                   |

Therefore, we have choose the following suites of benchmarks:

Table 4.1: Suite description and number of benchmarks per suite.

## 4.2 Metrics

To make an accurate and deep analysis we need a set of metrics that detail the behaviours of the experiments. Moreover, these metrics help us to compare different experiments between them. In this section we present the metrics and how they are obtained.

First and most basic metric is speed-up. It help us to calculate how much faster or slower is one experiment respect to other. Speed-up is calculated as:

$$Speedup = \frac{\text{Base Execution Time}}{\text{Improved Execution Time}}$$

When we calculate the speed-up respect to the same application but changing the number of cores, we usually talk about parallel efficiency. It measures how an application speeds-up respect to the number of cores used and is calculated as:

Parallel Efficiency =

$$\frac{Speed - up}{Number of Threads}$$

Another performance metric commonly used when comparing different processors with different frequency is GFlops. It measures the number of floating operations executed by time unit. In most benchmarks the main part of the computation work is done by floating point operations, therefore measuring the number of floating point instructions is more accurate than measuring the total number of instructions. It is calculated as:

$$\label{eq:GFlops} \text{GFlops} = \frac{\text{Number of Floating Point Instructions Executed}}{\text{Execution Time} \times 10^9}$$

When an in-depth analysis is made is common to measure the number of misses per kilo instruction (MPKI). This metric is hard to understand because it describes part of the architectural behaviour hidden to the programmer. This metric is also ambiguous because some times higher is worse (a bad code manages worst data and therefor generates more misses) and in others is better (a good code executes in less instructions and thus with higher misses per kilo instructions). MPKI is calculated as

$$\label{eq:MPKI} \text{MPKI} = \frac{\text{Number of Misses}}{\text{Number Kilo of Instructions Executed}}$$

A common way of measuring power efficiency is calculating performance (GFlops) per Watt. This metric measures performance per power unit. It is calculates as follows:

$$GFlops/Watt = \frac{Number\ of\ Floating\ Point\ Instructions\ Executed}{Average\ Power\ Consumption\times Execution\ Time\times 10^9}$$

Finally we also want to measure energy efficiency with two distinct metrics. First one is total energy consumed by processor during the experiment. We only have power measuring tools, therefore we will obtain total energy consumed as follows:

$$\label{eq:energy} \text{Energy (Joules)} = \text{Average Power Consumed} \times \text{Execution Time (Seconds)}$$

The last experimental metric is energy delay product (EDP), it relates time to the energy consumed. Sometimes EDP is a better metric than total energy consumed because some codes can be slower in order to consume less energy. But we are interested not only in the energy consumption reductions but also about the performance.

$$EDP = Energy consumed(Joules) \times Execution Time (Seconds)$$

Finally, we present a theretical metric that we will compute for every benchmark using only the high level code. This metric measures the amount of floating point operations a benchmark does for every byte of data brougth from memory, it is called Arithmemtic Intensity. It can help us clasify benchmarks and it is calculated as follows:

$$\label{eq:arithmetic} \text{Arithmetic Intensity (AI)} = \frac{\text{Number of floating point operations}}{\text{Number of bytes read from memory}}$$

## 4.3 Software Stack

In this section we will describe the main software packages used to generate HPC benchmark binaries and profile them.

## 4.3.1 Compilers

There are many different compiler solutions in the market, like Fujitsu or Cray compilers. However, for compiling our applications we have used the only two representative and available compilers: GCC 8.2.0 [30] and Arm Compiler for HPC 19.0 [31]. The latter is based on the LLVM 7.0.2 tool chain. Both compilers support SVE and NEON vectorization and implement the OpenMP standard and runtime. In particular, OpenMP 4.5 is fully supported for C/C++ in GCC through the libgomp library (GOMP), while Arm compiler offers C/C++ support for OpenMP 3.1 and some features of OpenMP 4.0/4.5 through the libiomp library. Both compilers have entirely different processes to generate optimized code. In fact, Arm has been working with to development teams two improve both compilers ARM ISA assembly generation [20].

#### 4.3.2 Performance Libraries

Some applications like HPCG use Arm Performance Libraries (PL) that provide BLAS, LAPACK, FFT, and standard math routines. PL routines are tuned specifically for ARM processors. We have used version 19.0 of the PL for both GCC 8.2.0 and Arm HPC Compiler 19.0.

#### 4.3.3 Hardware Counters

Because we want to characterize application behaviour we need more information than just execution time. Today's processors implement a set of registers and counters that can log architectural events inside the processor. Each processor can register a different subset of architectural events but almost all include cycle and instruction count.

There are several libraries that implement system calls that are available to developers so they can read performance counters. The two most famous are Performance Application Programming Interface (PAPI [33]) and libpfm [32]. We will use the former with extrae, explained in next subsection. We will use the latter to instrument benchmark code, capturing events during the execution of the region of interest (ROI). The concrete events we will capture are specified in section 4.3. We use both tools, instead only PAPI, because extrae generates big trace files that are difficult to understand and have a lot of information. Therefore, we will use libpfm for all the initial experiments, so we can obtain ROI performance counters. For the interesting cases, we will use PAPI with extrae for a finer grain level of detail with traces.

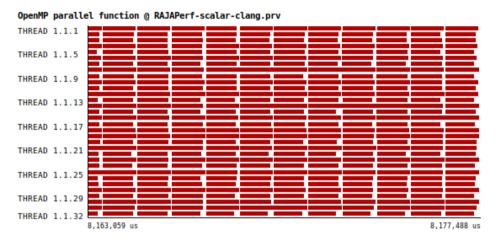

#### 4.3.4 Extrae and Paraver

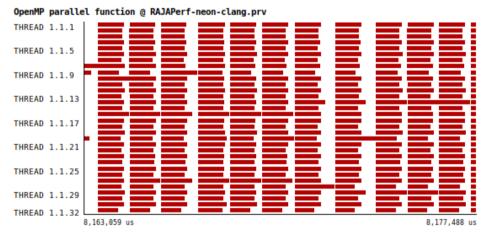

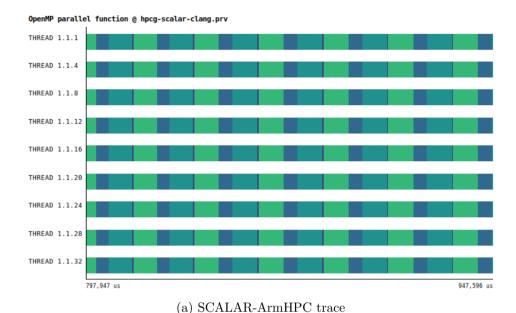

Extrae and Paraver are two tools developed by BSC. The former is a dynamic instrumentation package to trace programs already compiled and run with shared memory programming model (OpenMP or pthreads), the message passing (MPI) programming model, or both programming models. Extrae generates trace files that can be later visualized with Paraver. Paraver is a flexible parallel program visualization and analysis tool. Paraver was developed responding to the need of having a qualitative global perception of the application behavior by visual inspection and then to be able to focus on the detailed quantitative analysis of the problems. We will use extrae with OpenMP and PAPI, so we can visualize the hardware counters and OpenMP events through time.

#### 4.3.5 ArmIE

Arm Instruction Emulator (ArmIE [22]) is an emulation tool that allows the execution of binaries compiled for ARMv8.2 ISA on machines based on ARMv8.0 ISA. Therefore, we can emulate the execution of a SVE binary without a machine that implements SVE. However, emulation is not suitable to obtain performance metrics and execution times, because ArmIE's results are not related with the behaviour of a real machine implementing ARMv8.2 ISA.

One of the characteristics ArmIE implements is instruction counting, that allow us to count how many instructions are executed, and what number of them is emulated. With both numbers we can check how increasing the machine vector length used by SVE instructions the total number of instructions is reduced.

### 4.4 Test Machines Architecture

In this section we describe what are the processors that we will evaluate in our experiments. The description include the architectural characteristics of the processors.

#### 4.4.1 ThunderX

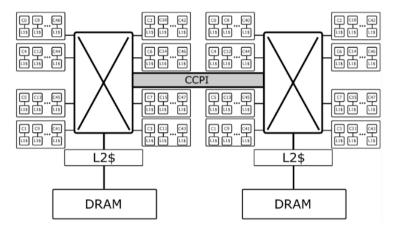

Figure 4.1: ThunderX1 cluster diagram [36]

The ThunderX node is dual socket system, this means that the node has two ThunderX processors. However, we will only use on the ThunderX processors. ThunderX processor is a 64-bit ARMv8 server SoCs, that enables servers and appliances optimized for compute, storage, network and secure compute workloads in the cloud and HPC datacenters [35]. One ThunderX processor has 48 in-order cores, manufactured in 28nm process technology under architectural license from Arm. It can run up to 2.5Ghz but our cluster is configured at 1.8Ghz, so the TDP is under its 120W. ThunderX memory hierarchy is described in Table 4.2 and Figure 4.1 describes processor layout.

|             | Policy        | Write-through |

|-------------|---------------|---------------|

| L1          | Type          | Private       |

| Data        | Size          | 32KiB         |

| Cache       | Associativity | 32-way        |

|             | Block         | 128-bytes     |

| T.1         | Size          | 72KiB         |

| Instruction | Associativity | 39-way        |

| Cache       | Block size    | 128-bytes     |

|             | Policy        | Write-back    |

| L2<br>Cache | Type          | Shared        |

|             | Size          | 16MiB         |

|             | Associativity | 16-way        |

|             | Block         | 128-bytes     |

Table 4.2: ThunderX memory hierarchy [34].

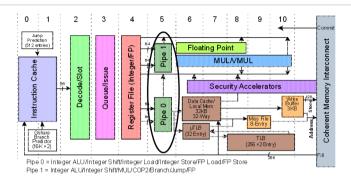

The ThunderX pipeline is still unknown today, but several articles [37] and compilers development logs [38] take into account that there are two execution pipelines inside each ThunderX core as shown in Figure 4.2. This pipeline comes from the Octeon III router core, but we can figure out that ThunderX's one is very similar. ThunderX SIMD and floating point instructions can only be executed in one of the execution pipelines.

Finally, hardware counters supported by this processor are not documented and most libraries cannot read most of them. Despite, this problem we have been able to read instructions, cycles and L1-data misses.

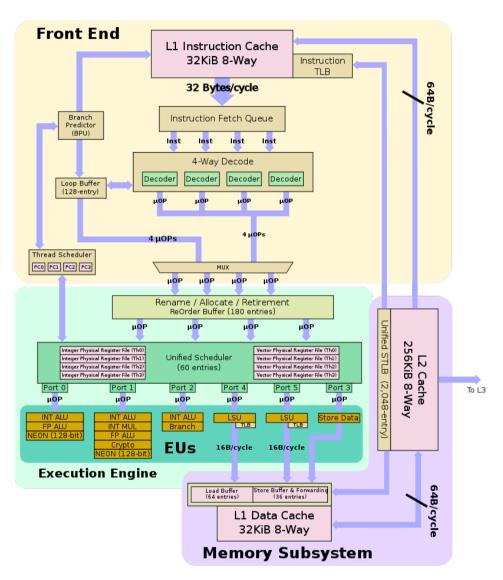

#### 4.4.2 ThunderX2

The second generation ThunderX2 product family introduced by Cavium was released for general availability in early 2018. ThunderX2 is a family of 64-bit ARMv8.1 processors re-branded by Cavium based on the original design of Broadcom's Vulcan. In the ThunderX2 CN99XX series, the ARM based SoC integrates high-performance custom out-of-order (OoO) cores, supporting up to 32 ARMv8.1 cores in a single-socket configuration and

## **Short Pipeline by Choice**

- Short pipes provide higher performance via lower misprediction penalties

- Short pipes provide lower power via lower misprediction penalties & simpler predictors

Figure 4.2: Pipe diagram of a ThunderX1 like processor (Octeon III) [37]

64 cores in a dual-socket configuration, with a frequency of up to 2.5GHz in nominal mode and 3GHz in Turbo mode, but in the Dibona prototype frequency is fixed at 2.0GHz. ThunderX2 has a Thermal Design Power (TDP) of 180 Watts. Simultaneous Multithreading (SMT) is supported which allows up to 4 threads per physical core, but we will not use it, SMT is deactivated in Dibona prototype by default. Each core has 32 KiB L1 instruction and data cache, as well as 256 KiB L2 cache. The 32 MiB L3 cache is distributed among the cores. Each ThunderX2 processor provides multiple, up to 8, DDR4-2666 memory controllers per chip with a maximum bandwidth of up to 170 GB/s [16].

In Figure 4.3 we can see the block diagram of one ThunderX2 core. The most interesting aspects of this core for our project is that there are 2 SIMD execution units and the double load bandwidth, two 128-bits load execution units. ThunderX2 memory hierarchy specs are shown in Table 4.3.

Figure 4.3: ThunderX2 block diagram [39]

| Characteristic | L1 D-Cache | L2 Cache | L3 Cache          |

|----------------|------------|----------|-------------------|

| Type           | Private    | Private  | Shared, Exclusive |

| Size           | 32KiB      | 256KiB   | 16MiB             |

| Associativity  | 8-way      | 8-way    | N/A               |

Table 4.3: ThunderX2 memory hierarchy.

## 4.4.3 Skylake

Because BSC power measurement tools broke before we could measure power consumption of ThunderX, we have decided to use another test node inside the same cluster for power consumption experiments. This machine is built with 2 Intel® Xeon® Platinum 8176 Processor [43]. Skylake is a family of x86 64 processors. This processor contains 28 Out-of-Order cores that support Intel® SSE4.2 (128 bits SIMD), Intel® AVX (256b SIMD), Intel® AVX2 (245b SIMD), Intel® AVX-512 (512b SIMD) instructions set extensions. Thanks to multithreading each core support 2 threads that suppose a total number of 56 threads. Base frequency is 2.1 Ghz but on turbo mode can reach 3.80 GHz. Last level of cache is L3 that has a size of 38.5 MB. The TDP is 165 Watts.

Its most important architectural characteristics are the 224 ROB entry, two 512 bits Vector Floating Point ALU.

## 4.5 Workload and Environment

Since most HPC systems run over MIMD and SIMD paradigms we have done our experiments over different combinations of them. First, we have compiled four basic binaries that correspond with: NEON supported binary compiled with Arm HPC compiler (NEON-ArmHPC), NEON supported binary compiled with GCC, no-SIMD support binary compiled with Arm HPC Compiler (SCALAR-ArmHPC) and no-SIMD support binary with GCC Compiler (SCALAR-GCC). And for the emulation experiments we have compiled two more binaries that are SVE support binary compiled with Arm HPC Compiler (SVE-ArmHPC) and SVE support binary compiled with GCC (SVE-GCC). We have compiled two

no-SIMD versions only to compare them with SIMD ones. MIMD paradigm has been tested executing these binaries with different number of threads and binding each thread to only one core of the machine.

## 4.5.1 Compilation

Tables 4.4 and 4.5 detail the base compiler flags enabled for GCC and Arm HPC Compiler. Tables describe only two sets of compiler flags that are shared by all binaries. There are only two compiler flags that change for every binary, they are listed in Table 4.6. These two flags must be concatenated to the end of the basic flags in order to achieve the correct compilation. Respect to the rest of the compiler flags, we only employ the default ones that came with the vanilla sources. Flags have only been modified to generate specific ARMv8 code and allow or deny vectorization. Skylake flags are listed in appendix B.

| Application | Flag SCALAR-GCC                                                                       |

|-------------|---------------------------------------------------------------------------------------|

| HACCK       | -O3 -ffast-math -fopenmp -funroll-loops -ffp-contract=fast                            |

| HPCG        | -O3 -ffast-math -fopenmp -funroll-loops -std=c++11 -ffp-contract=fast -larmpl_lp64_mp |

| RAJAPerf    | -O3 -fopenmp -ffast-math                                                              |

Table 4.4: Flags for GCC scalar version.