## Trabajo Fin de Máster

Diseño y evaluación de un generador multinivel

basado en GaN

Design and evaluation of a multilevel generator

based on GaN

Autor/es

Ignacio Álvarez Gariburo

Director/es

Óscar Lucía Gil

Héctor Sarnago Andía

Escuela de Ingeniería y Arquitectura

Zaragoza, Noviembre 2019

## Resumen

Este trabajo se centra en la implementación de un convertidor multinivel basado en tecnología GaN capaz de suministrar una tensión de +/- 1 kV, una corriente de +/- 50 A y sintetizar cualquier forma de onda desde DC hasta 100 kHz.

Para ello, en primer lugar, se menciona brevemente cuál es el objetivo y las aplicaciones principales del proyecto, después, se justifica la necesidad de este tipo de prototipos en el ámbito industrial y se elabora un breve estudio del estado arte de la tecnología existente. Se muestran las topologías y controles más extendidos actualmente y se justifica cuál es la opción escogida para el trabajo.

Una vez escogida la topología, y teniendo claras las especificaciones, se valoran diferentes alternativas de control y se comparan en base a una serie de parámetros establecidos previamente, para poder escoger cuantitativamente la mejor opción en cuanto a eficiencia, calidad de la señal generada y complejidad.

El siguiente paso que se ha realizado es la selección de cada uno de los componentes que formarán el prototipo, aportando los datos técnicos más relevantes para justificar su elección. Posteriormente se han diseñado las distintas PCBs que conforman el convertidor y se ha explicado cuál es el layout de las mismas, así como la conexión entre cada una de ellas. A continuación, se han realizado los experimentos necesarios en el laboratorio para verificar su correcto funcionamiento y demostrar que el convertidor es capaz cumplir con las especificaciones que se mencionan al comienzo del trabajo. Finalmente, se extraen las conclusiones del trabajo realizado y se plantean como posibles vías futuras algunas mejoras que podrían introducirse en el convertidor.

# Índice

|                                                              |    |

|--------------------------------------------------------------|----|

| Lista de acrónimos .....                                     | 2  |

| Lista de figuras .....                                       | 4  |

| 1 Introducción .....                                         | 8  |

| 1.1 Objetivo .....                                           | 8  |

| 1.2 Alcance .....                                            | 9  |

| 2 Estudio del estado del arte.....                           | 12 |

| 2.1 Convertidores multinivel .....                           | 13 |

| 2.1.1 Tipos y aplicaciones .....                             | 14 |

| 2.1.2 Estrategias de control.....                            | 22 |

| 3 Simulación y análisis.....                                 | 26 |

| 3.1 Especificaciones de diseño y topología de la etapa ..... | 26 |

| 3.2 Alternativas valoradas.....                              | 27 |

| 3.3 Comparativa entre alternativas .....                     | 29 |

| 3.3.1 Número de módulos.....                                 | 29 |

| 3.3.2 Pérdidas por conmutación.....                          | 30 |

| 3.3.3 Rizado (THD) .....                                     | 31 |

| 3.3.4 Complejidad del diseño .....                           | 32 |

| 3.4 Resultados de simulación.....                            | 33 |

| 4 Diseño del convertidor multinivel propuesto .....          | 38 |

| 5 Verificación experimental.....                             | 46 |

|     |                                    |    |

|-----|------------------------------------|----|

| 5.1 | Diseño hardware .....              | 46 |

| 5.2 | Resultados experimentales.....     | 54 |

| 6   | Conclusiones y líneas futuras..... | 60 |

| 6.1 | Conclusiones .....                 | 60 |

| 6.2 | Líneas futuras.....                | 61 |

| 7   | Bibliografía .....                 | 62 |

|     | Anexos .....                       | 64 |

## **Lista de acrónimos**

|        |                                                   |

|--------|---------------------------------------------------|

| AC     | Alternating Current                               |

| ADC    | Analog to Digital Conversor                       |

| CHB    | Cascaded H Bridge                                 |

| DAC    | Digital to Analog Conversor                       |

| DC     | Direct Current                                    |

| FB     | Full Bridge                                       |

| FC     | Flying Capacitors                                 |

| FPGA   | Field Programmable Gate Array                     |

| GaN    | Gallium Nitride                                   |

| LDO    | Low Dropout Regulator                             |

| MC     | Multilevel Converter                              |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| MSPS   | Mega samples per second                           |

| NPC    | Neutral Point Clamped                             |

| PCB    | Printed Circuit Board                             |

| PM     | Power Module                                      |

| PWM    | Pulse Width Modulation                            |

| THD    | Total Harmonic Distortion                         |

| TI     | Texas Instruments                                 |

| USB    | Universal Serial Bus                              |

## **Lista de figuras**

|                                                                                                                                                          |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 1: Aplicaciones propuestas para el generador de señales. (a) Electroporación de tejido hepático. (b) Caracterización de cargas de inducción. .... | 8  |

| Figura 2: Convertidor puente monofásico NPC de 5 niveles [6]. ....                                                                                       | 14 |

| Figura 3: Ejemplo de funcionamiento de un convertidor NPC de 5 niveles [6]. ....                                                                         | 15 |

| Figura 4: Tensión de línea de un convertidor NPC de 5 niveles [6]. ....                                                                                  | 15 |

| Figura 5: Perfil de carga y descarga de los condensadores. (a) Tensión y corriente en fase. (b) Tensión y corriente desfasados 90 ° [6].....             | 16 |

| Figura 6: Convertidor monofásico de 5 niveles utilizando la topología de FC [6]. ....                                                                    | 17 |

| Figura 7: Ejemplo de funcionamiento de un convertidor de FC de 5 niveles [6].....                                                                        | 18 |

| Figura 8: Topología y formas de onda de un convertidor multinivel CHB. (a) Topología. (b) Formas de onda de un convertidor de 9 niveles [7].....         | 20 |

| Figura 9:Comparativa de hardware entre los distintos tipos de convertidores multinivel para generar m niveles de tensión [7].....                        | 21 |

| Figura 10: Aplicaciones convertidores multinivel [15].....                                                                                               | 22 |

| Figura 11: Clasificación según el tipo de modulación en convertidores multinivel [15].                                                                   |    |

| .....                                                                                                                                                    | 23 |

| Figura 12: Aplicabilidad de los distintos métodos de modulación a cada una de las topologías de convertidores multinivel [15].....                       | 24 |

| Figura 13: Tensión de salida del convertidor multinivel con estrategia de modulación PWM.....                                                            | 27 |

| Figura 14: Tensión de salida del convertidor multinivel con módulos de tensión variable                                                                  |    |

| .....                                                                                                                                                    | 28 |

|                                                                                                                                                      |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 15: Modelo de simulación para un módulo del convertidor. ....                                                                                 | 29 |

| Figura 16: Número de commutaciones para cada alternativa.....                                                                                        | 30 |

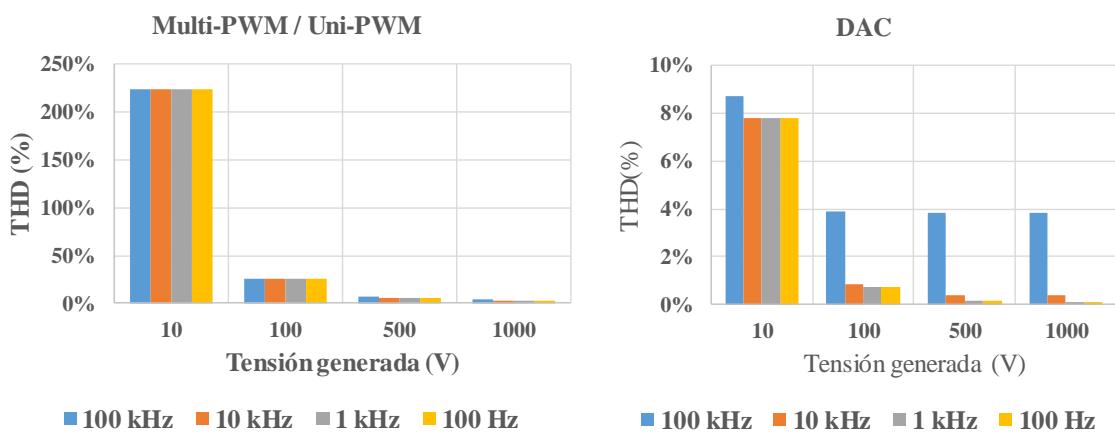

| Figura 17: Análisis de distorsión armónica, THD, para cada alternativa.....                                                                          | 31 |

| Figura 18: Tabla resumen de comparación entre las tres alternativas valoradas.....                                                                   | 33 |

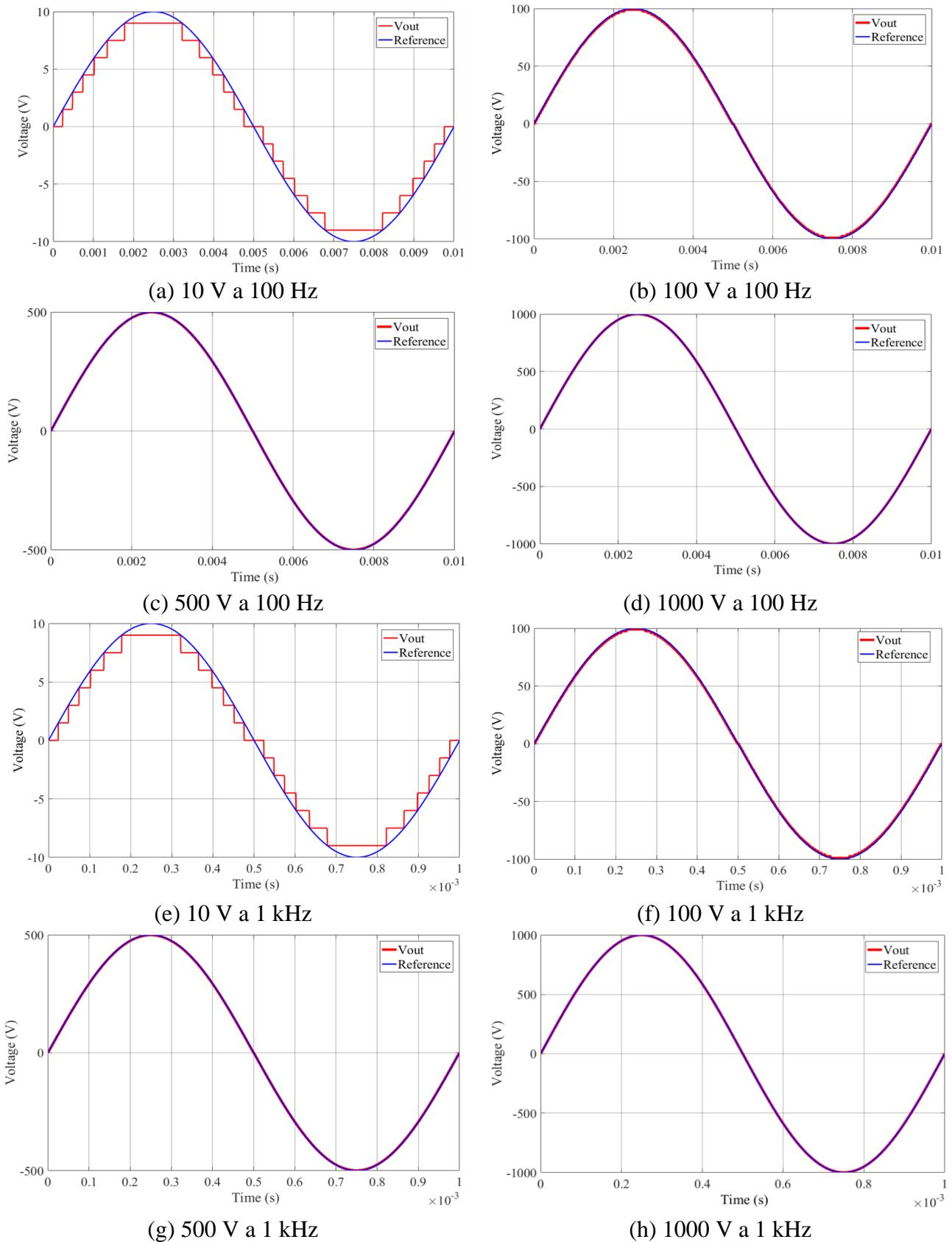

| Figura 19: Simulación del funcionamiento del prototipo a distintos valores de tensión y frecuencia. ....                                             | 35 |

| Figura 20: Diagrama de bloques del convertidor multinivel.....                                                                                       | 38 |

| Figura 21: Convertidor AC/DC. ....                                                                                                                   | 39 |

| Figura 22: Características técnicas AC/DC.....                                                                                                       | 39 |

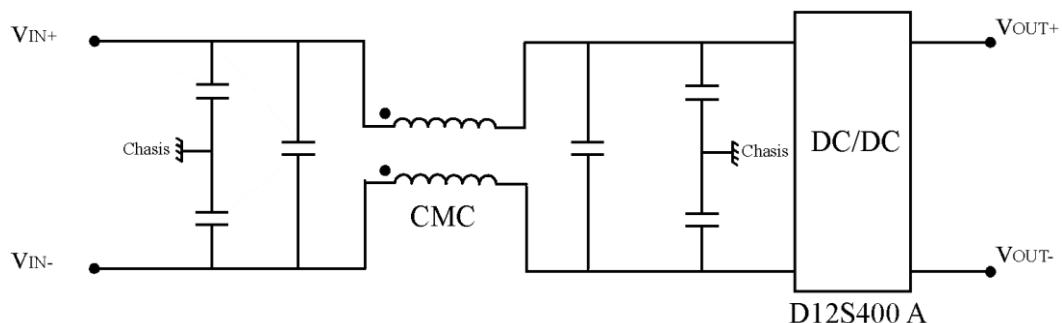

| Figura 23: Etapa de filtrado y conversión DC/DC para alimentar los PM.....                                                                           | 39 |

| Figura 24: Transistores GaN EPC2206 vistos desde bottom. ....                                                                                        | 40 |

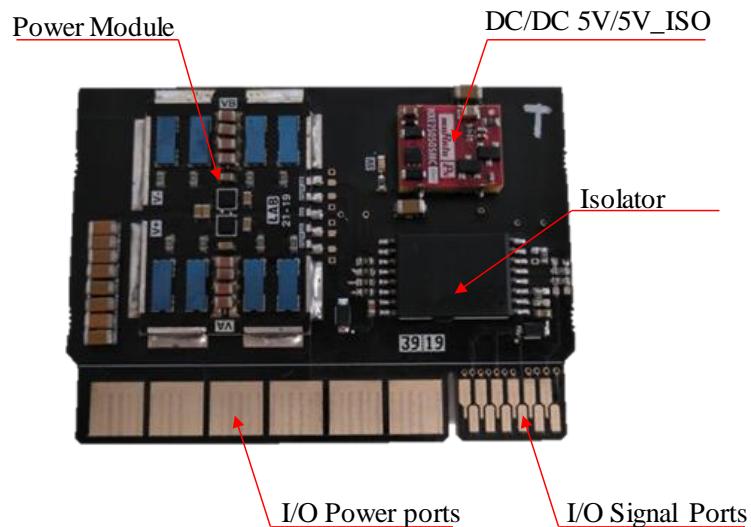

| Figura 25: Power Module (PM). ....                                                                                                                   | 41 |

| Figura 26: Circuito de supervisión para cada PM. ....                                                                                                | 41 |

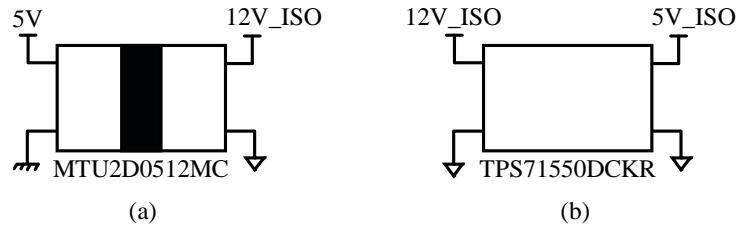

| Figura 27: Reguladores de tensión para alimentar los dispositivos de supervisión. (a) Regulador aislado de 5V a 12V. (b) Regulador de 12V a 5V. .... | 43 |

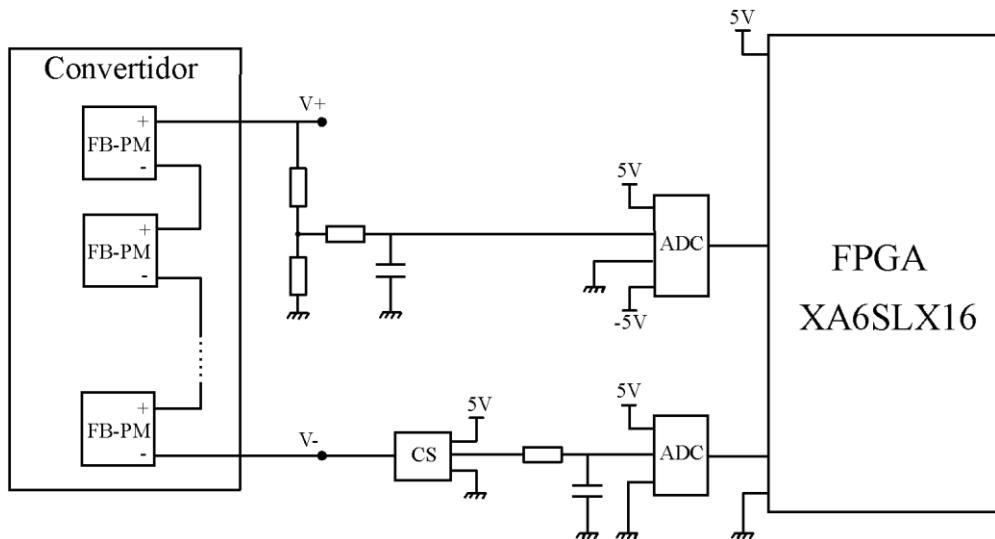

| Figura 28: Circuito de sensado de corriente y tensión del convertidor multinivel.....                                                                | 43 |

| Figura 29: Regulador de tensión para alimentar el ADC. ....                                                                                          | 44 |

| Figura 30: Convertidor DC/DC. (a) Filtro y condensador de bus. (b) DC/DC adicional para obtener los 3V y 1.5V.....                                   | 46 |

| Figura 31: carrier. ....                                                                                                                             | 47 |

| Figura 32: Conector PM con señales digitales y de potencia separadas. ....                                                                           | 48 |

| Figura 33: PCB global de medidas y control de cada módulo y del convertidor.....                                                                     | 49 |

| Figura 34: Esquema PCB de control. ....                                                                                                              | 50 |

| Figura 35: Zoom a un RAIL. ....                                                                                                                      | 51 |

| Figura 36: PCB de control, cara bottom. ....                                                                                                         | 52 |

|                                                                                                             |    |

|-------------------------------------------------------------------------------------------------------------|----|

| Figura 37: Flujo de potencia del convertidor.....                                                           | 53 |

| Figura 38: Montaje del prototipo experimental .....                                                         | 54 |

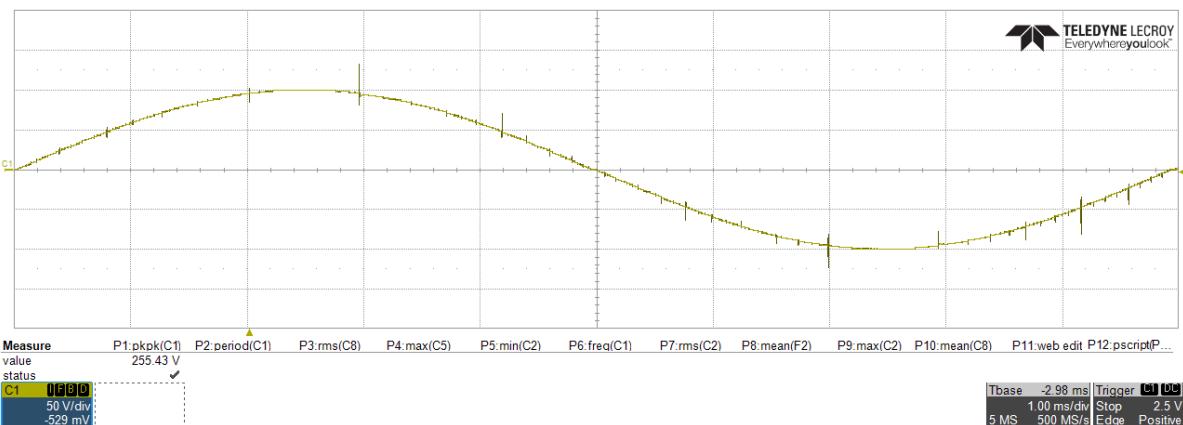

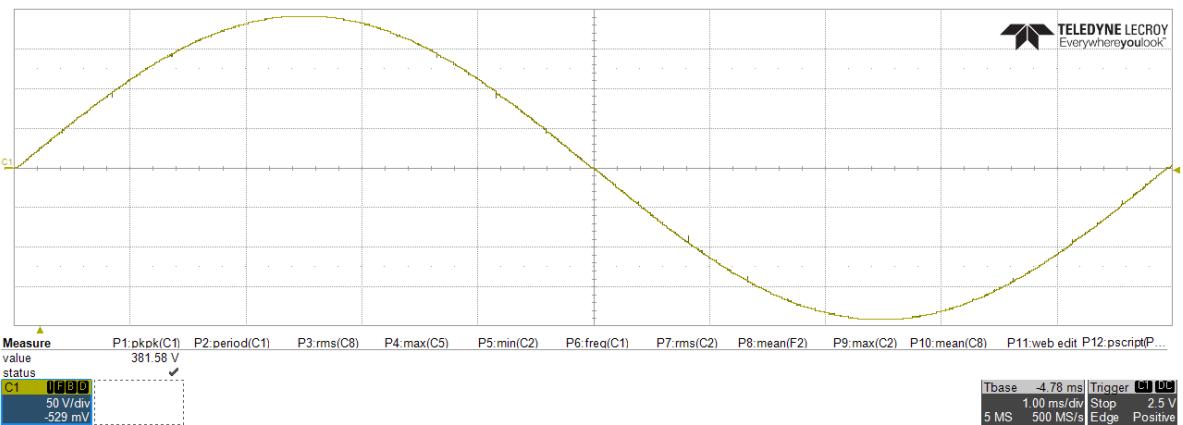

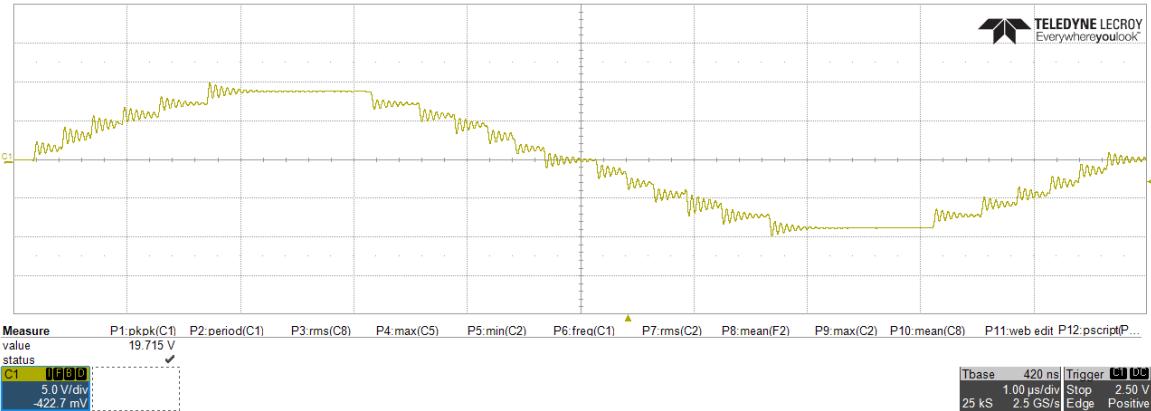

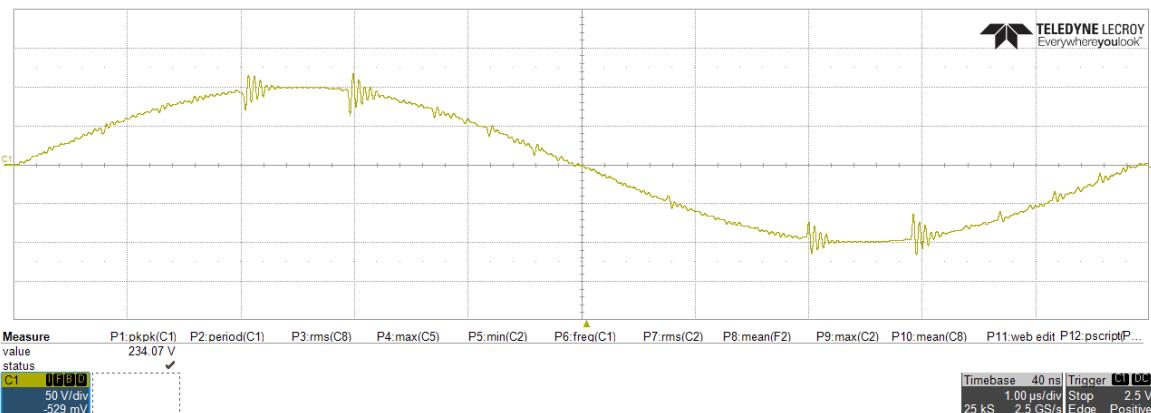

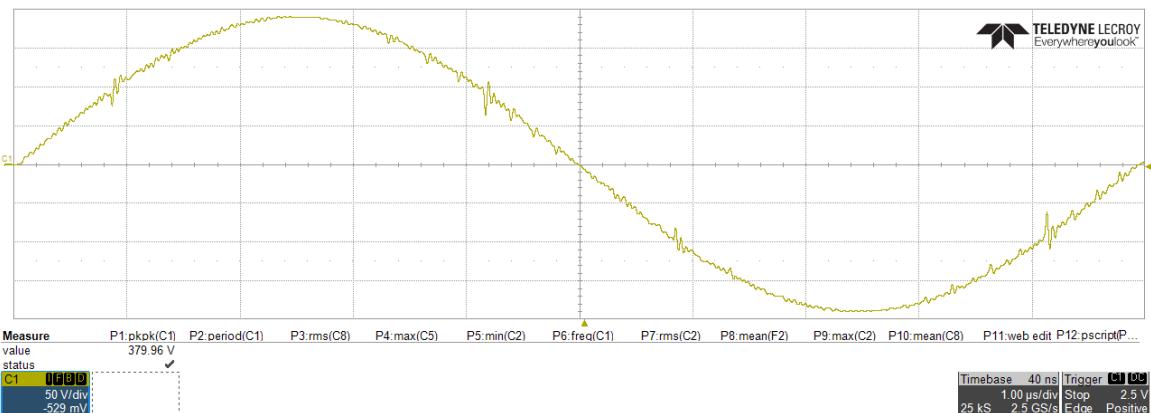

| Figura 39: Forma de onda de tensión de salida experimental. 10 V a 100 Hz (5 V/div. 2 ms/div).....          | 55 |

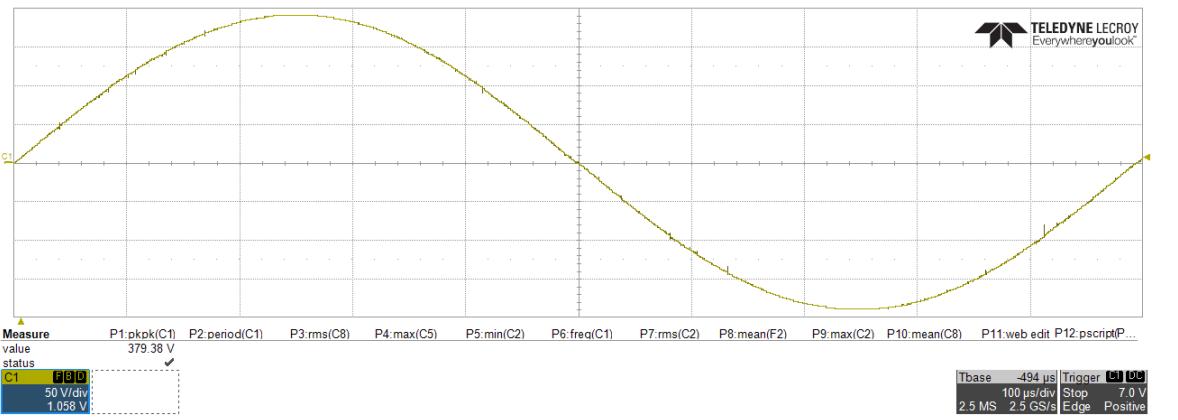

| Figura 40: Forma de onda de tensión de salida experimental. 100V a 100 Hz (50 V/div. 2 ms/div).....         | 55 |

| Figura 41: Forma de onda de tensión de salida experimental. 200 V a 100 Hz (50 V/div. 2 ms/div).....        | 55 |

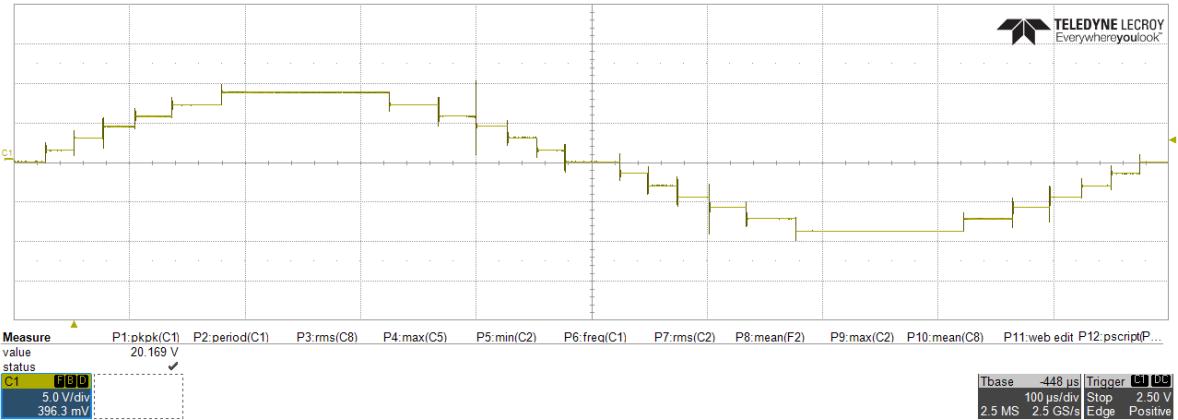

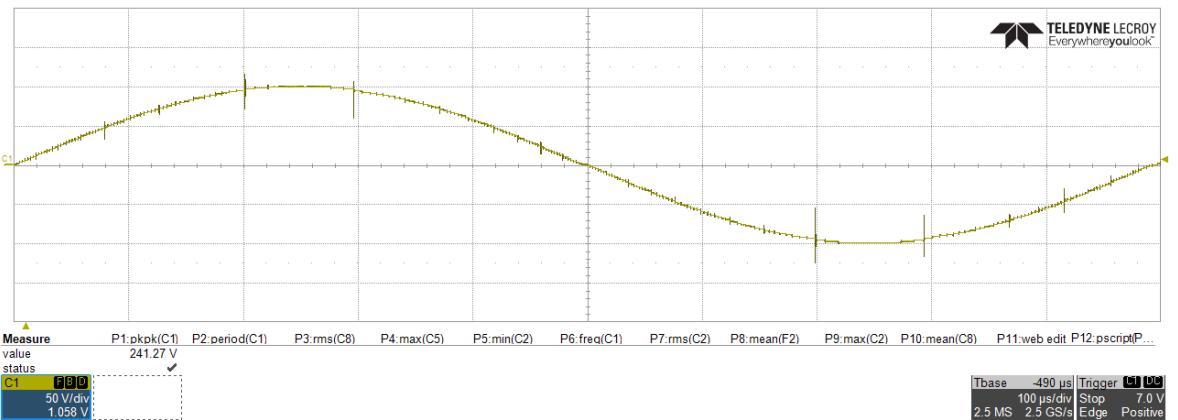

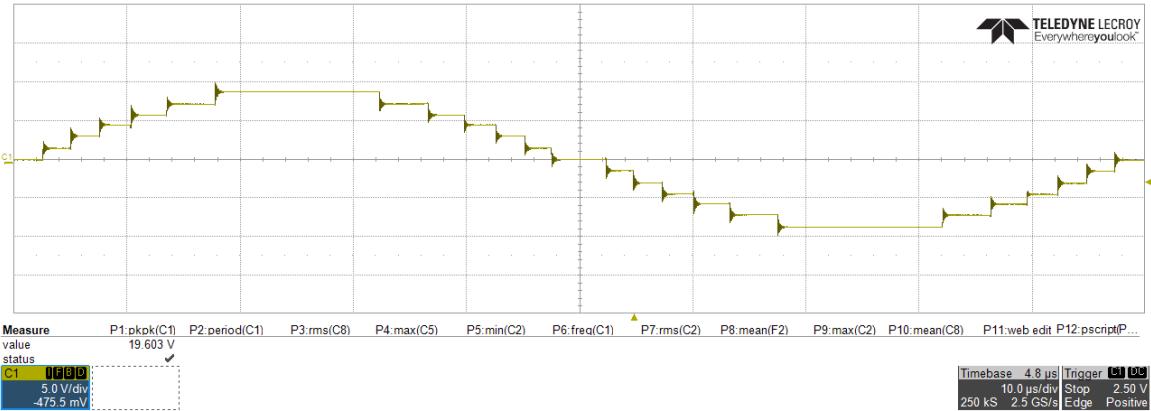

| Figura 42: Forma de onda de tensión de salida experimental. 10 V a 1 kHz (5 V/div. 100 $\mu$ s/div).....    | 56 |

| Figura 43: Forma de onda de tensión de salida experimental. 100 V a 1 kHz (50 V/div. 100 $\mu$ s/div).....  | 56 |

| Figura 44: Forma de onda de tensión de salida experimental. 200 V a 1 kHz. (50 V/div. 100 $\mu$ s/div)..... | 56 |

| Figura 45: Forma de onda de tensión de salida experimental. 10 V a 10 kHz (5 V/div. 10 $\mu$ s/div).....    | 57 |

| Figura 46: Forma de onda de tensión de salida experimental. 100 V a 10 kHz (50 V/div. 10 $\mu$ s/div).....  | 57 |

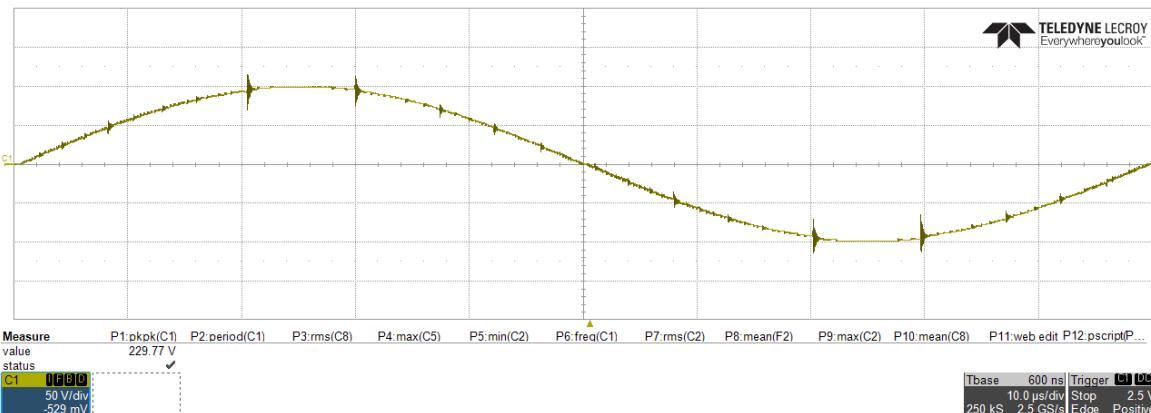

| Figura 47: Forma de onda de tensión de salida experimental. 200 V a 10 kHz (50 V/div. 10 $\mu$ s/div).....  | 57 |

| Figura 48: Forma de onda de tensión de salida experimental. 10 V a 100 kHz (5 V/div. 1 $\mu$ s/div).....    | 58 |

| Figura 49: Forma de onda de tensión de salida experimental. 100 V a 100 kHz (50 V/div. 1 $\mu$ s/div).....  | 58 |

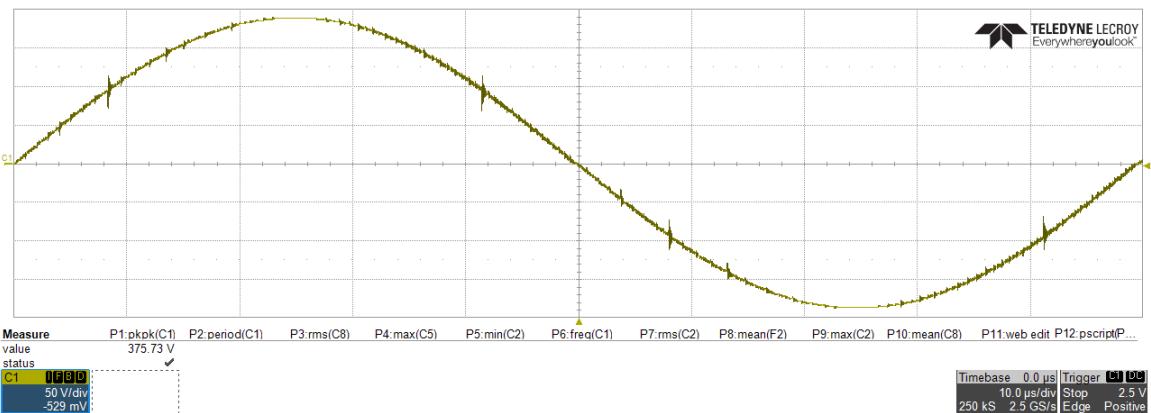

Figura 50: Forma de onda de tensión de salida experimental 200 V a 100 kHz. (50 V/div. 1  $\mu$ s/div)..... 58

# 1 Introducción

## 1.1 Objetivo

El objetivo de este trabajo es diseñar un generador de señales que sea capaz de sintetizar formas de onda arbitrarias de un amplio rango de frecuencias y tensiones. Concretamente una amplitud máxima de +/- 1 kV y frecuencias desde DC hasta 100 kHz entregando a la salida un máximo de 50 A.

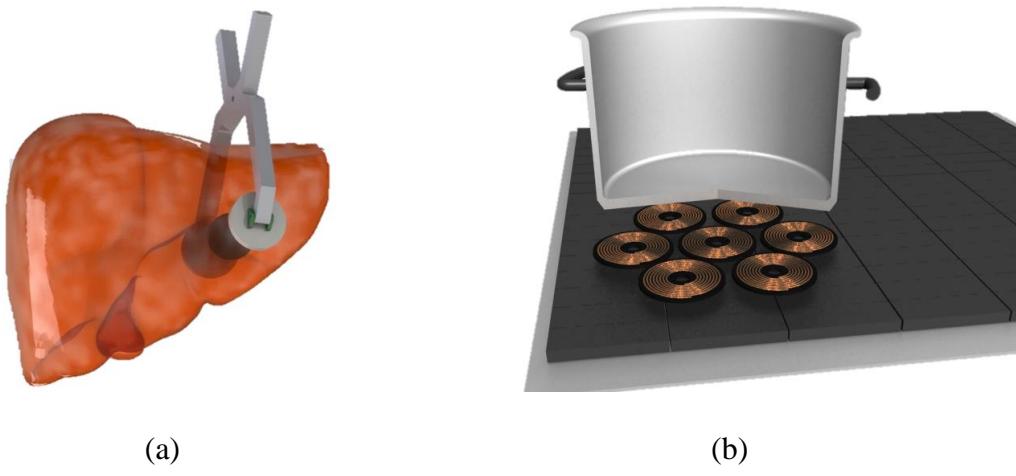

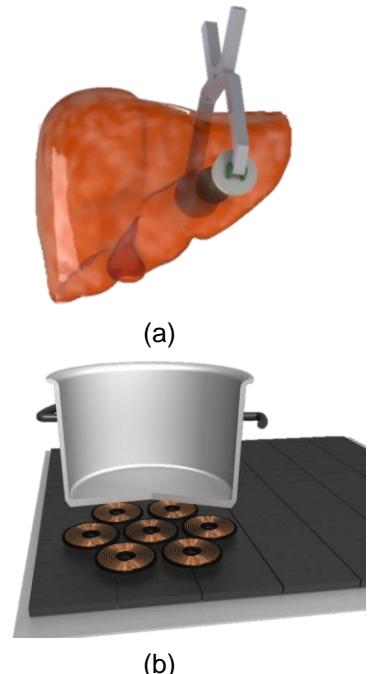

Este tipo de generadores de señales arbitrarias son requeridos en un amplio rango de aplicaciones industriales y biomédicas, donde es necesaria una reproducción precisa de una forma de onda dada, ya sea para excitar una carga en una aplicación industrial, como para aplicar un tratamiento concreto en ciertas aplicaciones biomédicas [1]. En la Figura 1, se muestran algunos ejemplos de aplicación, incluyendo aplicaciones de alta potencia como la tensión aplicada a dos electrodos en paralelo para la electroporación de tejido hepático [2] (a), o la caracterización de cargas para calentamiento por inducción [3] (b).

Figura 1: Aplicaciones propuestas para el generador de señales. (a) Electroporación de tejido hepático. (b) Caracterización de cargas de calentamiento por inducción.

En el pasado, este tipo de generadores han sido limitados en tensión, corriente y frecuencia debido principalmente a la limitación de los dispositivos de potencia [4]. Sin

embargo, los importantes avances en la tecnología de los semiconductores y las topologías utilizadas han permitido mejorar el diseño, y, por lo tanto, los resultados obtenibles con de este tipo de generadores.

En este trabajo se van a mostrar las alternativas valoradas para realizar el generador y se detalla el diseño y la implementación del sistema propuesto, verificando que se cumplen los propósitos marcados anteriormente.

Para verificar que el prototipo funciona correctamente, las simulaciones y verificaciones experimentales se han realizado con ondas sinusoidales, ya que es más fácil obtener comparativos o funciones de mérito como la tasa de distorsión armónica, THD, que ofrece una buena métrica de la calidad de la señal generada. Pero el objetivo final, no obstante, es el de sintetizar cualquier forma de onda, como por ejemplo emulando el comportamiento del condensador de resonancia en una placa de calentamiento por inducción.

## 1.2 Alcance

Para llevar a cabo el objetivo principal de este trabajo fin de máster se proponen las siguientes actividades:

- Estudio del estado del arte. Se realizará un estudio exhaustivo de los convertidores electrónicos de potencia aplicables para lograr la síntesis versátil de las formas de onda objeto de este trabajo. Dentro de este estudio, se realizará especial énfasis en la tecnología de convertidores multinivel.

- Estudio de las estrategias de modulación del convertidor propuesto. Una vez seleccionada la topología electrónica de potencia multinivel adecuada, se realizará un estudio analítico y por simulación de las diferentes

## Capítulo 1: Introducción

estrategias de modulación aplicables, prestando especial atención a aspectos como la calidad de la señal, la complejidad de la solución o su coste.

- Diseño del convertidor propuesto. Una vez seleccionada la topología, el control a implementar y las prestaciones que se desean conseguir, se llevará a cabo la selección de los componentes que formarán el prototipo y su justificará su elección en base a sus especificaciones técnicas. Así mismo, se diseñarán las placas de circuito impreso necesarias.

- Verificación experimental. Finalmente, con el prototipo montado, se sintetizarán diferentes formas de onda en distintos rangos de tensión y frecuencia y se analizarán los resultados.

## 2 Estudio del estado del arte

Para desarrollar el generador de señales que cumpla con las especificaciones mencionadas, se han considerado tres alternativas:

- **Amplificador lineal:** Basado, o bien en transistores lineales, o bien en un amplificador operacional de alta potencia. La desventaja que presenta este tipo de topología, es que al ser lineal las eficiencias obtenidas son bajas y presentan diseños muy voluminosos y costosos. Además, no permite alcanzar todo el rango de tensiones y corrientes que se precisan.

- **Convertidor de alta tensión con control PWM:** Este generador se basa en un único módulo alimentado con hasta 1000 V que, mediante el control de la tensión de bus por medio de un convertidor previo, y el control PWM de los dispositivos de conmutación, genera a la salida la tensión deseada. La principal desventaja de este prototipo es que el rango de frecuencias a sintetizar es muy reducido, obteniendo una alta tasa de distorsión armónica, especialmente en el caso de formas de onda de elevada frecuencia. Así mismo, el diseño del filtro de salida para un rango de frecuencias de operación tan elevado resultaría complejo

- **Convertidor multinivel:** Basado en una topología modular con diferentes módulos de media tensión que, conectados en serie entre sí, son capaces de ofrecer un amplio rango de tensiones. Seleccionando adecuadamente los dispositivos semiconductores, pueden sintetizarse formas de onda de frecuencias muy variadas, y con un correcto dimensionado de la topología pueden entregar la corriente necesaria.

La topología escogida para la realización del generador en este trabajo ha sido la del convertidor multinivel dado que permite lograr un diseño compacto y eficiente, sin necesidad de un complejo filtro de salida.

A continuación, se van a introducir los convertidores multinivel, se van a mostrar los principales tipos que existen actualmente en la industria, así como las principales aplicaciones de cada uno de ellos [5]. Posteriormente, se mostrarán las distintas estrategias de control adoptadas para poder entender de una manera más clara su funcionamiento. Finalmente, se explicará cuál ha sido la topología escogida para este trabajo en base a las especificaciones de diseño que se requieren.

## 2.1 Convertidores multinivel

Los convertidores multinivel son capaces de convertir una tensión de entrada continua en una tensión de salida con diferentes valores discretos escalonados. Estos valores escalonados vendrán dados por la tensión almacenada en cada nivel.

A consecuencia del cambio que está sufriendo el sector energético en dirección hacia las energías más limpias, este tipo de convertidores se están abriendo cada vez más camino en la industria debido a la necesidad de integrar este tipo de energía en la red y asegurar la calidad de la misma. Actualmente existe una dura competencia entre los convertidores clásicos con semiconductores de alta tensión, y los nuevos convertidores multinivel con dispositivos de media tensión.

En el siguiente apartado se mostrarán los principales tipos de convertidor multinivel que actualmente destacan en el mercado, así como sus principales aplicaciones.

### 2.1.1 Tipos y aplicaciones

Actualmente existen, principalmente, tres tipos de convertidores multinivel: *Diode-clamp* o *Neutral Point Clamped* (NPC), *Flying capacitors* (FC) y *Cascaded H-Bridge* (CHB). A continuación, se va a presentar brevemente cada uno de ellos.

#### 2.1.1.1 Neutral Point Clamped (NPC)

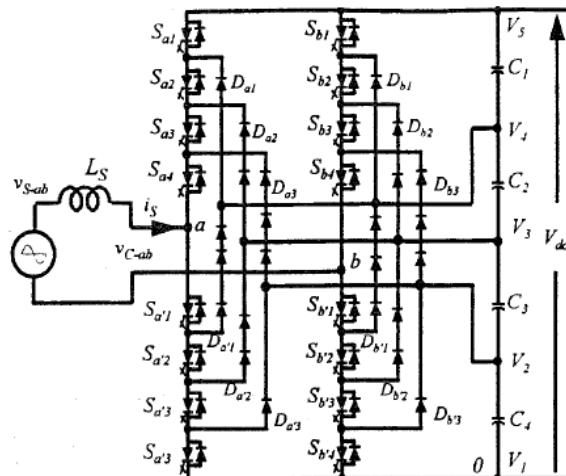

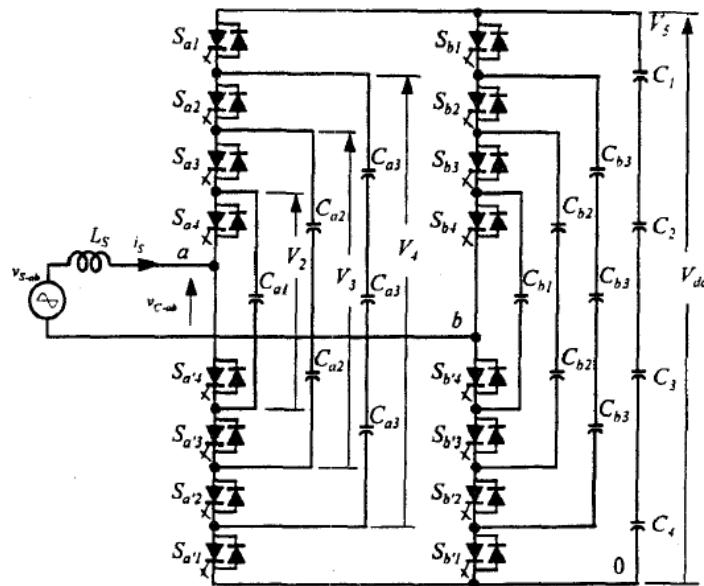

Un convertidor NPC de “ $m$ ” niveles, consiste típicamente en  $m-1$  condensadores en el bus DC y produce  $m$  niveles de tensión. La Figura 2 muestra un convertidor puente completo monofásico de cinco niveles en el que el bus de DC consiste en cuatro condensadores,  $C_1 - C_4$ . Para una tensión de bus  $V_{dc}$ , el voltaje a través de cada condensador es de  $V_{dc}/4$ .

Figura 2: Convertidor puente monofásico NPC de 5 niveles [6].

Con la topología mostrada, se pueden alcanzar cinco niveles de tensión diferentes de  $V_{ao}$  comutando los diferentes dispositivos, desde  $V_{dc}$  a 0 V. En la Figura 3, se muestra cómo se pueden obtener cada uno de los niveles de tensión en función del estado de conducción o no de los dispositivos.

| Output<br>$V_{a0}$ | Switch State |          |          |          |           |           |           |           |

|--------------------|--------------|----------|----------|----------|-----------|-----------|-----------|-----------|

|                    | $S_{a1}$     | $S_{a2}$ | $S_{a3}$ | $S_{a4}$ | $S_{a'1}$ | $S_{a'2}$ | $S_{a'3}$ | $S_{a'4}$ |

| $V_5 = V_{dc}$     | 1            | 1        | 1        | 1        | 0         | 0         | 0         | 0         |

| $V_4 = 3V_{dc}/4$  | 0            | 1        | 1        | 1        | 1         | 0         | 0         | 0         |

| $V_3 = V_{dc}/2$   | 0            | 0        | 1        | 1        | 1         | 1         | 0         | 0         |

| $V_2 = V_{dc}/4$   | 0            | 0        | 0        | 1        | 1         | 1         | 1         | 0         |

| $V_1 = 0$          | 0            | 0        | 0        | 0        | 1         | 1         | 1         | 1         |

Figura 3: Ejemplo de funcionamiento de un convertidor NPC de 5 niveles [6].

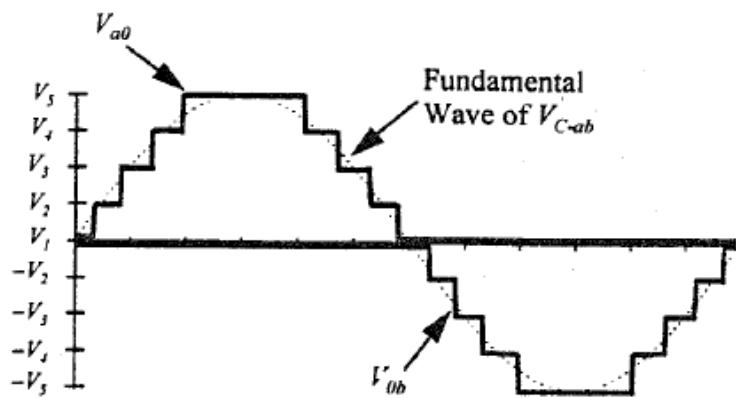

Si se representa la onda de tensión sintetizada junto a la real, el resultado sería el que se observa en la Figura 4, siendo  $V_{a0}$  la onda sintetizada por el convertidor en el semiciclo positivo, y  $V_{0b}$  en el semiciclo negativo.

Figura 4: Tensión de línea de un convertidor NPC de 5 niveles [6].

Se observa cómo el convertidor es capaz de sintetizar con gran precisión la tensión de referencia. El perfil de carga y descarga de los condensadores es un tema crucial en este tipo de topologías, el cual se muestra en la Figura 4.

Figura 5: Perfil de carga y descarga de los condensadores. (a) Tensión y corriente en fase. (b) Tensión y corriente desfasados 90 ° [6].

En esta figura, se puede observar cómo la descarga de los condensadores es asimétrica, lo que a la larga puede conllevar un desequilibrio entre las tensiones de cada nivel que supondría un problema en el convertidor, ya que no será capaz de llegar a la tensión de referencia impuesta.

A modo de resumen, a continuación, se presentan las ventajas e inconvenientes de esta topología.

Como ventajas destacan las siguientes:

- Cuando el número de niveles es lo suficientemente alto, el contenido de armónicos será lo suficientemente bajo para evitar la necesidad de filtros.

- Alta eficiencia y el flujo de potencia reactiva puede ser controlado.

- Control sencillo para un sistema de interconexión back to back.

Y como desventajas:

- Se requieren un número de diodos excesivo cuando el número de niveles es alto.

- Es difícil implementar un control real del flujo de potencia para el convertidor

### 2.1.1.2 Flying capacitors (FC)

Un convertidor basado en FC de nivel  $m$ , tiene  $m$  niveles de tensión y necesita  $(m-1)$  condensadores en el bus de DC. En la Figura 6 se muestra el esquemático de un convertidor monofásico de 5 niveles utilizando FC.

Figura 6: Convertidor monofásico de 5 niveles utilizando la topología de FC [6].

A la hora de sintetizar la tensión de referencia en este tipo de convertidores, se tiene más flexibilidad que en la topología NPC, y la tensión  $V_{a0}$  puede ser alcanzada a través de muchas más combinaciones. Una posible combinación para alcanzar cada nivel de tensión será la representada en la Figura 7.

| Output<br>$V_{a0}$ | Switch State |          |          |          |           |           |           |           |

|--------------------|--------------|----------|----------|----------|-----------|-----------|-----------|-----------|

|                    | $S_{a1}$     | $S_{a2}$ | $S_{a3}$ | $S_{a4}$ | $S_{a'4}$ | $S_{a'3}$ | $S_{a'2}$ | $S_{a'1}$ |

| $V_5 = V_{dc}$     | 1            | 1        | 1        | 1        | 0         | 0         | 0         | 0         |

| $V_4 = 3V_{dc}/4$  | 1            | 1        | 1        | 0        | 1         | 0         | 0         | 0         |

| $V_3 = V_{dc}/2$   | 1            | 1        | 0        | 0        | 1         | 1         | 0         | 0         |

| $V_2 = V_{dc}/4$   | 1            | 0        | 0        | 0        | 1         | 1         | 1         | 0         |

| $V_1 = 0$          | 0            | 0        | 0        | 0        | 1         | 1         | 1         | 1         |

Figura 7: Ejemplo de funcionamiento de un convertidor de FC de 5 niveles [6].

El hecho de que existan varias combinaciones es beneficioso porque permite equilibrar mejor las tensiones de los condensadores de bus. En cuanto a las formas de onda, el resultado sería similar al del convertidor NPC mostrado en la Figura 4.

Al igual que para el convertidor anterior, se van a mostrar las ventajas e inconvenientes de esta topología.

Ventajas:

- La gran cantidad de condensadores de almacenamiento proporciona mayor seguridad ante un corte de energía.

- Proporciona redundancia de combinación de conmutadores para equilibrar diferentes niveles de tensión.

- Cuando el número de niveles es lo suficientemente alto, el contenido de armónicos será lo suficientemente bajo para evitar la necesidad de filtros.

- Se puede controlar tanto el flujo de potencia real como el reactivo, lo que hace posible que el convertidor de fuente de tensión sea un candidato para la transmisión de alta tensión en corriente continua.

Inconvenientes:

- Se requiere un número excesivo de condensadores de almacenamiento cuando el número de niveles del convertidor es alto, luego mayor precio y más volumen

- El control del inversor será muy complicado, y la frecuencia de conmutación y las pérdidas de conmutación serán elevadas para la transmisión de potencia real.

### **2.1.1.3 Cascaded H-Bridge (CHB)**

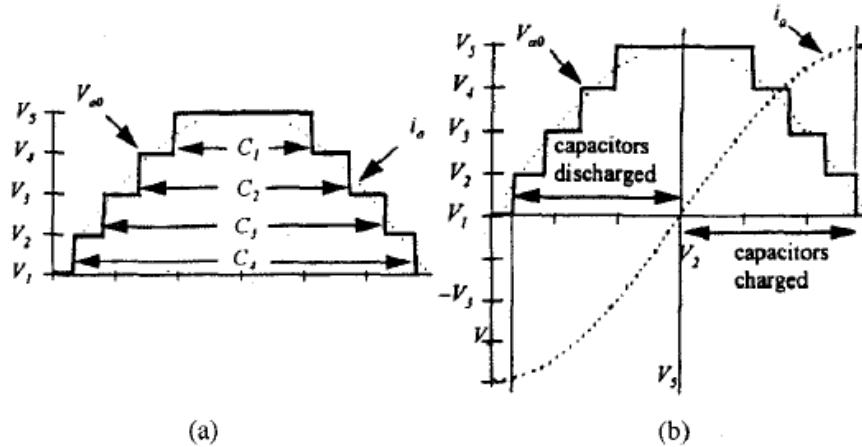

Este convertidor presenta novedades frente a los anteriores. Consiste principalmente en un conjunto de inversores puestos en serie con un condensador de bus en cada uno de ellos. Cada módulo o inversor puede generar tres salidas:  $-V_{DC}$ , 0 y  $V_{DC}$  y la tensión de salida del convertidor es la suma de la tensión de cada uno de los módulos. Además, se evita un exceso de hardware con respecto a las otras alternativas, ya que no se necesitan diodos ni condensadores extras.

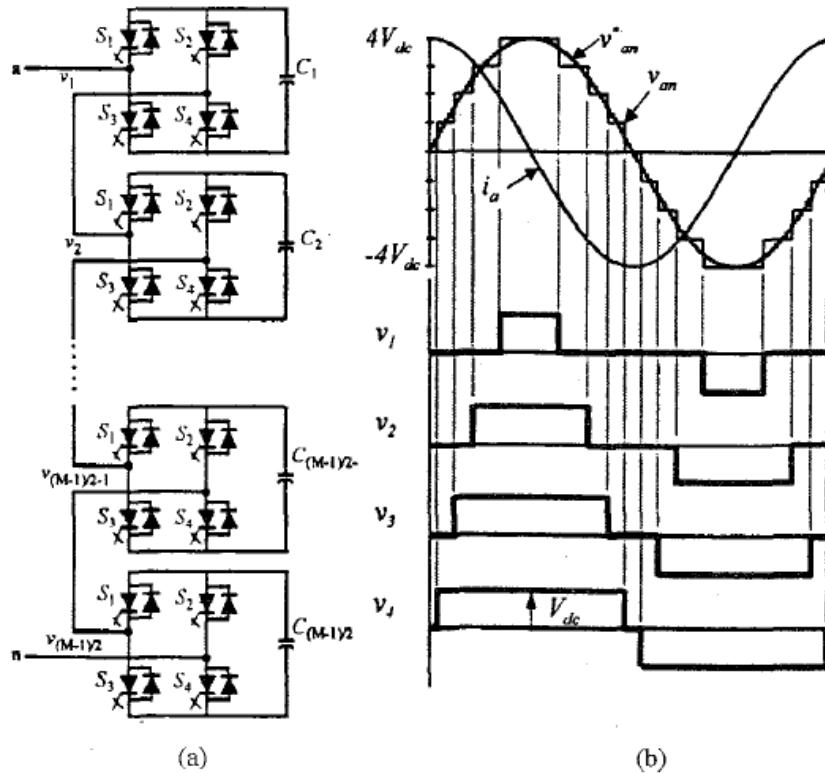

La topología de este convertidor, así como las formas de onda a la salida son las que se muestran en la Figura 8.

Figura 8: Topología y formas de onda de un convertidor multinivel CHB. (a) Topología. (b) Formas de onda de un convertidor de 9 niveles [7].

Se puede observar como la forma de la tensión a la salida del inversor sigue con gran precisión la tensión de referencia. También se puede ver como el tiempo en el que cada condensador está entregando corriente es asimétrico, lo que supone un desbalanceo entre sus tensiones. Esto puede solucionarse utilizando fuentes de tensión aisladas externas para suministrar el voltaje necesario. De esta manera, se evita la descarga de los condensadores y existe un mayor equilibrio entre sus tensiones.

Nuevamente, se van a mostrar las ventajas e inconvenientes de este diseño.

Ventajas:

- Requiere un menor número de componentes que el resto de implementaciones multinivel para alcanzar el mismo número de niveles de tensión.

- Presenta una gran modularidad y sencillez a la hora de realizar el montaje, ya que no hay diodos de sujeción ni condensadores de compensación de tensión y todos los niveles tienen la misma estructura.

- En caso de alimentar los módulos con fuentes de tensión aisladas, se evita el desbalanceo entre las tensiones de los condensadores de bus de cada módulo.

Inconvenientes:

- Para determinadas aplicaciones se necesitan fuentes DC aisladas para poder alimentar cada módulo, lo que supone un incremento de volumen y coste.

A modo de resumen general, en la Figura 9, se muestra una comparativa de hardware entre los tres convertidores que se han explicado, para  $m$  niveles de tensión.

| Convertidor                        | NPC                  | FC                     | CHB              |

|------------------------------------|----------------------|------------------------|------------------|

| <b>Dispositivos de conmutación</b> | $(m-1) \times 2$     | $(m-1) \times 2$       | $(m-1) \times 2$ |

| <b>Diodos principales</b>          | $(m-1) \times 2$     | $(m-1) \times 2$       | $(m-1) \times 2$ |

| <b>Diodos clamp</b>                | $(m-1) \times (m-2)$ | 0                      | 0                |

| <b>Condensadores de bus</b>        | $(m-1)$              | $(m-1)$                | $(m-1)/2$        |

| <b>Condensadores de balanceo</b>   | 0                    | $(m-1) \times (m-2)/2$ | 0                |

Figura 9: Comparativa de hardware entre los distintos tipos de convertidores multinivel para generar  $m$  niveles de tensión [7].

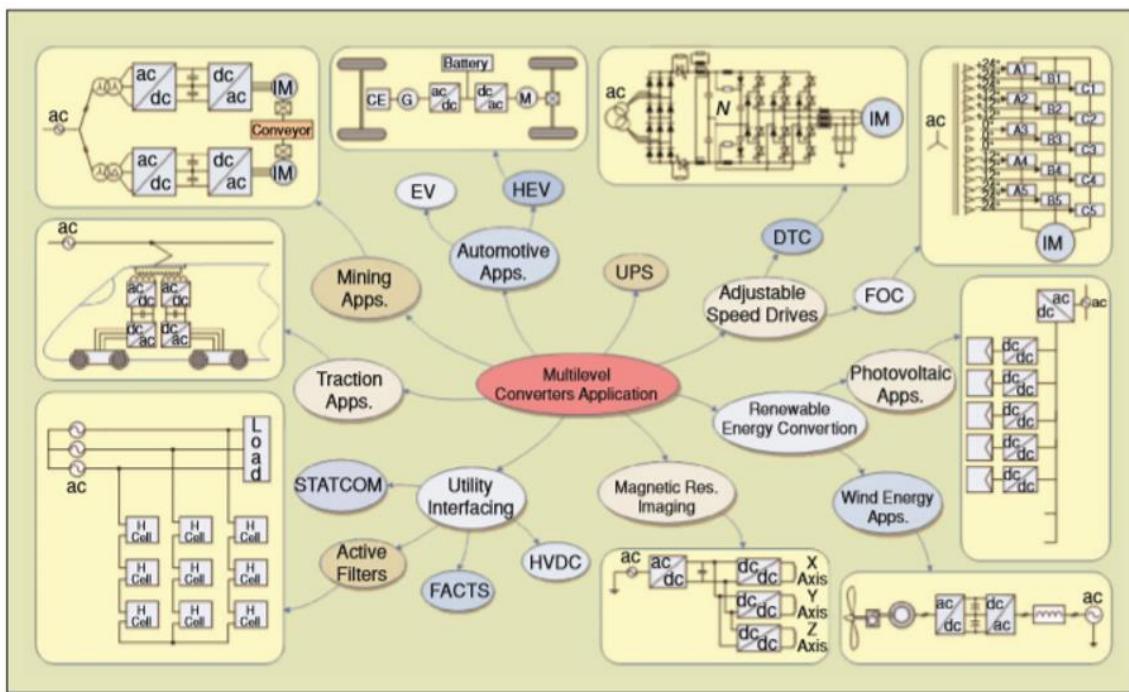

En cuanto a las aplicaciones de los convertidores multinivel, suelen ser una solución muy interesante para aplicaciones de media tensión y alta potencia.

Como se ha explicado anteriormente, el convertidor multinivel que se va a desarrollar en este trabajo está orientado fundamentalmente a aplicaciones de calentamiento por inducción y biomédicas, pero existen otros muchos campos en el mundo industrial en los que se podría aplicar [8].

Los convertidores multinivel suelen ser soluciones muy adecuadas para configuraciones back to back para aplicaciones regenerativas (conexión a la red de fuentes de energía renovables como la eólica, biomasa, solar...), accionamientos de motores de AC de alta potencia, convertidores AC/AC [9] y AC/DC [10], filtros activos, compensación de reactiva (STATCOM [11-13]), vehículos eléctricos [14] etc...

A modo de resumen, en la Figura 9 se muestran algunas aplicaciones de los convertidores multinivel.

Figura 10: Aplicaciones convertidores multinivel [15].

### 2.1.2 Estrategias de control

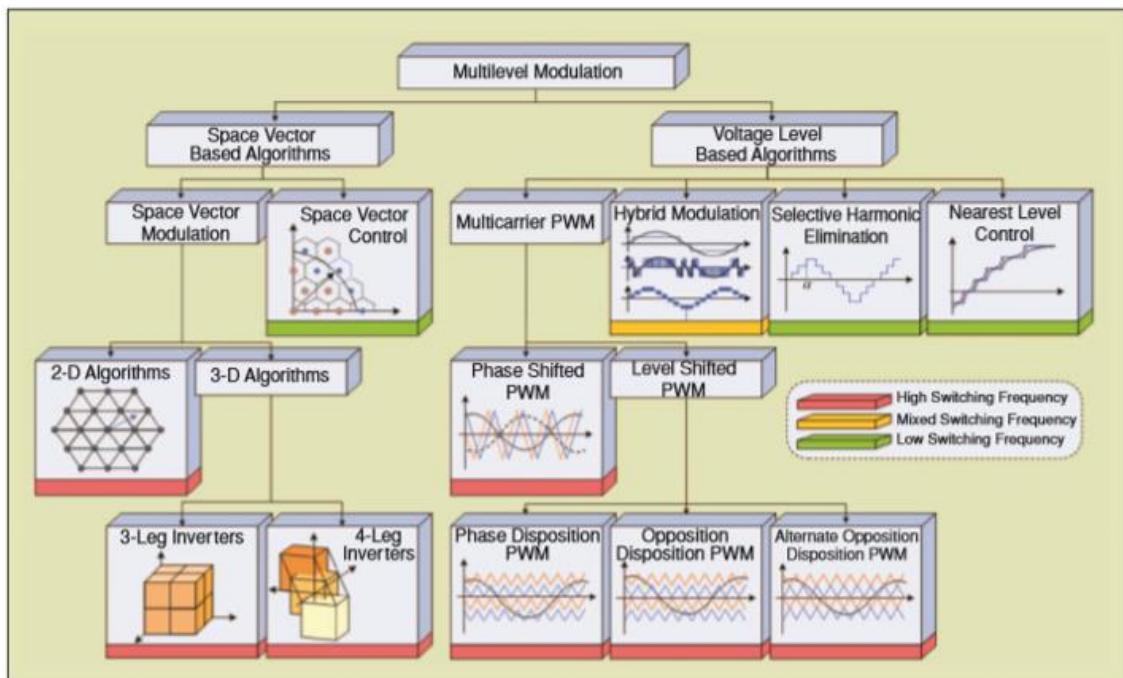

En este apartado se van a mostrar brevemente las distintas técnicas de control que existen para la modulación de este tipo de convertidores [16].

Para realizar el control de este tipo de convertidores, existen dos tipos de modulación: En primer lugar, está el dominio vectorial espacio-estado, donde se genera

el vector de tensión en función de la tensión de referencia, y en segundo lugar está el dominio temporal, donde lo que se hace es generar un nivel de tensión a lo largo de un marco temporal (control PWM [17, 18], eliminación de armónicos, ...).

En la Figura 11 se muestra un esquema general de los tipos de control para los convertidores multinivel, en función de la frecuencia de conmutación que producen.

Figura 11: Clasificación según el tipo de modulación en convertidores multinivel [15].

Para ponerlo en relación con los tipos de convertidores multinivel descritos anteriormente, se muestra la Figura 11, en la cual se representa una tabla donde se muestra qué tipos de controles son más adecuados para cada tipo de convertidor, y cuáles son menos recomendables o no aplicables.

| Modulation Methods | Topologies |    |     |

|--------------------|------------|----|-----|

|                    | NPC        | FC | CHB |

| SVM                | ✓          | ✓  | ✓   |

| LS-PWM             | ✓          | ✓  | —   |

| PS-PWM             | ✗          | ✓  | ✓   |

| Hybrid Modulation  | ✗          | ✗  | ✓   |

| SHE                | ✓          | ✓  | ✓   |

| SVC                | —          | ✓  | ✓   |

| NLC                | —          | ✓  | ✓   |

✓ Applicable/Recommended ✗ Not Applicable — Applicable/Not Recommended

Figura 12: Aplicabilidad de los distintos métodos de modulación a cada una de las topologías de convertidores multinivel [15].

Concretamente, en este trabajo se han valorado dos tipos de controles de entre los mostrados anteriormente. Por un lado un control basado en modulación PWM, y por otro lado un control basado en *Nearest Level Control* (Control en base a nivel cercano) mostrados en la Figura 11

Una vez explicados los tipos de convertidores multinivel, así como ver los tipos de control que se van a analizar, en el siguiente apartado se muestra la topología escogida, así como una comparación entre las prestaciones de la misma utilizando distintos controles.

### 3 Simulación y análisis

En este apartado se van a explicar las especificaciones de diseño para justificar la topología de la etapa y se van a analizar las alternativas de control para implementar el convertidor, estableciendo una comparativa entre cada una de ellas en base a una serie de parámetros.

Una vez hecha la comparativa, se escogerá la topología definitiva y se mostrará su correcto funcionamiento en simulación para distintas frecuencias y tensiones.

#### 3.1 Especificaciones de diseño y topología de la etapa

Las especificaciones de diseño del convertidor son las siguientes:

- Amplitud máxima de tensión: +/- 1 kV.

- Corriente de salida: +/- 50 A.

- Rango de frecuencias a sintetizar: DC – 100 kHz.

- Frecuencia de conmutación máxima: 5 MHz.

La topología seleccionada para el convertidor multinivel es un CHB por diferentes razones que se exponen a continuación.

En primer lugar, con la topología CHB se reduce considerablemente el hardware con respecto a las otras alternativas especialmente cuando el número de niveles es elevado. Además, la topología es mucho más escalable, ya que en el convertidor NPC o FC, una vez que se fija la tensión de bus es muy difícil modificarla, en cambio en el CHB se pueden añadir más módulos sin problema aparente. Finalmente, en cuanto al control, se pueden implementar un mayor número de controles en el convertidor CHB con una mayor sencillez que para el resto de alternativas.

### 3.2 Alternativas valoradas

La tensión máxima que se va a considerar por módulo a la hora de realizar la simulación van a ser 50 V. El problema que surge al tener esa tensión de 50 V por módulo, es cómo realizar un ajuste fino para no tener escalones de tensión de 50 V y poder tener valores de tensión intermedios a la salida.

Para poder solventar este problema, se han evaluado tres alternativas:

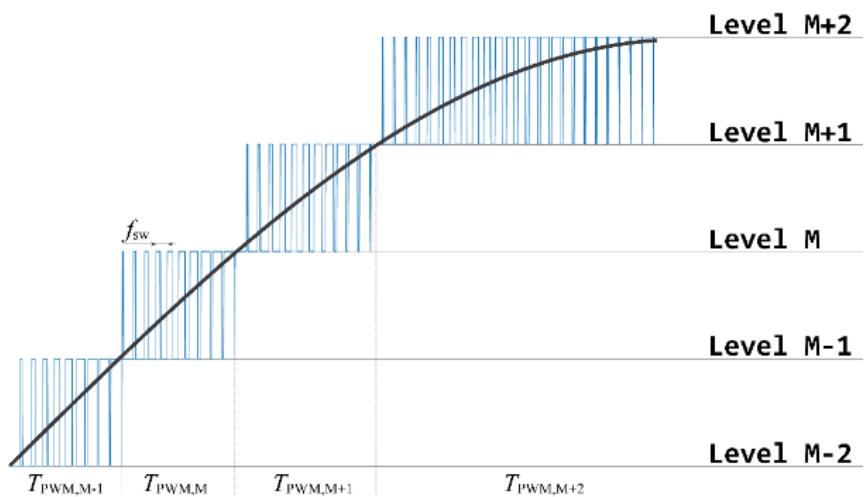

- **Multi-PWM (Voltaje constante y PWM variable):** Uno de los módulos realizará el ajuste fino con un duty variable con control PWM. Este control irá rotando por todos los módulos para que conmuten el mismo número de veces (aproximadamente) cada uno. La tensión a la salida del convertidor sería como la mostrada en la Figura 13.

Figura 13: Tensión de salida del convertidor multinivel con estrategia de modulación PWM.

- **Uni-PWM (Voltaje constante y PWM fijo):** Similar a la alternativa anterior, pero el módulo que sigue el control PWM será siempre el mismo. Por ello, los dispositivos de este módulo tendrán que ser diferentes y tendrá que estar conectado a tierra con un filtro LC para filtrar el ruido que pueda

generarse con las conmutaciones. La tensión de salida es la misma que para la estrategia anterior, mostrada en la Figura 13.

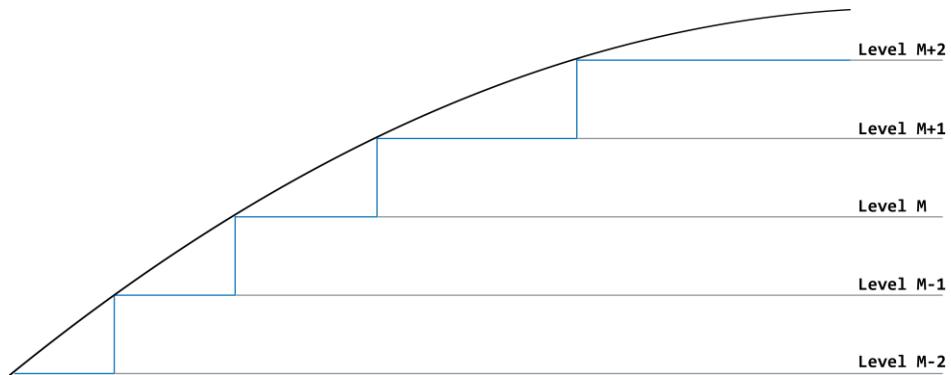

- **DAC (Voltaje variable):** En este caso se contará con módulos de diferentes tensiones (50 V, 25 V, 12,5 V, 6,25 V, 3 V y 1,5 V). El ajuste fino será realizado por los módulos de menor tensión. La forma de onda de la tensión a la salida del convertidor será la mostrada en la Figura 14.

*Figura 14: Tensión de salida del convertidor multinivel con módulos de tensión variable.*

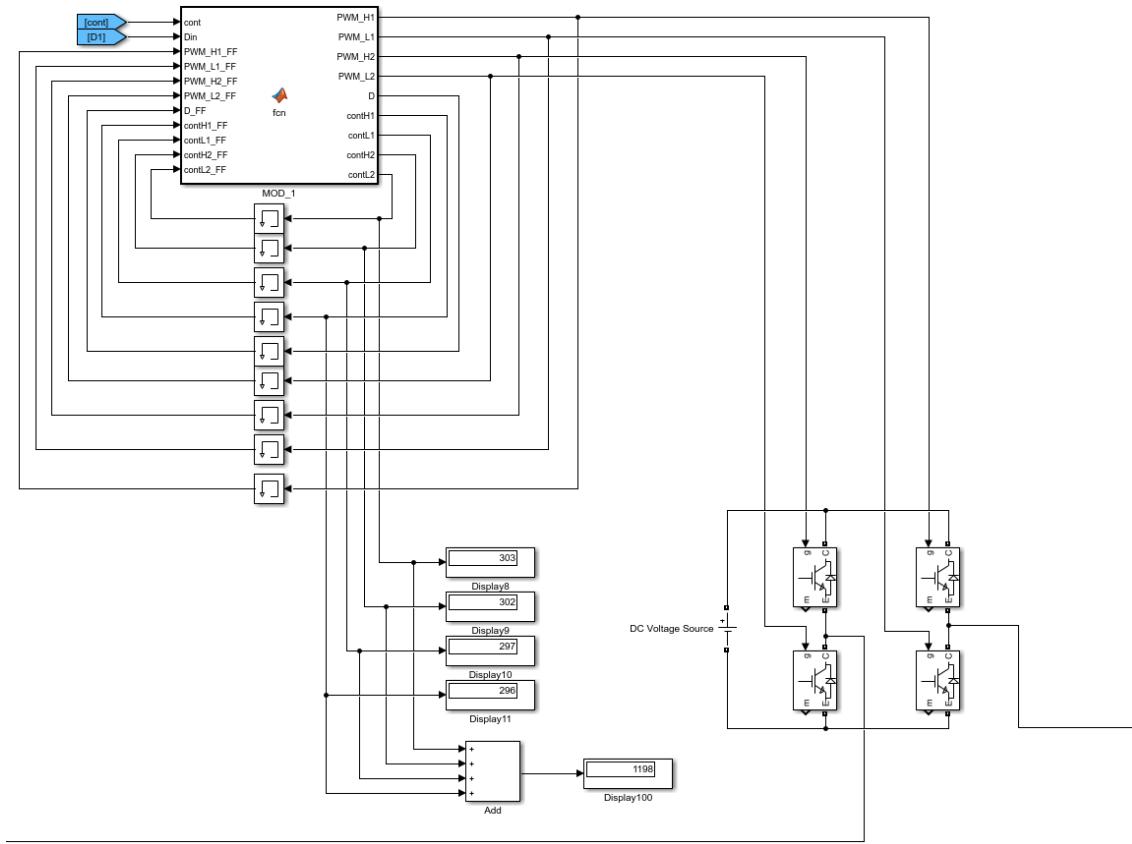

En la Figura 15, se muestra el modelo que se ha implementado en Simulink para modelar el convertidor. Los resultados que se mostrarán en el siguiente apartado para la comparativa entre alternativas, son resultado de la simulación con todos los módulos necesarios para cada una de ellas.

Figura 15: Modelo de simulación para un módulo del convertidor.

### 3.3 Comparativa entre alternativas

Para realizar la comparación entre las tres alternativas, se van a atender a cuatro factores: número de módulos, pérdidas por conmutación, rizado (basado en la tasa de distorsión armónica, THD) y complejidad del diseño.

#### 3.3.1 Número de módulos

Para establecer el número de módulos del que se va a disponer, hay que basarse en la tensión máxima que se quiere generar, es decir, +/- 1 kV.

Para las dos primeras alternativas, todos los módulos son iguales y de 50 V, luego los módulos necesarios serán:

$$\frac{1000 \text{ V}}{50 \text{ V/módulo}} = 20 \text{ módulos} \quad (1)$$

Para la tercera alternativa, el número de módulos variará ya que tienen diferentes tensiones. El módulo estándar, al igual que para los anteriores, será de 50V, pero también habrá módulos de 25 V, 12,5 V, 6,25 V, 3 V y 1,5 V. Por tanto, para llegar a 1 kV de tensión que se necesita generar, se necesitarán 19 módulos estándar de 50 V más uno de cada tensión mencionada, por lo tanto, se obtiene un total de 24 módulos.

### 3.3.2 Pérdidas por conmutación

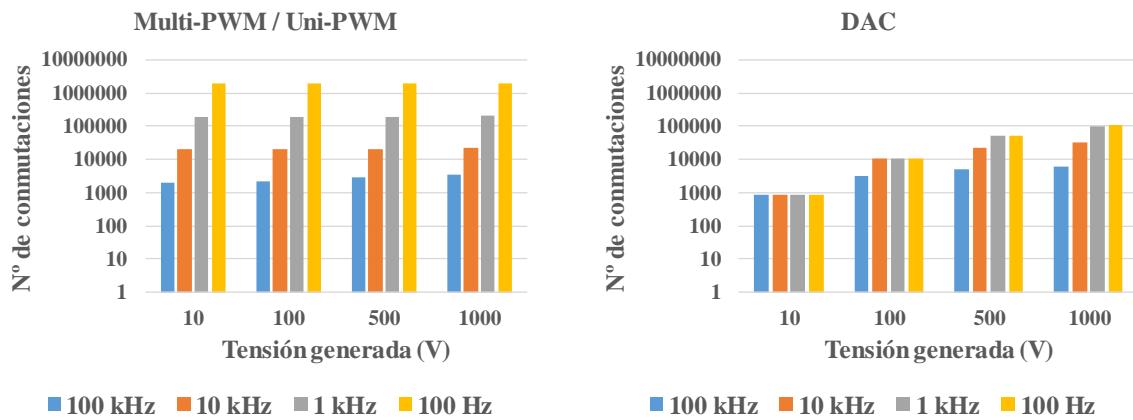

Para analizar las pérdidas por conmutación, en lugar de calcularlas en términos de potencia, se han calculado el número total de conmutaciones de todos los dispositivos para diferentes frecuencias y tensiones a la salida durante 10 ciclos.

Se ha tratado de representar un seno de amplitud 10 V, 100 V, 500 V y 1000 V a unas frecuencias de 100 Hz, 1 kHz, 10 kHz y 100 kHz. Los resultados se muestran en la Figura 16.

Figura 16: Número de conmutaciones para cada alternativa.

En el caso de las alternativas con control PWM, el número de conmutaciones es prácticamente el mismo, ya que lo único que varía es el módulo que sigue el control PWM, que en el caso del Multi-PWM son todos y en el del Uni-PWM es uno solo.

Para el caso del DAC, se puede observar como el número de conmutaciones es significativamente menor que para las otras dos alternativas, sobre todo a bajas frecuencias llegando a ser un orden de magnitud menos.

Este análisis es muy importante ya que las pérdidas por conmutación van directamente asociadas a la eficiencia del prototipo, y éste ha de ser capaz de funcionar correctamente a cualquier tensión y frecuencia dentro de sus especificaciones.

### 3.3.3 Rizado (THD)

Para el caso del rizado, se han analizado los mismos casos que para las pérdidas por conmutación y se ha calculado la tasa de distorsión armónica (THD) en cada caso. Los resultados se pueden observar en la Figura 17.

Figura 17: Análisis de distorsión armónica, THD, para cada alternativa.

Se observa como para la tensión más pequeña, de 10 V, el THD en las estrategias de control PWM se dispara, ya que los módulos son de 50 V, y aunque se realice un buen control PWM el rizado es muy grande, en cambio para el DAC, el rizado es en torno al 8%, ya que, para llegar a esa tensión, únicamente se activan los módulos de 1,5 V, 3 V y 6,25 V.

De igual modo, para tensiones más altas, sigue teniendo un mejor comportamiento el DAC ya que tiene una mayor resolución que las otras dos alternativas. Se observa también como el rizado aumenta conforme aumenta la frecuencia, sobre todo apreciable en el DAC, pero sigue siendo mucho menor que para las técnicas de control PWM (0% - 4% en el DAC frente a 3% - 25% en PWM).

Este aspecto del rizado también es muy importante ya que, cuanto menos rizado se obtenga, más preciso es el prototipo y menor necesidad de filtros externos se necesitan para adecuar la señal.

### 3.3.4 Complejidad del diseño

En cuanto a la complejidad del diseño se ha valorado sobre todo la modularidad y robustez del prototipo, así como la flexibilidad ante posibles fallos.

En este aspecto, la técnica de Multi-PWM es la más sencilla y que menor complejidad presenta, ya que todos los módulos son iguales, de la misma tensión y conmutan el mismo número de veces, lo cual implica que en caso de fallo de uno de los módulos, se puede sustituir de manera sencilla por otro igual.

Para el caso de la técnica Uni-PWM, todos los módulos serán de 50 V, pero uno de ellos estará conmutando continuamente por lo que necesitará otros dispositivos más robustos y una etapa de filtrado LC para filtrar el ruido. Esto le hace perder un punto de modularidad y flexibilidad antes fallos ya que, si el fallo se produce en el módulo que conmuta, es crítico.

Por último, para el DAC, pese a que se tienen módulos de diferente tensión, los dispositivos van a ser los mismos, es decir, todos los módulos serán iguales por lo que en ese aspecto se tiene una buena modularidad y una buena respuesta frente a fallos. Como contrapartida, será necesario generar tensiones aisladas de distinto valor en cada nivel.

Finalmente, a modo de resumen, en la Figura 18 se muestra una tabla comparativa entre cada una de las alternativas.

| Alternativa | Nº de módulos | Pérdidas por conmutación | Rizado (THD) | Complejidad del diseño |

|-------------|---------------|--------------------------|--------------|------------------------|

| Multi-PWM   | ✓             | ✗                        | ✗            | ✓                      |

| Uni-PWM     | ✓             | ✗                        | ✗            | ✗                      |

| DAC         | ✗             | ✓                        | ✓            | ✗                      |

Figura 18: Tabla resumen de comparación entre las tres alternativas valoradas.

Se puede observar como en número de módulos y complejidad del diseño la mejor alternativa es la Multi-PWM, pero en cuanto a pérdidas de conmutación y rizado la mejor es el DAC. Teniendo en cuenta la mayor importancia de las pérdidas a la hora de obtener una mayor eficiencia en el prototipo, y del rizado para asegurar la calidad de la señal y evitar la necesidad de filtros externos, la alternativa seleccionada es el DAC.

### 3.4 Resultados de simulación

El objetivo de este apartado es mostrar cómo la topología escogida es capaz de representar formas de onda de distintas frecuencias y tensiones correctamente con un rizado razonablemente pequeño.

En las siguientes figuras se va a mostrar el funcionamiento del prototipo en simulación tratando de reproducir un seno de frecuencias desde 100 Hz hasta 100 kHz y amplitudes desde 10 V hasta 1 kV.

## Capítulo 3: Simulación y análisis

## Capítulo 3: Simulación y análisis

Figura 19: Simulación del funcionamiento del prototipo a distintos valores de tensión y frecuencia.

### Capítulo 3: Simulación y análisis

Se puede observar como el comportamiento más crítico se presenta con las tensiones de referencia de 10 V, donde el rizado es más visible tal y como se mostraba en la Figura 17 (entre el 7% y el 9% en función de la frecuencia).

Para el resto de tensiones el comportamiento es prácticamente ideal para todas las frecuencias presentando rizados más pequeños (0% - 1%), excepto para la frecuencia de 100 kHz. Para esta frecuencia el convertidor se ve más exigido ya que conmuta un menor número de veces por ciclo. Pese a ello, los rizados son algo menores del 4%, lo cual entra dentro de lo previsto.

En conclusión, el prototipo cumple con las especificaciones y es capaz de generar tensiones de +/- 1 kV en un amplio espectro de frecuencias presentando un rizado muy pequeño.

## 4 Diseño del convertidor multinivel propuesto

En este apartado se va a describir el convertidor, mostrando cada una de las partes que lo componen, desde su conexión a la red, hasta la salida del convertidor multinivel, y se irán mencionando los componentes que la conforman justificando su elección en base a las especificaciones mencionadas en el capítulo 3.

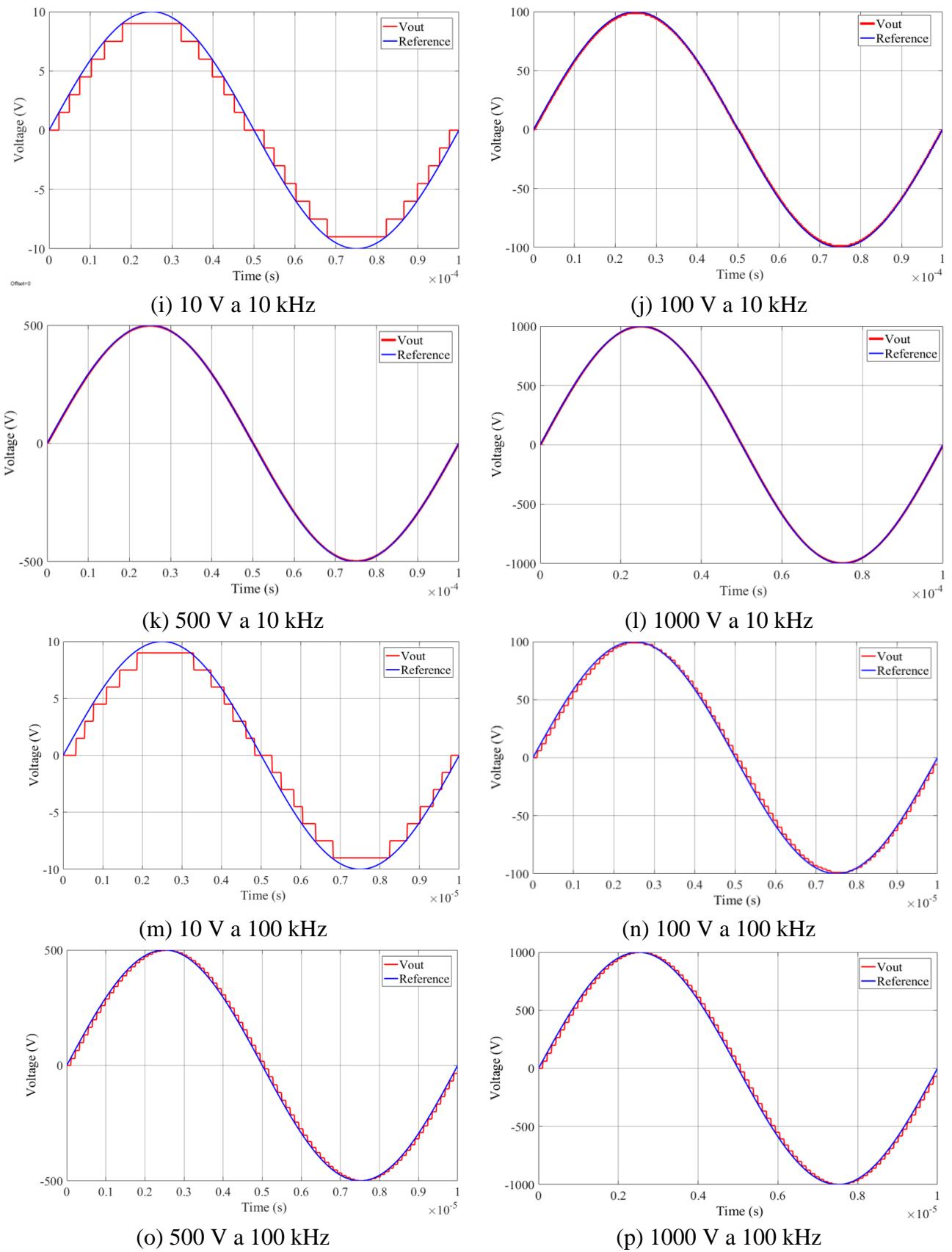

El esquema general de la topología es el mostrado en la Figura 20, donde, en primer lugar, se tiene un conversor AC/DC para conseguir una tensión continua y aislada para alimentar cada nivel del convertidor desde la red. En segundo lugar, se adecúa y se filtra la tensión DC por medio de un convertidor DC/DC. Por último, esta tensión es usada para alimentar cada uno de los módulos del convertidor multinivel (CHB).

Figura 20: Diagrama de bloques del convertidor multinivel.

El convertidor AC/DC utilizado es un convertidor comercial (UHP-500R) y se muestra en la Figura 21.

Figura 21: Convertidor AC/DC.

Las características técnicas del convertidor son las mostradas en la Figura 22.

|                            | UHP-500-4,2            | UHP-500-12    | UHP-500-24    | UHP-500-48    |

|----------------------------|------------------------|---------------|---------------|---------------|

| <b>Tensión de entrada</b>  | 90-264 AC / 127-370 DC |               |               |               |

| <b>Tensión de salida</b>   | 4,5 – 5,5 V            | 11,4 – 12,6 V | 22,8 – 25,2 V | 45,6 – 50,4 V |

| <b>Corriente de salida</b> | 80 A                   | 41,7 A        | 20,9 A        | 10,45 A       |

| <b>Aislamiento</b>         | 3,75 kVAC              |               |               |               |

Figura 22: Características técnicas AC/DC

Se cuenta con distintos convertidores para poder suministrar las tensiones necesarias para los módulos de menor tensión.

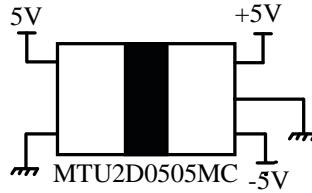

El objetivo del conversor DC/DC es adecuar al nivel de tensión deseado la salida del AC/DC y filtrarla para que la tensión obtenida no tenga prácticamente rizado. El DC/DC implementado ha sido el que se muestra en la Figura 23.

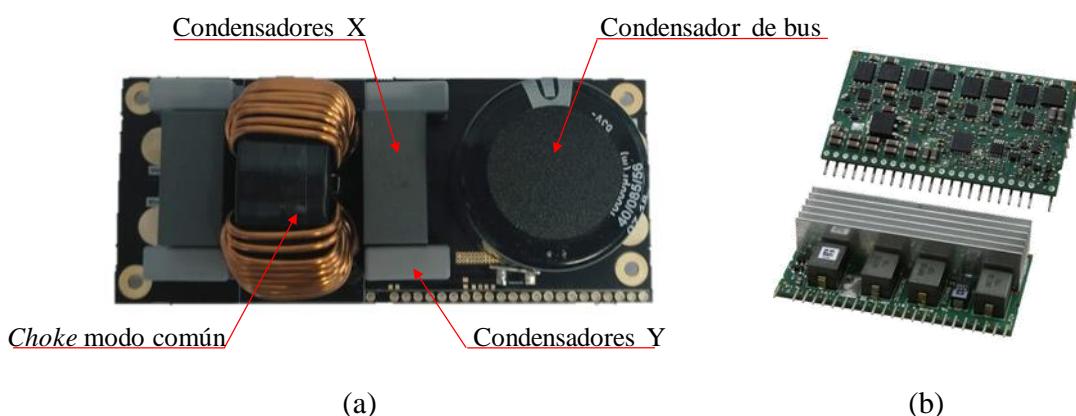

Figura 23: Etapa de filtrado y conversión DC/DC para alimentar los PM.

El DC/DC mostrado (D12S400) solo será necesario para obtener las tensiones de 1,5 V y de 3 V, ya que no se disponen de AC/DC que ofrezcan a la salida tensiones tan reducidas.

En cuanto al PM, lo más crítico es la elección de los semiconductores. Para poder representar formas de onda de hasta 100 kHz con una elevada calidad, es necesario que los dispositivos comuten a una frecuencia muy superior, en este caso, hasta 5 MHz. Conseguir estas frecuencias con los dispositivos convencionales de silicio difícil debido a las elevadas capacidades de entrada y salida que presentan los dispositivos. Como consecuencia, se ha optado por transistores de nitruro de galio (GaN), cuyas capacidades de entrada y salida son muy pequeñas, permitiendo operar en el rango de los MHz, manteniendo una elevada frecuencia. Además, tienen menos pérdidas, mayor temperatura de funcionamiento, resistencia en ambientes exigentes y altos voltajes de ruptura. Los transistores escogidos son los EPC2206, que se muestran en la Figura 24 y tienen una tensión de bloqueo de 80 V, una  $R_{DS(ON)}$  de 2,2 mΩ, una  $Q_G$  de 15 nC y una  $Q_{oss}$  de 72 nC. En este estudio se ha establecido su punto de operación en 50 V para asegurar unas condiciones de operación seguras.

Figura 24: Transistores GaN EPC2206 vistos desde bottom.

Además, con el fin de entregar los 50 A máximos que se exige en las especificaciones, se necesitará un puente completo (FB) con dos transistores en paralelo tanto en el lado alto como en el lado bajo sumando un total de 8 transistores por cada PM.

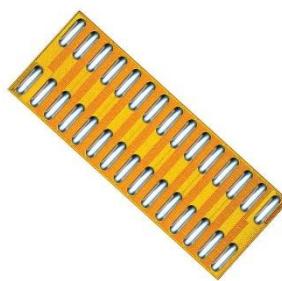

Los drivers utilizados para disparar estos dispositivos son los LMG1205YFXR de Texas Instruments (TI), que están enfocados principalmente a dispositivos GaN. Dentro del PM están también los condensadores de desacoplo y pines de salida para poder realizar el control y darle alimentación. En la Figura 25, se puede ver un PM.

Figura 25: Power Module (PM).

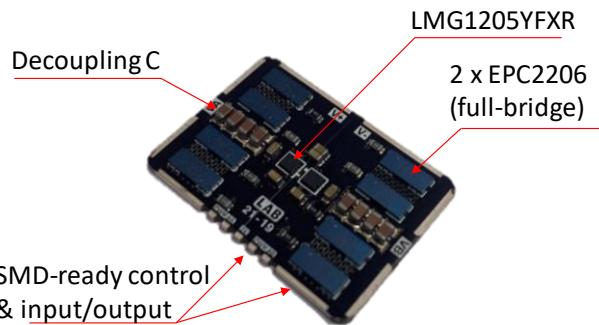

Para monitorizar cada uno de los módulos en corriente y tensión y protegerlo frente a posibles fallos, se va a disponer de un circuito de supervisión como el de la Figura 26.

Figura 26: Circuito de supervisión para cada PM.

En la figura,  $V_{DC+}$  y  $V_{DC-}$  representan la salida del convertidor DC/DC que adecúa y filtra la tensión DC que sale del convertidor AC/DC. Esta tensión es la que alimentará

el modulo en cuestión. Para medir esta tensión se ha utilizado un divisor resistivo que adecúa la tensión a un rango de 0-5 V y se aplica en la entrada del optoacoplador aislado que se muestra en la figura (AMC1311DWV). La salida del optoacoplador va a un ADC (ADCS7476) de 12 bits y 1 Msps, y de ahí a la FPGA de control (XA6SLX16).

Para medir la corriente que entra al módulo se procede de forma similar que con la tensión. Se dispondrá de un sensor de corriente (MCR1101-50-5) que se colocará en el nodo negativo del módulo. La salida del sensor irá a un ADC, igual que para la tensión, y posteriormente a la FPGA.

El MOSFET (IPT015N10N5) es el encargado de dar tensión a cada módulo y de deshabilitarlo en caso de detectarse algún fallo. Es una medida de seguridad para evitar conmutaciones erróneas o propagación de errores de un módulo a otro. Si se detecta que hay un fallo en alguno de los módulos, automáticamente se desactivarán todos los módulos por precaución.

El driver que dispara el MOSFET (UCC5350) está alimentado a 12 V y es controlado por la FPGA. Es importante mencionar que el driver, el optoacoplador, y el sensor de corriente han de estar aislados, ya que la tierra de cada módulo es diferente a la de los demás y deben estar correctamente referenciados.

Las señales que van de la FPGA al PM, representan las señales digitales para controlar los disparos de los dispositivos GaN. Como se puede observar, la alimentación general (la de la FPGA) es de 5 V, por tanto, para obtener los 5 V aislados (5 V\_ISO) que necesita el optoacoplador y los 12 V aislados (12 V\_ISO) que necesita el driver, se necesitarán los dos reguladores mostrados en la Figura 27.

## Capítulo 4: Diseño del convertidor multinivel propuesto

Figura 27: Reguladores de tensión para alimentar los dispositivos de supervisión. (a) Regulador aislado de 5V a 12V. (b) Regulador de 12V a 5V.

El primer regulador, es un convertidor elevador que parte de 5 V y entrega 12 V aislados y el segundo, transforma esos 12 V aislados en 5 V.

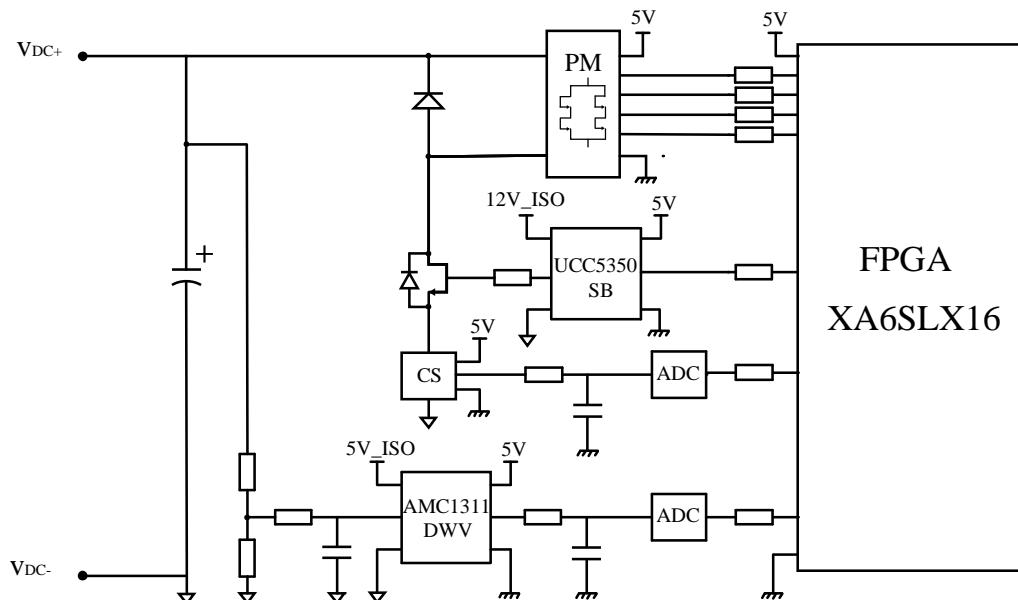

Finalmente, para monitorizar todo el convertidor, es necesario medir tensión y corriente a la salida del mismo, es decir entre el módulo 1 y el módulo  $n$ . En la Figura 28 se muestra el circuito de medida de ambas variables.

Figura 28: Circuito de sensado de corriente y tensión del convertidor multinivel.

En esta figura, se observa como la medida de tensión es similar a la de cada módulo por separado. Divisor resistivo, ADC y FPGA, pero en este caso la tensión que se va a medir es bipolar, puede variar desde -1 kV hasta 1 kV, por ello se ha escogido otro ADC capaz de leer a la entrada tensiones bipolares, es decir, el divisor resistivo reducirá la tensión  $V+$  a un rango de valores entre -2,5 V y 2,5 V. El ADC escogido es el LTC1420, que es un conversor paralelo. El conversor es de 12 bits y 10 Msps y ha de estar

alimentado a  $-5$  V y  $+5$  V, luego se necesitará otro DC-DC aislado que tenga como entrada  $+5$  V y como salida  $+/-5$  V aislados, como se ve en la Figura 29.

Figura 29: Regulador de tensión para alimentar el ADC.

Para el caso de la corriente, el sensor es el mismo que el utilizado para medir la corriente de cada módulo, y se sitúa en el módulo de menor tensión del convertidor. El ADC utilizado es también el LTC1420, pero en este caso no es necesario alimentarlo a  $-5$  V porque el sensor de corriente directamente genera una tensión positiva incluso cuando mide una corriente negativa, ya que la salida se encuentra montada sobre un offset de  $2,5$  V.

La comunicación entre el convertidor y el usuario se realizará por medio de fibra óptica. Para ello se necesitará un adaptador fibra óptica – USB.

## 5 Verificación experimental

En este apartado, en primer lugar, se mostrarán las PCBs desarrolladas para el prototipo explicando cada una de sus partes y, posteriormente, se mostrarán los resultados experimentales verificados en el laboratorio con el prototipo en funcionamiento.

### 5.1 Diseño hardware

Para explicar el diseño hardware, conviene recordar el diseño de la etapa explicado en el Capítulo 4, compuesto por un convertidor AC/DC (Figura 21), un convertidor DC/DC (Figura 23) y finalmente el PM (Figura 25). Además, cada PM cuenta con un circuito de supervisión (Figura 26) y el convertidor, a su vez, con un circuito de sensado de tensión y corriente (Figura 28).

En este apartado se van a mostrar las PCBs realizadas para poder implementar el prototipo, así como el montaje que se va a llevar a cabo.

El convertidor AC/DC se muestra en la Figura 21 junto son sus características técnicas en la Figura 22. A continuación, se encuentra el convertidor DC/DC que filtra y convierte esa tensión DC a la deseada para cada módulo, y el montaje es el mostrado en la Figura 30.

Figura 30: Convertidor DC/DC. (a) Filtro y condensador de bus. (b) DC/DC adicional para obtener los 3V y 1.5V.

De izquierda a derecha en la PCB se observa: en primer lugar, los conectores de entrada desde el convertidor AC/DC, a continuación, aparece el filtro de DC formado por los condensadores X e Y, y el *choke* modo común. Se ha incorporado en la misma PCB el condensador de bus de cada módulo representado en negro, y finalmente los conectores de salida del DC/DC que alimentarán el PM. El DC/DC extra que se tiene en la Figura 30 (b), es para poder conseguir las tensiones de 3 V y 1,5 V, ya que los AC/DC comerciales no son capaces de generar esas tensiones aisladas a partir de tensión de red. Este convertidor tiene un rango de tensión de entrada de 10,8 V a 13,2 V y genera una tensión de salida configurable de 0,8375 V a 5 V.

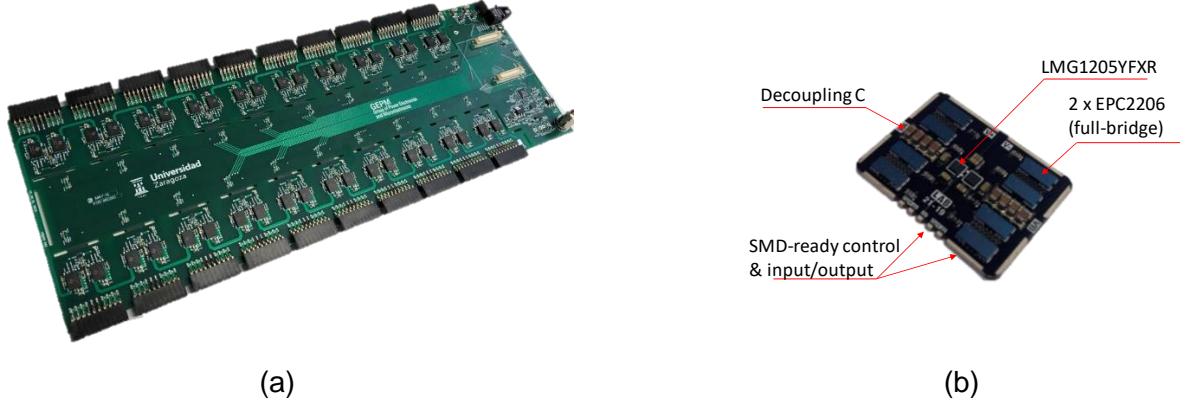

A continuación, en el esquema de la etapa se encuentra el PM, cuya apariencia es la mostrada en la Figura 25. Este PM va a ir montado en tarjetas (*carrier*) junto con otros circuitos integrados como se muestra en la Figura 31, donde habrá un PM en la cara top y otro en la cara bottom, de esta manera se consigue un prototipo más compacto, donde el cambio de dispositivos únicamente requiere retirar el *carrier* dañado e introducir otro nuevo.

Figura 31: carrier.

Los dos circuitos integrados que se pueden ver en la figura junto con el PM son, por un lado, el aislador (ISO7840FDWWR) alimentado a 3,3 V cuya función es aislar las señales de disparo de los dispositivos GaN, y, por otro lado, el DC/DC para alimentar el PM con 5 V aislados. Además, el *carrier* va montado en un conector que separa las señales digitales y de potencia para que no haya interferencia entre ellas. El conector es el mostrado en la Figura 32.

Figura 32: Conector PM con señales digitales y de potencia separadas.

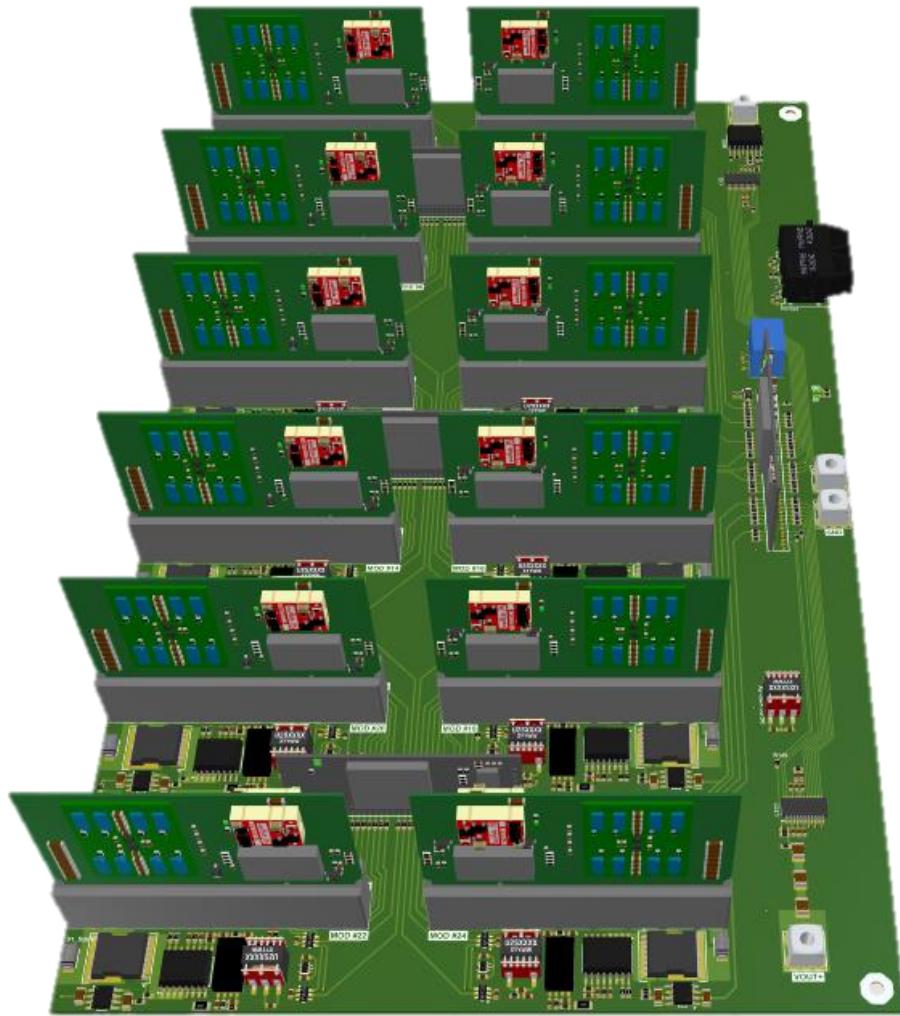

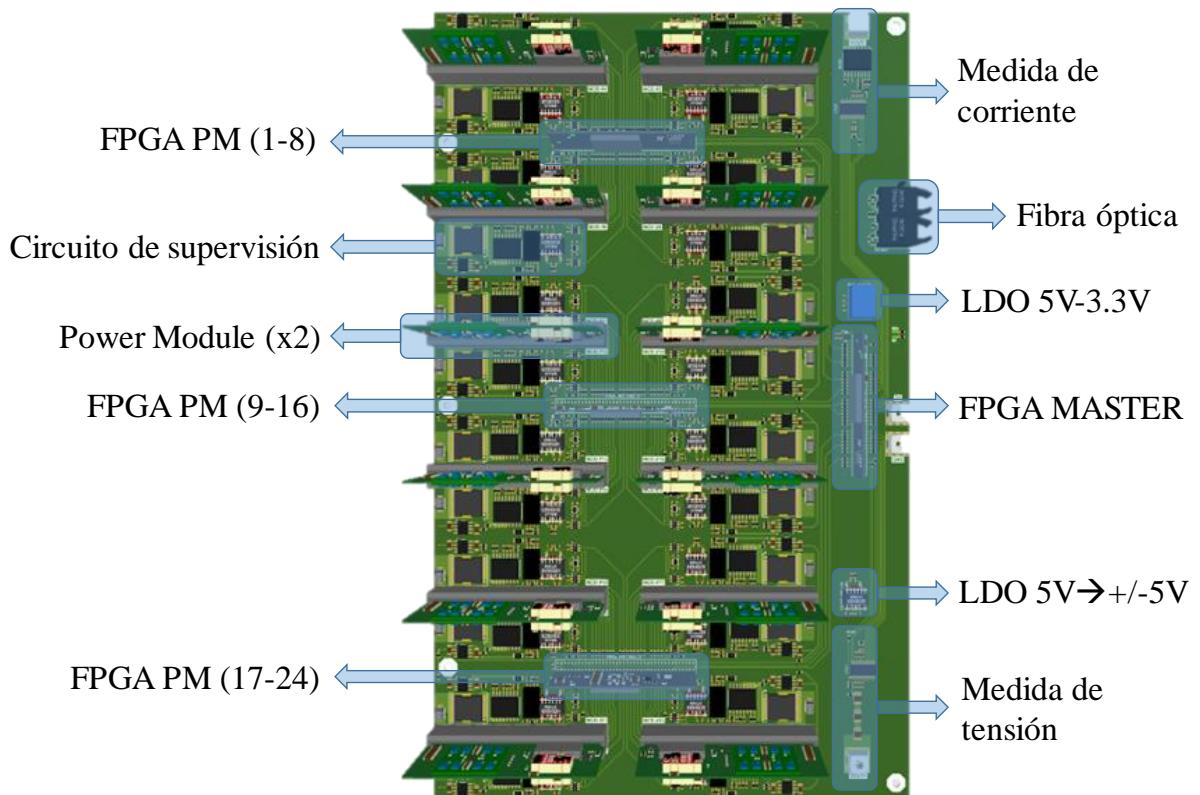

La PCB que integra todos los módulos, así como sus circuitos de supervisión y el resto de control y medidas del convertidor, es la mostrada en la Figura 33.

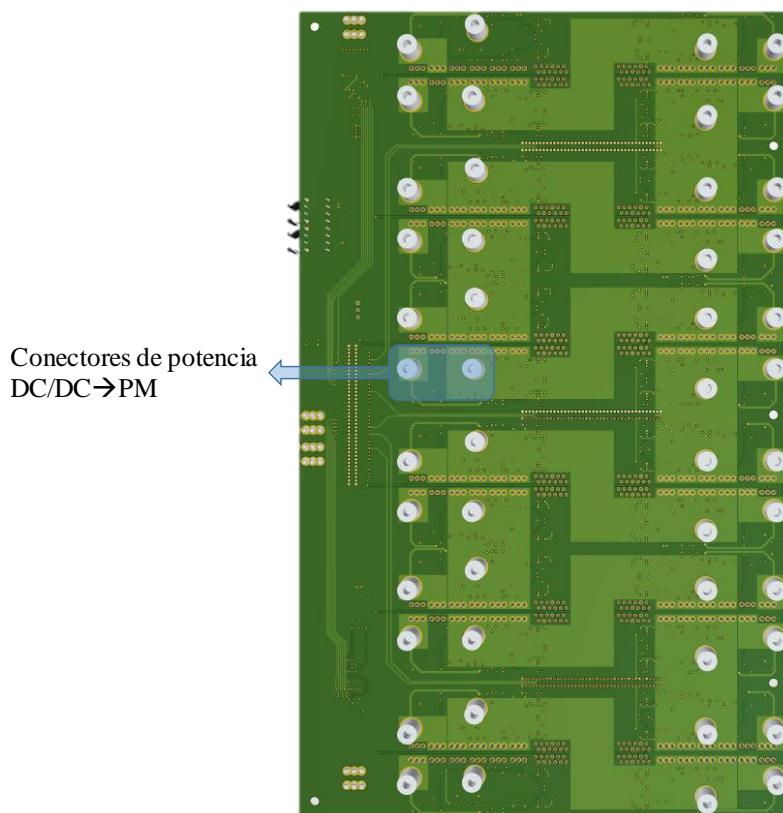

*Figura 33: PCB global de medidas y control de cada módulo y del convertidor.*

Para mostrar un poco más en detalle cada parte de la PCB y ver como se ha organizado el layout de la misma, se muestra la Figura 34.

Figura 34: Esquema PCB de control.

En primer lugar, cabe reseñar que, por simplicidad a la hora de realizar el ruteo, se han dividido los PM en 3 grupos de 8 (3 grupos de 4 *carrier*) a los que se denominará RAIL. Cada RAIL está controlado por una FPGA que genera las señales de control y monitoriza las tensiones y corrientes de cada PM. Como se ha mencionado anteriormente, cada *carrier* contiene dos PM, uno por la cara top y otro por la cara bottom, y al lado de cada uno de ellos se encuentra el circuito de supervisión de cada módulo.

Para poder controlar y monitorizar todos los módulos a la vez, las 3 FPGAs que controlan los 3 RAIL van conectadas a la FPGA MASTER que es con la que se comunica el usuario.

También se muestran las medidas de tensión (lado alto) y de corriente (lado bajo) del convertidor, así como los reguladores necesarios: 5 V/3.3 V para el aislador y 5 V/+-5 V para el ADC bipolar que mide la tensión del convertidor.

Los conectores que se ven en la parte derecha en el centro son los de alimentación de 5 V. Además, se han incluido 5 agujeros en el contorno de la PCB para poder anclarla en el soporte donde irá montada.

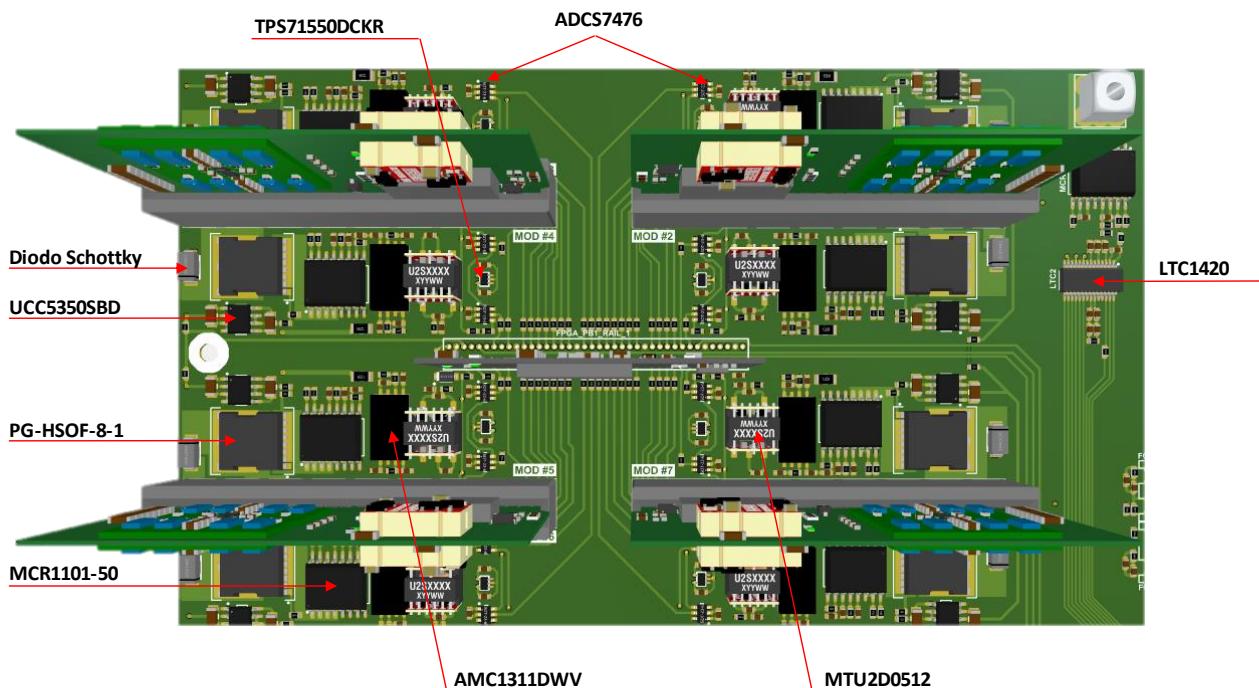

Para explicar mejor cómo está ruteada la PCB, en la Figura 35 se muestra el zoom de un RAIL donde se detallan cada uno de sus componentes principales.

Figura 35: Zoom a un RAIL.

El MOSFET que controla la alimentación del PM es el PG-HSOF-8-1, tiene una  $R_{DS(ON)}$  de 1.5 mΩ y una tensión de ruptura de 100 V. A su lado, también se puede observar el diodo Schottky ultrarrápido que controla la caída de tensión en caso de que el MOSFET deje de conducir. Muy cerca del MOSFET se encuentra el driver que lo controla, un UCC5350SBD alimentado a 12 V aislados, que se obtienen del DC/DC MTU2D0512 a partir de los 5 V globales.

El optoacoplador que mide la tensión de cada PM, es el AMC1311DWV que va alimentado a 5 V aislados obtenidos del regulador lineal TPS71550DCKR que transforma de 12 V aislados a 5 V aislados. El sensor de corriente es el MCR1101-50, alimentado

directamente a los 5 V globales y capaz de medir los 50 A máximos que pueden pasar por cada módulo. Por último, en los circuitos de supervisión, se encuentran los ADCs de tensión y corriente que son los ADCS7476 de 12 bit y 1 Msps.

Se puede observar también como todas las señales de disparo de cada PM son llevadas desde la FPGA que controla el RAIL, y las medidas de tensión y corriente son llevadas a la misma desde los ADCs. Para comunicarse con la FPGA MASTER, se sacan 11 señales de cada FPGA que controla cada RAIL.

En la parte derecha de la imagen, también se puede ver el ADC que mide la corriente por el convertidor (no perteneciente al RAIL, sino globalmente al convertidor), el cual es un LTC1420 de 12 bits y 10 Msps.

En cuanto a la parte bottom de la PCB, es la mostrada en la Figura 36.

Figura 36: PCB de control, cara bottom.

Los conectores representan la conexión entre los DC/DC y los PM. El objetivo es que la PCB de control esté montada sobre los convertidores AC/DC y DC/DC, y se conecte con este último a través de los conectores situados en bottom para alimentar cada PM.

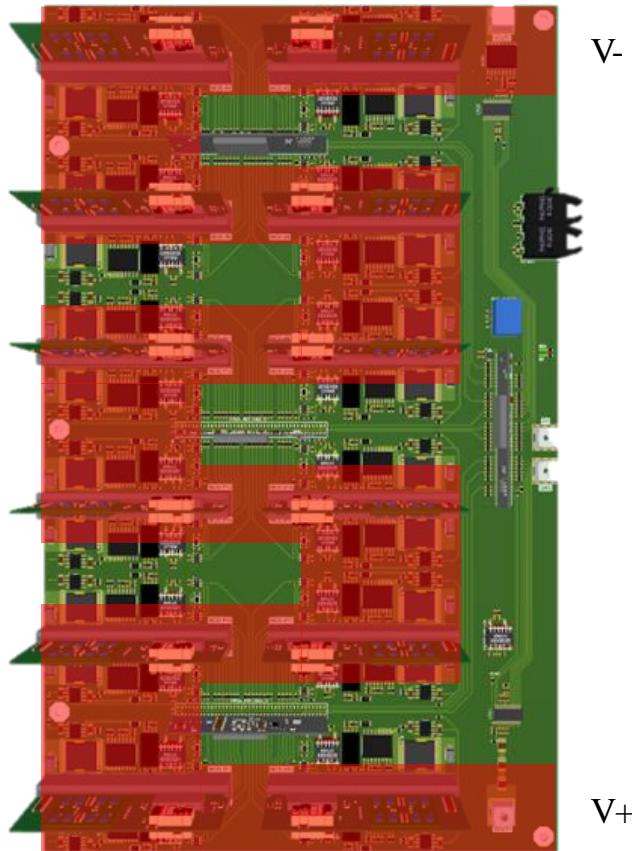

Por último, para mostrar de forma general el flujo de potencia y cómo están conectados los módulos entre ellos, se muestra la Figura 37.

Figura 37: Flujo de potencia del convertidor.

Como se explicaba en apartados anteriores, la topología CHB está basado en la conexión en serie un número determinado de inversores (lo que se ha denominado PM) para poder llegar a un determinado valor de tensión. En la figura se muestra cómo están conectados los PM que forman el convertidor, así como la salida de éste entre  $V+$  y  $V-$ .

Se observa cómo se ha dejado un espacio disponible para que las señales de las FPGA que controlan cada RAIL salgan limpias sin interferencias con las conexiones de potencia y garantizar de esa manera una mejor calidad de la señal.

## 5.2 Resultados experimentales

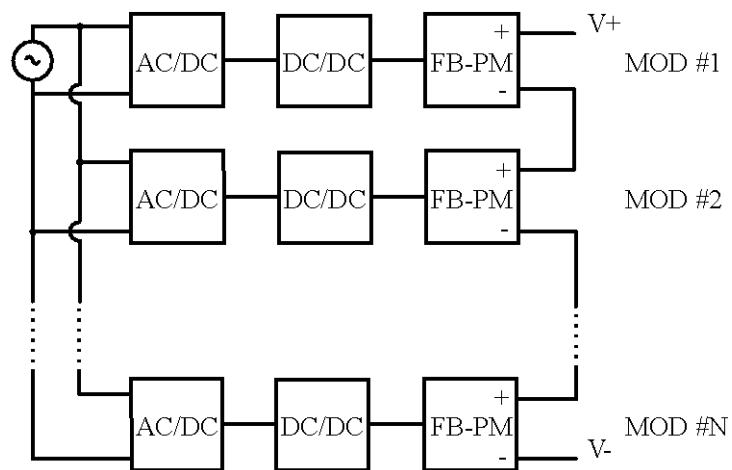

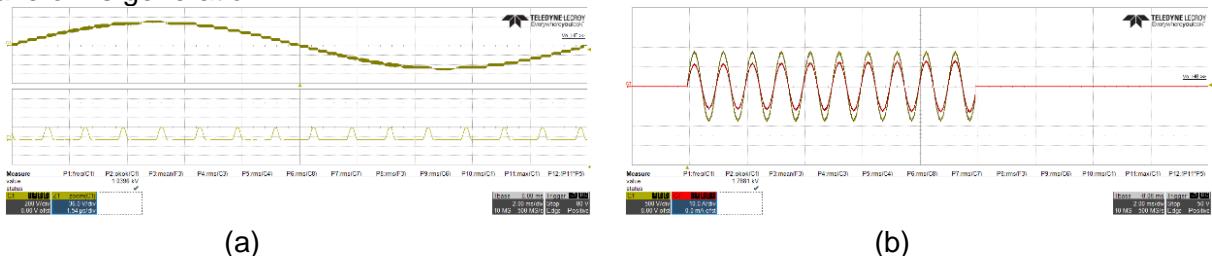

En este apartado se muestra la PCB de control con los todos los carrier montados, así como distintas capturas de osciloscopio obtenidas con el prototipo real en funcionamiento, donde se ha tratado de reproducir las formas de onda que se generaron en simulación.

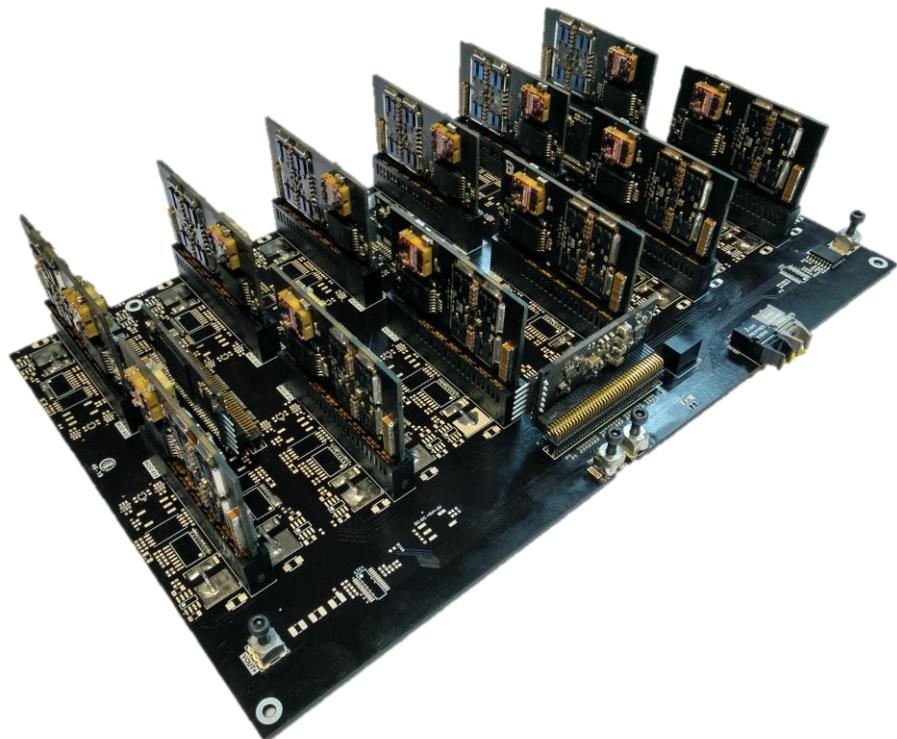

EL prototipo experimental montado es el que se muestra en la Figura 38.

*Figura 38: Montaje del prototipo experimental*

Las distintas formas de onda experimentales de tensión a la salida del convertidor para distintas frecuencias son las siguientes:

## Capítulo 5: Verificación experimental

Figura 39: Forma de onda de tensión de salida experimental. 10 V a 100 Hz (5 V/div. 1 ms/div).

Figura 40: Forma de onda de tensión de salida experimental. 100V a 100 Hz (50 V/div. 1 ms/div).

Figura 41: Forma de onda de tensión de salida experimental. 200 V a 100 Hz (50 V/div. 1 ms/div).

## Capítulo 5: Verificación experimental

Figura 42: Forma de onda de tensión de salida experimental. 10 V a 1 kHz (5 V/div. 100  $\mu$ s/div).

Figura 43: Forma de onda de tensión de salida experimental. 100 V a 1 kHz (50 V/div. 100  $\mu$ s/div).

Figura 44: Forma de onda de tensión de salida experimental. 200 V a 1 kHz. (50 V/div. 100  $\mu$ s/div).

## Capítulo 5: Verificación experimental

Figura 45: Forma de onda de tensión de salida experimental. 10 V a 10 kHz (5 V/div. 10  $\mu$ s/div).

Figura 46: Forma de onda de tensión de salida experimental. 100 V a 10 kHz (50 V/div. 10  $\mu$ s/div).

Figura 47: Forma de onda de tensión de salida experimental. 200 V a 10 kHz (50 V/div. 10  $\mu$ s/div).

## Capítulo 5: Verificación experimental

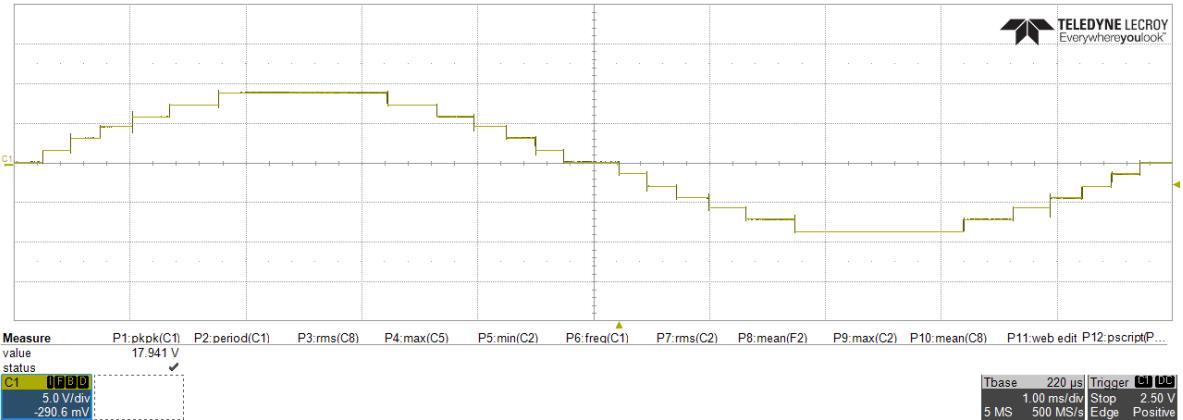

Figura 48: Forma de onda de tensión de salida experimental. 10 V a 100 kHz (5 V/div. 1 μs/div).

Figura 49: Forma de onda de tensión de salida experimental. 100 V a 100 kHz (50 V/div. 1 μs/div).

Figura 50: Forma de onda de tensión de salida experimental 200 V a 100 kHz. (50 V/div. 1 μs/div).

Se observa como el prototipo es capaz de sintetizar correctamente senos de distintas amplitudes a distintas frecuencias dentro de su rango de trabajo. El mayor

rizado se obtiene para bajas tensiones (10 V), pero los resultados son igualmente satisfactorios para todas las frecuencias y tensiones generadas.

En este punto, debe destacarse la complejidad de obtener este tipo de ondas en el rango de frecuencias y tensión propuestos, no existiendo un equipo comercial que permita realizar esta tarea con las mismas prestaciones propuestas.

## 6 Conclusiones y líneas futuras

En este último capítulo se recogen las principales conclusiones extraídas en el desarrollo de este trabajo y se proponen varias líneas de trabajo futuras para profundizar en algunos aspectos interesantes detectados en la realización del mismo.

### 6.1 Conclusiones

En este trabajo, se ha desarrollado un convertidor multinivel diferente y novedoso con respecto a lo que actualmente se encuentra en el mercado. La principal diferencia radica en el control y la arquitectura implementada. Hasta la fecha, los convertidores multinivel eran fundamentalmente controlados mediante un control PWM, lo que suponía un gran número de conmutaciones por parte de los semiconductores para poder representar la forma de tensión requerida, y se traducía en un aumento de las pérdidas y una reducción de la eficiencia.

Además, con el control que se ha implementado, no solo se obtienen menos pérdidas y una mayor eficiencia, sino que también se reduce considerablemente el rizado sobre todo a la hora de reproducir formas de onda a alta frecuencia. Esta reducción del rizado hace que la señal obtenida por el convertidor tenga una mejor calidad y se reduzca la necesidad de implementar complejas etapas de filtrado externas.

Otro factor importante que se ha mejorado en este prototipo es el de la robustez. Se han incluido circuitos de supervisión para cada uno de los módulos con el objetivo de dotar de una mayor robustez y seguridad al diseño, de tal forma que, si falla uno de los módulos, este fallo pueda detectarse lo suficientemente rápido como para mantener la integridad del convertidor en todo momento.

Finalmente, se debe destacar que parte de los resultados de este trabajo han sido enviados al congreso internacional PCIM, que se celebrará en Nüremberg en 2020 [19].

## 6.2 Líneas futuras

En cuanto a las líneas de trabajo futuras que abre este trabajo, se han extraído principalmente 3:

- Por un lado, compactar el diseño. Es un diseño robusto y seguro, pero también es muy voluminoso. Si se dedicase un mayor esfuerzo a la optimización del convertidor, podría reducirse considerablemente su tamaño.

- Por otro lado, ahondar en el control. El convertidor está controlado por 4 FPGAs, una por cada RAIL y la FPGA MASTER. Quizá esto podría reducirse y hacer más sencilla y compacta la programación del prototipo con una sola FPGA.

- Finalmente, aumentar el espectro de tensiones y frecuencias a representar cumpliendo siempre un compromiso con la seguridad, la modularidad y la compactación del convertidor.

## 7 Bibliografía

- [1] H. Sarnago, J. M. Burdío, T. García-Sánchez, L. Mir, and O. Lucia, "A Versatile Large-Signal High-Frequency Arbitrary Waveform Generator Using GaN Devices," in *2019 IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2019, pp. 458-462.

- [2] H. Sarnago, L. Ó, A. Naval, J. M. Burdío, Q. Castellví, and A. Ivorra, "A Versatile Multilevel Converter Platform for Cancer Treatment Using Irreversible Electroporation," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, pp. 236-242, 2016.

- [3] J. Ó, L. Ó, L. A. Barragán, D. Navarro, J. I. Artigas, and I. Urriza, "FPGA-Based Test-Bench for Resonant Inverter Load Characterization," *IEEE Transactions on Industrial Informatics*, vol. 9, pp. 1645-1654, 2013.

- [4] K. Hongjoon, A. B. Kozyrev, H. Sung-un, and D. W. v. d. Weide, "Fourier synthesizer using left-handed transmission lines," in *IEEE MTT-S International Microwave Symposium Digest, 2005.*, 2005, p. 4 pp.

- [5] S. Debnath, J. Qin, B. Bahrani, M. Saeedifard, and P. Barbosa, "Operation, Control, and Applications of the Modular Multilevel Converter: A Review," *IEEE Transactions on Power Electronics*, vol. 30, pp. 37-53, 2015.

- [6] L. Jih-Sheng and P. Fang Zheng, "Multilevel converters-a new breed of power converters," *IEEE Transactions on Industry Applications*, vol. 32, pp. 509-517, 1996.

- [7] J. Rodriguez, L. Jih-Sheng, and P. Fang Zheng, "Multilevel inverters: a survey of topologies, controls, and applications," *IEEE Transactions on Industrial Electronics*, vol. 49, pp. 724-738, 2002.

- [8] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B. Wu, *et al.*, "Recent Advances and Industrial Applications of Multilevel Converters," *IEEE Transactions on Industrial Electronics*, vol. 57, pp. 2553-2580, 2010.

- [9] M. Glinka and R. Marquardt, "A new AC/AC multilevel converter family," *IEEE Transactions on Industrial Electronics*, vol. 52, pp. 662-669, 2005.

- [10] J. E. Huber and J. W. Kolar, "Optimum Number of Cascaded Cells for High-Power Medium-Voltage AC-DC Converters," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 5, pp. 213-232, 2017.

- [11] C. Han, A. Q. Huang, Y. Liu, and B. Chen, "A Generalized Control Strategy of Per-Phase DC Voltage Balancing for Cascaded Multilevel Converter-based STATCOM," in *2007 IEEE Power Electronics Specialists Conference*, 2007, pp. 1746-1752.

- [12] K. Jafri, B. C. Chen, Y. Song Zhong, and C. Yaojun, "Static and dynamic characteristics of a novel STATCOM based on modular multilevel converter," in *IET International Conference on Information Science and Control Engineering 2012 (ICISCE 2012)*, 2012, pp. 1-5.

- [13] H. A. Pereira, M. R. Haddioui, L. O. M. d. Oliveira, L. Mathe, M. Bongiorno, and R. Teodorescu, "Circulating current suppression strategies for D-STATCOM based on modular multilevel converters," in *2015 IEEE 13th Brazilian Power Electronics Conference and 1st Southern Power Electronics Conference (COBEP/SPEC)*, 2015, pp. 1-6.

- [14] M. Gleißner and M. Bakran, "Comparison of multiphase versus multilevel DC/DC-converters for automotive power," in *2013 15th European Conference on Power Electronics and Applications (EPE)*, 2013, pp. 1-10.

## Capítulo 7: Bibliografía

- [15] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, and M. A. M. Prats, "The age of multilevel converters arrives," *IEEE Industrial Electronics Magazine*, vol. 2, pp. 28-39, 2008.

- [16] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, "A Survey on Cascaded Multilevel Inverters," *IEEE Transactions on Industrial Electronics*, vol. 57, pp. 2197-2206, 2010.

- [17] S. Rohner, S. Bernet, M. Hiller, and R. Sommer, "Modulation, Losses, and Semiconductor Requirements of Modular Multilevel Converters," *IEEE Transactions on Industrial Electronics*, vol. 57, pp. 2633-2642, 2010.

- [18] M. Hagiwara and H. Akagi, "Control and Experiment of Pulsewidth-Modulated Modular Multilevel Converters," *IEEE Transactions on Power Electronics*, vol. 24, pp. 1737-1746, 2009.

- [19] I. Álvarez-Gariburo, H. Sarnago, J. M. Burdío, and O. Lucía, "Enviado a Congreso Internacional PCIM," in Enviado a Congreso Internacional PCIM 2020, pp. 1-10.

# **Anexos**

# DESIGN AND OPTIMIZATION OF A GAN-BASED HIGH-VOLTAGE WAVEFORM GENERATOR FOR INDUSTRIAL AND BIOMEDICAL APPLICATIONS

Ignacio Álvarez-Gariburo<sup>1</sup>, Héctor Sarnago<sup>1</sup>, José M. Burdío<sup>2</sup> and Oscar Lucía<sup>1</sup>

<sup>1</sup> Electronics Engineering and Communications Department. Universidad de Zaragoza, I3A, Spain.

Corresponding author: Óscar Lucía (olucia@unizar.es)

F03 AC-DC and DC-AC Converters

Poster presentation

## Abstract

Arbitrary waveform generators are required for multiple load characterization and excitation in a wide variety of industrial and biomedical applications. In the past, these generators have been typically limited in voltage/current/frequency due mainly to limitations of the power devices. However, advances in semiconductor technology have enabled the design of high-performance versatile waveform generators with improved operational ranges. This paper deals with the design, optimization and experimental validation of a 2000-V versatile large-signal high-frequency arbitrary waveform generator taking advantage of GaN devices. Several alternatives are studied, and the proposed system has been designed and implemented, proving the feasibility of this proposal.

## Introduction

Arbitrary waveform generators are required for a wide range of industrial and biomedical applications where precise waveforms are required to be applied to either characterize or stimulate loads [1]. Fig. 1 shows several examples including high-voltage application in parallel electrodes for electroporation in liver tissue [2] (a) or characterization of induction heating loads [3] (b).

In the past, several attempts have been made providing high-frequency signal generators but with limited voltage/current amplitudes [4]. In [5], an accurate Josephson arbitrary generator is proposed, but limited to 1 V and 1 kHz. One of the few large-signal generators is detailed in [6-8]. However, it is limited to sinusoidal waveforms and requires adapting the resonant tank, including frequency resolution and dynamic performance limitations. In [1], a GaN-based multi-level converter was implemented, but with limited total harmonic distortion performance and functionality. The aim of this paper is to optimize and provide a versatile large-signal high-frequency arbitrary waveform generator taking advantage of the new GaN devices.

## Proposed power converter

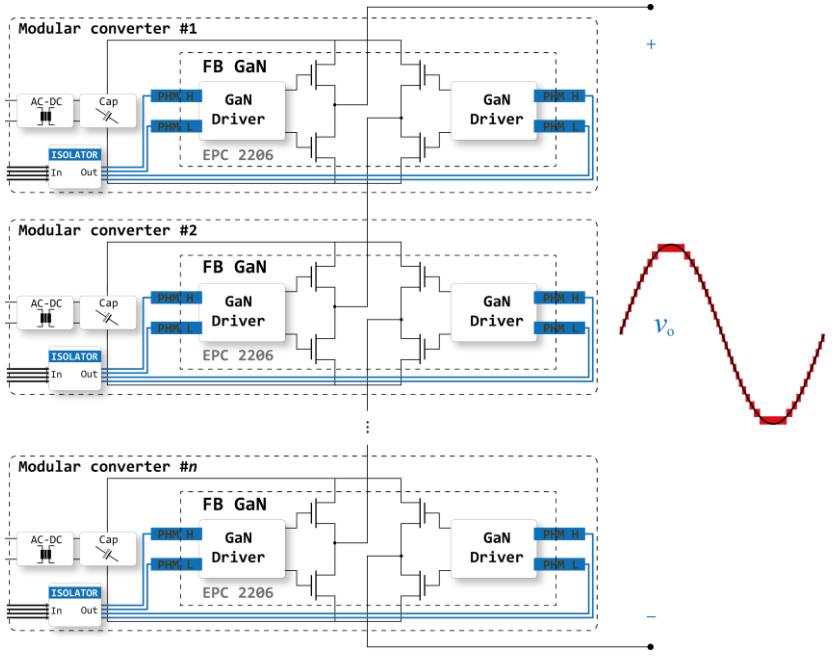

The proposed converter (Fig. 2) is based on a multi-level structure composed of  $n$  levels, each one composed of a full-bridge providing  $\pm V_{bus}$  voltage stored at an ultracapacitor. Consequently, the maximum output voltage is  $v_o = \pm nV_{bus}$  and arbitrary waveforms can be generated with an amplitude resolution  $V_{bus}$ . This topology reduces the voltage ratings at each level, enabling the use of high-performance GaN devices.

Fig. 1. Applications of the proposed versatile generator: Electroporation of liver tissue (a) and characterization of induction heating loads (b).

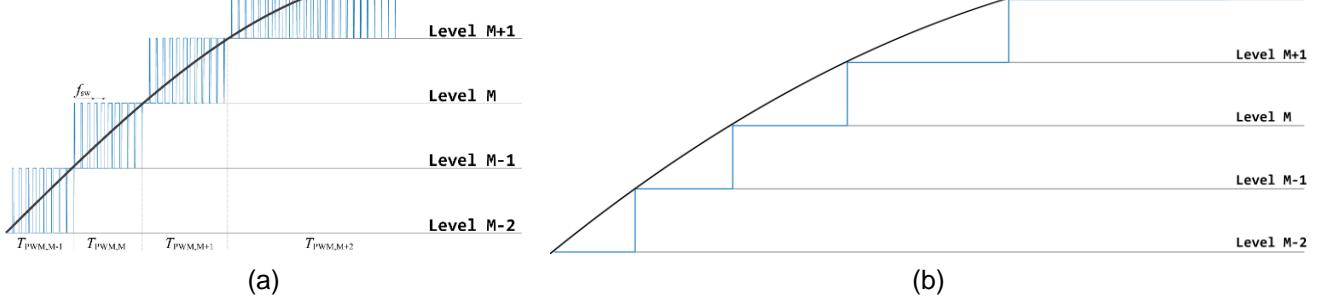

In order to obtain the desired arbitrary waveforms, each level is activated sequentially to obtain the desired output voltage. To achieve a good temporal/frequency resolution, WBG devices will be used in order to increase the switching frequency, providing a faster response. Several modulation strategies will be studied and compared (Fig. 3): Fixed-voltage PWM modulation and variable-voltage ladder modulation. The former enables to increase the resolution by applying high-frequency PWM [9, 10] taking advantage of WBG devices, whereas the latter uses a variable bus voltage modules to achieve the same low harmonic distortion. The final version of the paper will contain a detailed analysis of the proposed modulation which is summarized as follows.

Fig. 2. Proposed GaN-based multi-level topology.

Fig. 3. Proposed modulation strategies: (a) fixed-voltage PWM and (b) variable-voltage ladder modulation.

In order to select the optimum implementation and modulation strategy, a detailed analysis considering the number of levels, switching losses, total harmonic distortion and complexity has been performed. Variable-voltage ladder modulation is compared to fixed-voltage modulation with two alternative implementations: fixed modulation at each level and alternative modulation between levels to homogenize power loss.

| Control                       | Level # | Switching loss | Output THD | Complexity |

|-------------------------------|---------|----------------|------------|------------|

| Fixed-Voltage PWM             | ✓       | ✗              | ✗          | ✓          |

| Fixed-Voltage Alternative PWM | ✓       | ✗              | ✗          | ✗          |

| Variable-Voltage Ladder       | ✗       | ✓              | ✓          | ✗          |

Fig. 4. Comparative analysis.

Fig. 4 shows a summary of the comparative modulation analysis. Despite requiring a higher number of switching modules to implement the same output voltage, variable-voltage ladder modulation achieves better performance considering switching losses and output voltage THD. For this reason, and despite the control complexity, this modulation will be selected for implementation. The following table summarizes the main compared aspects.

### Implementation and experimental results

The proposed versatile large-signal arbitrary waveform generator has been implemented to provide up to 2 kV output power. A fixed-voltage version using 20 levels with maximum  $V_{bus} = 60$ . And featuring LM5200 GaN devices from Texas Instruments has been implemented (Fig. 5(a)). Besides, a variable-voltage version featuring 2 paralleled EPC2206 devices with LMG1205YFXR driver has been implemented, providing an improved 50-A RMS output current. This implementation has been made using a modular approach, where each full-bridge has been implemented as an SMD component.

Fig. 5. Experimental prototypes: (a) prototype using fixed voltage modulation and (b) improved modular implementation for variable-voltage ladder modulation.

Fig. 6 shows a summary of representative experimental results, including generation of 50 Hz sinusoidal waveform with PWM detail (a), 100 kHz sinusoidal waveform, 1 kHz sinusoidal waveform with capacitive load, and a train-pulse typical of electroporation applications. These results prove the correct operation of the proposed converter and its feasibility for large-signal high-frequency arbitrary waveforms generation.

Fig. 6. Main preliminary experimental results using fixed-voltage PWM modulation: (a) 50 Hz sinusoidal waveform with PWM detail and (b) burst mode operation.

### Conclusions

This paper has proposed a versatile large-signal high-frequency arbitrary waveform generator following a multi-level structure and taking advantage of GaN devices. Several modulation strategies have been analysed, selecting variable voltage ladder modulation to optimize switching losses and output voltage THD. The proposed converter has been implemented and designed, achieving both high voltage and high temporal/amplitude resolution, opening the window to future industrial and biomedical applications.

## References

- [1] H. Sarnago, J. M. Burdío, T. García-Sánchez, L. M. Mir, and O. Lucía, "A Versatile Large-Signal High-Frequency Arbitrary Waveform Generator Using GaN Devices," in *IEEE Applied Power Electronics Conference and Exposition*, 2019, pp. 458-462.

- [2] H. Sarnago, O. Lucía, A. Naval, J. M. Burdío, Q. Castellví, and A. Ivorra, "A versatile multi-level converter platform for cancer treatment using irreversible electroporation," *IEEE Journal on Emerging and Selected Topics in Power Electronics*, vol. 4, no. 1, pp. 236-242, 2016.

- [3] O. Jiménez, O. Lucía, L. A. Barragán, D. Navarro, J. I. Artigas, and I. Urriza, "FPGA-based test bench for resonant inverter load characterization," *IEEE Transactions on Industrial Informatics*, vol. 9, no. 3, pp. 1645-1654, August 2013.

- [4] K. Hongjoon, A. B. Kozyrev, H. Sung-un, and D. W. v. d. Weide, "Fourier synthesizer using left-handed transmission lines," in *IEEE MTT-S International Microwave Symposium Digest*, 2005., 2005, p. 4 pp.