# **A**NEXOS

ANEXO I. DATASHEET ATMEGA2560

#### **Features**

- High Performance, Low Power AVR® 8-Bit Microcontroller

- Advanced RISC Architecture

- 135 Powerful Instructions Most Single Clock Cycle Execution

- 32 x 8 General Purpose Working Registers

- Fully Static Operation

- Up to 16 MIPS Throughput at 16 MHz

- On-Chip 2-cycle Multiplier

- Non-volatile Program and Data Memories

- 64K/128K/256K Bytes of In-System Self-Programmable Flash Endurance: 10,000 Write/Erase Cycles

- Optional Boot Code Section with Independent Lock Bits In-System Programming by On-chip Boot Program

True Read-While-Write Operation

- 4K Bytes EEPROM

Endurance: 100,000 Write/Erase Cycles

- 8K Bytes Internal SRAM

- Up to 64K Bytes Optional External Memory Space

- Programming Lock for Software Security

- JTAG (IEEE std. 1149.1 compliant) Interface

- Boundary-scan Capabilities According to the JTAG Standard

- Extensive On-chip Debug Support

- Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

- Peripheral Features

- Two 8-bit Timer/Counters with Separate Prescaler and Compare Mode

- Four 16-bit Timer/Counter with Separate Prescaler, Compare- and Capture Mode

- Real Time Counter with Separate Oscillator

- Four 8-bit PWM Channels

- Six/Twelve PWM Channels with Programmable Resolution from 2 to 16 Bits (ATmega1281/2561, ATmega640/1280/2560)

- Output Compare Modulator

- 8/16-channel, 10-bit ADC

- Two/Four Programmable Serial USART (ATmega1281/2561,ATmega640/1280/2560)

- Master/Slave SPI Serial Interface

- Byte Oriented 2-wire Serial Interface

- Programmable Watchdog Timer with Separate On-chip Oscillator

- On-chip Analog Comparator

- Interrupt and Wake-up on Pin Change

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated Oscillator

- External and Internal Interrupt Sources

- Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby, and Extended Standby

- I/O and Packages

- 51/86 Programmable I/O Lines (ATmega1281/2561, ATmega640/1280/2560)

- 64-lead (ATmega1281/2561)

- 100-lead (ATmega640/1280/2560)

- 100-lead TQFP (64-lead TQFP Option)

- Temperature Range:

- -40°C to 85°C Industrial

- Speed Grade:

- ATmega1281/2561V/ATmega640/1280/2560V:

- 0 4 MHz @ 1.8 5.5V, 0 8 MHz @ 2.7 5.5V

- ATmega640/1280/1281/2560/2561:

- 0 8 MHz @ 2.7 5.5V, 0 16 MHz @ 4.5 5.5V

8-bit **AVR**® Microcontroller with 256K Bytes In-System Programmable Flash

ATmega1281/25 61/V ATmega640/128 0/2560/V

Advance Information

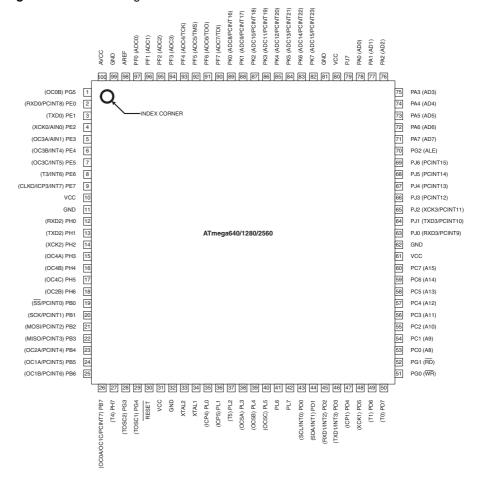

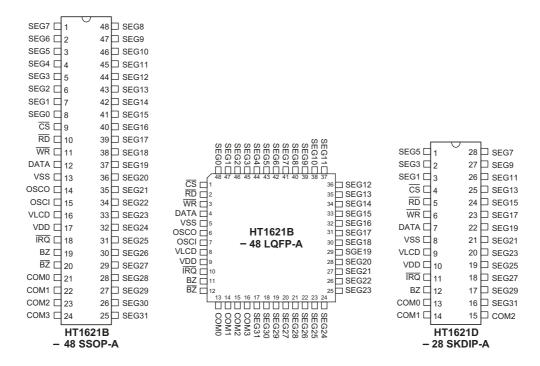

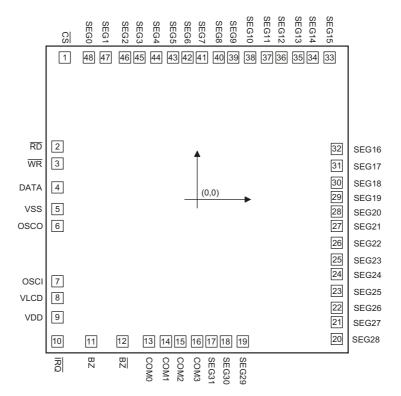

## **Pin Configurations**

Figure 1. Pinout ATmega640/1280/2560

PF6 (ADC6/TD0) PF4 (ADC4/TCK) PF1 (ADC1) PF2 (ADC2) PF3 (ADC3) PA1 (AD1) PA2 (AD2)

69

63

64

65

67

68

69

61

62

63

64

65

67

68

69

69

60

60

61

62

63

64

65

64

65

66

67

68

69

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

</tr 48 PA3 (AD3) (OC0B) PG5 (RXD0/PCINT8/PDI) PE0 2 47 PA4 (AD4) INDEX CORNER 3 46 (TXD0/PDO) PE1 PA5 (AD5) 4 45 (XCK0/AIN0) PE2 PA6 (AD6) 5 (OC3A/AIN1) PE3 44 PA7 (AD7) (OC3B/INT4) PE4 6 43 PG2 (ALE) (OC3C/INT5) PE5 42 PC7 (A15) (T3/INT6) PE6 8 41 PC6 (A14) ATmega1281/2561 (ICP3/CLKO/INT7) PE7 9 40 PC5 (A13) (SS/PCINT0) PB0 10 39 PC4 (A12) (SCK/PCINT1) PB1 11 PC3 (A11) 12 (MOSI/PCINT2) PB2 PC2 (A10) 13 (MISO/PCINT3) PB3 PC1 (A9) 36 (OC2A/PCINT4) PB4 14 35 PC0 (A8) 15 (OC1A/PCINT5) PB5 34 PG1 (RD) (OC1B/PCINT6) PB6 33 PG0 (WR) (ICP1) PD4 (OC0A/OC1C/PCINT7) PB7 XTAL1 (SCL/INT0) PD0 (SDA/INT1) PD1 (RXD1/INT2) PD2 (TXD1/INT3) PD3 (T0) PD7 (TOSC2) PG3

Figure 2. Pinout ATmega1281/2561

Note: The large center pad underneath the QFN/MLF package is made of metal and internally connected to GND. It should be soldered or glued to the board to ensure good mechanical stability. If the center pad is left unconnected, the package might loosen from the board.

## Disclaimer

Typical values contained in this datasheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min and Max values will be available after the device is characterized.

## Overview

The ATmega640/1280/1281/2560/2561 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega640/1280/1281/2560/2561 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

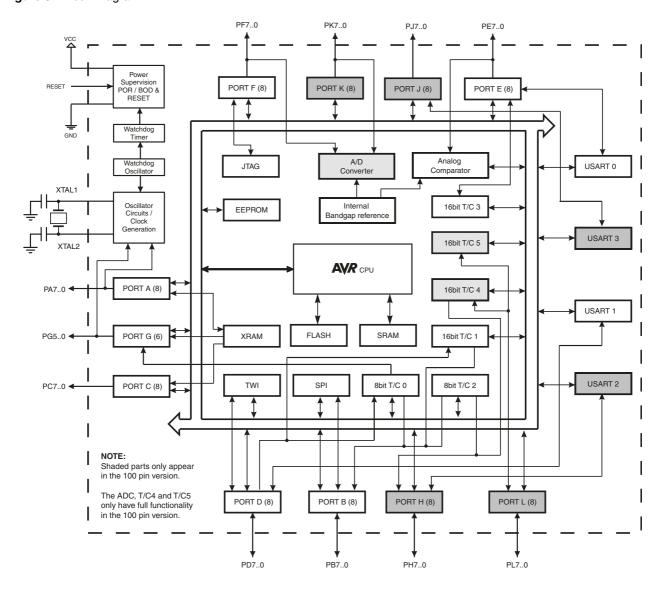

## **Block Diagram**

4

Figure 3. Block Diagram

## ATmega640/1280/1281/2560/2561

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega640/1280/1281/2560/2561 provides the following features: 64K/128K/256K bytes of In-System Programmable Flash with Read-While-Write capabilities, 4K bytes EEPROM, 8K bytes SRAM, 54/86 general purpose I/O lines, 32 general purpose working registers, Real Time Counter (RTC), six flexible Timer/Counters with compare modes and PWM, 4 USARTs, a byte oriented 2-wire Serial Interface, a 16-channel, 10bit ADC with optional differential input stage with programmable gain, programmable Watchdog Timer with Internal Oscillator, an SPI serial port, IEEE std. 1149.1 compliant JTAG test interface, also used for accessing the On-chip Debug system and programming and six software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or Hardware Reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except Asynchronous Timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the Crystal/Resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low power consumption. In Extended Standby mode, both the main Oscillator and the Asynchronous Timer continue to run.

The device is manufactured using Atmel's high-density nonvolatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega640/1280/1281/2560/2561 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATmega640/1280/1281/2560/2561 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

## Comparison Between ATmega1281/2561 and ATmega640/1280/2560

Each device in the ATmega640/1280/1281/2560/2561 family differs only in memory size and number of pins. Table 1 summarizes the different configurations for the six devices.

Table 1. Configuration Summary

| Device     | Flash | EEPROM | RAM | General<br>Purpose I/O pins | 16 bits resolution PWM channels | Serial<br>USARTs | ADC<br>Channels |

|------------|-------|--------|-----|-----------------------------|---------------------------------|------------------|-----------------|

| ATmega640  | 64KB  | 4KB    | 8KB | 86                          | 12                              | 4                | 16              |

| ATmega1280 | 128KB | 4KB    | 8KB | 86                          | 12                              | 4                | 16              |

| ATmega1281 | 128KB | 4KB    | 8KB | 54                          | 6                               | 2                | 8               |

| ATmega2560 | 256KB | 4KB    | 8KB | 86                          | 12                              | 4                | 16              |

| ATmega2561 | 256KB | 4KB    | 8KB | 54                          | 6                               | 2                | 8               |

## **Pin Descriptions**

6

VCC Digital supply voltage.

GND Ground.

Port A (PA7..PA0) Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each

bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset

condition becomes active, even if the clock is not running.

Port A also serves the functions of various special features of the

ATmega640/1280/1281/2560/2561 as listed on page 88.

Port B (PB7..PB0) Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each

bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset

condition becomes active, even if the clock is not running.

Port B has better driving capabilities than the other ports.

Port B also serves the functions of various special features of the

ATmega640/1280/1281/2560/2561 as listed on page 89.

Port C (PC7..PC0) Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each

bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset

condition becomes active, even if the clock is not running.

Port C also serves the functions of special features of the

ATmega640/1280/1281/2560/2561 as listed on page 92.

Port D (PD7..PD0) Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each

bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source

## ATmega640/1280/1281/2560/2561

current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATmega640/1280/1281/2560/2561 as listed on page 94.

Port E (PE7..PE0)

Port E is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port E also serves the functions of various special features of the ATmega640/1280/1281/2560/2561 as listed on page 96.

Port F (PF7..PF0)

Port F serves as analog inputs to the A/D Converter.

Port F also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port F output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port F pins that are externally pulled low will source current if the pull-up resistors are activated. The Port F pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PF7(TDI), PF5(TMS), and PF4(TCK) will be activated even if a reset occurs.

Port F also serves the functions of the JTAG interface.

Port G (PG5..PG0)

Port G is a 6-bit I/O port with internal pull-up resistors (selected for each bit). The Port G output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port G pins that are externally pulled low will source current if the pull-up resistors are activated. The Port G pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port G also serves the functions of various special features of the ATmega640/1280/1281/2560/2561 as listed on page 102.

Port H (PH7..PH0)

Port H is a 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port H output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port H pins that are externally pulled low will source current if the pull-up resistors are activated. The Port H pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port H also serves the functions of various special features of the ATmega640/1280/1281/2560/2561 as listed on page 104.

Port J (PJ7..PJ0)

Port J is a 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port J output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port J pins that are externally pulled low will source current if the pull-up resistors are activated. The Port J pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port J also serves the functions of various special features of the ATmega640/1280/1281/2560/2561 as listed on page 106.

Port K (PK7..PK0)

Port K serves as analog inputs to the A/D Converter.

Port K is a 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port K output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port K pins that are externally pulled low will source current if the pull-up resistors are activated. The Port K pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port K also serves the functions of various special features of the ATmega640/1280/1281/2560/2561 as listed on page 108.

Port L (PL7..PL0)

Port L is a 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port L output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port L pins that are externally pulled low will source current if the pull-up resistors are activated. The Port L pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port L also serves the functions of various special features of the ATmega640/1280/1281/2560/2561 as listed on page 110.

RESET

Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 23 on page 58. Shorter pulses are not guaranteed to generate a reset.

XTAL1

Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

XTAL2

Output from the inverting Oscillator amplifier.

**AVCC**

AVCC is the supply voltage pin for Port F and the A/D Converter. It should be externally connected to  $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to  $V_{CC}$  through a low-pass filter.

**AREF**

This is the analog reference pin for the A/D Converter.

# About Code Examples

This documentation contains simple code examples that briefly show how to use various parts of the device. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documentation for more details.

These code examples assume that the part specific header file is included before compilation. For I/O registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

## **AVR CPU Core**

## Introduction

This section discusses the AVR core architecture in general. The main function of the CPU core is to ensure correct program execution. The CPU must therefore be able to access memories, perform calculations, control peripherals, and handle interrupts.

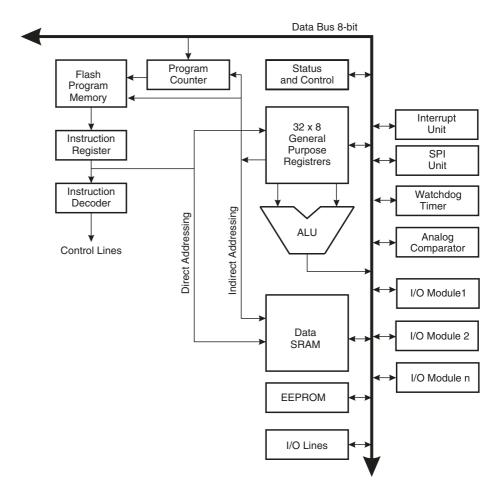

## **Architectural Overview**

Figure 4. Block Diagram of the AVR Architecture

In order to maximize performance and parallelism, the AVR uses a Harvard architecture – with separate memories and buses for program and data. Instructions in the program memory are executed with a single level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This concept enables instructions to be executed in every clock cycle. The program memory is In-System Reprogrammable Flash memory.

The fast-access Register File contains 32 x 8-bit general purpose working registers with a single clock cycle access time. This allows single-cycle Arithmetic Logic Unit (ALU) operation. In a typical ALU operation, two operands are output from the Register File,

the operation is executed, and the result is stored back in the Register File – in one clock cycle.

Six of the 32 registers can be used as three 16-bit indirect address register pointers for Data Space addressing – enabling efficient address calculations. One of the these address pointers can also be used as an address pointer for look up tables in Flash program memory. These added function registers are the 16-bit X-, Y-, and Z-register, described later in this section.

The ALU supports arithmetic and logic operations between registers or between a constant and a register. Single register operations can also be executed in the ALU. After an arithmetic operation, the Status Register is updated to reflect information about the result of the operation.

Program flow is provided by conditional and unconditional jump and call instructions, able to directly address the whole address space. Most AVR instructions have a single 16-bit word format. Every program memory address contains a 16- or 32-bit instruction.

Program Flash memory space is divided in two sections, the Boot Program section and the Application Program section. Both sections have dedicated Lock bits for write and read/write protection. The SPM instruction that writes into the Application Flash memory section must reside in the Boot Program section.

During interrupts and subroutine calls, the return address Program Counter (PC) is stored on the Stack. The Stack is effectively allocated in the general data SRAM, and consequently the Stack size is only limited by the total SRAM size and the usage of the SRAM. All user programs must initialize the SP in the Reset routine (before subroutines or interrupts are executed). The Stack Pointer (SP) is read/write accessible in the I/O space. The data SRAM can easily be accessed through the five different addressing modes supported in the AVR architecture.

The memory spaces in the AVR architecture are all linear and regular memory maps.

A flexible interrupt module has its control registers in the I/O space with an additional Global Interrupt Enable bit in the Status Register. All interrupts have a separate Interrupt Vector in the Interrupt Vector table. The interrupts have priority in accordance with their Interrupt Vector position. The lower the Interrupt Vector address, the higher the priority.

The I/O memory space contains 64 addresses for CPU peripheral functions as Control Registers, SPI, and other I/O functions. The I/O Memory can be accessed directly, or as the Data Space locations following those of the Register File, 0x20 - 0x5F. In addition, the ATmega640/1280/1281/2560/2561 has Extended I/O space from 0x60 - 0x1FF in SRAM where only the ST/STS/STD and LD/LDS/LDD instructions can be used.

# ALU – Arithmetic Logic Unit

The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate are executed. The ALU operations are divided into three main categories – arithmetic, logical, and bit-functions. Some implementations of the architecture also provide a powerful multiplier supporting both signed/unsigned multiplication and fractional format. See the "Instruction Set" section for a detailed description.

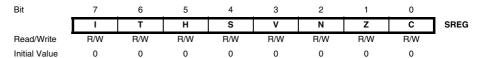

## **Status Register**

The Status Register contains information about the result of the most recently executed arithmetic instruction. This information can be used for altering program flow in order to perform conditional operations. Note that the Status Register is updated after all ALU operations, as specified in the Instruction Set Reference. This will in many cases

## ATmega640/1280/1281/2560/2561

remove the need for using the dedicated compare instructions, resulting in faster and more compact code.

The Status Register is not automatically stored when entering an interrupt routine and restored when returning from an interrupt. This must be handled by software.

The AVR Status Register - SREG - is defined as:

### • Bit 7 - I: Global Interrupt Enable

The Global Interrupt Enable bit must be set for the interrupts to be enabled. The individual interrupt enable control is then performed in separate control registers. If the Global Interrupt Enable Register is cleared, none of the interrupts are enabled independent of the individual interrupt enable settings. The I-bit is cleared by hardware after an interrupt has occurred, and is set by the RETI instruction to enable subsequent interrupts. The I-bit can also be set and cleared by the application with the SEI and CLI instructions, as described in the instruction set reference.

## • Bit 6 - T: Bit Copy Storage

The Bit Copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source or destination for the operated bit. A bit from a register in the Register File can be copied into T by the BST instruction, and a bit in T can be copied into a bit in a register in the Register File by the BLD instruction.

## • Bit 5 - H: Half Carry Flag

The Half Carry Flag H indicates a Half Carry in some arithmetic operations. Half Carry Is useful in BCD arithmetic. See the "Instruction Set Description" for detailed information.

## • Bit 4 – S: Sign Bit, S = N ⊕ V

The S-bit is always an exclusive or between the Negative Flag N and the Two's Complement Overflow Flag V. See the "Instruction Set Description" for detailed information.

## Bit 3 – V: Two's Complement Overflow Flag

The Two's Complement Overflow Flag V supports two's complement arithmetics. See the "Instruction Set Description" for detailed information.

## Bit 2 – N: Negative Flag

The Negative Flag N indicates a negative result in an arithmetic or logic operation. See the "Instruction Set Description" for detailed information.

## • Bit 1 – Z: Zero Flag

The Zero Flag Z indicates a zero result in an arithmetic or logic operation. See the "Instruction Set Description" for detailed information.

## • Bit 0 - C: Carry Flag

The Carry Flag C indicates a carry in an arithmetic or logic operation. See the "Instruction Set Description" for detailed information.

## General Purpose Register File

The Register File is optimized for the AVR Enhanced RISC instruction set. In order to achieve the required performance and flexibility, the following input/output schemes are supported by the Register File:

- · One 8-bit output operand and one 8-bit result input

- Two 8-bit output operands and one 8-bit result input

- · Two 8-bit output operands and one 16-bit result input

- · One 16-bit output operand and one 16-bit result input

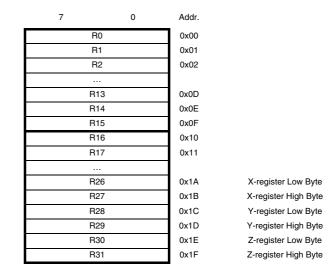

Figure 5 shows the structure of the 32 general purpose working registers in the CPU.

Figure 5. AVR CPU General Purpose Working Registers

General

Purpose

Working

Registers

Most of the instructions operating on the Register File have direct access to all registers, and most of them are single cycle instructions.

As shown in Figure 5, each register is also assigned a data memory address, mapping them directly into the first 32 locations of the user Data Space. Although not being physically implemented as SRAM locations, this memory organization provides great flexibility in access of the registers, as the X-, Y- and Z-pointer registers can be set to index any register in the file.

## ATmega640/1280/1281/2560/2561

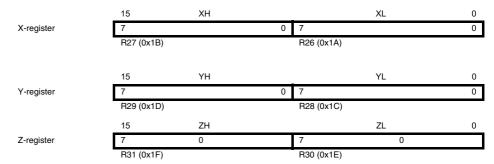

## The X-register, Y-register, and Z-register

The registers R26..R31 have some added functions to their general purpose usage. These registers are 16-bit address pointers for indirect addressing of the data space. The three indirect address registers X, Y, and Z are defined as described in Figure 6.

Figure 6. The X-, Y-, and Z-registers

In the different addressing modes these address registers have functions as fixed displacement, automatic increment, and automatic decrement (see the instruction set reference for details).

## **Stack Pointer**

The Stack is mainly used for storing temporary data, for storing local variables and for storing return addresses after interrupts and subroutine calls. The Stack Pointer Register always points to the top of the Stack. Note that the Stack is implemented as growing from higher memory locations to lower memory locations. This implies that a Stack PUSH command decreases the Stack Pointer.

The Stack Pointer points to the data SRAM Stack area where the Subroutine and Interrupt Stacks are located. This Stack space in the data SRAM must be defined by the program before any subroutine calls are executed or interrupts are enabled. The Stack Pointer must be set to point above 0x0200. The initial value of the stack pointer is the last address of the internal SRAM. The Stack Pointer is decremented by one when data is pushed onto the Stack with the PUSH instruction, and it is decremented by three when the return address is pushed onto the Stack with subroutine call or interrupt. The Stack Pointer is incremented by one when data is popped from the Stack with the POP instruction, and it is incremented by three when data is popped from the Stack with return from subroutine RET or return from interrupt RETI.

The AVR Stack Pointer is implemented as two 8-bit registers in the I/O space. The number of bits actually used is implementation dependent. Note that the data space in some implementations of the AVR architecture is so small that only SPL is needed. In this case, the SPH Register will not be present.

| Bit           | 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8   |     |

|---------------|------|------|------|------|------|------|-----|-----|-----|

|               | SP15 | SP14 | SP13 | SP12 | SP11 | SP10 | SP9 | SP8 | SPH |

|               | SP7  | SP6  | SP5  | SP4  | SP3  | SP2  | SP1 | SP0 | SPL |

|               | 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0   | _   |

| Read/Write    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W | R/W |     |

|               | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W | R/W |     |

| Initial Value | 0    | 0    | 1    | 0    | 0    | 0    | 0   | 1   |     |

|               | 1    | 1    | 1    | 1    | 1    | 1    | 1   | 1   |     |

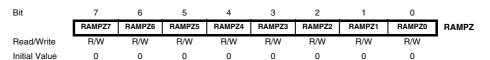

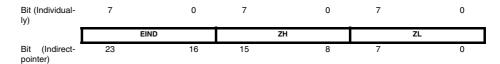

## Extended Z-pointer Register for ELPM/SPM - RAMPZ

For ELPM/SPM instructions, the Z-pointer is a concatenation of RAMPZ, ZH, and ZL, as shown in Figure 7. Note that LPM is not affected by the RAMPZ setting.

Figure 7. The Z-pointer used by ELPM and SPM

The actual number of bits is implementation dependent. Unused bits in an implementation will always read as zero. For compatibility with future devices, be sure to write these bits to zero.

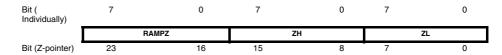

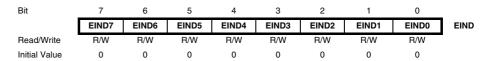

## Extended Indirect Register - EIND

For EICALL/EIJMP instructions, the Indirect-pointer to the subroutine/routine is a concatenation of EIND, ZH, and ZL, as shown in Figure 8. Note that ICALL and IJMP are not affected by the EIND setting.

Figure 8. The Indirect-pointer used by EICALL and EIJMP

The actual number of bits is implementation dependent. Unused bits in an implementation will always read as zero. For compatibility with future devices, be sure to write these bits to zero.

# Instruction Execution Timing

14

This section describes the general access timing concepts for instruction execution. The AVR CPU is driven by the CPU clock clk<sub>CPU</sub>, directly generated from the selected clock source for the chip. No internal clock division is used.

Figure 9 shows the parallel instruction fetches and instruction executions enabled by the Harvard architecture and the fast-access Register File concept. This is the basic pipelining concept to obtain up to 1 MIPS per MHz with the corresponding unique results for functions per cost, functions per clocks, and functions per power-unit.

Clk<sub>CPU</sub>

1st Instruction Fetch

1st Instruction Execute

2nd Instruction Fetch

2nd Instruction Execute

3rd Instruction Fetch

3rd Instruction Execute

4th Instruction Fetch

Figure 9. The Parallel Instruction Fetches and Instruction Executions

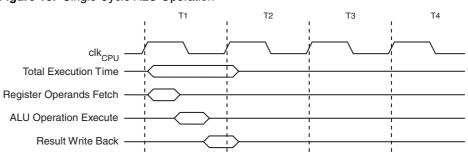

Figure 10 shows the internal timing concept for the Register File. In a single clock cycle an ALU operation using two register operands is executed, and the result is stored back to the destination register.

Figure 10. Single Cycle ALU Operation

# Reset and Interrupt Handling

The AVR provides several different interrupt sources. These interrupts and the separate Reset Vector each have a separate program vector in the program memory space. All interrupts are assigned individual enable bits which must be written logic one together with the Global Interrupt Enable bit in the Status Register in order to enable the interrupt. Depending on the Program Counter value, interrupts may be automatically disabled when Boot Lock bits BLB02 or BLB12 are programmed. This feature improves software security. See the section "Memory Programming" on page 335 for details.

The lowest addresses in the program memory space are by default defined as the Reset and Interrupt Vectors. The complete list of vectors is shown in "Interrupts" on page 69. The list also determines the priority levels of the different interrupts. The lower the address the higher is the priority level. RESET has the highest priority, and next is INTO – the External Interrupt Request 0. The Interrupt Vectors can be moved to the start of the Boot Flash section by setting the IVSEL bit in the MCU Control Register (MCUCR). Refer to "Interrupts" on page 69 for more information. The Reset Vector can also be moved to the start of the Boot Flash section by programming the BOOTRST Fuse, see "Memory Programming" on page 335.

When an interrupt occurs, the Global Interrupt Enable I-bit is cleared and all interrupts are disabled. The user software can write logic one to the I-bit to enable nested interrupts. All enabled interrupts can then interrupt the current interrupt routine. The I-bit is automatically set when a Return from Interrupt instruction – RETI – is executed.

There are basically two types of interrupts. The first type is triggered by an event that sets the Interrupt Flag. For these interrupts, the Program Counter is vectored to the actual Interrupt Vector in order to execute the interrupt handling routine, and hardware clears the corresponding Interrupt Flag. Interrupt Flags can also be cleared by writing a logic one to the flag bit position(s) to be cleared. If an interrupt condition occurs while the corresponding interrupt enable bit is cleared, the Interrupt Flag will be set and remembered until the interrupt is enabled, or the flag is cleared by software. Similarly, if one or more interrupt conditions occur while the Global Interrupt Enable bit is cleared, the corresponding Interrupt Flag(s) will be set and remembered until the Global Interrupt Enable bit is set, and will then be executed by order of priority.

The second type of interrupts will trigger as long as the interrupt condition is present. These interrupts do not necessarily have Interrupt Flags. If the interrupt condition disappears before the interrupt is enabled, the interrupt will not be triggered.

When the AVR exits from an interrupt, it will always return to the main program and execute one more instruction before any pending interrupt is served.

Note that the Status Register is not automatically stored when entering an interrupt routine, nor restored when returning from an interrupt routine. This must be handled by software.

When using the CLI instruction to disable interrupts, the interrupts will be immediately disabled. No interrupt will be executed after the CLI instruction, even if it occurs simultaneously with the CLI instruction. The following example shows how this can be used to avoid interrupts during the timed EEPROM write sequence..

```

Assembly Code Example

in r16, SREG

; store SREG value

; disable interrupts during timed sequence

cli

sbi EECR, EEMPE

; start EEPROM write

sbi EECR, EEPE

out SREG, r16

; restore SREG value (I-bit)

C Code Example

char cSREG:

cSREG = SREG; /* store SREG value */

/* disable interrupts during timed sequence */

__disable_interrupt();

EECR |= (1<<EEMPE); /* start EEPROM write */

EECR \mid = (1 << EEPE);

SREG = cSREG; /* restore SREG value (I-bit) */

```

When using the SEI instruction to enable interrupts, the instruction following SEI will be executed before any pending interrupts, as shown in this example.

### Assembly Code Example

```

sei  ; set Global Interrupt Enable

sleep ; enter sleep, waiting for interrupt

; note: will enter sleep before any pending

; interrupt(s)

```

### C Code Example

```

__enable_interrupt(); /* set Global Interrupt Enable */

__sleep(); /* enter sleep, waiting for interrupt */

/* note: will enter sleep before any pending interrupt(s) */

```

#### **Interrupt Response Time**

The interrupt execution response for all the enabled AVR interrupts is five clock cycles minimum. After five clock cycles the program vector address for the actual interrupt handling routine is executed. During these five clock cycle period, the Program Counter is pushed onto the Stack. The vector is normally a jump to the interrupt routine, and this jump takes three clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served. If an interrupt occurs when the MCU is in sleep mode, the interrupt execution response time is increased by five clock cycles. This increase comes in addition to the start-up time from the selected sleep mode.

A return from an interrupt handling routine takes five clock cycles. During these five clock cycles, the Program Counter (three bytes) is popped back from the Stack, the Stack Pointer is incremented by three, and the I-bit in SREG is set.

## ANEXO II. DATASHEET ADXL345

# 3-Axis, $\pm 2$ g/ $\pm 4$ g/ $\pm 8$ g/ $\pm 16$ g Digital Accelerometer

Data Sheet ADXL345

#### **FEATURES**

Ultralow power: as low as 23  $\mu A$  in measurement mode and 0.1  $\mu A$  in standby mode at  $V_S = 2.5$  V (typical) Power consumption scales automatically with bandwidth User-selectable resolution

**Fixed 10-bit resolution**

Full resolution, where resolution increases with *g* range, up to 13-bit resolution at ±16 *g* (maintaining 4 m*g*/LSB scale factor in all *g* ranges)

Embedded memory management system with FIFO technology minimizes host processor load Single tap/double tap detection Activity/inactivity monitoring Free-fall detection

Supply voltage range: 2.0 V to 3.6 V I/O voltage range: 1.7 V to  $V_{\text{S}}$

SPI (3- and 4-wire) and I<sup>2</sup>C digital interfaces

Flexible interrupt modes mappable to either interrupt pin Measurement ranges selectable via serial command

Bandwidth selectable via serial command

Wide temperature range (-40°C to +85°C)

10,000 g shock survival Pb free/RoHS compliant

Small and thin: 3 mm  $\times$  5 mm  $\times$  1 mm LGA package

## **APPLICATIONS**

Handsets

Medical instrumentation

Gaming and pointing devices

Industrial instrumentation

Personal navigation devices

Hard disk drive (HDD) protection

#### **GENERAL DESCRIPTION**

The ADXL345 is a small, thin, ultralow power, 3-axis accelerometer with high resolution (13-bit) measurement at up to  $\pm 16$  g. Digital output data is formatted as 16-bit twos complement and is accessible through either a SPI (3- or 4-wire) or I<sup>2</sup>C digital interface.

The ADXL345 is well suited for mobile device applications. It measures the static acceleration of gravity in tilt-sensing applications, as well as dynamic acceleration resulting from motion or shock. Its high resolution (3.9 mg/LSB) enables measurement of inclination changes less than  $1.0^{\circ}$ .

Several special sensing functions are provided. Activity and inactivity sensing detect the presence or lack of motion by comparing the acceleration on any axis with user-set thresholds. Tap sensing detects single and double taps in any direction. Freefall sensing detects if the device is falling. These functions can be mapped individually to either of two interrupt output pins. An integrated memory management system with a 32-level first in, first out (FIFO) buffer can be used to store data to minimize host processor activity and lower overall system power consumption.

Low power modes enable intelligent motion-based power management with threshold sensing and active acceleration measurement at extremely low power dissipation.

The ADXL345 is supplied in a small, thin, 3 mm  $\times$  5 mm  $\times$  1 mm, 14-lead, plastic package.

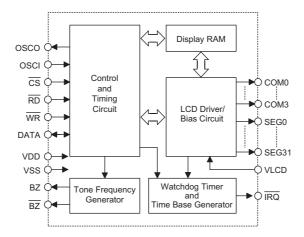

# ADXL345 ADXL345 POWER MANAGEMENT CONTROL INT1 AND INTERRUPT LOGIC INT2 SENSOR SDA/SDI/SDIO SDA/SDI/SDIO SDA/SDI/SDIO SSCI/SCLK GND GND

Figure 1.

Rev. E Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2009–2015 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

ADXL345 Data Sheet

## TABLE OF CONTENTS

| Features1                                   |

|---------------------------------------------|

| Applications1                               |

| General Description                         |

| Functional Block Diagram                    |

| Revision History                            |

| Specifications                              |

| Absolute Maximum Ratings6                   |

| Thermal Resistance                          |

| Package Information                         |

| ESD Caution6                                |

| Pin Configuration and Function Descriptions |

| Typical Performance Characteristics         |

| Theory of Operation                         |

| Power Sequencing                            |

| Power Savings 14                            |

| Serial Communications                       |

| SPI                                         |

| I <sup>2</sup> C18                          |

| Interrupts                                  |

| EIEO 21                                     |

| Self- lest                              | 22 |

|-----------------------------------------|----|

| Register Map                            | 23 |

| Register Definitions                    | 24 |

| Applications Information                | 28 |

| Power Supply Decoupling                 | 28 |

| Mechanical Considerations for Mounting  | 28 |

| Tap Detection                           | 28 |

| Threshold                               | 29 |

| Link Mode                               | 29 |

| Sleep Mode vs. Low Power Mode           | 30 |

| Offset Calibration                      | 30 |

| Using Self-Test                         | 31 |

| Data Formatting of Upper Data Rates     | 32 |

| Noise Performance                       | 33 |

| Operation at Voltages Other Than 2.5 V  | 33 |

| Offset Performance at Lowest Data Rates | 34 |

| Axes of Acceleration Sensitivity        | 35 |

| Layout and Design Recommendations       | 36 |

| Outline Dimensions                      | 37 |

| Ordanina Cuida                          | 27 |

Data Sheet ADXL345

## **REVISION HISTORY**

| 6/15—Rev. D to Rev. E                                          |   |

|----------------------------------------------------------------|---|

| Changes to Features Section and General                        |   |

| Description Section                                            | 1 |

| Change to Figure 361                                           | 5 |

| Change to FIFO Section                                         | 1 |

| 2/13—Rev. C to Rev. D                                          |   |

| Changes to Figure 13, Figure 14, and Figure 15                 | 9 |

| Change to Table 15                                             | 2 |

| 5/11—Rev. B to Rev. C                                          |   |

| Added Preventing Bus Traffic Errors Section1                   | 5 |

| Changes to Figure 37, Figure 38, Figure 391                    | 6 |

| Changes to Table 121                                           | 9 |

| Changes to Using Self-Test Section3                            | 1 |

| Changes to Axes of Acceleration Sensitivity Section            | 5 |

| 11/10—Rev. A to Rev. B                                         |   |

| Change to 0 g Offset vs. Temperature for Z-Axis Parameter,     |   |

| Table 1                                                        |   |

| Changes to Figure 10 to Figure 15                              | 9 |

| Changes to Ordering Guide                                      | 7 |

| 4/10—Rev. 0 to Rev. A                                          |   |

| Changes to Features Section and General                        |   |

| Description Section                                            | 1 |

| Changes to Specifications Section                              | 3 |

| Changes to Table 2 and Table 3                                 | 5 |

| Added Package Information Section, Figure 2, and Table 4;      |   |

| Renumbered Sequentially                                        | 5 |

| Changes to Pin 12 Description, Table 5                         | 6 |

| Added Typical Performance Characteristics Section              | 7 |

| Changes to Theory of Operation Section and Power Sequencin     | g |

| Section1                                                       | 2 |

| Changes to Powers Savings Section, Table 7, Table 8, Auto Slee | р |

| Mode Section, and Standby Mode Section                         | 3 |

| Changes to SPI Section 1                                       | 4 |

| Changes to Figure 36 to Figure 3815                           |

|---------------------------------------------------------------|

| Changes to Table 9 and Table 1016                             |

| Changes to I <sup>2</sup> C Section and Table 1117            |

| Changes to Table 1218                                         |

| Changes to Interrupts Section, Activity Section, Inactivity   |

| Section, and FREE_FALL Section19                              |

| Added Table 13                                                |

| Changes to FIFO Section20                                     |

| Changes to Self-Test Section and Table 15 to Table 1821       |

| Added Figures 42 and Table 1421                               |

| Changes to Table 1922                                         |

| Changes to Register 0x1D—THRESH_TAP (Read/Write)              |

| Section, Register 0x1E, Register 0x1F, Register 0x20—OFSX,    |

| OFSY, OSXZ (Read/Write) Section, Register 0x21—DUR            |

| (Read/Write) Section, Register 0x22—Latent (Read/Write)       |

| Section, and Register 0x23—Window (Read/Write) Section23      |

| Changes to ACT_X Enable Bits and INACT_X Enable Bit           |

| Section, Register 0x28—THRESH_FF (Read/Write) Section,        |

| Register 0x29—TIME_FF (Read/Write) Section, Asleep Bit        |

| Section, and AUTO_SLEEP Bit Section24                         |

| Changes to Sleep Bit Section                                  |

| Changes to Power Supply Decoupling Section, Mechanical        |

| Considerations for Mounting Section, and Tap Detection        |

| Section                                                       |

| Changes to Threshold Section                                  |

| Changes to Sleep Mode vs. Low Power Mode Section29            |

| Added Offset Calibration Section29                            |

| Changes to Using Self-Test Section30                          |

| Added Data Formatting of Upper Data Rates Section, Figure 48, |

| and Figure 4931                                               |

| Added Noise Performance Section, Figure 50 to Figure 52, and  |

| Operation at Voltages Other Than 2.5 V Section32              |

| Added Offset Performance at Lowest Data Rates Section and     |

| Figure 53 to Figure 55                                        |

6/09—Revision 0: Initial Version

ADXL345 Data Sheet

## **SPECIFICATIONS**

$T_A = 25$ °C,  $V_S = 2.5$  V,  $V_{DD\,I/O} = 1.8$  V, acceleration = 0 g,  $C_S = 10~\mu F$  tantalum,  $C_{I/O} = 0.1~\mu F$ , output data rate (ODR) = 800 Hz, unless otherwise noted. All minimum and maximum specifications are guaranteed. Typical specifications are not guaranteed.

Table 1.

| Parameter                                                             | Test Conditions                                                                    | Min   | Typ <sup>1</sup> | Max     | Unit           |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------|-------|------------------|---------|----------------|

| SENSOR INPUT                                                          | Each axis                                                                          |       |                  |         |                |

| Measurement Range                                                     | User selectable                                                                    |       | ±2, ±4, ±8, ±16  |         | g              |

| Nonlinearity                                                          | Percentage of full scale                                                           |       | ±0.5             |         | %              |

| Inter-Axis Alignment Error                                            |                                                                                    |       | ±0.1             |         | Degree         |

| Cross-Axis Sensitivity <sup>2</sup>                                   |                                                                                    |       | ±1               |         | %              |

| OUTPUT RESOLUTION                                                     | Each axis                                                                          |       |                  |         |                |

| All g Ranges                                                          | 10-bit resolution                                                                  |       | 10               |         | Bits           |

| ±2 g Range                                                            | Full resolution                                                                    |       | 10               |         | Bits           |

| ±4 g Range                                                            | Full resolution                                                                    |       | 11               |         | Bits           |

| ±8 g Range                                                            | Full resolution                                                                    |       | 12               |         | Bits           |

| ±16 g Range                                                           | Full resolution                                                                    |       | 13               |         | Bits           |

| SENSITIVITY                                                           | Each axis                                                                          |       |                  |         | - 100          |

| Sensitivity at X <sub>OUT</sub> , Y <sub>OUT</sub> , Z <sub>OUT</sub> | All g-ranges, full resolution                                                      | 230   | 256              | 282     | LSB/g          |

| Jensierity 447,0017 10017 2001                                        | $\pm 2 g$ , 10-bit resolution                                                      | 230   | 256              | 282     | LSB/g          |

|                                                                       | $\pm 4 g$ , 10-bit resolution                                                      | 115   | 128              | 141     | LSB/g          |

|                                                                       | $\pm 8  g$ , 10-bit resolution                                                     | 57    | 64               | 71      | LSB/g          |

|                                                                       | $\pm 16  g$ , 10-bit resolution                                                    | 29    | 32               | 35      | LSB/g          |

| Sensitivity Deviation from Ideal                                      | All g-ranges                                                                       | 29    | ±1.0             | 33      | %              |

| •                                                                     |                                                                                    | 2.5   |                  | 4.2     |                |

| Scale Factor at Xout, Yout, Zout                                      | All g-ranges, full resolution                                                      | 3.5   | 3.9              | 4.3     | mg/LSE         |

|                                                                       | ±2 g, 10-bit resolution                                                            | 3.5   | 3.9              | 4.3     | mg/LSE         |

|                                                                       | ±4 g, 10-bit resolution                                                            | 7.1   | 7.8              | 8.7     | mg/LSE         |

|                                                                       | ±8 g, 10-bit resolution                                                            | 14.1  | 15.6             | 17.5    | mg/LSE         |

|                                                                       | $\pm 16 g$ , 10-bit resolution                                                     | 28.6  | 31.2             | 34.5    | mg/LSE         |

| Sensitivity Change Due to Temperature                                 |                                                                                    |       | ±0.01            |         | %/°C           |

| 0 g OFFSET                                                            | Each axis                                                                          |       |                  |         |                |

| 0 g Output for Хоит, Yоит                                             |                                                                                    | -150  | 0                | +150    | m <i>g</i>     |

| 0 g Output for Z <sub>ouт</sub>                                       |                                                                                    | -250  | 0                | +250    | m <i>g</i>     |

| 0 $g$ Output Deviation from Ideal, $X_{OUT}$ , $Y_{OUT}$              |                                                                                    |       | ±35              |         | m <i>g</i>     |

| $0 g$ Output Deviation from Ideal, $Z_{OUT}$                          |                                                                                    |       | ±40              |         | m <i>g</i>     |

| 0 g Offset vs. Temperature for X-, Y-Axes                             |                                                                                    |       | ±0.4             |         | mg/°C          |

| 0 $g$ Offset vs. Temperature for Z-Axis                               |                                                                                    |       | ±1.2             |         | m <i>g</i> /°C |

| NOISE                                                                 |                                                                                    |       |                  |         |                |

| X-, Y-Axes                                                            | ODR = 100 Hz for $\pm 2 g$ , 10-bit resolution or all $g$ -ranges, full resolution |       | 0.75             |         | LSB rm         |

| Z-Axis                                                                | ODR = 100 Hz for $\pm 2 g$ , 10-bit resolution or all $g$ -ranges, full resolution |       | 1.1              |         | LSB rms        |

| OUTPUT DATA RATE AND BANDWIDTH                                        | User selectable                                                                    |       |                  |         |                |

| Output Data Rate (ODR) <sup>3, 4, 5</sup>                             |                                                                                    | 0.1   |                  | 3200    | Hz             |

| SELF-TEST <sup>6</sup>                                                |                                                                                    |       |                  |         |                |

| Output Change in X-Axis                                               |                                                                                    | 0.20  |                  | 2.10    | g              |

| Output Change in Y-Axis                                               |                                                                                    | -2.10 |                  | -0.20   | g              |

| Output Change in Z-Axis                                               |                                                                                    | 0.30  |                  | 3.40    | g              |

| POWER SUPPLY                                                          |                                                                                    |       |                  | -       |                |

| Operating Voltage Range (V <sub>s</sub> )                             |                                                                                    | 2.0   | 2.5              | 3.6     | V              |

| Interface Voltage Range (VDD VO)                                      |                                                                                    | 1.7   | 1.8              | $V_{S}$ | V              |

| Supply Current                                                        | ODR ≥ 100 Hz                                                                       |       | 140              | -       | μA             |

| F. F. A                                                               | ODR < 10 Hz                                                                        |       | 30               |         | μΑ             |

|                                                                       |                                                                                    |       |                  |         | l L.,          |

| Standby Mode Leakage Current                                          |                                                                                    |       | 0.1              |         | μΑ             |

Rev. E | Page 4 of 40

**Data Sheet** ADXL345

| Parameter                   | Test Conditions | Min Typ¹ | Max | Unit       |

|-----------------------------|-----------------|----------|-----|------------|

| TEMPERATURE                 |                 |          |     |            |

| Operating Temperature Range |                 | -40      | +85 | °C         |

| WEIGHT                      |                 |          |     |            |

| Device Weight               |                 | 30       |     | m <i>g</i> |

<sup>&</sup>lt;sup>1</sup> The typical specifications shown are for at least 68% of the population of parts and are based on the worst case of mean ±1 σ, except for 0 g output and sensitivity, which represents the target value. For 0 g offset and sensitivity, the deviation from the ideal describes the worst case of mean ±1 σ.

<sup>2</sup> Cross-axis sensitivity is defined as coupling between any two axes.

5 Output data rates below 6.25 Hz exhibit additional offset shift with increased temperature, depending on selected output data rate. Refer to the Offset Performance at Lowest Data Rates section for details.

6 Self-test change is defined as the output (g) when the SELF\_TEST bit = 1 (in the DATA\_FORMAT register, Address 0x31) minus the output (g) when the SELF\_TEST bit = 0. Due to device filtering, the output reaches its final value after  $4 \times \tau$  when enabling or disabling self-test, where  $\tau = 1/(\text{data rate})$ . The part must be in normal power operation (LOW\_POWER bit = 0 in the BW\_RATE register, Address 0x2C) for self-test to operate correctly.

<sup>7</sup> Turn-on and wake-up times are determined by the user-defined bandwidth. At a 100 Hz data rate, the turn-on and wake-up times are each approximately 11.1 ms. For other data rates, the turn-on and wake-up times are each approximately  $\tau + 1.1$  in milliseconds, where  $\tau = 1/(data \, rate)$ .

<sup>&</sup>lt;sup>3</sup> Bandwidth is the –3 dB frequency and is half the output data rate, bandwidth = ODR/2.

<sup>4</sup> The output format for the 3200 Hz and 1600 Hz ODRs is different than the output format for the remaining ODRs. This difference is described in the Data Formatting of Upper Data Rates section.

ADXL345 Data Sheet

## **ABSOLUTE MAXIMUM RATINGS**

## Table 2.

| Parameter                     | Rating                                                                    |

|-------------------------------|---------------------------------------------------------------------------|

| Acceleration                  |                                                                           |

| Any Axis, Unpowered           | 10,000 <i>g</i>                                                           |

| Any Axis, Powered             | 10,000 <i>g</i>                                                           |

| $V_S$                         | −0.3 V to +3.9 V                                                          |

| V <sub>DD I/O</sub>           | −0.3 V to +3.9 V                                                          |

| Digital Pins                  | $-0.3 \text{ V to V}_{DD \text{ I/O}} + 0.3 \text{ V or } 3.9 \text{ V},$ |

|                               | whichever is less                                                         |

| All Other Pins                | −0.3 V to +3.9 V                                                          |

| Output Short-Circuit Duration | Indefinite                                                                |

| (Any Pin to Ground)           |                                                                           |

| Temperature Range             |                                                                           |

| Powered                       | -40°C to +105°C                                                           |

| Storage                       | −40°C to +105°C                                                           |

|                               |                                                                           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

**Table 3. Package Characteristics**

| Package Type    | θ <sub>JA</sub> | θις    | Device Weight |

|-----------------|-----------------|--------|---------------|

| 14-Terminal LGA | 150°C/W         | 85°C/W | 30 mg         |

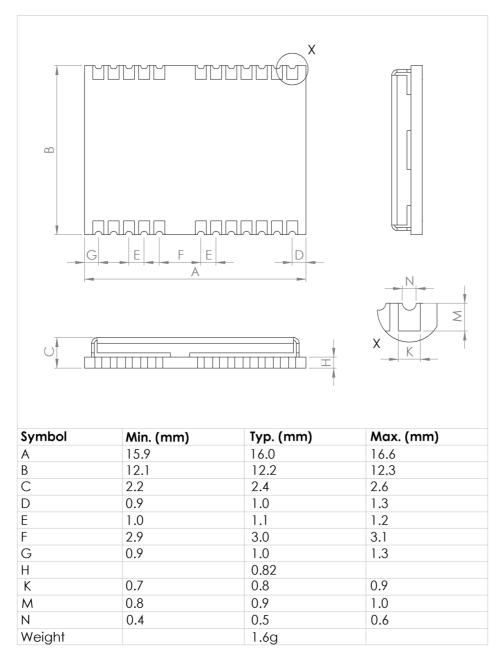

## **PACKAGE INFORMATION**

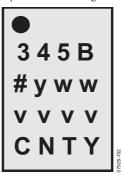

The information in Figure 2 and Table 4 provide details about the package branding for the ADXL345. For a complete listing of product availability, see the Ordering Guide section.

Figure 2. Product Information on Package (Top View)

**Table 4. Package Branding Information**

| Branding Key | Field Description           |

|--------------|-----------------------------|

| 345B         | Part identifier for ADXL345 |

| #            | RoHS-compliant designation  |

| yww          | Date code                   |

| vvvv         | Factory lot code            |

| CNTY         | Country of origin           |

## **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

ADXL345 **Data Sheet**

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

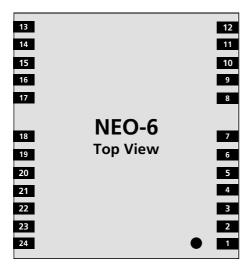

Figure 3. Pin Configuration (Top View)

**Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic            | Description                                                                                              |

|---------|---------------------|----------------------------------------------------------------------------------------------------------|

| 1       | V <sub>DD I/O</sub> | Digital Interface Supply Voltage.                                                                        |

| 2       | GND                 | This pin must be connected to ground.                                                                    |

| 3       | RESERVED            | Reserved. This pin must be connected to $V_{\mbox{\scriptsize S}}$ or left open.                         |

| 4       | GND                 | This pin must be connected to ground.                                                                    |

| 5       | GND                 | This pin must be connected to ground.                                                                    |

| 6       | Vs                  | Supply Voltage.                                                                                          |

| 7       | CS                  | Chip Select.                                                                                             |

| 8       | INT1                | Interrupt 1 Output.                                                                                      |

| 9       | INT2                | Interrupt 2 Output.                                                                                      |

| 10      | NC                  | Not Internally Connected.                                                                                |

| 11      | RESERVED            | Reserved. This pin must be connected to ground or left open.                                             |

| 12      | SDO/ALT ADDRESS     | Serial Data Output (SPI 4-Wire)/Alternate I <sup>2</sup> C Address Select (I <sup>2</sup> C).            |

| 13      | SDA/SDI/SDIO        | Serial Data (I <sup>2</sup> C)/Serial Data Input (SPI 4-Wire)/Serial Data Input and Output (SPI 3-Wire). |

| 14      | SCL/SCLK            | Serial Communications Clock. SCL is the clock for I <sup>2</sup> C, and SCLK is the clock for SPI.       |

## ANEXO III. DATASHEET HC-12

## HC-12 Wireless Serial Port Communication Module

## User Manual v1.18

## **Product Application**

- Wireless sensor

- Community building security

- Robot wireless control

- Industrial remote control and telemetering

- Automatic data acquisition

- Container information management

- POS system

- Wireless acquisition of gas meter data

- Vehicle keyless entry system

- PC wireless networking

. . . . . .

Document: 2012/10

### **Product Features**

- Long-distance wireless transmission (1,000m in open space/baud rate 5,000bps in the air)

- Working frequency range (433.4-473.0MHz, up to 100 communication channels)

- Maximum 100mW (20dBm) transmitting power (8 gears of power can be set)

- Three working modes, adapting to different application situations

- Built-in MCU, performing communication with external device through serial port

- The number of bytes transmitted unlimited to one time

- Update software version through serial port

### **Product Introduction**

HC-12 wireless serial port communication module is a new-generation multichannel embedded wireless data transmission module. Its wireless working frequency band is 433.4-473.0MHz, multiple channels can be set, with the stepping of 400 KHz, and there are totally 100 channels. The maximum transmitting power of module is 100mW (20dBm), the receiving sensitivity is -117dBm at baud rate of 5,000bps in the air, and the communication distance is 1,000m in open space.

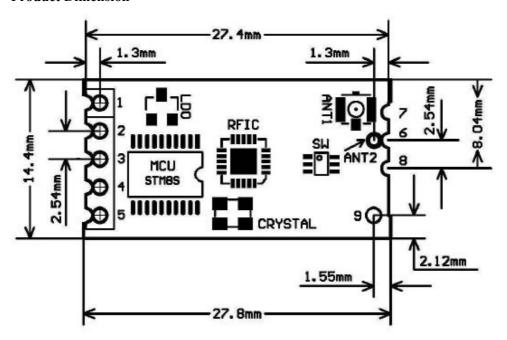

The module is encapsulated with stamp hole, can adopt patch welding, and its dimension is  $27.8 \text{mm} \times 14.4 \text{mm} \times 4 \text{mm}$  (including antenna cap, excluding spring antenna), so it is very convenient for customers to go into application system. There is a PCB antenna pedestal ANT1 on the module, and user can use external antenna of 433M frequency band through coaxial cable; there is also an antenna solder eye ANT2 in the module, and it is convenient for user to weld spring antenna. User could select one of these antennas according to use requirements.

There is MCU inside the module, and user don't need to program the module separately, and all transparent transmission mode is only responsible for receiving and sending serial port data, so it is convenient to use. The module adopts multiple serial port transparent transmission modes, and user could select them by AT command according to use requirements. The average working current of three modes FU1, FU2 and FU3 in idle state is  $80\mu a$ , 3.6mA an 16mA respectively, and the maximum working current is 100mA (in transmitting state).

## **Product Configuration**

Standard configuration of HC-12 module only contains one 433MHz-frequency-band wireless communication module with IPEX20279-001E-03 standard RF socket. The optional accessories are 433MHz-frequency-band spring antenna, IPEX-to-BNC coaxial cable and matching 433MHz-frequency-band omni-directional rubber antenna of BNC connector. User could purchase them according to use requirements.

## **Product Dimension**

## **Definition of Pins**

HC-12 module can adopt patch welding, or weld 2.54mm-spacing pin header, and directly insert it onto user's PCB. The module totally has nine pins and one RF antenna pedestal ANT1, and their definitions are as shown in the table below:

| Pin | Definition Definition | I/O direction | Note                                                                                                                                                                                                                                                                                                          |

|-----|-----------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VCC                   |               | Power supply input, DC3.2V-5.5V, with load capacity not less than 200mA. (Note: If the module is working in transmitting state for a long time, it is suggested that one 1N4007 diode should be connected in series when the power voltage is greater than 4.5V, to avoid heating of built-in LDO of module.) |

| 2   | GND                   |               | Common ground                                                                                                                                                                                                                                                                                                 |

| 3    | RXD | Input, weak         | URAT input port,       |

|------|-----|---------------------|------------------------|

|      |     | pull-up             | TTL level; 1k          |

|      |     |                     | resistance has been    |

|      |     |                     | connected in series    |

|      |     |                     | inside                 |

| 4    | TXD | Output              | URAT output port,      |

|      |     |                     | TTL level; 1k          |

|      |     |                     | resistance has been    |

|      |     |                     | connected in series    |

|      |     |                     | inside                 |

| 5    | SET | Input, internal 10k | Parameter setting      |

|      |     | pull-up resistance  | control pin, valid for |

|      |     |                     | low level; 1k          |

|      |     |                     | resistance has been    |

|      |     |                     | connected in series    |

|      |     |                     | inside                 |

| 6    | ANT | Input/output        | 433MHz antenna pin     |

| 7    | GND |                     | Common ground          |

| 8    | GND |                     | Common ground          |

| 9    | NC  |                     | No connection, used    |

|      |     |                     | in fixing, compatible  |

|      |     |                     | with HC-11 module      |

|      |     |                     | pin position           |

| ANT1 | ANT | Input/output        | IPEX20279-001E-03      |

|      |     |                     | antenna socket         |

| ANT2 | ANT | Input/output        | 433MHz spring          |

|      |     |                     | antenna solder eye     |

Pints 1-6 have two bonding pads respectively, and the outer half-hole bonding pad is used in patch welding. When the inner bonding pad ANT2 of Pin 6 is used in patch welding, the spring antenna can be welded with hands. The inner round-hole bonding pads of Pins 1-5 are used to weld 2.54mm-spacing pin header, and can be directly inserted onto user's PCB socket.

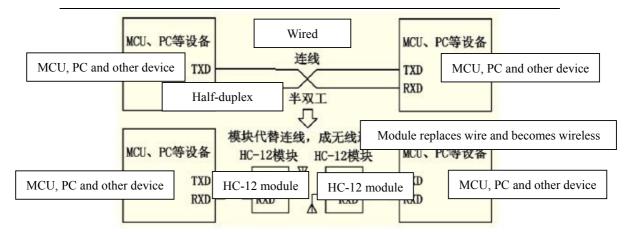

Wireless serial port transparent transmission

(1) Simple introduction of working p principle

As shown in the above figure, HC-12 module is used in physical wiring when replacing half duplex communication. The left device sends serial port data to module, and after RXD port of left module receives the serial port data, it will automatically send the data into the air via radio wave. The right module can automatically receive the data, and restore, from TXD, the serial port data originally sent by the left device. It is the same from right to left. Only half duplex state is available between modules, and they cannot receive and send data at the same time.

## (2) Serial port transparent transmission

HC-12 module has three serial port transparent transmission modes, expressed with FU1, FU2 and FU3 respectively. In the use, all modes are only responsible for receiving and sending serial port data rather than wireless transmission. The default working mode of system is in FU3 full-speed mode, and in this mode, the baud rate in this air can be automatically adjusted according to baud rate of serial port, and the communication distance will be the farthest at the low baud rate. Different modes cannot transmit data to each other, and user could select the optimal mode according to practical circumstances.

The modules are usually used in pairs, and transmit data by means of half duplex. Meanwhile, the transparent transmission mode, serial port baud rate, and wireless communication channel of two paired modules shall be set to be the same. The default setting is FU3, 9,600bps (8-dibit data, no check, one stop bit), CH001 (433.4MHz).

Use the number of bytes continuously sent to serial port of module unlimited to one time. However, considering ambient interference and other factors, if thousands of data size is sent continuously at a time, some number of bytes may be lost. Therefore, the upper computer shall have response and resending mechanism, to avoid information loss.

### (3) Three serial port transparent transmission modes

When HC-12 module leaves the factory, its default serial port transparent transmission mode is FU3. Then the module is in full-speed state, and the idle current is about

16mA. In this mode, the module can automatically adjust the baud rate of wireless transmission in the air according to serial port baud rate, and the corresponding relationship is as shown in the table below:

| Seri | 1,200b   | 2,400b | 4,800b    | 9,600b | 19,200b   | 38,400b | 57,600b    | 115,200b |

|------|----------|--------|-----------|--------|-----------|---------|------------|----------|

| al   | ps       | ps     | ps        | ps     | ps        | ps      | ps         | ps       |

| port |          |        |           |        |           |         |            |          |

| bau  |          |        |           |        |           |         |            |          |

| d    |          |        |           |        |           |         |            |          |

| rate |          |        |           |        |           |         |            |          |

| Bau  | 5,000bps |        | 15,000bps |        | 58,000bps |         | 236,000bps |          |

| d    |          |        |           |        |           |         |            |          |

| rate |          |        |           |        |           |         |            |          |

| in   |          |        |           |        |           |         |            |          |

| the  |          |        |           |        |           |         |            |          |

| air  |          |        |           |        |           |         |            |          |

To get the farthest communication distance, the serial port baud rate can be set to be low. For short-time transmission of mass data, set the serial port baud rate to be high, but the communication distance will be reduced accordingly.

The receiving sensitivity of module at different baud rates in the air is as shown in the table below: